# **Introduction to Logic Design**

# **Second Edition**

Sajjan G. Shjiva

University of Alabama in Huntsville Huntsville, Alabama

MARCEL DEKKER, INC.

New York • Basel • Hong Kong

#### **Library of Congress Cataloging-in-Publication Data**

Shiva, Sajjan G.

Introduction to logic design / Sajjan G. Shiva — 2nd ed.

p. cm

Includes index.

ISBN 0-8247-0082-1

1. Digital electronics. 2. Logic design. I. Title.

TK7868.D5S433 1998

621.39'5—dc21

94-46945

**CIP**

The publisher offers discounts on this book when ordered in bulk quantities. For more information, write to Special Sales/Professional Marketing at the address below.

This book is printed on acid-free paper.

Copyright © 1998 by Marcel Dekker, Inc. All Rights Reserved.

Neither this book nor any part may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying, microfilming, and recording, or by any information storage and retrieval system, without permission in writing from the publisher.

Marcel Dekker, Inc.

270 Madison Avenue, New York, New York 10016

http://www.dekker.com

Current printing (last digit):

10987654321

PRINTED IN THE UNITED STATES OF AMERICA

In Memory of My Mother

### **Preface**

This book is an introduction to analysis and design of digital circuits. A course in digital systems design is now required in both electrical/computer engineering and computer science curricula. Computer science students in general are good at assimilating algorithmic solutions to problems, while electrical/computer engineering students absorb hardware concepts readily. I have therefore attempted to blend the theoretical and practical implementation aspects of digital systems in each chapter of this book. Thus the book is suitable for use in both curricula at the sophomore or junior level. It covers all the topics for the ACM curriculum 79 course CS4 and IEEE Computer Society's model program course SA6. It is also suitable for self-study, for professionals requiring a knowledge of digital hardware design, and as a reference for modern techniques in logic design for those familiar with older design methodologies.

This edition of the book covers the same set of topics covered in the first edition; however, the topics were rearranged to provide a smoother transition. The material on memory systems design from the first edition has been omitted, since that topic more aptly belongs to the first course on computer architecture. Details on integrated circuits (ICs) have been updated and several sections have been rewritten to clarify presentation. Also, the end-of-chapter problems have been updated.

# **Number Systems and Codes**

# 1.1 Digital System Organization

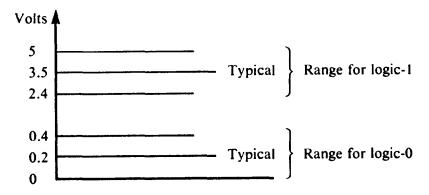

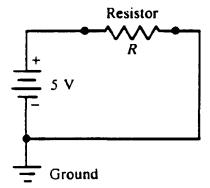

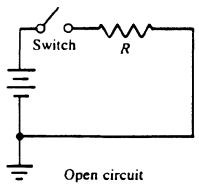

We are surrounded today by a myriad of digital devices. Digital watches, electronic calculators, digital meters, microprocessors, and digital computers are all examples of such systems. A digital system manipulates data that are composed of a finite number of discrete elements. The results that the digital system produces are also made up of a set of discrete elements. In contrast, an analog system manipulates data that are represented in a continuous form, producing results that also appear in continuous form. In electronic digital systems, the discrete elements of data correspond to signals which are either voltage levels or current magnitudes. Each specified voltage level can represent an element of data. The signal thus can be at only one of these specified levels. In an analog system, signals assume values in a continuous range of voltage.

For example, the signals in a digital system might be restricted to two levels (0 and +5 volts), corresponding to the two discrete elements of information, while analog signals may take any value in the range of +5 to -5 volts. Compared with analog systems, digital systems are more accurate and reliable. Hence, they are replacing analog systems wherever possible, although for certain applications analog systems are clearly superior. In order to introduce the terminology, we will now examine two popular digital devices.

An electronic calculator is a digital device in which input data are composed of discrete values entered through the keyboard, and the instructions to manipulate the data are also entered through the keyboard by means of the function keys. The output is a set of discrete values represented as digits on the display. In a programmable calculator, the sequence of instructions (i.e., the *program*) is stored in the calculator memory and used repeatedly on various sets of input data to produce results.

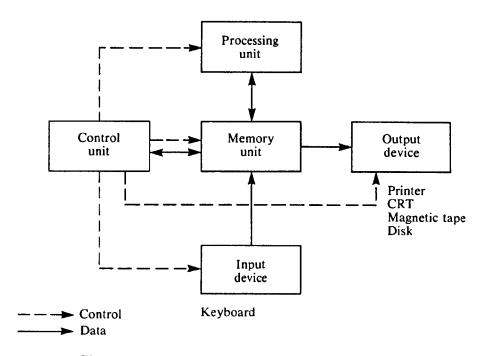

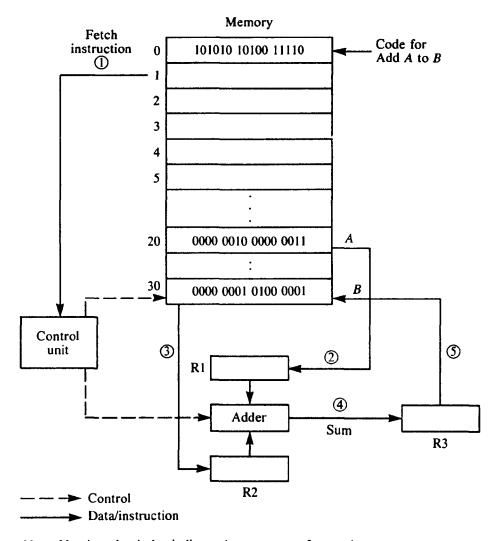

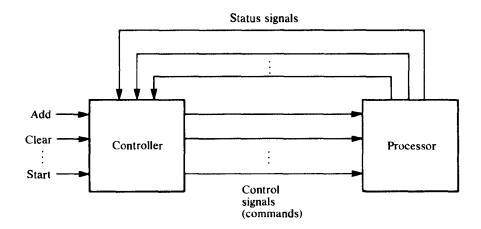

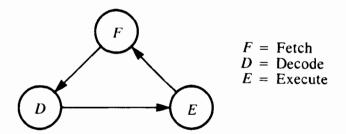

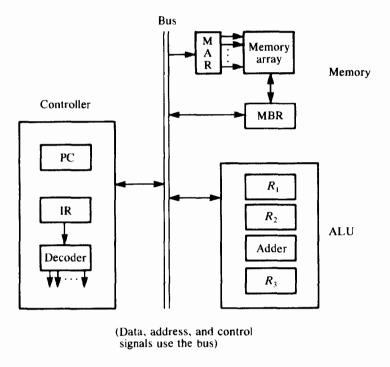

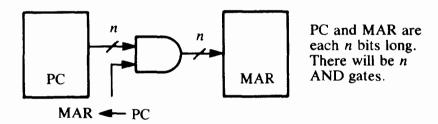

Figure 1.1 shows the components of a digital computer, the most general digital device. The program to manipulate the data is first brought into the *memory unit* through the *input device*. The data to be processed are then brought into the memory unit, also through the input device. The *control unit* fetches instructions from the program stored in the memory one at a time, analyzes each instruction, and instructs the *processing unit* to perform the operations called for by the instruction. The results produced by the processing unit are forwarded to the memory unit for storage and then transferred to the *output device*.

As mentioned earlier, the elements in the discrete data representation correspond to discrete voltage levels or current magnitudes in the digital system hardware. If the digital system is required to manipulate only numeric data, for instance, it will be best to use 10 voltage levels, with each level corresponding to a decimal digit. But the noise introduced by multiple levels make such representation impractical. Therefore, digital systems typ-

Figure 1.1 Components of a digital computer.

ically use a two-level representation, with one voltage level representing a 0 and the other representing a 1. To represent all 10 decimal digits using this *binary* (two-valued) alphabet of 0 and 1, a unique pattern of 0s and 1s is assigned to each digit. For example, in an electronic calculator, each keystroke should produce a pattern of 0s and 1s corresponding to the digit or the operation represented by that key.

Because the data elements and operations are all represented in binary form in all practical digital systems, a good understanding of the binary number system and data representation is basic to the analysis and design of digital system hardware. In this chapter, we will discuss the binary number system in detail. In addition we will discuss two other widely used systems: *octal* and *hexadecimal*. These two number systems are useful in representing binary information in a compact form. When the human user of the digital system works with data manipulated by the system, either to verify it or to communicate it to another user, the compactness provided by these systems is helpful. As we will see in this chapter, data conversion from one number system to the other can be performed in a straightforward manner.

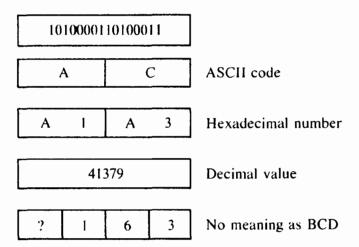

The data to be processed by the digital system are made up of decimal digits, alphabetic characters, and special characters, such as +, -, \*. The digital system uses a unique pattern of 0s and 1s to represent each of these digits and characters in the binary form. The collection of these binary patterns is called the *binary code*. Various binary codes have been devised by digital system designers over the years. Some popular codes will be discussed in this chapter.

# 1.2 Number Systems

Let us review the decimal number system, the system with which we are most familiar. There are 10 symbols (0 through 9), called digits, in the system—along with a set of relations defining the operations of addition (+), subtraction (-), multiplication  $(\times)$ , and division (/). The total number of digits in a number system is called the *radix* or *base* of the system. The digits in the system range in value from 0 through r-1, where r is the radix. For the decimal system, r=10 and the digits range in value from 0 through (10-1)=9.

In the so-called *positional notation* of a number, the radix point separates the "integer" portion of the number from the "fraction" portion. If there is no fraction portion, the radix point is not explicitly shown in the positional notation. Furthermore, each position in the representation has a weight associated with it. The weight of each position is equivalent to the radix raised to a power. The power starts with a 0 at the position immediately

to the left of the radix point and increases by 1 as we move each position toward the left, and decreases by 1 as we move each position toward the right. A typical number in the decimal system is shown in the following example.

#### Example 1.1

This number can also be represented as a polynominal:

$$1 \times 10^{3} + 2 \times 10^{2} + 5 \times 10^{1} + 6 \times 10^{0} + 9 \times 10^{-1} + 3 \times 10^{-2} + 2 \times 10^{-3}$$

We can thus generalize these two representations to any number system. The general positional notation of a number N is

$$N = (a_n \cdots a_3 a_2 a_1 a_0 \cdot a_{-1} a_{-2} a_{-3} \cdots a_{-m})_r \tag{1.1}$$

where r is the radix of the number systems;  $a_{-1}$ ,  $a_0$ ,  $a_1$ ,  $a_2$ , and so on, are digits such that  $0 \le a_i \le (r-1)$  for all i;  $a_n$  is the most significant digit (MSD), and  $a_{-m}$  is the least significant digit (LSD). The polynomial representation of the above number is

$$N = \sum_{i=-m}^{n} a_i r^i \tag{1.2}$$

There are n + 1 integer digits and m fraction digits in the number shown above.

Consider an integer with n digits. A finite range of values can be represented by this integer. The smallest value in this range is 0 and corresponds to each digit of the n-digit integer being equal to 0. When each digit corresponds in value to r-1, the highest digit in the number system, the n-digit number attains the highest value in the range. This value is equal to  $r^n-1$ . Table 1.1 lists the first few numbers in various systems. We will discuss binary, octal, and hexadecimal systems next.

TABLE 1.1

Number Systems

| Decimal $(r = 10)$ | Binary $(r = 2)$ | Ternary $(r = 3)$ | Quaternary $(r = 4)$ | Octal $(r = 8)$ | Hexadecimal $(r = 16)$ |

|--------------------|------------------|-------------------|----------------------|-----------------|------------------------|

| 0                  | 0                | 0                 | 0                    | 0               | 0                      |

| 1                  | 1                | 1                 | 1                    | 1               | 1                      |

| 2                  | 10               | 2                 | 2                    | 2               | 2                      |

| 3                  | 11               | 10                | 3                    | 3               | 3                      |

| 4                  | 100              | 11                | 10                   | 4               | 4                      |

| 5                  | 101              | 12                | 11                   | 5               | 5                      |

| 6                  | 110              | 20                | 12                   | 6               | 6                      |

| 7                  | 111              | 21                | 13                   | 7               | 7                      |

| 8                  | 1000             | 22                | 20                   | 10              | 8                      |

| 9                  | 1001             | 100               | 21                   | 11              | 9                      |

| 10                 | 1010             | 101               | 22                   | 12              | Α                      |

| 11                 | 1011             | 102               | 23                   | 13              | В                      |

| 12                 | 1100             | 110               | 30                   | 14              | C                      |

| 13                 | 1101             | 111               | 31                   | 15              | D                      |

| 14                 | 1110             | 112               | 32                   | 16              | E                      |

| 15                 | 1111             | 120               | 33                   | 17              | F                      |

| 16                 | 10000            | 121               | 100                  | 20              | 10                     |

| 17                 | 10001            | 122               | 101                  | 21              | 11                     |

| 18                 | 10010            | 200               | 102                  | 22              | 12                     |

| 19                 | 10011            | 201               | 103                  | 23              | 13                     |

| 20                 | 10100            | 202               | 110                  | 24              | 14                     |

# 1.2.1 Binary System

In this system, the radix is 2 and the two allowed digits are 0 and 1. BInary digiT is abbreviated as BIT. A typical binary number is shown in the positional notation in the following example.

### Example 1.2

$$N = (11010.1101)_{2}$$

$$2^{4}2^{3}2^{2}2^{1}2^{0}.2^{-1}2^{-2}2^{-3}2^{-4} \text{ weights}$$

$$16.8.4.2.1.\frac{1}{2}.\frac{1}{4}.\frac{1}{8}.\frac{1}{16} \text{ weights in decimal}$$

Weights double for each move to the left from the binary point.

Weights are halved for each move to the right from the binary point.

In polynomial form, this number is

$$N = 1 \times 2^{4} + 1 \times 2^{3} + 0 \times 2^{2} + 1 \times 2^{1} + 0 \times 2^{0}$$

$$+ 1 \times 2^{-1} + 1 \times 2^{-2} + 0 \times 2^{-3} + 1 \times 2^{-4}$$

$$= 16 + 8 + 0 + 2 + 0 + \frac{1}{2} + \frac{1}{4} + 0 + \frac{1}{16} \text{ (decimal)}$$

$$= 26 + \frac{1}{2} + \frac{1}{4} + \frac{1}{16} \text{ (decimal)}$$

$$= (26\frac{13}{16})_{10}$$

As we can see from the polynomial expansion and summation shown here, the positions containing a 0 do not contribute to the sum. To convert a binary number into decimal, we can simply accumulate the weights corresponding to each nonzero bit of the number.

Each bit can take either of the two values: 0 or 1. With two bits, we can derive  $2^2$ , or 4, combinations: 00, 01, 10, and 11. The decimal values of these combinations (binary numbers) are 0, 1, 2, and 3, respectively. Similarly, with three bits we can derive  $2^3$ , or 8, combinations ranging in value form 000 (0 in decimal) to 111 (7 in decimal). In general, with n bits it is possible to generate  $2^n$  combinations of 0s and 1s, and these combinations when viewed as binary numbers range in value from 0 to  $(2^n - 1)$ . Table 1.2 shows some binary numbers for various values of n. The  $2^n$  combinations possible for any n are obtained by starting with n 0s and counting in binary until the number with n 1s is reached. A more mechanical method of generating these combinations is described herein.

The first combination has n 0s and the last has n 1s. As we can see from Table 1.2, the value of the least significant bit (LSB)—i.e., bit position 0—alternates in value between 0 and 1 every row, as we move from row to row. Similarly, the value of the bit in position 1 alternates every two rows (i.e., two 0s followed by two 1s). In general, the value of the bit in position i alternates ever  $2^i$  rows starting from 0s. This observation can be utilized in generating all the  $2^n$  combinations.

# 1.2.2 Octal System

In this system, r = 8, and the allowed digits are 0, 1, 2, 3, 4, 5, 6, and 7. A typical number is shown in positional notation in the following example.

TABLE 1.2 Binary Numbers

| n = 2 | n = 3 | n = 4                                                    |

|-------|-------|----------------------------------------------------------|

|       |       |                                                          |

| 1 0   | 2 1 0 | $\boxed{3} \boxed{2} \boxed{1} \boxed{0} \leftarrow Bit$ |

| 00    | 000   | 0000 position                                            |

| 01    | 001   | 0001                                                     |

| 10    | 010   | 0010                                                     |

| 11    | 011   | 0011                                                     |

|       | 100   | 0100                                                     |

|       | 101   | 0101                                                     |

|       | 110   | 0110                                                     |

|       | 111   | 0111                                                     |

|       |       | 1000                                                     |

|       |       | 1001                                                     |

|       |       | 1010                                                     |

|       |       | 1011                                                     |

|       |       | 1100                                                     |

|       |       | 1101                                                     |

|       |       | 1110                                                     |

|       |       | 1111                                                     |

|       |       |                                                          |

### Example 1.3

$$N = (4 \ 5 \ 2 \ 6 \ .2 \ 3)_{8}$$

$$8^{3}8^{2}8^{1}8^{0}.8^{-1}8^{-2} \text{ weights}$$

$$= 4 \times 8^{3} + 5 \times 8^{2} + 2 \times 8^{1} + 6 \times 8^{0} + 2 \times 8^{-1}$$

$$+ 3 \times 8^{-2} \text{ polynomial form}$$

$$= 2048 + 320 + 16 + 6 + \frac{2}{8} + \frac{3}{64} \text{ (decimal)}$$

$$= (2390\frac{19}{64})_{10}$$

# 1.2.3 Hexadecimal System

In this system, r = 16, and the allowed digits are 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, and F. Digits A through F correspond to decimal values 10 through 15, respectively. A typical number is shown in the following example.

#### Example 1.4

$$N = (A \ 1 \ F \ . \ 1 \ C)_{16}$$

$$16^{2}16^{1}16^{0}.16^{-1}16^{-2} \text{ weights}$$

$$= A \times 16^{2} + 1 \times 16^{1} + F \times 16^{0} + 1 \times 16^{-1}$$

$$+ C \times 16^{-2} \text{ polynomial form}$$

$$= 10 \times 16^{2} + 1 \times 16^{1} + 15 \times 16^{0} + 1 \times 16^{-1}$$

$$+ 12 \times 16^{-2} \text{ (decimal)}$$

$$= (2591\frac{28}{256})_{10}$$

### 1.3 Conversion

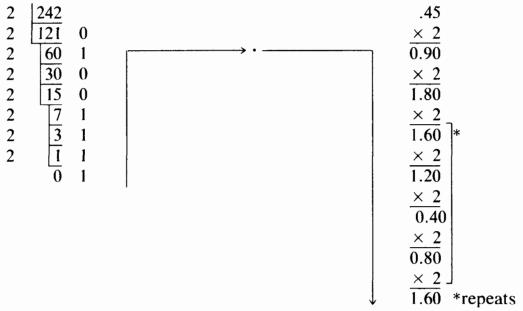

To convert numbers from a nondecimal system to decimal, we simply expand the given number as a polynomial and evaluate the polynomial using decimal arithmetic, as shown in Examples 1.1 through 1.4. When a decimal number is converted to any other system, the integer and fraction portions of the number are handled separately. The *radix divide technique* is used to convert the integer portion, and the *radix multiply technique* is used for the fraction portion.

### 1.3.1 Radix Divide Technique

- (i) Divide the given integer successively by the required radix, noting the remainder at each step. The quotient at each step becomes the new dividend for subsequent division. Stop the division process when the quotient becomes zero.

- (ii) Collect the remainders from each step (last to first) and place them left to right to form the required number.

The following examples illustrate the procedure.

### Example 1.5

$$(245)_{10} = (?)_2$$

(i.e., convert  $(245)_{10}$  to binary)

Here, 245 is first divided by 2, generating a quotient of 122 and a remainder of 1. Next 122 is divided, generating 61 as the quotient and 0 as the remainder. The division process is continued until the quotient is 0, with the remainders noted at each step. The remainder bits form each step (last to first) are then placed left to right to form the number in base 2.

To verify the validity of the radix divide technique, consider the polynomial representation of a four-bit integer  $A = (a_4 a_3 a_2 a_1)$ :

$$A = \sum_{i=1}^4 a_i \cdot r^i$$

This can be rewritten as

$$A = 2(2(2(a_3) + a_2) + a_1) + a_0$$

From this form, it can be seen that the bits of the binary number correspond to the remainder at each divide-by-two operation. Some examples follows.

#### Example 1.6

$$(245)_{10} = (?)_{8}$$

$$\begin{array}{ccc}

8 & 245 \\

8 & 30 & 5 \\

\hline

8 & 3 & 6 \\

\hline

0 & 3 & = (365)_{8}

\end{array}$$

#### Example 1.7

$$(245)_{10} = (?)_{16}$$

$$16 \quad 245$$

$$16 \quad 15 \quad 5 = 5 \quad = (F5)_{16}$$

$$0 \quad 15 = F \quad = (F5)_{16}$$

# 1.3.2 Radix Multiply Technique

As we move each position to the right of the radix point, the weight corresponding to each bit in the binary fraction is halved. The radix multiply technique uses this fact and multiplies the given decimal number by 2 (i.e., divides the given number by half) to obtain each fraction bit. The technique consists of the following steps:

(i) Successively multiply the given fraction by the required base, noting the integer portion of the product at each step. Use the fractional part of the product as the multiplicand for subsequent steps. Stop when the fraction either reaches 0 or recurs.

(ii) Collect the integer digits at each step from first to last and arrange them left to right.

If the radix multiplication process does not converge to 0, it is not possible to represent a decimal fraction in binary exactly. Accuracy, then, depends on the number of bits used to represent the fraction. Some examples follow.

#### Example 1.8

$$(.250)_{10} = (?)_{2}$$

$$.25$$

$$\times \frac{2}{0.50}$$

$$\times \frac{2}{1.00} = (.01)_{2}$$

#### Example 1.9

$$(.345)_{10} = (?)_{2}$$

$$.345$$

$$\frac{\times 2}{0.690}$$

$$\frac{\times 2}{1.380}$$

$$\frac{\times 2}{0.760}$$

Multiply fractions only

$$\frac{\times 2}{1.520}$$

$$\frac{\times 2}{1.040}$$

$$\frac{\times 2}{0.080} = (.010110)_{2}$$

The fraction may never reach 0; stop when the required number of fraction digits is obtained; the fraction will not be accurate.

#### Example 1.10

$$(.345)_{10} = (?)_{8}$$

$$.345$$

$$\times 8$$

$$\overline{2.760}$$

$$\times 8$$

$$\overline{6.080}$$

$$\times 8$$

$$\overline{0.640}$$

$$\times 8$$

$$\overline{5.120} = (.2605)_{8}$$

#### Example 1.11

$$(242.45)_{10} = (?)_2$$

$$= (1111\ 0010\ .\ 01\ \overline{11\ 00})_2$$

The radix divide and multiply algorithms are applicable to the conversion of numbers from any base to any other base. When a number is converted from base p to base q, the number in base p is divided (or multiplied) by q in base p arithmetic. Because of our familiarity with decimal arithmetic, these methods are convenient when p equals 10. In general, it is easier to convert a base p number to base q ( $p \neq 10$ ,  $q \neq 10$ ) by first converting the number to decimal from base p and then converting that decimal number to base q (i.e.,  $(N)_p \rightarrow (?)_{10} \rightarrow (?)_q$ ), as shown by the following example.

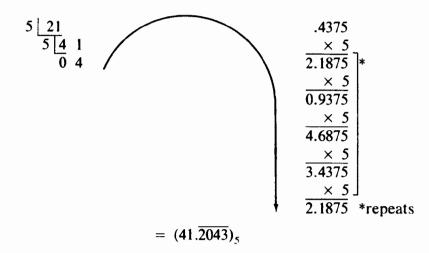

#### Example 1.12

$$(25.34)_8 = (?)_5$$

Convert to base 10:

$$(25.34)_8 = 2 \times 8^1 + 5 \times 8^0 + 3 \times 8^{-1} + 4 \times 8^{-2} \text{ decimal}$$

$$= 16 + 5 + \frac{3}{8} + \frac{4}{64} \text{ decimal}$$

$$= (21\frac{28}{64})_{10}$$

$$= (21.4375)_{10}$$

Convert to base 5:

# 1.3.3 Base 2<sup>k</sup> Conversion

Each of the eight octal digits can be represented by a three-bit binary number. Similarly, each of the 16 hexadecimal digits can be represented by a four-bit binary number. In general, each digit of the base p number system, where p is an integral power k of 2, can be represented by a k-bit binary number.

In converting a base p number to base q, if p and q are both integral powers of 2, the base p number can first be converted to binary, and this can in turn be converted to base q by inspection. This conversion procedure is called the base  $2^k$  conversion.

#### Example 1.13

$$(4\ 2\ A\ 5\ 6\ .\ F\ 1)_{16} = (?)_8$$

$p = 16 = 2^4, \qquad q = 8 = 2^3$

Therefore,

$$k_{1} = 4, \quad k_{2} = 3$$

Start

$$k_{1} = 4$$

Zero  $\rightarrow 0$  0100 0010 1010 0101 0110 . 1111 0001  $\bigcirc 0$   $\leftarrow$  Zero included

$$k_{2} = 3$$

$$= (1025126.742)_{8}$$

#### Example 1.14

$$(AF5.2C)_{16} = (?)_4$$

A F 5 . 2 C base  $16 = 2^4$   $k_1 = 4$

$1010 \ 1111 \ 0101.0010 \ 1100$  base  $4 = 2^2$  :  $k_2 = 2$

$= (223311.0230)_4$

#### Example 1.15

$$(567.23)_8 = (?)_{16}$$

Zeros included

$$000101110111.01001100$$

base 8  $\therefore k_1 = 3$

$$1 \quad 7 \quad 7 \quad . \quad 4 \quad C \quad \text{base } 16 \quad \therefore k_2 = 4$$

$$= (177.4C)_{16}$$

It is thus possible to represent binary numbers in a very compact form by using octal and hexadecimal systems. The conversion between these systems is also straightforward. Because it is easier to work with fewer digits than with a large number of bits, digital system users prefer to work with octal or hexadecimal systems when understanding or verifying the results

produced by the system or communicating data between users or between users and the machine.

#### 1.4 Arithmetic

Arithmetic in all other number systems follows the same general rules as in decimal. Binary arithmetic is simpler than decimal arithmetic since only two digits (0 and 1) are involved. Arithmetic in octal and hexadecimal systems requires some practice because of the general unfamiliarity with those systems. In this section, we will describe binary arithmetic in detail, followed by a brief discussion of octal and hexadecimal arithmetic. For simplicity, integers will be used in all the examples in this section. Nontheless, the procedures are valid for fractions and numbers with both integer and fraction portions.

In the so-called *fixed-point representation* of binary numbers in digital systems, the radix point is assumed to be either at the right end or the left end of the field in which the number is represented. In the first case the number is an integer, and in the second it is a fraction. Fixed-point representation is the most common type of representation. In scientific computing applications, in which a large range of numbers must be represented, *floating-point representation* is used. Floating-point representation of numbers will be discussed in Section 1.6.

# 1.4.1 Binary Arithmetic

Table 1.3 illustrates the rules for binary addition, subtraction, and multiplication.

TABLE 1.3

Binary Arithmetic

| (a) | (a) Addition     |            |    | (b)      | Subtract | (c) Multiplication |       |         |   |            |   |   |

|-----|------------------|------------|----|----------|----------|--------------------|-------|---------|---|------------|---|---|

|     |                  |            | .  | A        |          |                    | l A   | 4       |   |            | . | A |

|     | $\boldsymbol{A}$ | + <b>B</b> | j  |          |          | A - B              | 1     |         | Α | $\times B$ | 1 |   |

|     |                  |            | 0  | 1        |          |                    | 0     | 1       |   |            | 0 | 1 |

|     |                  | 0          | 0  | 1        |          | 0                  | 0     | 1       | _ | 0          | 0 | 0 |

|     | B                |            |    |          |          | В                  |       |         | В | }          |   |   |

|     |                  | 1          | 1  | 10       |          | 1                  | 11    | 0       | _ | 1          | 0 | 1 |

|     |                  |            | Ca | urry Sur | n        | Borrov             | w Dif | ference |   |            |   |   |

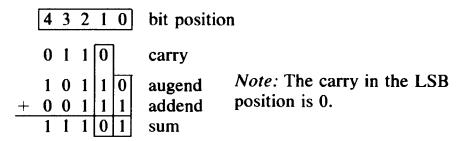

**Addition** In Table 1.3(a), note that 0 + 0 = 0, 0 + 1 = 1, 1 + 0 = 1, and 1 + 1 = 10. Thus, the addition of two 1s results in a SUM of 0 and a CARRY of 1.

When two binary numbers are added, the carry from any position is included in the addition of bits in the next most significant position, as in decimal arithmetic. Example 1.16 illustrates this.

#### Example 1.16

Here, bits in the LSB position (i.e., position 0) are first added, resulting in a sum bit of 1 and a carry of 0. The carry is included in the addition of bits at position 1. The three bits in position 1 are added using two steps (0 + 1 = 1, 1 + 1 = 10), resulting in a sum bit of 0 and a carry bit of 1 to the next most significant position (position 2). This process is continued through the most significant bit (MSB).

In general, the addition of two n-bit numbers results in a number that is n + 1 bits long. If the number representation is to be confined to n bits, the operands of the addition should be kept small enough so that their sum does not exceed n bits.

**Subtraction** From Table 1.3(b), we can see that 0 - 0 = 0, 1 - 0 = 1, 1 - 1 = 0, and 0 - 1 = 1 with a BORROW of 1. That is, subtracting a 1 from a 0 results in a 1 with a borrow from the next most significant position, as in decimal arithmetic. Subtraction of two binary numbers is performed stage by stage as in decimal arithmetic, starting from the LSB to the MSB. Some examples follow.

Example 1.17

|   | 5 | 4 | 3      | 2 | 1 | 0 | bit position |

|---|---|---|--------|---|---|---|--------------|

|   | 0 |   |        | 0 | r |   | •            |

|   | 1 | 0 | 1<br>1 | 1 | 0 | 1 | minuend      |

| _ | 0 | 1 | 1      | 0 | 1 | 0 | subtrahend   |

|   | 0 | 1 | 0      | 0 | 1 | 1 | difference   |

Bit position 1 requires a borrow from bit position 2. Because of this borrow, minuend bit 2 is a 0. The subtraction continues through the MSB.

#### Example 1.18

Bit 2 requires a borrow from bit 3; after this borrow, minuend bit 3 is 0. Then, bit 3 requires a borrow. Because bits 4 and 5 of the minuend are zeros, borrowing is from bit 6. In this process, the intermediate minuend bits 4 and 5 each attain a value of 1 (compare this with the decimal subtraction). The subtraction continues through the MSB.

**Multiplication** Binary multiplication is similar to decimal multiplication. From Table 1.3(c), we can see that  $0 \times 0 = 0$ ,  $0 \times 1 = 0$ ,  $1 \times 0 = 0$ , and  $1 \times 1 = 1$ . An example follows.

#### Example 1.19

In general, the product of two *n*-bit numbers is 2n bits long. In Example 1.19, there are two nonzero bits in the multiplier, one in position 2 corresponding to  $2^2$  and the other in position 3 corresponding to  $2^3$ . These two bits yield partial products whose values are simply that of the multiplicand shifted left two and three bits, respectively. The 0 bits in the multiplier contribute partial products with 0 values. Thus, the following shift-and-add algorithm can be adopted to multiply two *n*-bit number *A* and *B*, where  $B = (b_{n-1}, b_{n-2}, \cdots, b_1, b_0)$ .

- 1. Start with a 2n-bit product with a value of 0.

- 2. For each  $b_i$   $(0 \le i \le n 1) \ne 0$  shift A i positions to the left and add to the product.

This procedure reduces the multiplication to repeated shift and addition of the multiplicand.

**Division** The longhand (trial-and-error) procedure of decimal division can also be used in binary, as shown in Example 1.20.

#### Example 1.20

$$110101 \div 111 = ?$$

|     | 0111                | Quotient     |           |                 |

|-----|---------------------|--------------|-----------|-----------------|

|     |                     | $X \qquad Y$ |           |                 |

| 111 | 110,101             | 110 < 111    | $q_1 = 0$ | do not subtract |

|     | $\frac{-111}{1101}$ | 1101 > 111   | $q_2 = 1$ | subtract        |

|     | $\frac{-111}{1100}$ | 1100 > 111   | $a_2 = 1$ | subtract        |

|     | <u>– 111</u>        |              | -5        |                 |

|     | 1011<br>-111        | 1011 > 111   | $q_4 = 1$ | subtract        |

|     | 100                 | remainder    |           |                 |

In this procedure, the divisor is compared with the dividend at each step. If the divisor is greater than the dividend, the corresponding quotient bit is 0; otherwise, the quotient bit is 1, and the divisor is subtracted from the dividend. The compare-and-subtract process is continued until the LSB of the dividend. The procedure is formalized in the following steps.

- 1. Align the divisor (Y) with the most significant end of the dividend. Let the portion of the dividend from its MSB to its bit aligned with the LSB of the divisor be denoted X. We will assume that there are n bits in the divisor and 2n bits in the dividend. Let i = 0.

- 2. Compare X and Y. If  $X \ge Y$ , the quotient bit is 1: perform X Y. If X < Y, the quotient bit is 0.

- 3. Set i = i + 1. If  $i \ge n$ , stop. Otherwise, shift Y one bit to the right and go to step 2.

For the purposes of illustration, this procedure assumed the division of integers. If the divisor is greater than the dividend, the quotient is 0, and if the divisor is 0, the procedure should be stopped since dividing by 0 results in an error.

As we can see from these examples, multiplication and division operations can be reduced to repeated shift and addition (or subtraction). If the hardware can perform shift, add, and subtract operations, it can be programmed to perform multiplication and division as well. Older digital systems used such measures to reduce hardware costs. With the advances in digital hardware technology, it is now possible to implement these and more complex operations in an economical manner. (See the references at the end of this chapter for books that describe procedures for multiplication and division that are more elegant than the ones described here.)

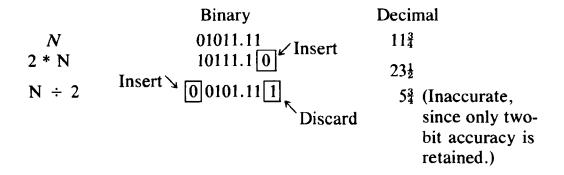

**Shifting** Generally, shifting a base r number left by one position (and inserting a 0 into the vacant LSD position) is equivalent to multiplying the number by r. Shifting the number right by one position (inserting a 0 into the vacant MSD position) generally is equivalent to dividing the number by r.

In binary system, each left shift multiplies the number by 2, and each right shift divides the number by 2, as shown in Example 1.21.

#### Example 1.21

If the MSB of an *n*-bit number is not 0, shifting it left would result in a number larger than the magnitude that can be accommodated in *n* bits—and the 1 shifted out of the MSB position cannot be discarded. If nonzero bits shifted out of the LSB position during a right shift are discarded, the accuracy is lost. Later in this chapter, we will discuss shifting in further detail.

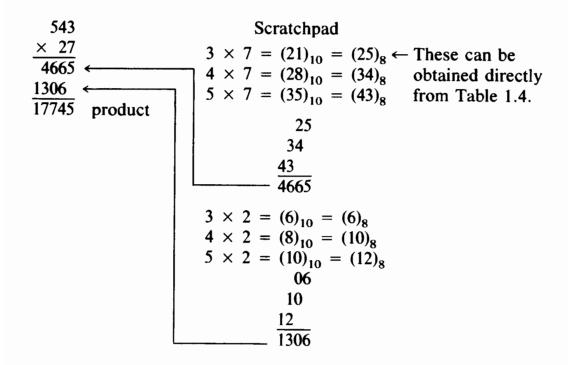

## 1.4.2 Octal Arithmetic

Table 1.4 shows the octal addition and multiplication tables. The examples that follow illustrate the four arithmetic operations in octal and their similarity to decimal arithmetic. (Table 1.4 can be used to look up the result at each stage in the arithmetic.) An alternate method is used in the following examples. The operation is first performed in decimal and then the result is converted into octal, before proceeding to the next stage, as shown in the scratchpad.

TABLE 1.4

Octal Arithmetic

| (a)              | Addition   | n      |    |    |    |    |    |    |    |

|------------------|------------|--------|----|----|----|----|----|----|----|

|                  |            |        |    |    |    | A  |    |    |    |

| $\boldsymbol{A}$ | + <i>B</i> | 0      | 1  | 2  | 3  | 4  | 5  | 6  | 7  |

|                  | 0          | 0      | 1  | 2  | 3  | 4  | 5  | 6  | 7  |

|                  | 1          | 1      | 2  | 3  | 4  | 5  | 6  | 7  | 10 |

|                  | 2          | 2      | 3  | 4  | 5  | 6  | 7  | 10 | 11 |

| D                | 3          | 3      | 4  | 5  | 6  | 7  | 10 | 11 | 12 |

| В                | 4          | 4      | 5  | 6  | 7  | 10 | 11 | 12 | 13 |

|                  | 5          | 5      | 6  | 7  | 10 | 11 | 12 | 13 | 14 |

|                  | 6          | 6      | 7  | 10 | 11 | 12 | 13 | 14 | 15 |

|                  | 7          | 7      | 10 | 11 | 12 | 13 | 14 | 15 | 16 |

| (b)              | Multipli   | cation |    |    |    |    |    |    |    |

|                  |            |        |    |    |    | A  |    |    |    |

| $\boldsymbol{A}$ | $\times$ B | 0      | 1  | 2  | 3  | 4  | 5  | 6  | 7  |

|                  | 0          | 0      | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

|                  | 1          | 0      | 1  | 2  | 3  | 4  | 5  | 6  | 7  |

|                  | 2          | 0      | 2  | 4  | 6  | 10 | 12 | 14 | 16 |

| n                | 3          | 0      | 3  | 6  | 11 | 14 | 17 | 22 | 25 |

| В                | 4          | 0      | 4  | 10 | 14 | 20 | 24 | 30 | 34 |

|                  | 5          | 0      | 5  | 12 | 17 | 24 | 31 | 36 | 43 |

|                  | 6          | 0      | 6  | 14 | 22 | 30 | 36 | 44 | 52 |

|                  | 7          | 0      | 7  | 16 | 25 | 34 | 43 | 52 | 61 |

### **Example 1.22: Addition**

## **Example 1.23: Subtraction**

### **Example 1.24: Subtraction**

$$\begin{array}{r}

377 \\

540045 \\

-325654 \\

\hline

212171

\end{array}$$

The intermediate 0s become r-1 or 7 when borrowed.

**Example 1.25: Multiplication**

#### **Example 1.26: Division**

Use the multiplication table in Table 1.4 to derive the quotient digit (by trial and error).

#### 1.4.3 Hexadecimal Arithmetic

Table 1.5 shows the addition and multiplication tables. The following examples illustrate hexadecimal arithmetic.

TABLE 1.5

Hexadecimal Arithmetic

| (a) A | ddition |    |    |    |    |    |    |    |    |    |    |              |            |              |            |            |

|-------|---------|----|----|----|----|----|----|----|----|----|----|--------------|------------|--------------|------------|------------|

| +     | 0       | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | Α  | В            | C          | D            | E          | F          |

| 0     | 0       | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | Α  | В            | С          | D            | Е          | F          |

| 1     | 1       | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | Α  | В  | C            | D          | $\mathbf{E}$ | F          | 10         |

| 2     | 2       | 3  | 4  | 5  | 6  | 7  | 8  | 9  | Α  | В  | C  | D            | E          | F            | 10         | 11         |

| 3     | 3       | 4  | 5  | 6  | 7  | 8  | 9  | Α  | В  | C  | D  | $\mathbf{E}$ | F          | 10           | 11         | 12         |

| 4     | 4       | 5  | 6  | 7  | 8  | 9  | Α  | В  | C  | D  | E  | F            | 10         | 11           | 12         | 13         |

| 5     | 5       | 6  | 7  | 8  | 9  | Α  | В  | C  | D  | E  | F  | 10           | 11         | 12           | 13         | 14         |

| 6     | 6       | 7  | 8  | 9  | Α  | В  | C  | D  | E  | F  | 10 | 11           | 12         | 13           | 14         | 15         |

| 7     | 7       | 8  | 9  | Α  | В  | C  | D  | E  | F  | 10 | 11 | 12           | 13         | 14           | 15         | 16         |

| 8     | 8       | 9  | Α  | В  | C  | D  | E  | F  | 10 | 11 | 12 | 13           | 14         | 15           | 16         | 17         |

| 9     | 9       | Α  | В  | C  | D  | E  | F  | 10 | 11 | 12 | 13 | 14           | 15         | 16           | 17         | 18         |

| Α     | Α       | В  | C  | D  | E  | F  | 10 | 11 | 12 | 13 | 14 | 15           | 16         | 17           | 18         | 19         |

| В     | В       | C  | D  | E  | F  | 10 | 11 | 12 | 13 | 14 | 15 | 16           | 17         | 18           | 19         | 1 <b>A</b> |

| C     | С       | D  | E  | F  | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17           | 18         | 19           | 1 <b>A</b> | 1B         |

| D     | D       | E  | F  | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18           | 19         | 1 <b>A</b>   | 1B         | 1C         |

| E     | E       | F  | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19           | 1 <b>A</b> | 1 <b>B</b>   | 1C         | 1D         |

| F     | F       | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 1A           | 1B         | 1C           | 1D         | 1E         |

| (b) M | Iultiplic | ation |              |            |    |            |            |    |    |            |            |            |            |            |              |            |

|-------|-----------|-------|--------------|------------|----|------------|------------|----|----|------------|------------|------------|------------|------------|--------------|------------|

| ×     | 0         | 1     | 2            | 3          | 4  | 5          | 6          | 7  | 8  | 9          | Α          | В          | C          | D          | Е            | F          |

| 0     | 0         | 0     | 0            | 0          | 0  | 0          | 0          | 0  | 0  | 0          | 0          | 0          | 0          | 0          | 0            | 0          |

| 1     | 0         | 1     | 2            | 3          | 4  | 5          | 6          | 7  | 8  | 9          | Α          | В          | C          | D          | $\mathbf{E}$ | F          |

| 2     | 0         | 2     | 4            | 6          | 8  | Α          | C          | E  | 10 | 12         | 14         | 16         | 18         | 1 <b>A</b> | 1C           | 1E         |

| 3     | 0         | 3     | 6            | 9          | C  | F          | 12         | 15 | 18 | 1 <b>B</b> | 1E         | 21         | 24         | 27         | 2A           | 2D         |

| 4     | 0         | 4     | 8            | C          | 10 | 14         | 18         | 1C | 20 | 24         | 28         | 2C         | 30         | 34         | 38           | 3C         |

| 5     | 0         | 5     | Α            | F          | 14 | 19         | 1E         | 23 | 28 | 2D         | 32         | 37         | 3C         | 41         | 46           | 4 <b>B</b> |

| 6     | 0         | 6     | C            | 12         | 18 | 1E         | 24         | 2A | 30 | 36         | 3C         | 42         | 48         | 4 <b>E</b> | 54           | 5 <b>A</b> |

| 7     | 0         | 7     | $\mathbf{E}$ | 15         | 1C | 23         | 2A         | 31 | 38 | 3F         | 46         | 4D         | 54         | 5B         | 62           | 69         |

| 8     | 0         | 8     | 10           | 18         | 20 | 28         | 30         | 38 | 40 | 48         | 50         | 58         | 60         | 68         | 70           | 78         |

| 9     | 0         | 9     | 12           | 1B         | 24 | 2D         | 36         | 3F | 48 | 51         | 5 <b>A</b> | 63         | 6C         | 75         | 7E           | 87         |

| Α     | 0         | Α     | 14           | 1 <b>E</b> | 28 | 32         | 3C         | 46 | 50 | 5 <b>A</b> | 64         | 6E         | 78         | 82         | 8C           | 96         |

| В     | 0         | В     | 16           | 21         | 2C | 37         | 42         | 4D | 58 | 63         | 6E         | 79         | 84         | 8F         | 9 <b>A</b>   | A5         |

| C     | 0         | C     | 18           | 24         | 30 | 3C         | 48         | 54 | 60 | 6C         | 78         | 84         | 90         | 9C         | <b>A</b> 8   | <b>B</b> 4 |

| D     | 0         | D     | 1 <b>A</b>   | 27         | 34 | 41         | 4E         | 5B | 68 | 75         | 82         | 8F         | 9C         | <b>A9</b>  | <b>B</b> 6   | C3         |

| E     | 0         | E     | 1C           | 2A         | 38 | 46         | 54         | 62 | 70 | 7E         | 8C         | 9 <b>A</b> | A8         | <b>B</b> 6 | C4           | D2         |

| F     | 0         | F     | 1 <b>E</b>   | 2D         | 3C | 4 <b>B</b> | 5 <b>A</b> | 69 | 78 | 87         | 96         | <b>A</b> 5 | <b>B</b> 4 | C3         | D2           | <b>E</b> 1 |

### **Example 1.27: Addition**

Scratchpad

1 5 F C

Decimal

$$+245D$$

$= 12$

$= 16$

$= 15$

$= 13$

$= 16$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

$= 15$

#### Decimal

$$1 = 1

F = 15

5 = 5

21 = (15)16$$

#### **Example 1.28: Subtraction**

Scratchpad

3

Decimal

2 4 5 D minuend

-1 5 F C subtrahend

$$0 E 6 1$$

difference

$$(15)_{16} = 21$$

$$-(F)_{16} = -15 = (6)_{16}$$

$$(13)_{16} = 19$$

$$-(5)16 = -5$$

$$14 = (E)_{16}$$

## **Example 1.29: Multiplication**

**Example 1.30: Division**

$$\begin{array}{c}

1 \text{ A F 3} \div \text{ E} \\

0 1 \text{ EC} & \longleftarrow \text{ Quotient} \\

\hline

1 \text{ A F 3} \\

0 \\

1 \text{ A F 3} \\

\hline

E \\

\hline

C \text{ F 3} \\

\hline

C \text{ 4} \\

\hline

B \text{ 3} \\

\hline

A 8 \\

\hline

\end{array}$$

Remainder

# 1.5 Representation of Negative Numbers

The examples shown so far have used only positive numbers. In practice, a digital system must represent both positive and negative numbers. To accommodate the sign of the number, an additional digit, called the sign digit, is included in the representation, along with the magnitude digits. Thus, to represent an n-digit number, we would need n+1 digits. Typically, the sign digit is the MSD. Two popular representation schemes have been used: the sign-magnitude system and the complement system.

# 1.5.1 Sign-Magnitude System

In this representation, n + 1 digits are used to represent a number, where the MSD is the sign digit and the remaining n digits are magnitude digits. The value of the sign digit is 0 for positive numbers and r - 1 for negative numbers, where r is the radix of the number system. Some sample representations follow.

#### Example 1.31

Here, we assume that five digits are available to represent each number. The sign and magnitude portions of the number are separated by "," for illusion purposes only. The "," is not used in the actual representation.

| Number       | Representation |                          |

|--------------|----------------|--------------------------|

| $(-2)_{2}$   | 1,0010         | All numbers are shown as |

| $(+56)_{8}$  | 0,0056         | five-digit numbers.      |

| $(-56)_{8}$  | 7,0056         |                          |

| $(+1F)_{16}$ | 0,001F         |                          |

| $(-1F)_{16}$ | F,001F         |                          |

|              | 1 -            |                          |

|              | Sign Magnitude |                          |

The sign and magnitude portions are handled separately in arithmetic using sign-magnitude numbers. The magnitude of the result is computed and then the appropriate sign is attached to the result, just as in decimal arithmetic. The sign-magnitude system has been used in such small digital systems as digital meters and typically when the decimal mode of arithmetic is used in digital computers. The decimal (or binary coded decimal) arithmetic mode will be described later in this chapter. Complement number representation is the most prevalent representation mode in modern-day computer systems.

### 1.5.2 Complement Number System

Consider the subtraction of a number A from a number B. This is equivalent to adding (-A) to B. The complement number system provides a convenient way of representing negative numbers (i.e., complements of positive numbers), thus reducing the subtraction to an addition. Because multiplication and division correspond respectively to repeated addition and subtraction, it is possible to perform the four basic arithmetic operations using only the hardware for addition when the negative numbers are represented in complement form. The two popular complement number systems are radix complement and diminished radix complement.

The radix complement of a number (N), is defined as

$$[N]_r = r^n - (N)_r$$

if  $(N)_r \neq 0$

= 0 if  $(N)_r = 0$  (1.3)

where [N], is the radix complement and n is the number of digits in the integer portion of the number  $(N)_r$ .

This system is commonly called either twos complement or tens complement, depending on which number system is used. This section will describe the twos complement system. Because the tens complement system displays the same characteristics as the twos complement system, it will not be discussed here.

#### Example 1.32

(a) The twos complement of  $(01010)_2$  is

$$2^5 - (01010) = 100000 - 01010 = 10110$$

Here n = 5 and r = 2.

(b) The twos complement of  $(0.0010)_2$  is

$$2^{1} - (0.0010) = 10.0000 - 0.0010 = 1.1110$$

Here, n = 1 and r = 2.

(c) The tens complement of  $(4887)_{10}$  is

$$10^4 - 4887 = 5113$$

Here, n = 4 and r = 10.

(d) The tens complement of  $(48.87)_{10}$  is

$$10^2 - 48.87 = 51.13$$

Here, n = 2 and r = 10.

As can be verified by Example 1.32, there are two other methods for obtaining the radix complement of a number.

#### METHOD 1

$[01010]_2 = ?$

10101

a. Complement each bit (i.e., change each 0 to 1 and 1 to 0).

+ 1  $\overline{10110}$

b. Add 1 to the LSB to get the twos complement.

#### METHOD 2

$$[010]_{10}_{2} = ?$$

101

101;10

- a. Copy the bits from the LSB until and including the first nonzero bit.

- b. Complement the remaining bits through the MSB to get the twos complement.

The diminished radix complement  $[N]_{r-1}$  of a number  $(N)_r$  is defined as:

$$[N]_{r-1} = r^n - r^{-m} - (N)_r (1.4)$$

where n and m are respectively the number of digits in integer and fraction portion of the number. Note that

$$[N]_r = [N]_{r-1} + r^{-m} (1.5)$$

That is, the radix complement of a number is obtained by adding a 1 to the LSB of the diminished radix complement form of the number.

The diminished radix complement is commonly called the *ones com*plement or nines complement, depending on which number system is used.

#### Example 1.33

(a)

$$(N)_r$$

$r$   $n$   $m$   $[N]_{r-1}$

$= 1001 2 4 0 2^4 - 2^0 - 1001$

$= 1000 - 1 - 1001$

$= 1111 - 1001 = 0110$

(b)  $100.1 2 3 1 = 2^3 - 2^{-1} - 100.1$

$= 1000 - 0.1 = 100.1$

$= 111.1 - 100.1 = 011.0$

(c)  $486.7 10 3 1 = 10^3 - 10^{-1} - 486.7$

$= 1000 - 0.1 - 486.7$

$= 999.9 - 486.7 = 513.2$

From Example 1.33 it can be seen that the ones complement of a number is obtained by subtracting each digit from the largest digit in the number system. In the binary system, this is equivalent to complementing (i.e., changing 1 to 0 and 0 to 1) each bit of the given number.

#### Example 1.34

$$N = 10110.110$$

Ones complement of  $N = 11111.111$

$$-10110.110$$

$$01001.001$$

which can also be obtained by complementing each bit of N.

As in sign-magnitude representation, a sign bit is included in the representation of numbers in complement systems as well. Because the complement of a number corresponds to its negative, positive numbers that are represented in complement systems remain in the same form as in the sign-

magnitude system. Only negative numbers are represented in the complement form as shown by the following example.

#### Example 1.35

Here we assume that five bits are available for representation and that the MSB is the sign bit.

| Decimal | Sign-magnitude | Twos complement | Ones complement |

|---------|----------------|-----------------|-----------------|

| +5      | 0,0101         | 0,0101          | 0,0101          |

| -5      | 1,0101         | 1,1011          | 1,1010          |

| +4      | 0,0100         | 0,0100          | 0,0100          |

| -4      | 1,0100         | 1,1100          | 1,1011          |

To obtain the complement of a number, we can start with the sign-magnitude form of the corresponding positive number and adopt the complementing procedures discussed here. In Example 1.35, the sign bit is separated from the magnitude bits by a "," for illustration purposes only. This separation is not necessary in complement systems since the sign bit also participates in the arithmetic as though it were a magnitude bit (as we will see later in this section).

Table 1.6 shows the range of numbers that can be represented in five bits, in the sign-magnitude, twos complement, and ones complement systems. Note that the sign-magnitude and ones complement systems have two representations for  $0 \ (+0 \ \text{and} \ -0)$ , whereas the twos complement system has a unique representation for 0. Note also the use of the combination 10000 to represent the largest negative number in the twos complement system. In general, the ranges of integers that can be represented in an n-bit field (using 1 sign bit and n-1 magnitude bits) in the three systems are

```

sign-magnitude: -(2^{n-1}-1) to +(2^{n-1}-1) ones complement: (2^{n-1}-1) to (2^{n-1}-1) twos complement: (2^{n-1}) to (2^{n-1}-1)

```

We will now illustrate the arithmetic in these systems of number representation.

**Twos Complement Addition** Example 1.36 illustrates the addition of numbers represented in twos complement form.

TABLE 1.6

The Three Representation Schemes

| Decimal                                | Sign-<br>magnitude | Twos complement | Ones complement |

|----------------------------------------|--------------------|-----------------|-----------------|

| —————————————————————————————————————— |                    | Complement      |                 |

| +15                                    | 01111              | 01111           | 01111           |

| +14                                    | 01110              | 01110           | 01110           |

| +13                                    | 01101              | 01101           | 01101           |

| +12                                    | 01100              | 01100           | 01100           |

| +11                                    | 01011              | 01011           | 01011           |

| +10                                    | 01010              | 01010           | 01010           |

| +9                                     | 01001              | 01001           | 01001           |

| +8                                     | 01000              | 01000           | 01000           |

| +7                                     | 00111              | 00111           | 00111           |

| +6                                     | 00110              | 00110           | 00110           |

| +5                                     | 00101              | 00101           | 00101           |

| +4                                     | 00100              | 00100           | 00100           |

| +3                                     | 00011              | 00011           | 00011           |

| +2                                     | 00010              | 00010           | 00010           |

| +1                                     | 00001              | 00001           | 00001           |

| +0                                     | 00000              | 00000           | 00000           |

| -0                                     | 10000              | 00000           | 11111           |

| -1                                     | 10001              | 11111           | 11110           |

| -2                                     | 10010              | 11110           | 11101           |

| -3                                     | 10011              | 11101           | 11100           |

| -4                                     | 10100              | 11100           | 11011           |

| -5                                     | 10101              | 11011           | 11010           |

| -6                                     | 10110              | 11010           | 11001           |

| -7                                     | 10111              | 11001           | 11000           |

| -8                                     | 11000              | 11000           | 10111           |

| <b>-9</b>                              | 11001              | 10111           | 10110           |

| -10                                    | 11010              | 10110           | 10101           |

| -11                                    | 11011              | 10101           | 10100           |

| -12                                    | 11100              | 10100           | 10011           |

| -13                                    | 11101              | 10011           | 10010           |

| <del>-14</del>                         | 11110              | 10010           | 10001           |

| -15                                    | 11111              | 10001           | 10000           |

| -16                                    |                    | 10000*          |                 |

<sup>\*</sup>Twos complement uses 1000 to expand the range to (-16).

#### Example 1.36

| (a) | Decimal | Sign-magnitude | Twos complement         |

|-----|---------|----------------|-------------------------|

|     | 5       | 0,0101         | 0,0101                  |

|     | 4       | 0,0100         | 0,0100                  |

|     |         |                | $\overline{0,1001} = 9$ |

Here the sign-magnitude and twos complement representations are the same, since both numbers are positive. In twos complement addition, the sign bit is also treated as a magnitude bit and participates in the addition process. In this example, the sign and magnitude portions are separated for illustration purposes only.

| (b) | Decimal              | Sign-magnitude       | Twos complement                   |

|-----|----------------------|----------------------|-----------------------------------|

|     | 5                    | 0,0101               | 0,0101                            |

|     | -4                   | 1,0100               | 1,1100                            |

|     |                      |                      | $\overline{10,0001} = + (0001)_2$ |

|     | Carry from the sign? |                      |                                   |

|     |                      | position is ignored. |                                   |

Here the negative number is represented in the complement form and the two numbers are added. The sign bits are also included in the addition process. There is a carry from the sign bit position, which is ignored. The sign bit is 0, indicating that the result is positive.

| (c) | Decimal | Sign-magnitude | Twos complement                 |

|-----|---------|----------------|---------------------------------|

|     | 4       | 0,0100         | 0,0100                          |

|     | -5      | 1,0101         | 1,1011                          |

|     |         |                | $\overline{1,1111} = -(0001)_2$ |

|     |         |                | The result is negative;         |

|     |         |                | no carry.                       |

Here, no carry is generated from the MSB during the addition. The result is negative since the sign bit is 1; the result is in the complement form and must be complemented to obtain the sign-magnitude representation.

| (d) | Decimal | Sign-magnitude | Twos complement       |

|-----|---------|----------------|-----------------------|

|     | -5      | 1,0101         | 1,1011                |

|     | -4      | 1,0100         | 1,1100                |

|     |         |                | $11,0111 = -(1001)_2$ |

|     |         |                | Ignore the carry; the |

|     |         |                | result is negative.   |

When subtraction is performed in decimal arithmetic (and in the sign-magnitude system), the number with the smaller magnitude is subtracted from the one with the larger magnitude, and the sign of the result is that of the larger number. Such comparison is not needed in the complement system as shown in Example 1.36.

In summary, in twos complement addition, the carry generated from the MSB is ignored. The sign bit of the result must be the same as that of the operands when both operands have the same sign. If it is not, the result is too large to fit into the magnitude field and hence an overflow occurs. When the signs of the operands are different, a carry from the sign bit indicates a positive result; if no carry is generated, the result is negative and must be complemented to obtain the sign-magnitude form. The sign bit participates in the arithmetic.

Ones Complement Addition Example 1.37 illustrates ones complement addition. It is similar to that in twos complement representation, except that the carry generated from the sign bit is added to the LSB of the result to complete the addition.

Sign-magnitude

Ones complement

is -(0001).

### Example 1.37

(a) Decimal

5 0, 0101 0, 0101

$$\frac{1, 1011}{10, 0000}$$

sum

Add the end-around carry  $\frac{1}{0, 0001}$  Ones complement

4 0, 0100 0, 0100  $\frac{1, 1010}{1, 1110}$  sum

No carry.

Complement and the result

## 1.5.3 Shifting Revisited

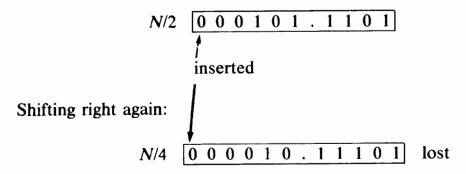

As we have seen before, shifting a binary number left one bit is equivalent to multiplying it by 2. Shifting a binary number right one bit is equivalent to dividing it by 2. Example 1.38 illustrates the effect of shifting an unsigned number.

#### Example 1.38

Consider the number N with six integer bits and four fraction bits:

Shifting N one bit left, with a 0 inserted into the LSB:

Shifting left again:

If we shift this number left again, the 1 in the MSB would be lost, thereby resulting in an overflow.

Shifting N right one bit:

The 1 in the LSB is lost because of this shift, thereby resulting in a less accurate fraction. If there are enough bits to retain all the nonzero bits in the fraction through the shift operation, no loss of accuracy will result. In practice, there will be a finite number of bits for number representation. Hence, care must be taken to see that shifting does not result in either overflow or inaccuracy.

**Sign-magnitude Shifting** When sign-magnitude numbers are shifted, the sign bit is not included in shift operations. Shifting follows the same procedure as in Example 1.38.

Twos Complement Shifting When twos complement numbers are shifted right, the sign bit value is copied into the vacant (MSB of the magnitude) bit position on the left, and a 0 is inserted in the vacant LSB position during the left shift. Example 1.39 illustrates this.

| 0 1       | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 |                   |          |

|-----------|---|---|---|---|---|---|---|---|-------------------|----------|

| $\bigcap$ | 0 | 0 | 1 | 0 | i | 0 | 0 | 0 | right shift (copy | sign bit |

| $\bigcap$ | 1 | 0 | 0 | i | 0 | 1 | 0 | 0 | right shift (copy | sign bit |

| 1         | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | left shift (inser | t 0)     |

| 1 0       | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | left shift (inser | t 0)     |

A change in the value of the sign bit during a left shift indicates that there is an overflow (i.e., the result is too large).

Ones Complement Shifting When ones complement numbers are shifted, a copy of the sign bit is inserted in the vacant LSB position during the left shift, or in the MSB position of the magnitude bits during the right shift. The sign bit receives the MSB of the magnitude during the left shift.

Example 1.40

|             | (a)            | (b)        |                 |

|-------------|----------------|------------|-----------------|

| N           | 1 1001         | 0 0001     |                 |

| 2 <i>N</i>  | 1 0011         | 0 0010     | insert sign bit |

| 4 <i>N</i>  | 0 0111         | 0 0100     |                 |

|             | overflow       | $\bigcirc$ |                 |

| <i>N</i> /2 | 1 1100         | 0 0000     | copy sign bit   |

| N/4         | í <b>1</b> 110 |            |                 |

# 1.5.4 Comparison of Complement Systems

Table 1.7 summarizes the operations in both the complement systems. The twos complement system is now used in almost all digital computer systems. The ones complement system has been used in older computer systems. The advantage of the ones complement system is that the ones complement can be obtained by inverting each bit of the original number from 1 to 0 and 0 to 1, which can be done very easily by the logic components of the digital system. The conversion of a number to twos complement system requires an addition operation after the ones complement of the number is obtained or a scheme to implement the copy/complement algorithm described earlier in this chapter. Twos complement is the most widely used system of representation.

One other popular representation—biased or excess-radix representa-

|            | A CONTRACTOR OF THE CONTRACTOR | Ones complement                                                     | Twos complement                              |                             |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|----------------------------------------------|-----------------------------|

| Operation  | If the carry from the MSB is:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Then perform:                                                       | Then perform:                                | Sign bit of the result      |

| Add        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | form); complet                                                      | complement<br>ment to convert<br>mitude form | 1                           |

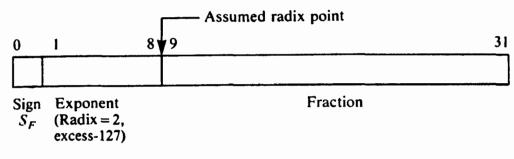

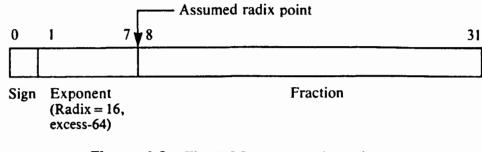

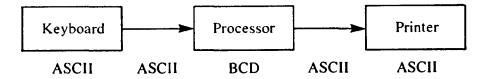

|            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | (Result is in sign-magnitude form); add 1 to the LSB of the result. | ,, <b>C</b>                                  | 0                           |