Sao-Jie Chen

Guang-Huei Lin

Pao-Ann Hsiung

Yu-Hen Hu

# Hardware Software Co-Design of a Multimedia SOC Platform

*Foreword by*

Giovanni de Micheli

# Hardware Software Co-Design of a Multimedia SOC Platform

# Hardware Software Co-Design of a Multimedia SOC Platform

by

**Sao-Jie Chen**

*National Taiwan University, Taipei, Taiwan, ROC*

**Guang-Huei Lin**

*National Taiwan University, Taipei, Taiwan, ROC*

**Pao-Ann Hsiung**

*National Chung Cheng University, Chia-Yi, Taiwan, ROC*

and

**Yu-Hen Hu**

*University of Wisconsin-Madison, Madison, USA*

Prof. Sao-Jie Chen

National Taiwan University

Dept. Electrical Engineering

Graduate Inst. of Electronics

Engineering

Taipei 106

Taiwan R.O.C.

csj@cc.ee.ntu.edu.tw

Dr. Pao-Ann Hsiung

National Chung Cheng

University

Chia-Yi 621

Taiwan R.O.C.

Dr. Guang-Huei Lin

National Taiwan University

Dept. Electrical Engineering

Graduate Inst. of Electronics

Engineering

Taipei 106

Taiwan R.O.C.

Dr. Yu-Hen Hu

University of Wisconsin,

Madison

Dept. Electrical & Computer

Engineering

1415 Engineering Drive

Madison WI 53706

2556 Engineering Hall

USA

ISBN: 978-1-4020-9622-8

e-ISBN: 978-1-4020-9623-5

DOI 10.1007/978-1-4020-9623-5

Library of Congress Control Number: 2008941282

© Springer Science+Business Media B.V. 2009

No part of this work may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, microfilming, recording or otherwise, without written permission from the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work.

Printed on acid-free paper

9 8 7 6 5 4 3 2 1

[springer.com](http://springer.com)

# Foreword

System-level design is a key design technology to realize integrated systems of various types, possibly integrated on a single die, i.e., *Systems on Chips*, or assembled in a single package, i.e., *Systems in Package*. As technology advances and systems become increasingly more complex, the use of high-level abstractions and platform-based design becomes more and more a necessity. Indeed the productivity of designers increases with the abstraction level, as demonstrated by practices in both the software and hardware domains. The use of high-level models and platforms allow designers to be productive, even when they have weaker specific skills in circuit design technology.

Software plays a key role in embedded system design and is crucial for system programmability and flexibility. The latter factor is extremely important for extending the life of components across different families of products. Compilation is the crucial technology to achieve effective system operation on platforms, starting from high-level programming constructs. The compiler technology has evolved tremendously, especially in the domain of *application-specific instruction set processor* design which is commonplace in embedded platforms.

Effective software compilation is the companion to hardware compilation, also called high-level synthesis. Both share important objectives, like addressing real-time constraints and system performance. The software and hardware design technologies show complementarities and find their most natural applications on platform-based design.

Multi-media systems benefit largely from modular and flexible realizations relying on platforms. The market for these systems is rapidly expanding and its future hinges in part on the industrial capability to deliver advanced systems with rapid turn-around time. In this perspective, the technologies described in this book are very significant for progress of science and technology and have direct impact on applications ranging from entertainment to medical imaging, from terrestrial environmental monitoring to defense.

Lausanne

November 25, 2008

Giovanni De Micheli

# Preface

This book is the outcome of a recent international collaborative research project aiming at developing both the hardware and software of a platform based SoC (System-on-Chip) architecture for embedded multimedia systems. Since its inception a decade ago, SoC has captured the attentions of application specific integrated circuit (ASIC) design houses, computer aided design (CAD) companies, and embedded system developers. In particular, the immense popularity of killer multimedia gadgets such as iPod, and iPhone has fueled unprecedented interests in developing new generation multimedia SoC systems.

However, the high level of integration also brings great challenges to system designers: Conventional component-oriented design methodologies can no longer handle the ever increasing system complexity. Hardware and software are necessarily becoming convergent and must be fully concurrent design endeavors. Hardware engineers must understand higher level signal processing algorithms, functional simulations, and design verifications. Software engineers, on the other hand, must pay great attention to heterogeneous instruction set architectures, timing and power constraints, and hardware-in-the-loop system level simulation and verifications. All these point to a diverse body of knowledge, and skills that a competent SoC designer must be equipped. Currently, such valuable knowledge sources are scattered in many different text books, research papers, and other on-line sources. For someone who is interested in gaining a comprehensive overview of issues related to the hardware and software development of multimedia SoC, a highly integrated book is unavailable.

This book is written to serve this purpose. Based on a joint research project co-ordinated by S. J. Chen at the National Taiwan University (NTU) in Taiwan, this book is co-authored by key participants of a project entitled: Implementation of a Multimedia SoC Platform for Scalable Power-Aware Custom Embedded Systems. In this 3-year research project, we focused on a novel SoC platform based on a Subword-Parallel Single Instruction Multiple Data (SWP-SIMD) micro-architecture. Much of the materials included in this monograph are drawn from outcomes of this research project. A distinct feature of this book is to incorporate a very diverse list of subjects and tied them together elegantly to the development of an SWP-SIMD based SoC platform. Specifically, subject areas that covered include system level design methodologies, H.264 video coding algorithms, sub-word parallel micro-architecture design, SIMD vectorized compiler technology, and real time operating

systems. Obviously, with limited space, it is impossible to engage in-depth discussion of each subject area. Instead, the authors' approach is to provide sufficient detail so that readers may appreciate the significance of each topic and understand the relations of a particular subject to other topics. Plenty of references are provided so that interested readers may pursue further investigation using materials presented in this book as a stepping stone. We understand that such an ambitious goal would not be easy to reach. We hope our efforts will make some tangible contributions toward promoting the SoC platform design and applications.

This book is written for engineers who are working in integrated circuit design houses, in computer aided design tool companies, and embedded system design companies; as well as graduate students who are pursuing a career in computer engineering, multimedia system implementation and related field. We will be very happy to hear readers' feedback and comments.

Taipei, Taiwan

Taipei, Taiwan

Chia-Yi, Taiwan

Madison, Wisconsin

Sao-Jie Chen

Guang-Huei Lin

Pao-Ann Hsiung

Yu-Hen Hu

# Acknowledgements

The authors are greatly thankful to the foreword writer, Professor and Director Giovanni De Micheli at the Institute of Electrical Engineering and the Integrated Systems Center at the École Polytechnique Fédérale de Lausanne, Switzerland.

The authors are also grateful to those who have made great contributions to the development of this book. The PLX instruction set architecture was originally developed by Professor Ruby Lee at the Princeton University. She has provided numerous valuable inputs to the design of the PLX core. She also generously provided us with an LCC compiler, Assembler, and Loader for the PLX architecture.

Many current and former graduate students in our research groups have made tangible contributions to portions of this book. Specifically, Ya-Nan Wen and Chia-Wen Tsai of National Taiwan University have made significant contributions to the PLX and H.264 chip implementations. Xiao-Long Wu, Cheng-Cho Jean, and Hong-Kuei Chen of National Taiwan University have contributed to the development of the SIMD compiler and profiler tools. Chun-Jen Wei of National Taiwan University contributed to the development of algebraic verification tool. Chao-Sheng Lin of National Chung-Cheng University has developed the RTOS described in this book.

Finally, we would like to express our appreciation to our family members for their encouragement and patience during the writing of this book.

Taipei, Taiwan

Taipei, Taiwan

Chia-Yi, Taiwan

Madison, Wisconsin

Sao-Jie Chen

Guang-Huei Lin

Pao-Ann Hsiung

Yu-Hen Hu

# Contents

|          |                                   |           |

|----------|-----------------------------------|-----------|

| <b>1</b> | <b>Introduction</b>               | <b>1</b>  |

| <b>2</b> | <b>Design Consideration</b>       | <b>5</b>  |

| 2.1      | Platform-Based Design             | 5         |

| 2.1.1    | OMAP                              | 8         |

| 2.2      | System Modeling                   | 10        |

| 2.2.1    | State-Oriented Models             | 11        |

| 2.2.2    | Activity-Oriented Models          | 12        |

| 2.3      | Video Coding                      | 15        |

| 2.3.1    | H.264 Coding Process              | 17        |

| 2.3.2    | Motion Estimation                 | 17        |

| 2.3.3    | Intra Prediction                  | 22        |

| 2.3.4    | Transform and Quantization        | 24        |

| 2.3.5    | De-Blocking Filter                | 26        |

| 2.3.6    | Entropy Encoding                  | 27        |

| 2.4      | Image Processing                  | 27        |

| 2.5      | Cryptography                      | 31        |

| 2.5.1    | RSA                               | 32        |

| 2.5.2    | DES                               | 34        |

| 2.5.3    | AES                               | 34        |

| 2.6      | Digital Communication             | 36        |

| 2.7      | Multimedia Instruction Set Design | 39        |

| <b>3</b> | <b>System Level Design</b>        | <b>41</b> |

| 3.1      | Abstraction Levels                | 42        |

| 3.1.1    | Algorithm Level                   | 42        |

| 3.1.2    | Architecture Level                | 42        |

| 3.1.3    | Behavior Level                    | 44        |

| 3.2      | Algorithm Level Verification      | 45        |

| 3.2.1    | Algebraic Simulation              | 46        |

| 3.2.2    | Algebraic Analysis                | 48        |

| 3.2.3    | Error Evaluation                  | 48        |

|          |                                        |           |

|----------|----------------------------------------|-----------|

| 3.3      | Transaction Level Modeling .....       | 52        |

| 3.4      | System Level Development Tools .....   | 55        |

| 3.4.1    | SystemC .....                          | 56        |

| 3.4.2    | LISA .....                             | 58        |

| <b>4</b> | <b>Embedded Processor Design .....</b> | <b>63</b> |

| 4.1      | Specific Instruction-Set .....         | 63        |

| 4.2      | Data Level Parallelism .....           | 64        |

| 4.2.1    | SIMD .....                             | 64        |

| 4.2.2    | SWP-SIMD .....                         | 67        |

| 4.3      | Instruction Level Parallelism .....    | 70        |

| 4.3.1    | SuperScalar .....                      | 70        |

| 4.3.2    | VLIW .....                             | 71        |

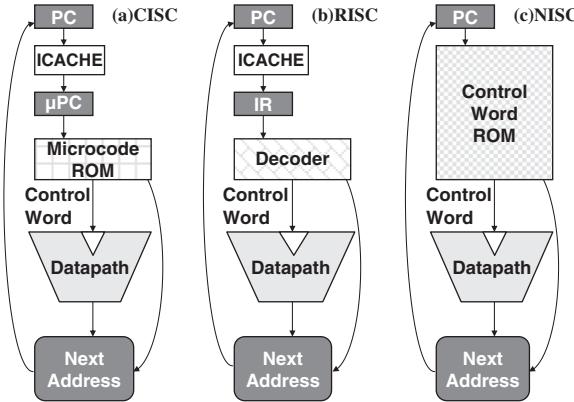

| 4.3.3    | NISC .....                             | 74        |

| 4.4      | Thread Level Parallelism .....         | 76        |

| 4.4.1    | Multi-Threading .....                  | 76        |

| 4.4.2    | Multi-Processor .....                  | 77        |

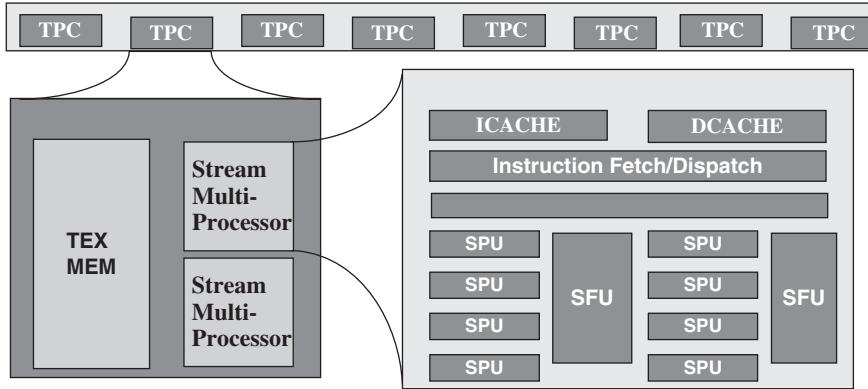

| 4.4.3    | Massively Parallel .....               | 78        |

| <b>5</b> | <b>Parallel Compiler .....</b>         | <b>81</b> |

| 5.1      | Vectorization .....                    | 81        |

| 5.1.1    | Dependence Analysis .....              | 81        |

| 5.1.2    | Loop Normalization .....               | 83        |

| 5.1.3    | Loop Transformation .....              | 84        |

| 5.1.4    | Dependence Removal .....               | 84        |

| 5.1.5    | Strongly Connected Components .....    | 85        |

| 5.1.6    | Loop Distribution .....                | 86        |

| 5.2      | Simdization .....                      | 87        |

| 5.2.1    | Control Flow Conversion .....          | 87        |

| 5.2.2    | Memory Alignment .....                 | 88        |

| 5.2.3    | Permutation Optimization .....         | 89        |

| 5.2.4    | Subword Fusion .....                   | 90        |

| 5.2.5    | Matrix Transpose .....                 | 90        |

| 5.2.6    | Reduction .....                        | 90        |

| 5.2.7    | Loop Unrolling .....                   | 91        |

| 5.3      | ILP Scheduling .....                   | 92        |

| 5.3.1    | Software Pipelining .....              | 92        |

| 5.3.2    | Basic Block Extension .....            | 93        |

| 5.3.3    | Speculation .....                      | 93        |

| 5.4      | Threading .....                        | 94        |

| 5.4.1    | Profiling and Analysis .....           | 94        |

| 5.4.2    | Pthread .....                          | 95        |

| 5.4.3    | Structuring .....                      | 97        |

| 5.4.4    | OpenMP .....                           | 99        |

|                         |                                                    |            |

|-------------------------|----------------------------------------------------|------------|

| 5.5                     | Compiler Technique .....                           | 100        |

| 5.5.1                   | Lexical Analysis .....                             | 100        |

| 5.5.2                   | Syntax Analysis .....                              | 101        |

| 5.5.3                   | Abstract Syntax .....                              | 102        |

| 5.5.4                   | Semantic Analysis .....                            | 103        |

| 5.5.5                   | Symbol-Table Management .....                      | 104        |

| 5.5.6                   | Intermediate Representation .....                  | 104        |

| 5.5.7                   | Code Optimization .....                            | 105        |

| 5.5.8                   | Code Generation .....                              | 106        |

| 5.6                     | Compiler Infrastructures .....                     | 106        |

| 5.6.1                   | LCC Compiler Infrastructure .....                  | 107        |

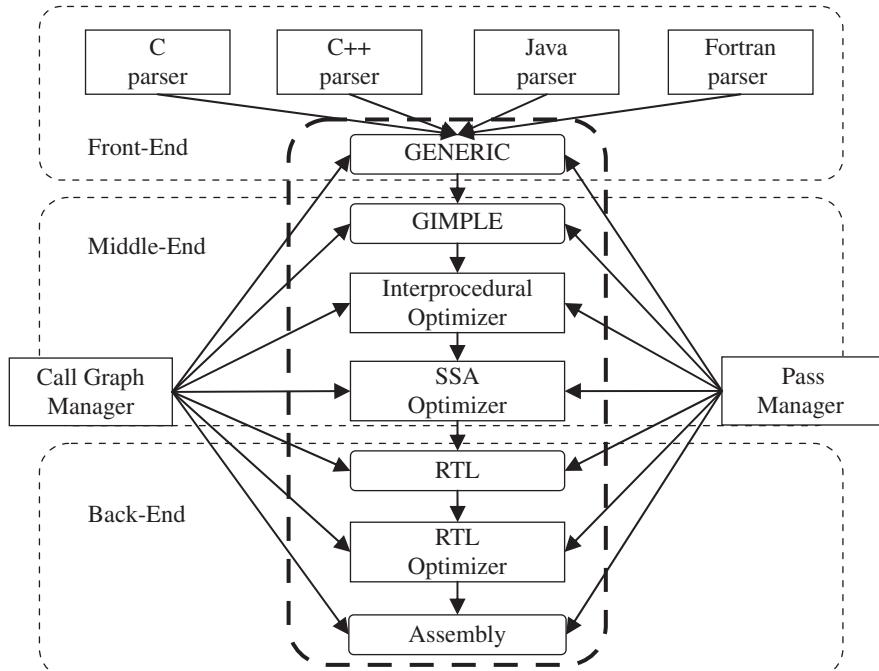

| 5.6.2                   | GCC Compiler Infrastructure .....                  | 107        |

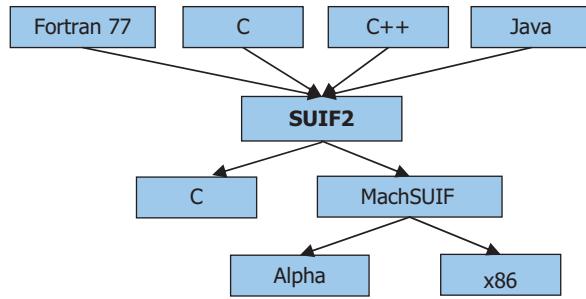

| 5.6.3                   | SUIF Compiler Infrastructure .....                 | 109        |

| 5.6.4                   | IMPACT Compiler Infrastructure .....               | 113        |

| <b>6</b>                | <b>Implementation of H.264 on PLX .....</b>        | <b>115</b> |

| 6.1                     | Instruction Set Decision for H.264 .....           | 115        |

| 6.2                     | Hardware/Software Partitioning .....               | 116        |

| 6.3                     | Untimed Virtual Prototype .....                    | 117        |

| 6.4                     | Timed SystemC Modeling .....                       | 122        |

| 6.5                     | PLX Chip Design .....                              | 127        |

| <b>7</b>                | <b>Real-Time Operating System for PLX .....</b>    | <b>129</b> |

| 7.1                     | PRRP Scheduler .....                               | 131        |

| 7.2                     | Memory Management .....                            | 133        |

| 7.3                     | Communication and Synchronization Primitives ..... | 134        |

| 7.4                     | Multimedia Applications in RTOS for PLX .....      | 135        |

| 7.5                     | Application Development Environment .....          | 136        |

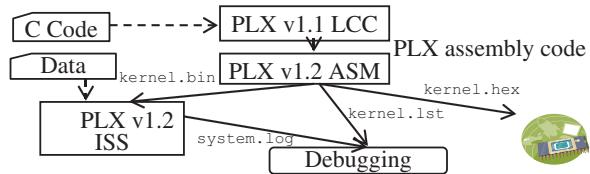

| 7.5.1                   | Compilers .....                                    | 137        |

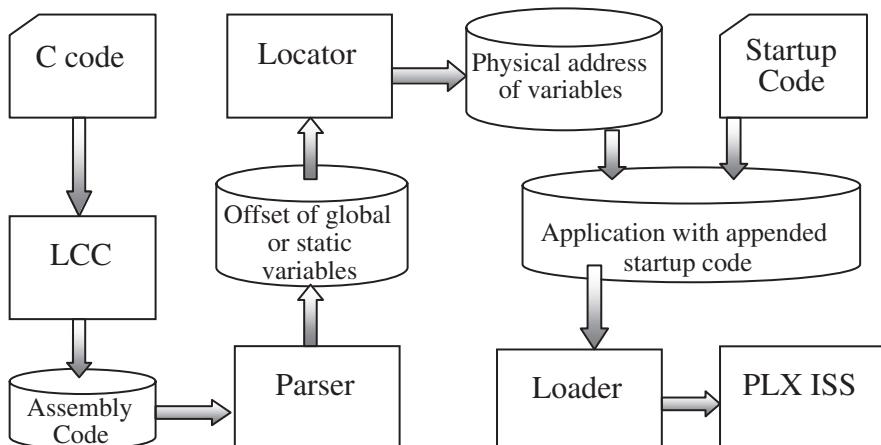

| 7.5.2                   | Parser, Locator, Loader, and Startup Code .....    | 137        |

| 7.5.3                   | PLX Platform Simulator .....                       | 139        |

| 7.6                     | Experimental Results .....                         | 139        |

| <b>8</b>                | <b>Conclusion .....</b>                            | <b>145</b> |

| <b>References .....</b> |                                                    | <b>147</b> |

# List of Figures

|      |                                                              |    |

|------|--------------------------------------------------------------|----|

| 2.1  | System platform design concept .....                         | 6  |

| 2.2  | ARM-based wireless communication platform .....              | 7  |

| 2.3  | Mix-and-match methodology .....                              | 8  |

| 2.4  | OMAP software architecture .....                             | 9  |

| 2.5  | Profiling report .....                                       | 10 |

| 2.6  | Resource utilization .....                                   | 10 |

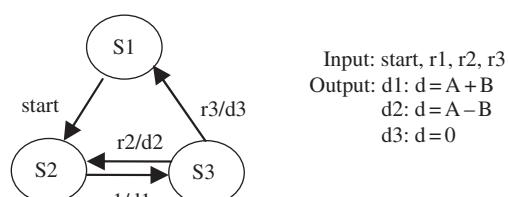

| 2.7  | Mealy finite state machine .....                             | 11 |

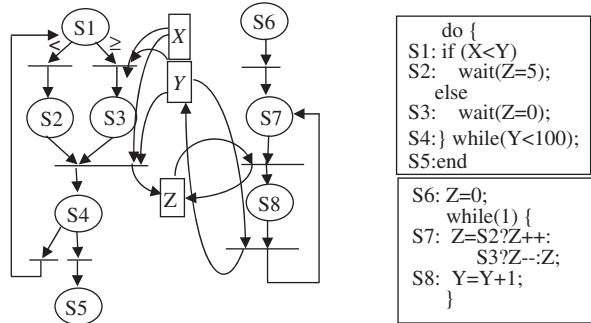

| 2.8  | Petri-nets of two concurrent processes .....                 | 12 |

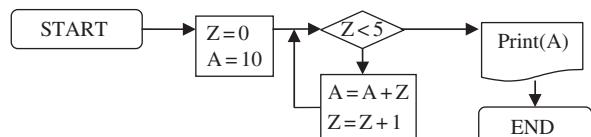

| 2.9  | Flow chart .....                                             | 12 |

| 2.10 | CDFG .....                                                   | 13 |

| 2.11 | Compound if-else statements in HTG form .....                | 14 |

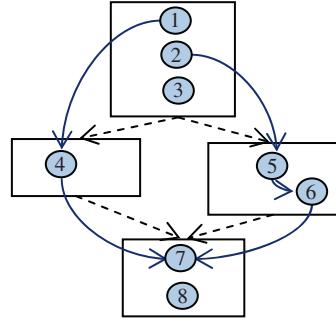

| 2.12 | An example of PDG .....                                      | 15 |

| 2.13 | An example of SDG .....                                      | 16 |

| 2.14 | H.264 coding process .....                                   | 18 |

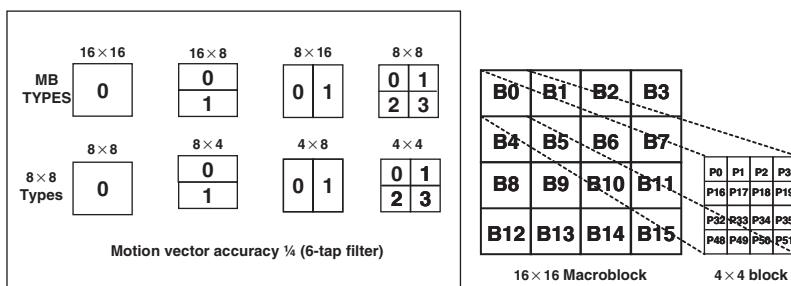

| 2.15 | Variable block size and segmented macroblock .....           | 19 |

| 2.16 | 1-D motion estimation architecture .....                     | 20 |

| 2.17 | Schedule of data input for each PE .....                     | 21 |

| 2.18 | Three-step search .....                                      | 22 |

| 2.19 | INTRA_4×4 prediction neighbors .....                         | 23 |

| 2.20 | INTRA_4×4 prediction modes .....                             | 23 |

| 2.21 | INTRA_16×16 prediction modes .....                           | 24 |

| 2.22 | Filtered edges of 16×16 luma and 8×8 chroma macroblock ..... | 27 |

| 2.23 | Filters with Gaussian and Semi-Gaussian coefficients .....   | 28 |

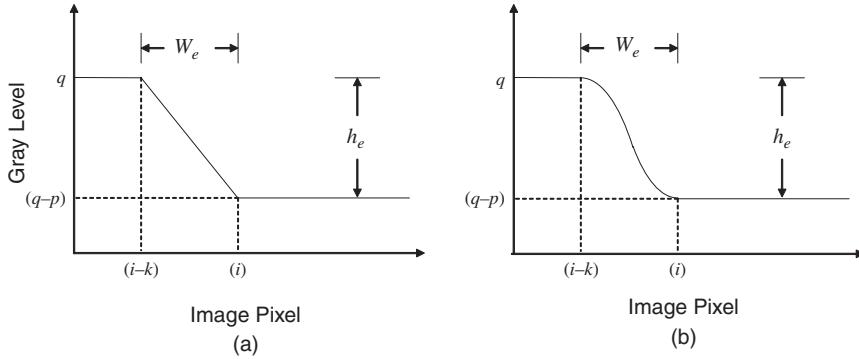

| 2.24 | Linear edge and non-linear edge .....                        | 29 |

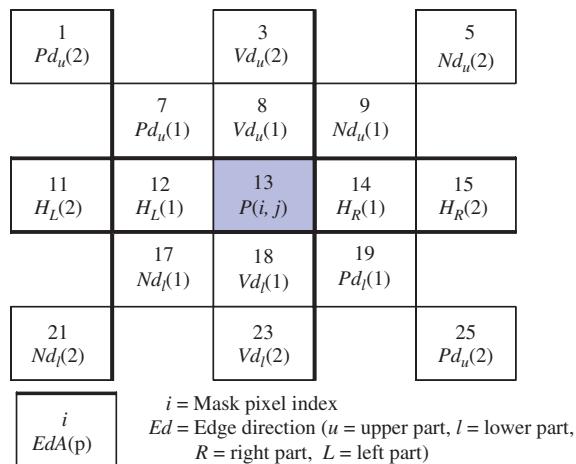

| 2.25 | Absolute difference mask .....                               | 29 |

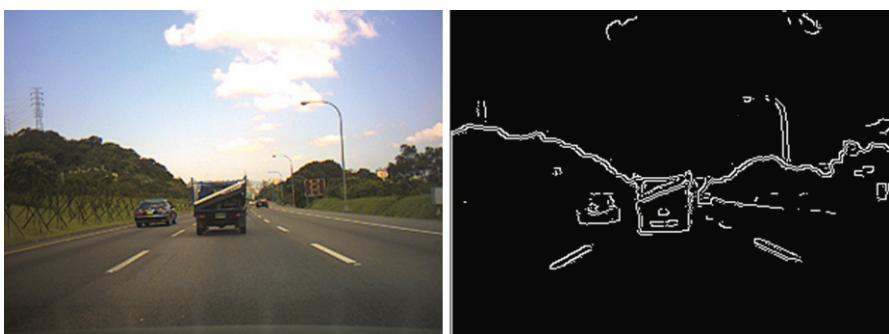

| 2.26 | Symmetric feature .....                                      | 30 |

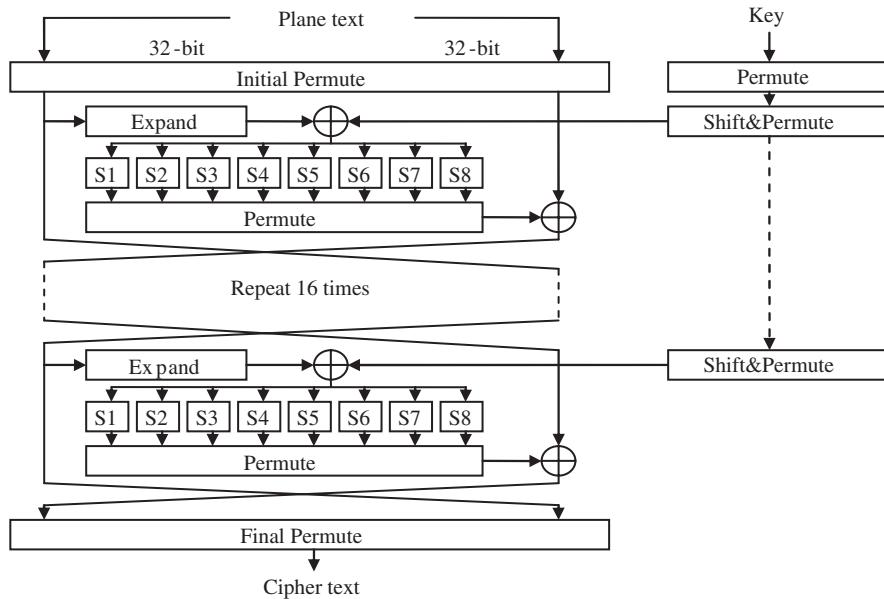

| 2.27 | DES encryption flow .....                                    | 35 |

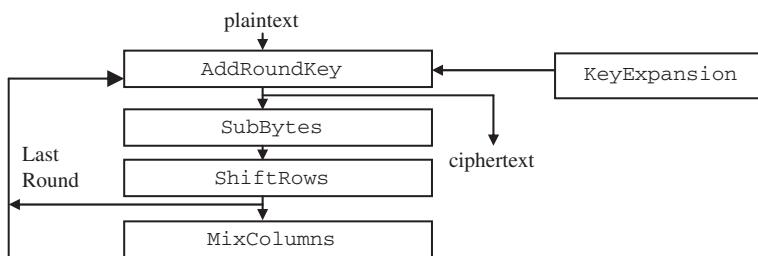

| 2.28 | AES encryption flow .....                                    | 35 |

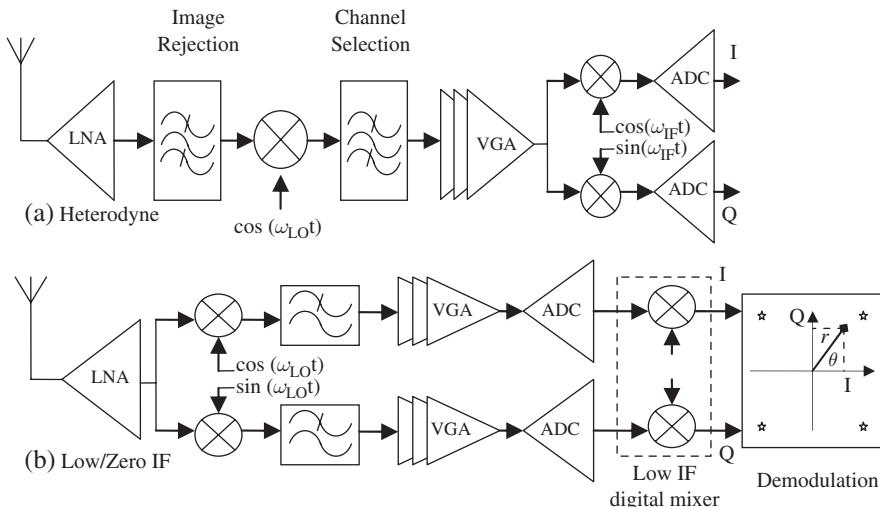

| 2.29 | Receiver front-end architectures .....                       | 36 |

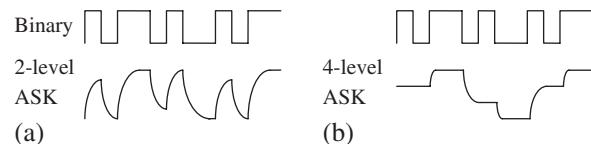

| 2.30 | Waveform of ASK modulation .....                             | 37 |

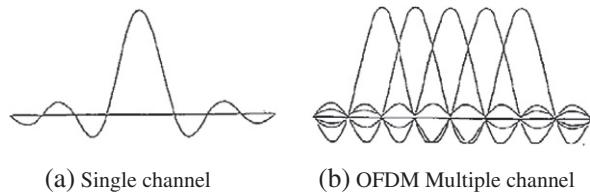

| 2.31 | OFDM spectrum .....                                          | 38 |

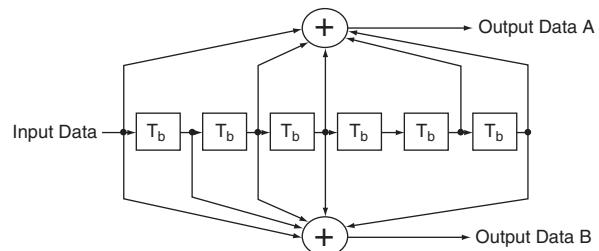

| 2.32 | Convolution coding .....                                     | 38 |

| 3.1  | System level design .....                                    | 41 |

|      |                                                                                          |     |

|------|------------------------------------------------------------------------------------------|-----|

| 3.2  | A $4 \times 4$ Matrix transpose in PLX assembly . . . . .                                | 47  |

| 3.3  | Matrix transpose modeled in Mathematica . . . . .                                        | 47  |

| 3.4  | Result of matrix transpose . . . . .                                                     | 47  |

| 3.5  | An implementation of SAD on the PLX platform . . . . .                                   | 49  |

| 3.6  | Symbolic verification and error prediction algorithm . . . . .                           | 50  |

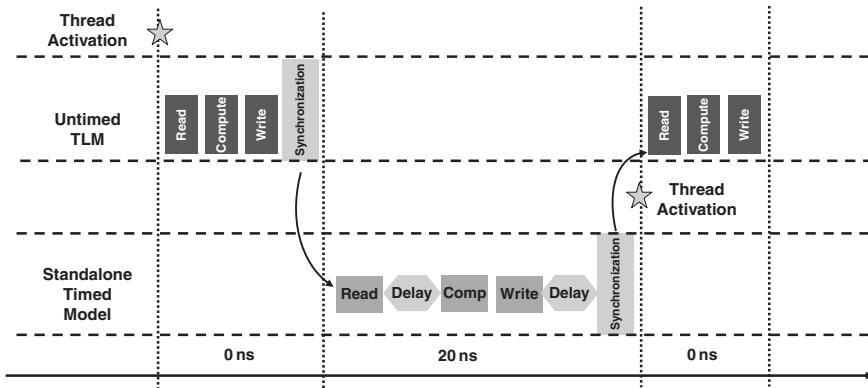

| 3.7  | Inter-execution of untimed and timed models . . . . .                                    | 55  |

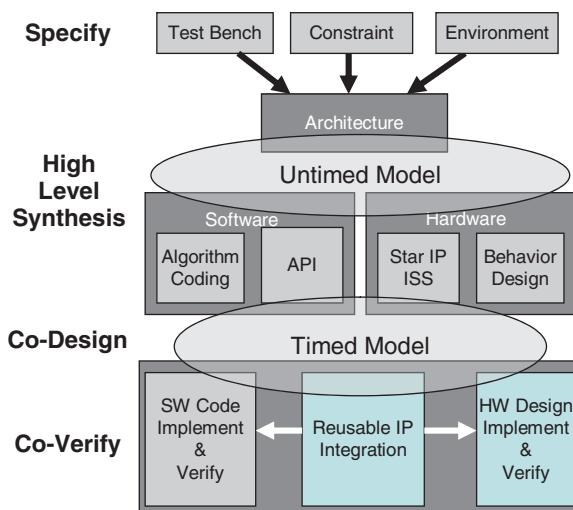

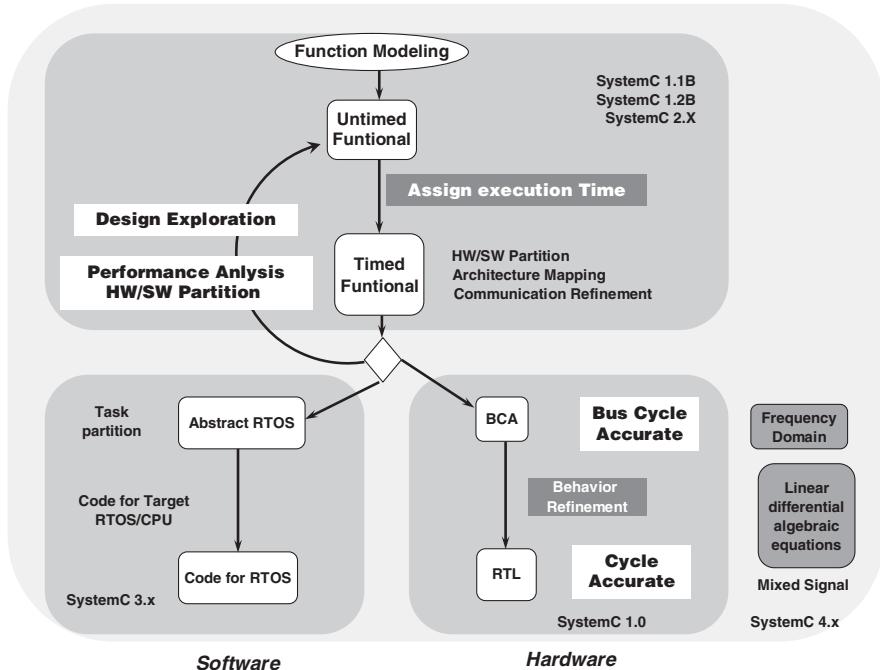

| 3.8  | SystemC versions and scopes . . . . .                                                    | 56  |

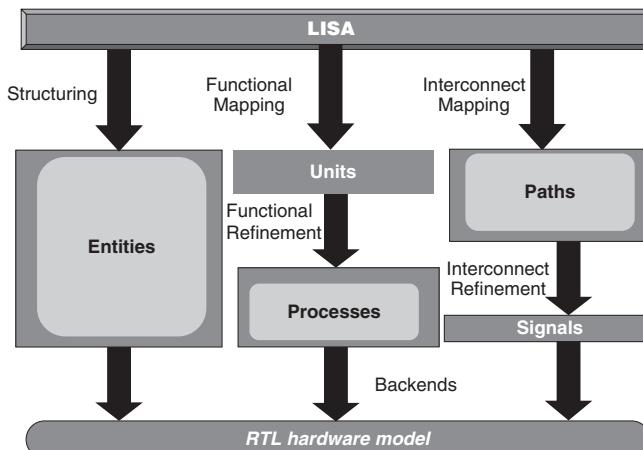

| 3.9  | LISA behavior synthesis process . . . . .                                                | 60  |

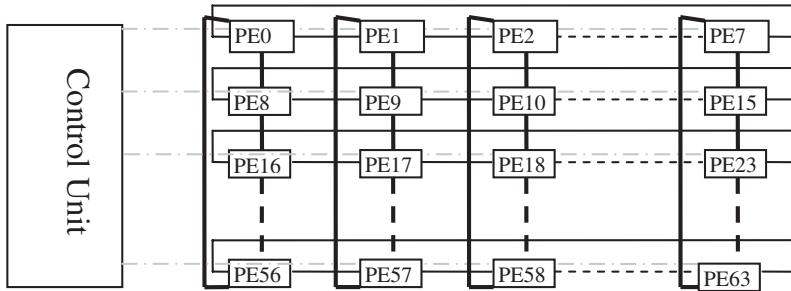

| 4.1  | ILLIAC-IV architecture . . . . .                                                         | 65  |

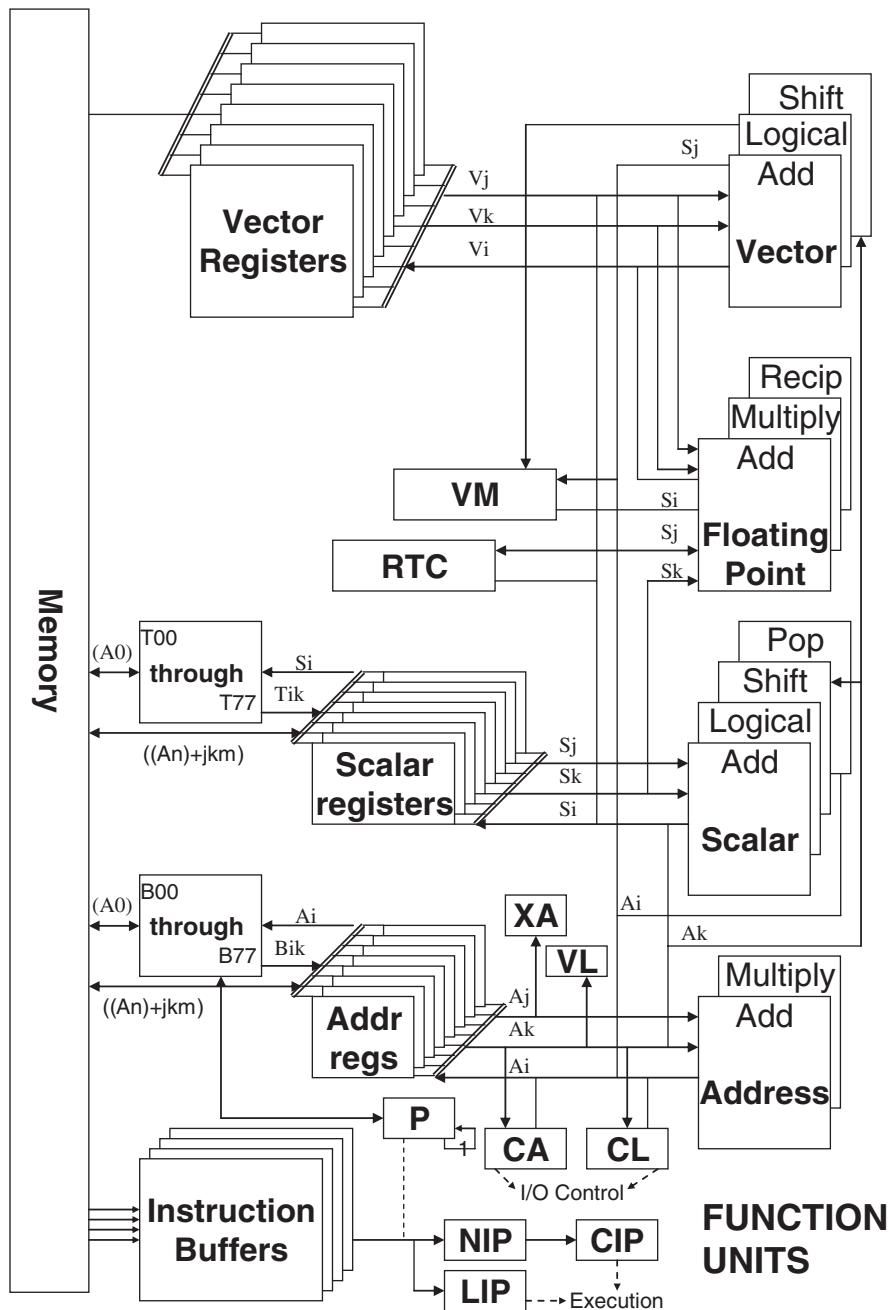

| 4.2  | Cray-1 architecture . . . . .                                                            | 66  |

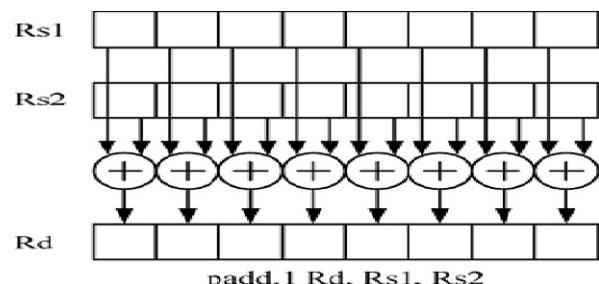

| 4.3  | Subword-parallel execution . . . . .                                                     | 68  |

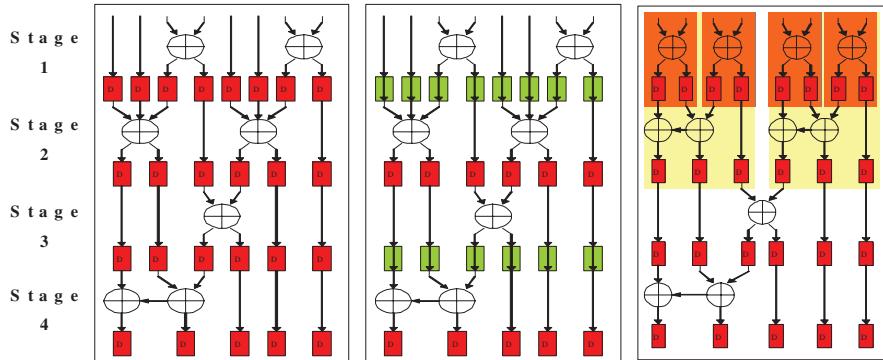

| 4.4  | Power-aware reconfigurable pipeline adder . . . . .                                      | 69  |

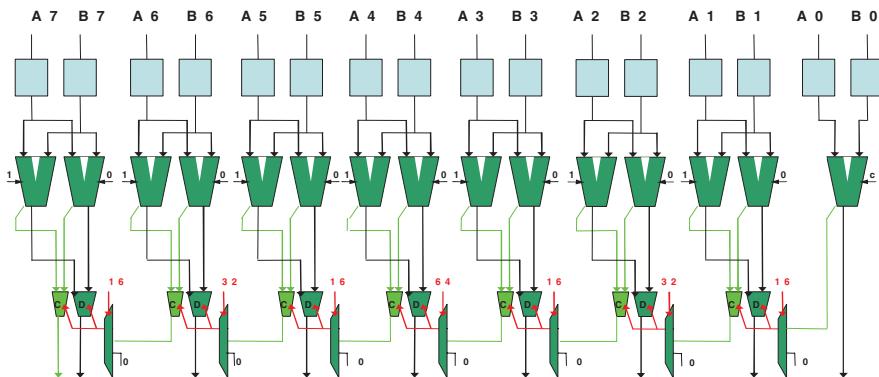

| 4.5  | High-performance subword-parallel design . . . . .                                       | 69  |

| 4.6  | Pentium 4 processor micro-architecture . . . . .                                         | 71  |

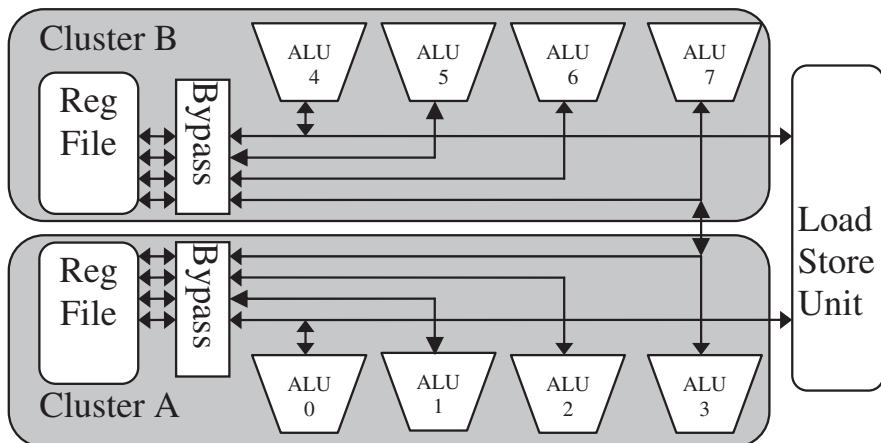

| 4.7  | A generic two-cluster VLIW architecture . . . . .                                        | 72  |

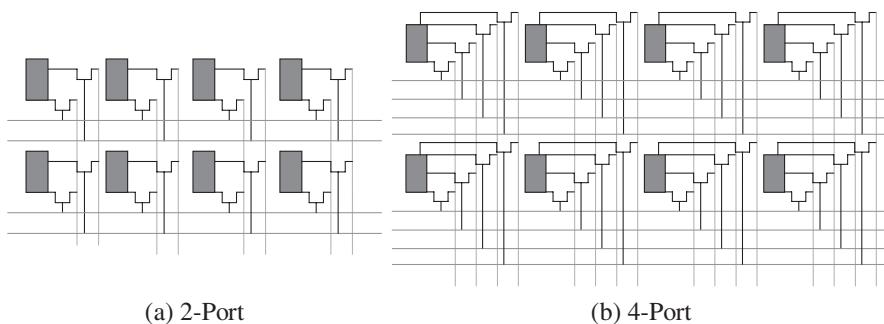

| 4.8  | Register file . . . . .                                                                  | 72  |

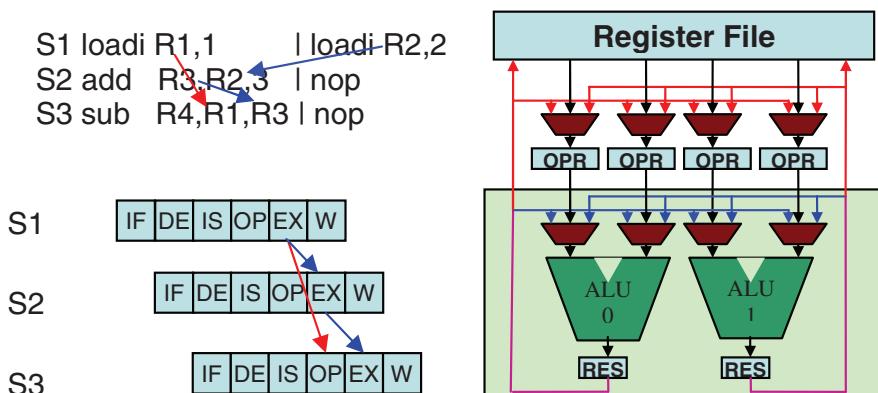

| 4.9  | Bypass path in a 2-issue VLIW . . . . .                                                  | 73  |

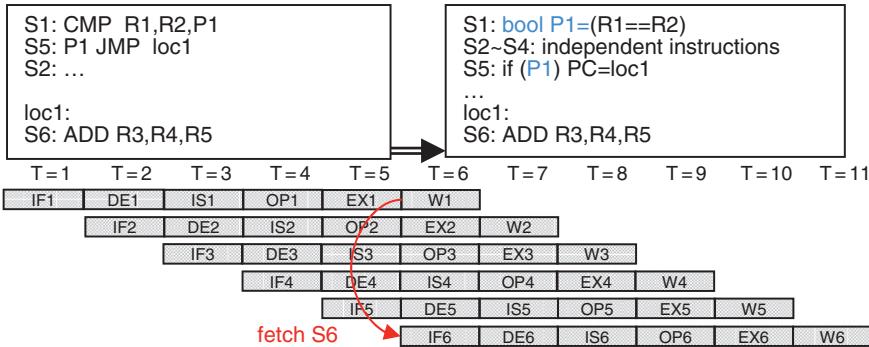

| 4.10 | Unbundled branch . . . . .                                                               | 74  |

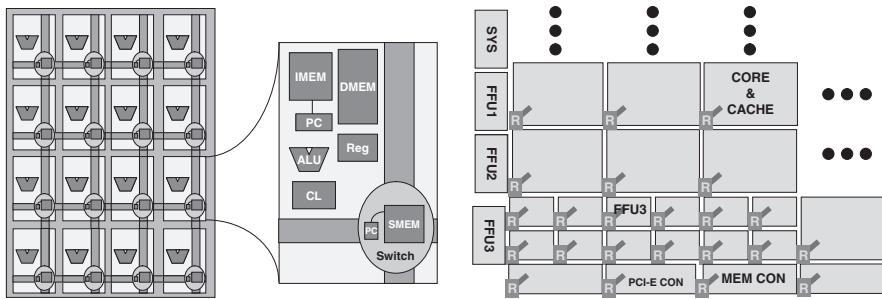

| 4.11 | Processor architectures . . . . .                                                        | 76  |

| 4.12 | nVIDIA GeForce 8800 . . . . .                                                            | 79  |

| 4.13 | Many cores: <b>(a)</b> MIT RAW Processor and <b>(b)</b> Intel Tera-Flops chip . . . . .  | 79  |

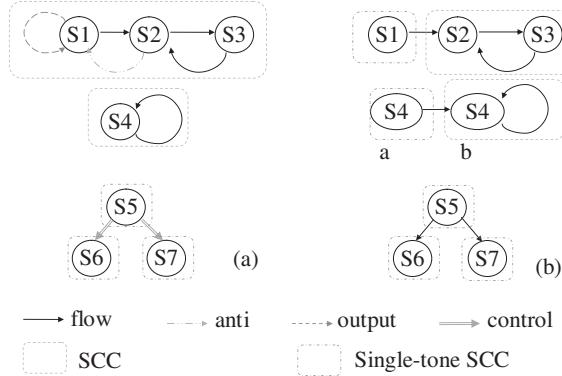

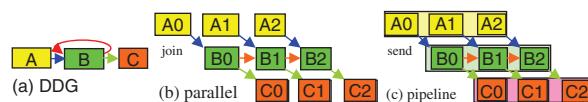

| 5.1  | Dependence graphs: <b>(a)</b> original and <b>(b)</b> after dependence removal . . . . . | 86  |

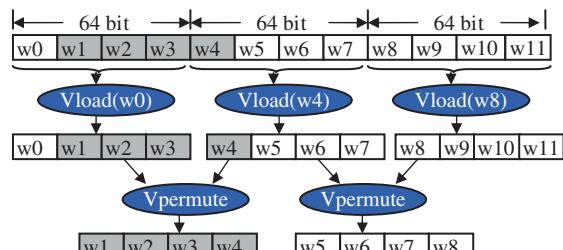

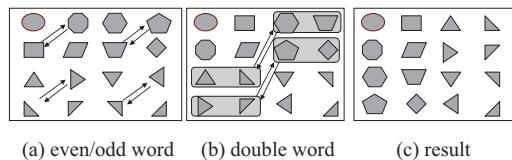

| 5.2  | Load vector by streaming . . . . .                                                       | 88  |

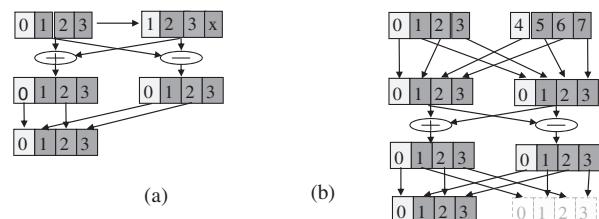

| 5.3  | Interleaved average/difference implementations . . . . .                                 | 89  |

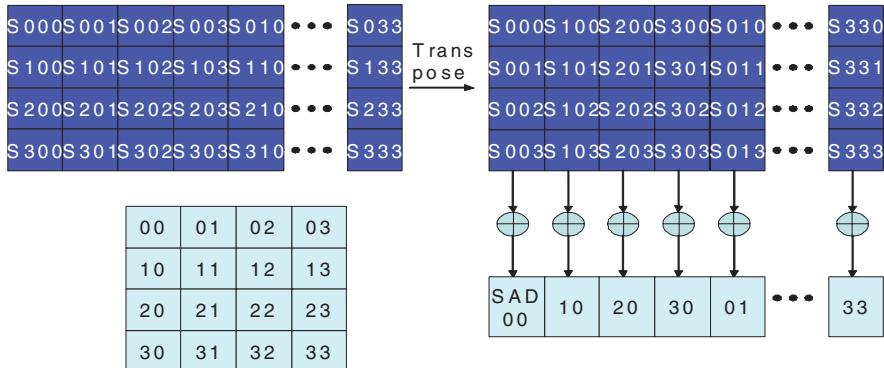

| 5.4  | Matrix transpose in SWP-SIMD . . . . .                                                   | 90  |

| 5.5  | Software pipelining . . . . .                                                            | 92  |

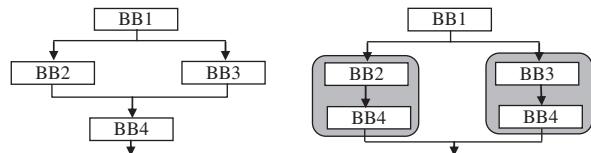

| 5.6  | Basic block tail duplication . . . . .                                                   | 93  |

| 5.7  | Loop parallelism . . . . .                                                               | 97  |

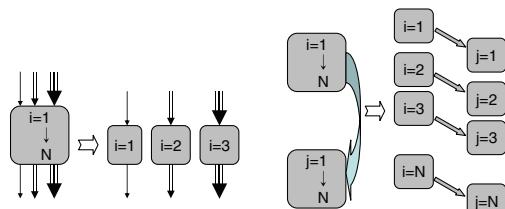

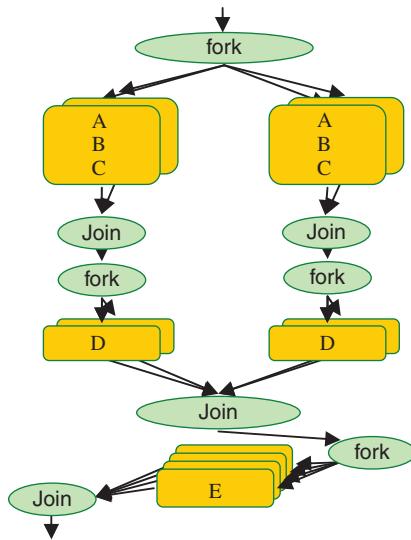

| 5.8  | Data decomposition threading . . . . .                                                   | 98  |

| 5.9  | Pipeline thread structure . . . . .                                                      | 98  |

| 5.10 | SPMD code example . . . . .                                                              | 99  |

| 5.11 | OpenMP code of SPMD . . . . .                                                            | 99  |

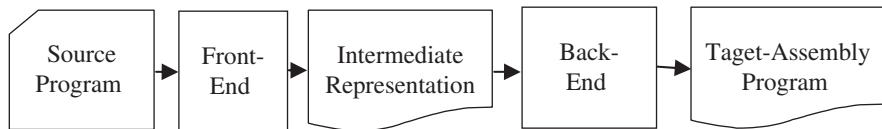

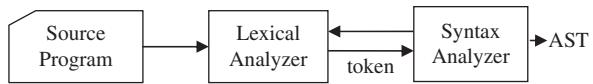

| 5.12 | Main phases of a compiler . . . . .                                                      | 100 |

| 5.13 | Communication between lexical and syntax analyzers . . . . .                             | 101 |

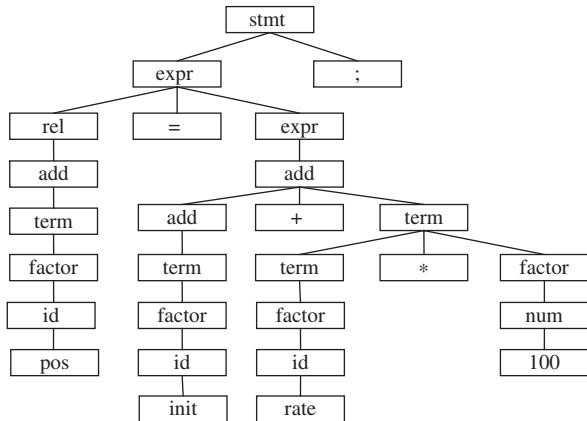

| 5.14 | Grammar for simple arithmetic expressions . . . . .                                      | 102 |

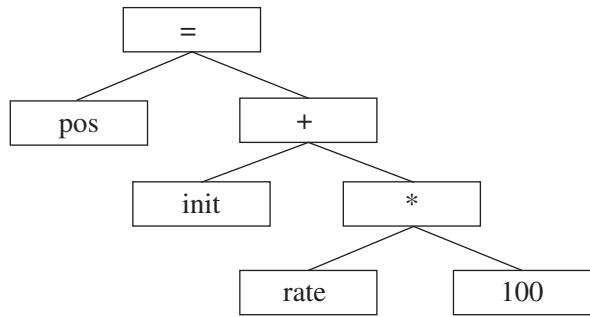

| 5.15 | Parse tree for “pos = init + rate * 100;” . . . . .                                      | 102 |

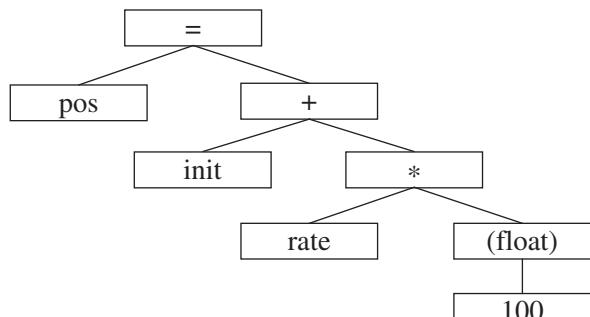

| 5.16 | AST for “pos = init + rate * 100;” . . . . .                                             | 103 |

| 5.17 | AST after semantic analysis . . . . .                                                    | 103 |

| 5.18 | An overview of GCC . . . . .                                                             | 108 |

| 5.19 | SUIF system . . . . .                                                                    | 110 |

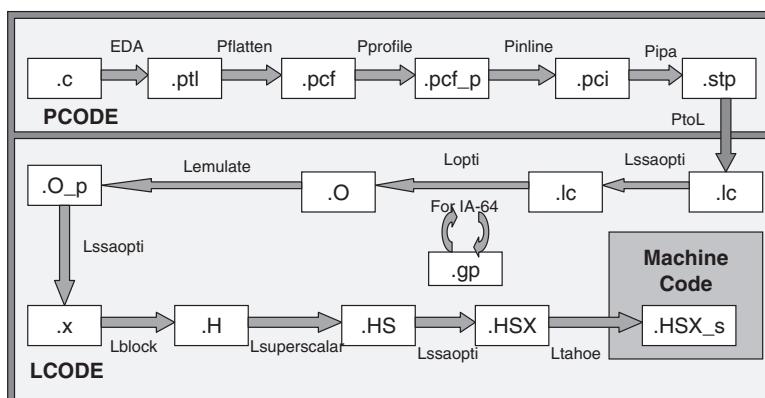

| 5.20 | IMPACT compiler flow . . . . .                                                           | 113 |

| 6.1  | SAD calculation in a 128-bit SWP-SIMD . . . . .                                          | 117 |

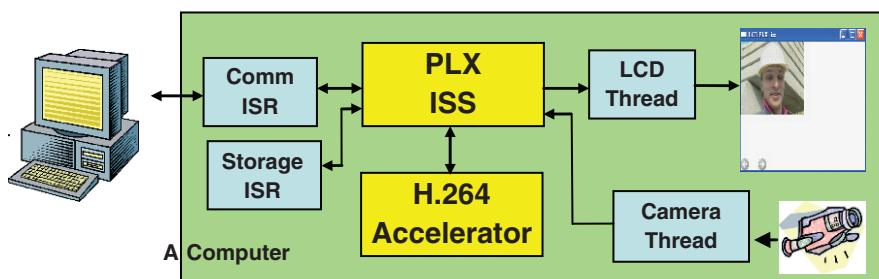

| 6.2  | A PLX-H.264 virtual prototype platform . . . . .                                         | 118 |

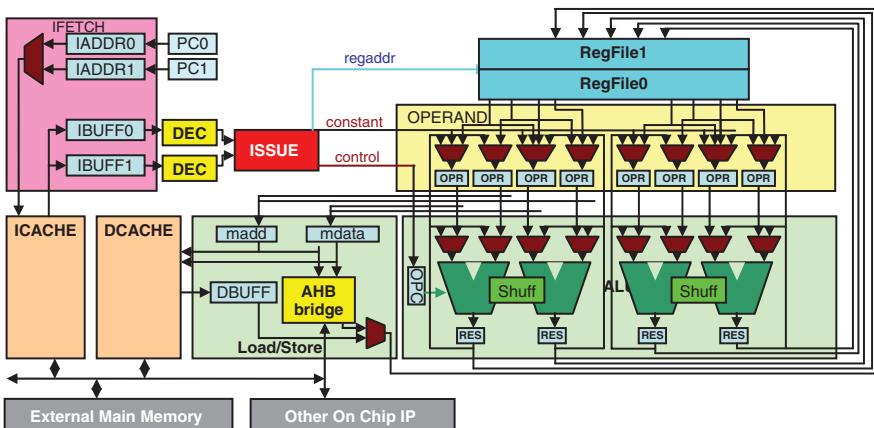

| 6.3  | PLX chip architecture . . . . .                                                          | 127 |

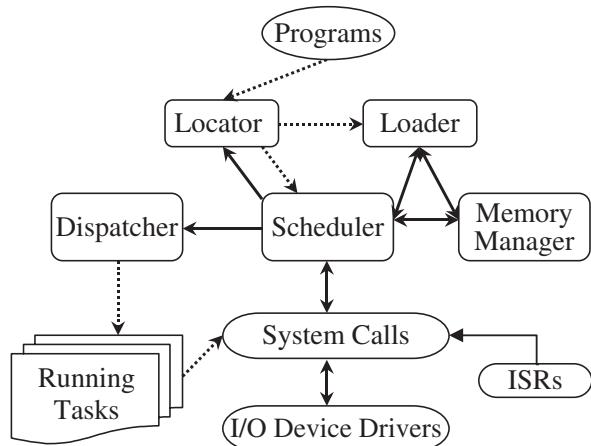

| 7.1  | RTOS components and relations . . . . .                                                  | 130 |

|      |                                                                                            |     |

|------|--------------------------------------------------------------------------------------------|-----|

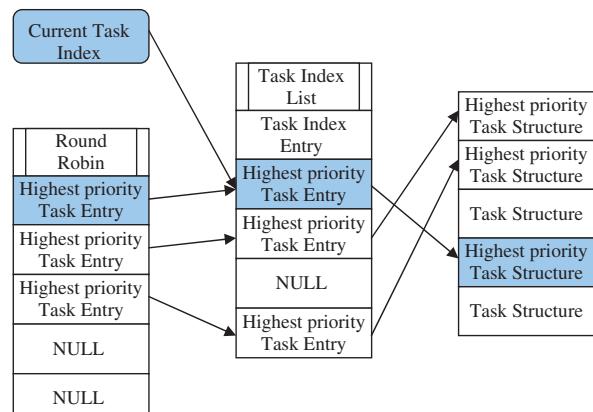

| 7.2  | Extended data structure for the PRRP scheduler . . . . .                                   | 131 |

| 7.3  | PRRP scheduling algorithm in RTOS for PLX . . . . .                                        | 132 |

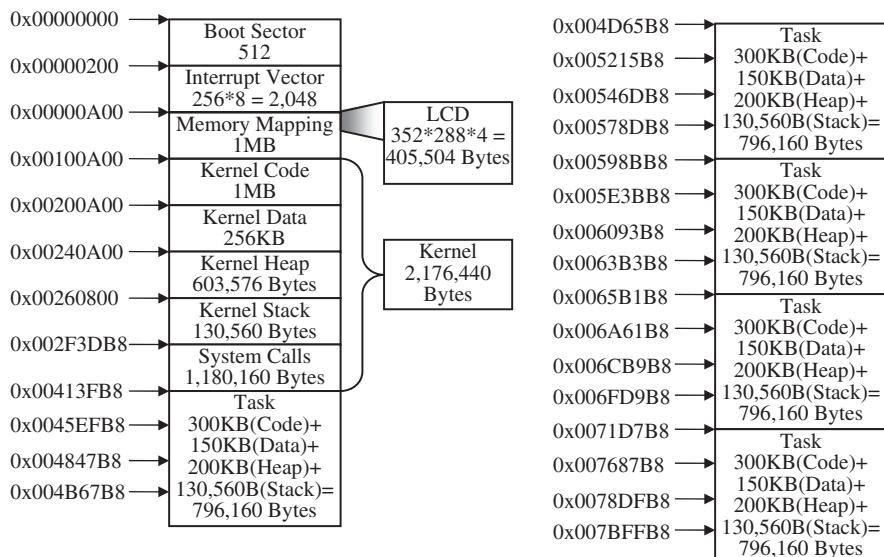

| 7.4  | Memory layout in RTOS for PLX . . . . .                                                    | 133 |

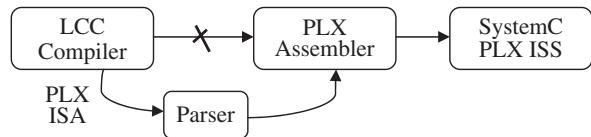

| 7.5  | Toolchain flow for application development on RTOS for PLX . . . . .                       | 137 |

| 7.6  | Toolchain incompatibilities solved by our parser . . . . .                                 | 138 |

| 7.7  | Data flow among parser, locator, and Loader . . . . .                                      | 138 |

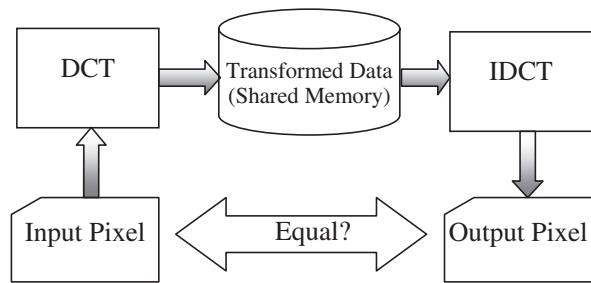

| 7.8  | Test flow using DCT and IDCT . . . . .                                                     | 140 |

| 7.9  | Start addresses for binary files in the DCT/IDCT example . . . . .                         | 142 |

| 7.10 | Two-dimensional matrix input/output of DCT . . . . .                                       | 142 |

| 7.11 | Segment of multimedia extension instructions for (a) DCT and (b)<br>Quantization . . . . . | 143 |

## List of Tables

|                                                    |     |

|----------------------------------------------------|-----|

| 2.1 Popular platforms .....                        | 7   |

| 2.2 Quantization table .....                       | 26  |

| 6.1 PSNR in SAD with 3 different resolutions ..... | 116 |

# Chapter 1

## Introduction

What is embedded processing? One of the simplest definitions is that embedded processing is not for general purpose. General purpose processors are the ones used in desktop PCs and servers. Development tools for desktop processor are popular, and there are millions of software developed for desktop processor. Thus, using general purpose processor can reduce time-to-market. But this solution is not optimized on some critical metrics including performance, cost, power, and size. Many embedded multimedia systems are handheld systems, such as MP3 players, PDAs and 3G phones. A single general purpose processor is unable to handle real-time functions such as communication, camera, video, audio, touch screen, TV, and GPS in time, or it will consume too much power.

Many embedded processors have worse performance on general applications, but have much better performance on some specific applications than the general purpose processors. The well-known examples are *digital signal processor* (DSP) and network processor.

Embedded system devices normally embody the functionality they implemented. In other words, they are designed to run a few codes with a predictable pattern. In contrast, applications of a general purpose system are barely known in advance. A traditional embedded system design flow is to select proper processor and peripheral device controllers, then to spend most of the effort on developing software for this system.

In 1965, Gordon Moore predicted that the number of transistors incorporated in an IC would increase twofold every year. This was really an amazing prediction that proved to be more accurate than Moore had believed. In the past few decades, the scale of IC integration has been soaring high. It started from *Small Scale Integration* (SSI) with around 100 transistors per IC in 1960s, up to *Very Large Scale Integration* (VLSI) accommodating more than 10000 transistors per IC in 1980s. There is no sign that such tendency would ever cease. In recent years, the integration scale has only slightly slowed down to a factor of two for every eighteen months. The outburst of IC complexity, as predicted by Moore's Law, is driving the current semiconductor industry to challenge another cutting edge revolution: *System-on-Chip* (SoC) with the capacity of integrating more transistors in a single chip to form an entire electronic system. This concept is feasible thanks to the very exceptional manufacturing advances that bring IC nanotechnology to fruition.

As Moore's Law continues unencumbered into the nanometer era, process geometries have shrunken to 65 nm, chips are reaching the giga-gate scale. It brings the possibility to integrate all processors and peripheral device controllers into a chip.

Traditional hardware-software partitioning is simply as: critical functions performed by specific hardware and control-oriented functions by software. Here specific hardware is defined as an *application specific integrated circuit* (ASIC) which is a special design dedicated for an application, and software means running a code on a general purpose processor. In the last century, most embedded systems need specific hardware to process multimedia applications, with the constraint of power consumption or performance. In general, specific hardware is more power-efficient than software for an application with the same performance. But specific hardware is less flexible to adapt to new features.

In SoC era, *time-in-market* becomes as important as *time-to-market*. Any new chip production needs to pay very high *non-returnable engineering* (NRE) cost even if there is only a little modification from the previous version. By the same reason, we wish that the chip can sustain longer and useable for more applications. For example, in IP-based 4G wireless communication, we would like to design a chip used for both WiMAX (*Worldwide Interoperability for Microwave Access*) and LTE (*Long Term Evolution*), while these standards are not well-defined. The key to applying a single integrated circuit to multiple applications for both time-to-market and time-in-market is *programmability*.

An *application specific instruction-set processor* (ASIP) is a software-programmable processing-element tailored for this purpose. It provides efficient and economic way for a particular application computation. An ASIP may add some multimedia operations or encryption operations into its instruction-set to improve performance with low cost-overhead.

To compete with the performance of ASIC, many parallelization techniques are adapted into ASIP. These techniques include *data level parallelism* (DLP) in a *single instruction multiple data* (SIMD) processor, *instruction level parallelism* (ILP) in a *very large instruction word* (VLIW) processor, and *thread level parallelism* (TLP) in a multi-threading processor. Armed with these parallelism mechanisms, multi-core becomes more and more feasible and popular in embedded SoCs.

Therefore, a specialized parallel compiler becomes more important to optimize an application on a specific multi-core processor. This kind of parallel compiler has not only to translate high-level programming language instructions into the target ASIP codes, but also to schedule these instructions to exploit the parallelization capability of that ASIP.

Software needs to run on its target processor. While processor and compiler are designing, software is unable to design until a prototype was developed. Without verification by software, the processor is not guaranteed to meet system constraints, thus the ASIP needs to be re-designed many times. To reduce the long cycle, both developing software as early as possible and evaluating system constraints at a higher system level become very important.

The fundamental building blocks of an SoC are its *intellectual property* (IP) cores, which are reusable hardware blocks designed to perform a particular task

of a given component. An IP core could either be a programmable component like a processor, or a hardware entity with fixed behavior like an MPEG accelerator. Different IP cores are interconnected on an SoC by a communication structure, such as a shared bus or *network-on-chip* (NoC), in order to establish communication among them.

IP reuse drives the progress of system-level design. A reusable IP can be obtained from the third-party IP provider. Typically IP providers would not release RTL design. The time spent to identify a third-party IP and integrate it into the designed system places this approach at an unfavorable position compared to designing the IP in-house. A higher level *Transaction Level Modeling* (TLM) description is more feasible for IP providers to protect their design.

TLM is the current promotion methodology used for hardware/software co-design before and after hardware/software partitioning. Before partitioning, TLM could be used to create a point-to-point, addressless functional yet concurrent system model, reusing IP behaviors from application engineers. After partitioning, TLM automatically wraps the behavior in the address-mapped TLM model for embedded software functional verification.

Most embedded systems are real-time, which time constraint is critical. A real-time embedded operating system is required to serve memory allocation, peripheral I/O device system calls, inter-process communication, and priority-based task scheduling.

PLX [1], developed by Professor Ruby Lee at Princeton University, is a native *subword-parallel single instruction multiple data* (SWP-SIMD) processor [2] that supports high-performance, low-cost multimedia information processing, 3-D graphical processing and permutation instructions for security operations. This book intends to discuss many of the above mentioned hardware-software codesign issues that we encountered in designing a PLX-based embedded multimedia SoC platform.

The book contents are organized as follows. Chapter 2 introduces traditional platform-based hardware-software co-design and some multimedia algorithms that require ASIP. Chapter 3 introduces some system level design techniques that we used to design our SIMD PLX core. Chapter 4 introduces ASIP processor design techniques and parallelization methodologies, such as DLP, ILP and TLP. Chapter 5 introduces parallel compiler techniques specifically tailored for PLX. Chapter 6 describes the design of PLX processor and its virtual platform TLM modeling. Chapter 7 introduces real-time operating system OS development experience for PLX. Finally, a conclusion is drawn in Chapter 8.

# Chapter 2

## Design Consideration

In this chapter, we briefly describe the basic concepts of a platform-based design, system-level modeling techniques used in designing a platform, and some multimedia algorithms that require specific instruction set design in a processor core, such as PLX, a native *single-instruction multiple-data* (SIMD) core developed by Professor Ruby Lee at Princeton University [1].

### 2.1 Platform-Based Design

A platform is a library of components that can be assembled to generate a design. This library not only contains computational blocks that carry out the appropriate computation but also communication components that are used to interconnect the functional components.

Platform-based design changes design flow from vertically-oriented into horizontally-oriented. For information protection, a product is fully designed and manufactured in an early industrial company. The increase of electronic design complexity and the advances in technologies force designers to focus on their core competence. The pressure for reducing time-to-market of electronics products in the presence of exponentially increasing complexity has forced designers to adopt methods that favor component reuse. Furthermore, each organization that contributes a component to the final product naturally strives for a position that allows it to make continuous adjustments and accommodate last-minute engineering changes.

Each design should satisfy constraints on characteristics such as performance, cost, power consumption, and weight. It brings a choice for designer to implement a function as a hardware component or as a software code running on a programmable component.

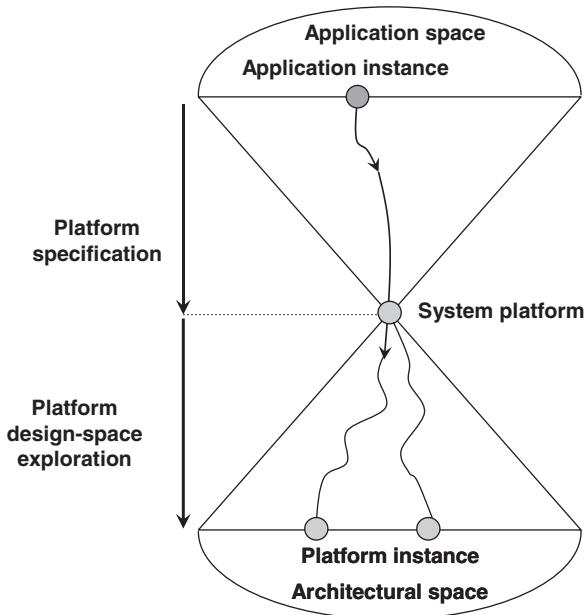

Platform-based design is a meet-in-the-middle process, where successive refinements of specifications meet with abstractions of potential implementations that are captured in the models of the elements of the platform. Figure 2.1 shows this concept [3]. The comprehensive model includes the views of platforms from the application and the implementation architecture perspectives that meet at the vertex of the two cones.

**Fig. 2.1** System platform design concept

Hardware and software reuse is the key concept on platform-based design. Reusing a reference platform is the only solution to time-to-market. Table 2.1 lists some popular platforms. There are hundreds of embedded-system SoC platforms on market for different applications. Prototyping is important to verify a newly designed hardware in a platform. Some SoC platforms contains configurable field programmable gate array (FPGA) which allow users to add their hardware, such as Philip's RSP (Rapid System Prototyping) and Altera's Excalibur.

A platform should contain an architecture model and its associated design methodology. The architecture model is a predefined architecture which consists of various families of components such as processor, memory, function blocks, and system bus/communications. The design methodology is constructed as an integrated design flow with multiple levels at which component modeling, simulation environment, and in-circuit emulator (ICE) are provided.

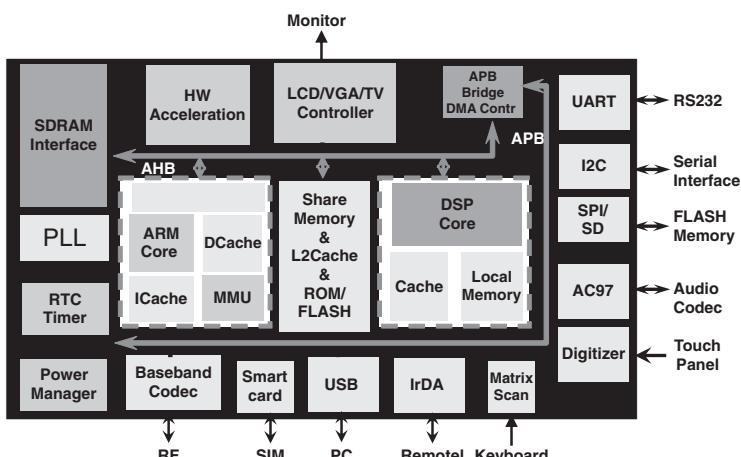

A platform is mostly provided by a processor vendor. Today the most widely used platform for SoC is based on the ARM processor. Figure 2.2 shows an example.

The above platform contains a DSP to handle communication and image processing, and a CPU (an ARM core) to handle peripheral function blocks and general-purpose processing. The two processors share memory by a system bus (ASB). Many of the following function blocks need these two processors to handle: the Real-Time Clock (RTC) for scheduling; LCD/VGA Controllers for display; Keyboard Controller (K/B), Digitizer and Joystick Controllers for human interface input; Voice Codec for speaker and microphone; Baseband Codec connected to a radio front-end (RF); SPI interface for storage cards, Smartcard Controller for authentication; USB/UART to communicate with other system; and a hardware accelerator

**Table 2.1** Popular platforms

| Market   | Target application | Platform name | Manufacturer |

|----------|--------------------|---------------|--------------|

| Consumer | Digital Camera     | Raptor II     | Conexant     |

|          | PDA                | PXA240        | Intel        |

|          | PDA                | DragonBall    | Motorola     |

|          | DVD R/W            | Dimension8600 | LSI          |

|          | Set Top Box        | Omega Sti5512 | ST           |

|          | Digital TV         | TL850         | Teralogic    |

|          | Digital Audio      | TMS320Daxx    | TI           |

|          | MP3                | Maverick      | Cirrus       |

|          | DAB                | TMS320DRE200  | TI           |

|          | Home Plug          | Piranha       | Cogency      |

|          | USB device         | PSoC          | Cypress      |

|          | General            | CSoC          | Triscend     |

|          | General            | Excalibur     | Altera       |

|          | General            | SoC-Raptor    | Wipro        |

|          | General            | PalmPak       | Palmchip     |

|          | General            | RSP           | Philips      |

|          | General            | PSA           | Improv       |

| Wireless | CDMA               | MSM3000       | Qualcomm     |

|          | GSM 2.5G           | SGOLD         | Infineon     |

|          | GSM 2.5G           | OMAP710       | TI           |

|          | 3G                 | I300          | Motorola     |

|          | BlackBerry         | SoftFone+     | ADI          |

|          | 802.11b/Bluetooth  | TrueRadio     | Mobilian     |

|          | 802.11a            | Tondelayo     | Systemonic   |

|          | 802.11a AP         | AR5001AP      | Atheros      |

|          | Bluetooth          | Bluecore      | CSR          |

|          | GPS                | Sifstar       | Sirf         |

**Fig. 2.2** ARM-based wireless communication platform

to assist image processing. All these blocks support real-time functions. All above function blocks on the system are connected by a bus hierarchy. Each function block that is using a bus will affect the performance of other function blocks on the bus. Before access to the bus, each function block needs to get authentication from the bus arbiter. Too many function blocks connected on a bus will make it unable to work while most time are spent on authentication.

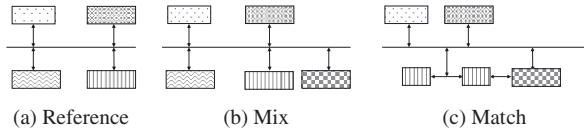

On a desktop PC, possible peripheral to integrate is unknown, thus *Plug-and-Play* is required. System bus should be designed to satisfy the highest possible bandwidth, thus it is over-designed for normal work-load. In embedded systems, a Mix-and-Match methodology is used instead. At first a reference platform is selected, which is mostly provided by the processor vendor. Then function blocks are inserted or removed, and workloads are rescheduled by system level analysis. If bandwidth constraint is not satisfied, modify either a function block or the bus architecture and try again. For example, if the new function occupies too many bandwidths to access a shared memory, adding a dedicated memory and a local bus as shown in Fig. 2.3 can solve this problem.

**Fig. 2.3** Mix-and-match methodology

### 2.1.1 OMAP

OMAP (Open Multimedia Application Platform) is a series of dual-core processor developed by TI for multimedia and wireless applications. OMAP1510 is built of an ARM925 processor core, a TI TMS320C55x DSP core, a 192 KB share-memory interface, and some peripherals for multimedia applications [4]. The ARM925 core containing a 16 KB instruction cache and an 8 KB data cache can work up to 175 MHz. The TMS320C55 DSP core containing a 16 KB instruction cache and an 8 KB data cache can work up to 200 MHz. It embeds 64 KB dual-port RAM and 96 KB single-port RAM, and a graphic accelerator with two multiply-accumulator (MAC) units.

Running with the same clock frequency, power consumption of a DSP core is higher than an ARM core. The DSP core is efficient to compute data-oriented codes, and the ARM core is better on control-oriented codes. A typical 1024-point FFT computation run on an ARM needs 1 mega cycles, but only 40 K cycles on a DSP. Both the ARM and DSP software codes can be developed under a single Code Composer Studio (CCS) environment, which helps to reduce the dual-core programming complexity. TI offer abundant of Chip Support Library application interface (CSLAPI) to low level programming effort.

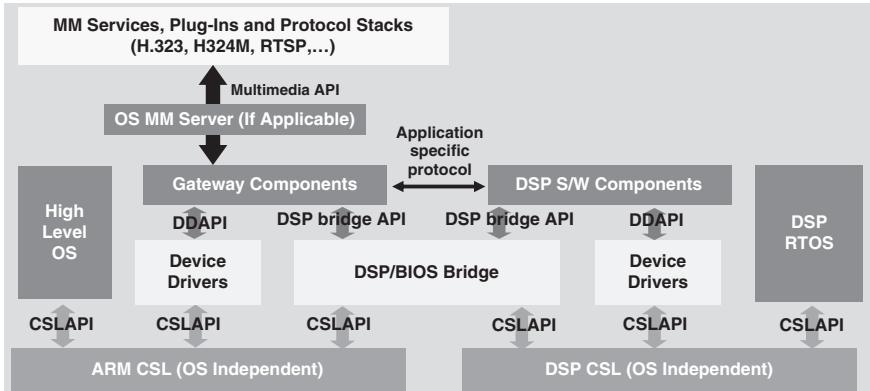

The key technique used in the OMAP software architecture as shown in Fig. 2.4 is the DSP/BIOS Bridge. Both ARM and DSP are working under a single operating

Fig. 2.4 OMAP software architecture

system (OS). Programmer can treat DSP as a device attached under Linux OS directory `/dev`. A high level multimedia API offers a unified interface to designer. High computation operation is dispatched to DSP/BIOS Bridge by DSP API. DSP/BIOS Bridge handles the scheduling and inter-core communication.

ARM and DSP use shared-memory message-passing architecture for communication. Message is packed as a mailbox, including command, data and flag. Both cores can create more than one task, each of which will create a mailbox channel under the `/dev` directory for communication. When a message is ready in shared-memory, an interrupt will wake up the device driver to inform a corresponding task to receive the message.

Following shows the implementation of an MP3 decoder as an example. MP3 (MPEG-1 layer-3) is an audio coding standard. MP3 stream is composed of many frames. A single channel frame contains 2 granules and each granule has 576 16-bit samples. The 576 samples are down-sampled into 32 sub-bands, where each sub-band contains 18 samples. The down-sampling is a 5-iteration process. And in each iteration, the samples are partitioned into two sub-bands respectively by low-pass and high-pass filters. The 32 sub-bands are transformed into frequency domain by Modified Discrete Cosine Transform (MDCT), and quantized by a psychoacoustic model. Finally Huffman Entropy Encoding is applied to reduce bit rate.

Before implementing the decoder on OMAP, we have to analyze which parts of MP3 decoding take most execution time and have to implement on a DSP. A profiling tool, GNU `gprof`, is used to analyze the decoding C code on a desktop PC and Fig. 2.5 shows a partial profiling report. By the profiling report, we know that function `IMDCT32` is the bottleneck.

We now compare two implementations on the OMAP platform. The first implementation runs the whole C code by ARM925. The second uses DSP library to implement `IMDCT32` function. Figure 2.6 shows their resource utilization report. The upper part gives the first implementation report, showing that its CPU utilization rate is 40.0%. The lower part for the second implementation shows that its

```

Flat profile:

```

```

Each sample counts as 0.01 seconds.

% cumulative self      self      total

time    seconds    seconds    calls  us/call  us/call  name

38.64      0.34      0.34    14554    23.36    23.36  IMDCT32

14.77      0.47      0.13    2266    57.37    57.37  playingwiththread

6.82      0.53      0.06

5.68      0.58      0.05    13104     3.82     6.11  layer3fixtostereo

3.41      0.61      0.03    14554     2.06     2.06  extractlaver3

```

**Fig. 2.5** Profiling report

|                                                            |

|------------------------------------------------------------|

| 1:24am up 1:24, 1 user, load average: 0.92, 1.67, 1.48     |

| 17 processes: 15 sleeping, 2 running, 0 zombie, 0 stopped  |

| CPU states: 40.0% user, 3.7% system, 0.0% nice, 56.1% idle |

| Mem: 30672K av, 11856K used, 18816K free, 0K shrd, 0K buff |

| Swap: 0K av, 0K used, 0K free, 8680K cached                |

| 1:30am up 1:30, 1 user, load average: 2.60, 1.90, 1.46     |

| 17 processes: 13 sleeping, 4 running, 0 zombie, 0 stopped  |

| CPU states: 20.1% user, 79.8% system, 0.0% nice, 0.0% idle |

| Mem: 30672K av, 11784K used, 18888K free, 0K shrd, 0K buff |

| Swap: 0K av, 0K used, 0K free, 8680K cached                |

**Fig. 2.6** Resource utilization

CPU utilization rate is 20.1%. As shown, using a DSP can share CPU loading, thus improve performance for MP3 player application.

## 2.2 System Modeling

On platform-based design, the selection of platform is based on designer's experience. It is a fast way to implement a system, but does not guarantee that it is optimized.

At system level, we need to consider more about environment and user friendliness. Does the product need to work at the Sahara Desert or the North Pole? What human interface does a user prefer? If the bit error rate will become too high at some environment, should we add error correction policy? All these questions and solutions should be decided at system level before entering detailed design.

At system level, we need a model to describe function behavior of a system. This level of modeling targets for a unified representation for hardware and software, which contains the following features:

- (1) It can describe high level system architecture.

- (2) It is independent to the implementation of hardware and software.

- (3) It supports refinement for hardware/software partitioning.

- (4) It enables architecture exploration for hardware/software cross-fertilization.

- (5) It supports co-simulation environment for communication. And

- (6) It supports functional co-verification.

Using a unified representation, we can identify system bottleneck, evaluate performance, and calculate the cost of a hardware/software partitioning at early design stage.

For different purposes, many modeling methods have been introduced. They will be briefly introduced in the following subsections.

### 2.2.1 State-Oriented Models

The system temporal behavior of a machine can be represented as state transfer in a finite state machine. The state number of a real machine is finite. Two models are used to represent a finite state machine:

- (1) Mealy machine: The output is determined by current state and input.

- (2) Moore machine: The output is determined only by the state.

In circuit view, the input signals of a Moore machine are all buffered in internal state registers, and mealy machine allows input signals to pass to output by combination of states.

Finite state machine behavior is represented by state transfer chart. Figure 2.7 shows a simple example of Mealy machine model. Each node represents a state. Thus a 3-state machine requires 2 or 3 registers to implement the states, depending on timing and cost constraints. The arc between two states represents a state transfer, which is derived by an input signal which is attached on the arc. The output signal is also attached on the arc, which can be a datapath computation.

The state transfer chart is not suitable to represent hierarchy and concurrency. When two state machines are working concurrently, their state registers should be combined together, and the state number will increase exponentially. The size of the state transfer chart becomes soon explosive for a complex system.

Petri-net is a graphical and mathematical tool to provide a uniform environment for modeling, formal analysis, and design of discrete event systems [5]. It was named after Carl A. Petri who created the concept in 1962. Petri-net offers the ability to represent concurrency. Petri-net can be used to model properties, such as process synchronization, asynchronous events, concurrent operations, and conflicts or resource sharing. Petri-net is identified as a particular directed graph by three types of objects: *place*, *transition* and directed *arc*. *Place* represented as a circle is used for an operation. *Transition* is represented as a bar. *Arc* demonstrates state transfer

**Fig. 2.7** Mealy finite state machine

**Fig. 2.8** Petri-nets of two concurrent processes

and data node association. Data nodes, represented as rectangles and associated on transition, are used for the event trigger point and data dependency, which combine the control graph and data graph together. Decision branch modeled in Petri-net is a single *place* input to multiple competing *transitions*. Figure 2.8 shows a Petri-net example. It contains two concurrent processes, one has 5 states and another has 3 states. The two processes share variable Y and variable Z, they will affect each other.

### 2.2.2 Activity-Oriented Models

The *activity-oriented model* focuses on representing what tasks to do and their dependences, but it lacks of temporal information. Flow chart is a widely-used activity-oriented model. It is useful on control-oriented representation. Figure 2.9 shows an example.

*Control and Data Flow Graph* (CDFG) [6] is a widely-used intermediate representation in compiler. CDFG is the model for capturing design descriptions for compiler and high-level synthesis which work well for traditional scheduling and binding techniques.

CDFG retains high level information about code structures and semantics in terms of control flow graph (CFG) and data flow graph (DFG), which are often used in compilers. Control flow graphs (CFG) are used to handle code sequences. Each node in a CFG represents a basic block. Data flow graphs (DFG) maintain the data dependencies between operations. Control flow graph is transformed from the control structures in a code, such as `if-else` and `for-loop` control statements, for describing the code statement execution orders. Because of the sequential ingredient of most software languages, like C and C++, building a control flow graph from a sequential code is simply a direct mapping. Data flow graph is basically a

**Fig. 2.9** Flow chart

**Fig. 2.10 CDFG**

```

S1: t=a+b;

S2: u=a-b;

S3: if(a<b)

S4: v=t+c;

else

{

S5: w=u+c;

S6: v=w-d;

}

S7: x=v+e;

S8: y=f-e;

```

data dependence graph which nodes are operations and edges are data dependence relations. Figure 2.10(a) shows a code segment and Fig. 2.10(b) illustrates its control and data flow graphs. The solid rectangles represent basic blocks. A dashed arrow between basic blocks denotes a control flow and a solid arrow denote a data flow between operations.

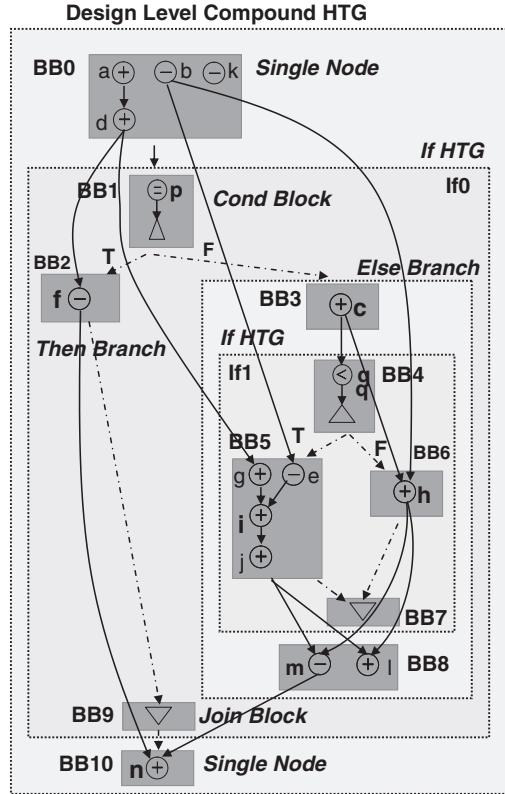

*Hierarchical Task Graph* (HTG) [7] is based on CDFG, maintaining the hierarchical structuring of a code such as `if-then-else` blocks, `for` and `while` loops. HTG extends the range of optimizations, especially beneficial to source-to-source optimization and other coarse-grain transformations. HTG also enables higher order manipulation, *e.g.*, coarse-grain code restructuring and operation moving across large pieces of code. A design HTG is constructed by creating a compound node corresponding to each control construct in the design. Figure 2.11 shows the nested `if-else` statements in terms of nested HTG forms.

The following paragraphs list the formal definition of an HTG.

A hierarchical task graph HTG is a hierarchy of directed acyclic graphs  $G_{HTG}$  ( $V_{HTG}$ ,  $E_{HTG}$ ), where the vertices  $V_{HTG} = \{htg_i | i = 1, 2, \dots, n_{htgs}\}$  can be one of the following three types.

- (1) Single nodes represent nodes that have no sub-nodes and are used to encapsulate basic blocks. Basic blocks are a sequential aggregation of operations that have no control flow (branches) between them.

- (2) Compound nodes are recursively defined as HTG, that is, they contain other HTG nodes. They are used to represent structures like `if-then-else` blocks, `switch-case` blocks or a series of HTG.

- (3) Loop nodes are used to represent the types of loops (`for`, `while-do`, `do-while`). Loop nodes consist of a loop head and a loop tail that are single nodes and a loop body that is a compound node.

The edge set  $E_{HTG}$  in  $G_{HTG}$  represents the flow of control between HTG nodes. An edge  $(htg_i, htg_j)$  in  $E_{HTG}$ , where  $htg_i, htg_j \in V_{HTG}$ , signifies that  $htg_j$  will be executed after  $htg_i$  has finished execution. Each node  $htg_i$  in  $V_{HTG}$  has two distinguished nodes,  $htg_{Start}(i)$  and  $htg_{Stop}(i)$ , belonging to  $V_{HTG}$  such that there exists a path from  $htg_{Start}(i)$  to every node in  $htg_i$  and a path from every node in  $htg_i$  to

**Fig. 2.11** Compound if-else statements in HTG form

$\text{htg}_{\text{Stop}}(i)$ . The  $\text{htg}_{\text{Start}}$  and  $\text{htg}_{\text{Stop}}$  nodes belonged to an HTG compound or loop node are always single nodes.

Actually, when the dotted rectangles in Fig. 2.11 are removed, the HTG diagram becomes a CDFG diagram. The basic blocks are shown by shaded boxes within the HTG nodes (BB0 to BB10) and operations are denoted by circular nodes with an operator symbol inside. Dashed lines denote control flow between HTG nodes. Solid lines denote data flow between operations. A fork in the control flow is denoted by a triangle ( $\Delta$ ) and a merge by an inverted triangle ( $\nabla$ ).

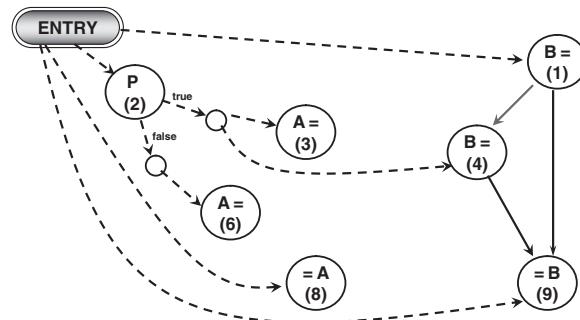

Program Dependence Graph (PDG) [8] represents a code in its original design concepts. PDG is another variant of the CDFG which relaxes the sequential flow restrictions. Figure 2.12 demonstrates the characteristics of PDG.

The dotted lines denote the control flow dependences, *e.g.*, the ENTRY node must go to node (2), then node (3). The solid lines denote the data dependences, *e.g.*, node (4) depends on node (1), and node (9) depends on nodes (1) and (4). There are two places worth notice in Fig. 2.12. Since the statements in lines (8) and (9) are counterparts of nodes (8) and (9), it is obvious to see that the entry nodes (3) and (4) respectively have a data dependence relation with nodes (8) and (9) because of the solid lines. The second place is the introduction of relation nodes under node (2) with two edges labeled T (True) and F (False), respectively. Relation nodes are used when a new basic block is encountered, *e.g.*, the nodes (3) and (4) create a

**Fig. 2.12** An example of PDG

new basic block. PDGs relieve the ordering property of CDFGs. There is no need to add ordering information in CDFGs. However, PDGs still need various compilation techniques to detect *true data dependences*. For instance, the data dependence edge between nodes (1) and (4) is an *output data dependence*, where nodes (1) and (4) write data to the same memory location, B.

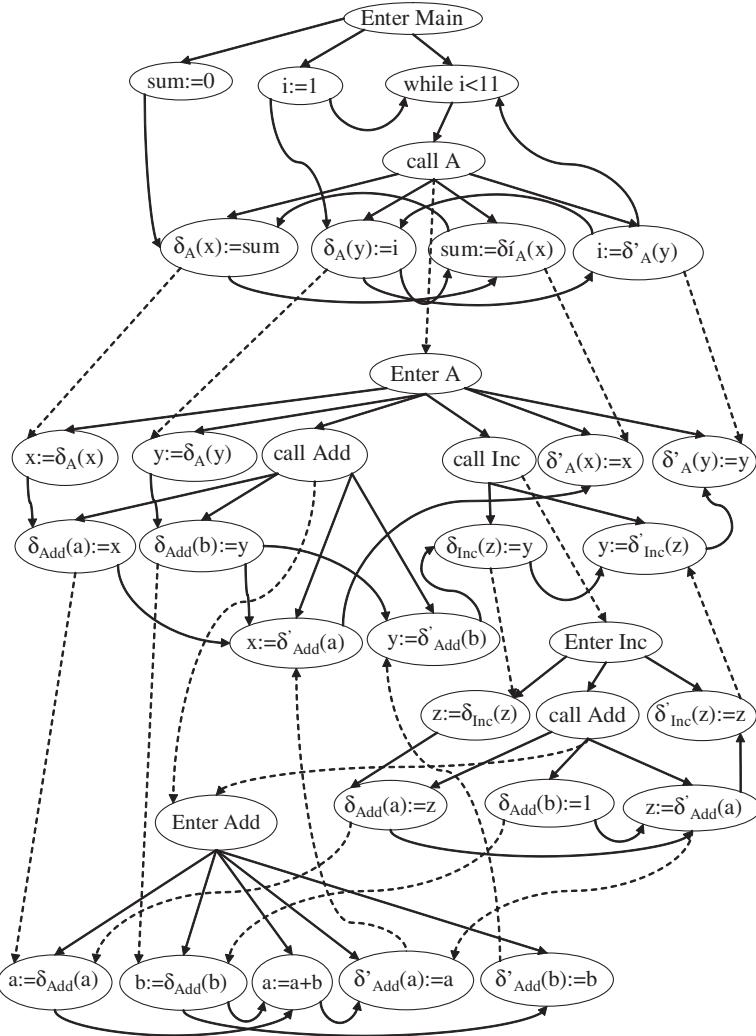

System Dependence Graph (SDG) [9] is an extension of PDG. It is designed to incorporate collections of procedures (with procedure calls) rather than just monolithic program codes. Figure 2.13 depicts an SDG example. The straight medium-bold edges represent the *control dependences*, e.g., the edges between the “ENTER Main” node and its three child nodes. The light solid arcs represent *flow dependences* of the source code, e.g., the arcs from node “ $i := 1$ ” to node “ $\text{while } i < 11$ ”. The heavy-bold arcs represent *transitive inter-procedural flow dependencies* (corresponding to subordinate characteristics graph edges), e.g., the arcs from node “ $\delta_A(x) := \text{sum}$ ” to node “ $\text{sum} := \delta'_A(x)$ ”. Dashed arrows represent call edges, linkage-entry edges, and linkage-exit edges.

## 2.3 Video Coding

H.264 advanced video coding (AVC) [10] is one of the latest international video coding standards. This standard is developed by the ITU-T Video Coding Experts Group and the ISO/IEC Moving Picture Experts Group. It can achieve higher coding efficiency than previous standards. The advantages of this new video coding standard H.264/AVC are its higher quality, less storage, less bandwidth, more robust transmission, easier random access, more kinds of manipulations and intelligent processing.

H.264/AVC is developed for the next generation application. It aims at not only video content compression but also video conferences, television broadcasting, and internet streaming. It is designed to replace all the past video standards in almost all kinds of applications. So, it defines different profiles to meet the various requirements in different applications. *Baseline Profile* is used in real-time communication applications and conversational services which are important for low latency and low bit stream size requirements. *Main Profile* is designed for the highest coding-efficient storage to use in entertainment video applications, such as satellite broad-

|                                                                                      |                                                                  |                                            |                                                  |

|--------------------------------------------------------------------------------------|------------------------------------------------------------------|--------------------------------------------|--------------------------------------------------|

| program Main<br>sum:=0;<br>i:=1;<br>while(i<11) do<br>call A(sum,i);<br>enddo<br>end | Procedure<br>A(x,y)<br>call Add(x,y);<br>call Inc(y);<br>return; | procedure<br>Add(a,b)<br>a:=a+b<br>return; | procedure<br>Inc(z)<br>call Add(z,1);<br>return; |

|--------------------------------------------------------------------------------------|------------------------------------------------------------------|--------------------------------------------|--------------------------------------------------|

Fig. 2.13 An example of SDG

casting, cable modem, and DVD players for standard and high definition video, *etc.* *Extended Profile* is defined for supporting services that operate at 50–1500 Kbps and have two seconds or more latency.

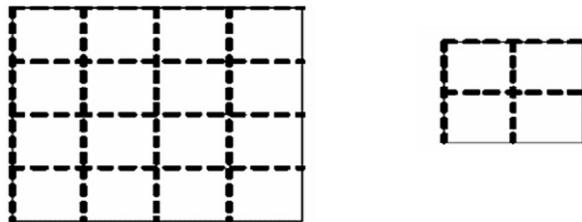

A picture in an H.264 video sequence could be partitioned into slices. The minimum number of slices in a picture is one. Slice is a collection of macroblocks which are processed in the order of a raster scan. The luminance and chrominance format defined in H.264 is YUV 4:2:2. So, a macroblock has one  $16 \times 16$  luma (Y) sample and two  $8 \times 8$  chroma (Cb, Cr) samples. A macroblock is the basic processing unit in H.264 coding process.

The video sequences in H.264 comprise 4 types of frames: I (Intra), P (Prediction), B (Bi-directional), and S (Switched) frames. *I frame* is a basic component in all H.264 profiles that uses intra coding to remove spatial redundancy. *P frame* is also a basic frame in all profiles, but it uses inter prediction method to predict its values from previous encoded P and I frames to remove temporal redundancy. *B frame* is used in Main profile and Extended profile. It uses both forward and backward motion compensations as inter prediction to achieve higher compression rate than other frames. *S frame* is a new frame type introduced by H.264 only and used in an Extended profile. This new frame is used for efficient switching between two different bitstreams.

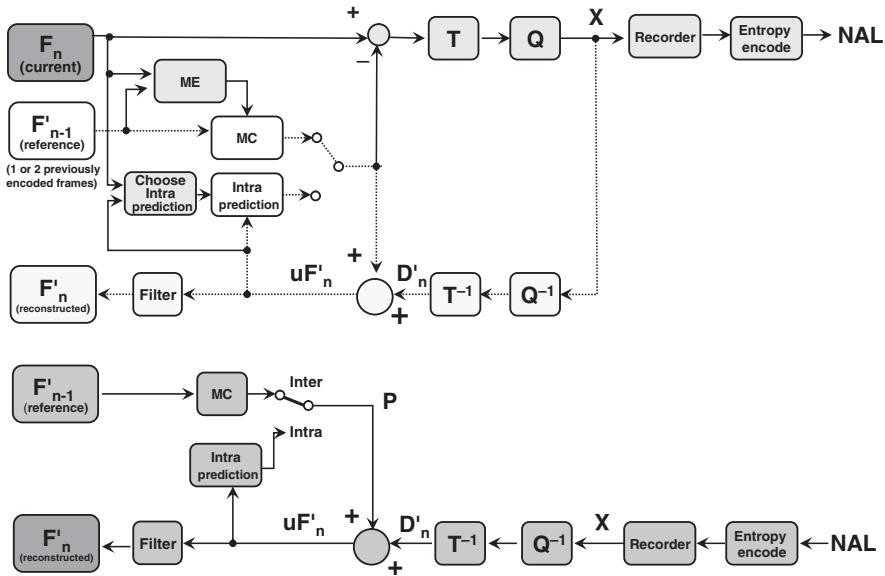

### 2.3.1 H.264 Coding Process

A typical H.264 *coding process* is shown in Fig. 2.14. When encoding a picture, we first split the picture into  $16 \times 16$  macroblocks (MBs). Each of the  $16 \times 16$  MBs is a basic process unit in the encoding scheme. Once a MB is encoded, the encoder will predict what the MB should be. The MB data is divided by a prediction value. Then the residual data is processed by transform (T) and quantization (Q). After quantization, the data can be encoded by an entropy encoder to compress the data size and sent to the decoder. To be consistent with the decoder, prediction is done by referring to a reconstructed picture, not the original picture. The reconstruction is built from the quantization data by inverse quantization and inverse transformation, and adding the prediction value to recover the picture. Based on this reconstructed picture, the encoder can further do prediction for the next MB from performing intra prediction for the MB in the same frame, or motion estimation from the past decoded pictures. Thus the encoding process can be completed in such a loop process.

The *decoding process* is similar to the reconstruction process, but adding an entropy decoding stage before inverse quantization.

### 2.3.2 Motion Estimation

*Motion Estimation* finds the best matching candidate block between a current macroblock and its reference frames in a search window. It can efficiently reduce the

Fig. 2.14 H.264 coding process

temporal redundancies. With motion estimation, we can promote the bit rate effectively by transferring the motion vectors of a MB. Thus, motion estimation is one of the most important functions in many video coding standards. In H.264/AVC, the standard supports multiple reference frames in order to find the objects which appear suddenly. Besides, it also supports variable block sizes coding in matching blocks. Although these two functions indeed increase the coding gain, both of them will greatly increase the computational complexity with the comparison of previous standards which only support one or two reference frames and only one fixed MB size.

The selected frames for prediction are indicated by a reference index which is associated with the frame index in the buffer. The process of encoding which is based on the values predicted to form the best matching candidate block is called *motion compensation*. When the best matching candidate block is found, it will be used to form a reference frame to be pasted on the current frame. Then, a vector called *motion vector* can be drawn from the reference frame.

If an encoder wants to transfer a block data in Frame  $t$ , there are two ways to get it. (1) Let the encoder transfer all pixels of this block to decoder. (2) Since there is not much difference between Frame  $t$  and Frame  $t-1$ , and the data of Frame  $t-1$  had already reconstructed by a decoder and is stored in the buffer, we can take Frame  $t-1$  as a reference and exploit the data of Frame  $t-1$  in the decoder buffer. Thus, we just need some information, the motion vector, to construct the Frame  $t$ .

There are many criteria used to judge the best matching block. One of the most widely used criteria is *sum of absolute differences* (SAD). The function of SAD is

shown as:

$$SAD(m, n) = \sum_{i=0}^{N-1} \sum_{j=0}^{N-1} |C(i, j) - R(i + m, j + n)|,$$

where  $(m, n)$  is the distance of the candidate block corresponding to coding block C at position  $(i, j)$ , and  $N$  is the macroblock size. H.264/AVC defines the maximum of  $(m, n)$  as *search range* for different levels. The *motion vector MV* is defined as:

$$MV = \arg \min_{(m,n) \in \text{search range}} SAD(m, n).$$

H.264/AVC supports seven block size modes ( $16 \times 16$ ,  $16 \times 8$ ,  $8 \times 16$ ,  $8 \times 8$ ,  $8 \times 4$ ,  $4 \times 8$ , and  $4 \times 4$ ). And H.264/AVC allows 10 reference frames in each single direction (forward/backward). This property is different from the prior standard like MPEG-2, which used only one previous picture to compensate.

A  $16 \times 16$  macroblock is a basic process unit in a coding loop. In the inter prediction, we will test if a macroblock is suitable to be predicted in  $16 \times 16$ ,  $16 \times 8$ ,  $8 \times 16$ , or  $8 \times 8$  size. If the most suitable size is  $8 \times 8$ , it can be further segmented into  $8 \times 4$ ,  $4 \times 8$ , or  $4 \times 4$  blocks for motion estimation. By the variable block sizes, we must compute up to 41 modes of motion vectors, as shown in Fig. 2.15.

Most prior standards allow half-sample motion vector accuracy at most. H.264 improves on this by adding quarter-sample motion vector accuracy. With this precise accuracy, the quality will be improved effectively. After integer pixel motion estimation is done. The neighbor pixels will be used to interpolate the half pixels and quarter pixels values, and then do the same ME operations to find out the best matching motion vector.

The motion vector mentioned above is defined for luma motion vector. And the motion vector of the chroma parts can be derived from the luma one. Since the size of a luma vector resolution is twice as large as the chroma vector, the chroma vector can be obtained by dividing the corresponding luma vector by two. Since the accuracy of the luma motion vectors is 1/4 sample pixel, and the chroma is half resolution of luma, thus the chroma motion vector accuracy is 1/8 sample pixel.

Fig. 2.15 Variable block size and segmented macroblock

To get best MV, we should evaluate all distances ( $m, n$ ) and 41 modes. The computation effort is very high. Many speedup implementations for motion estimation had been introduced.

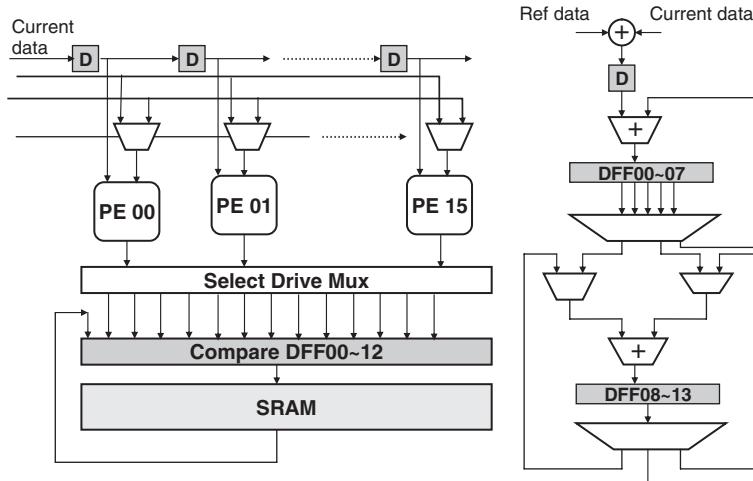

In hardware implementation, the goal is to compute 41 motion vectors concurrently. Figure 2.16 is an 1-D implementation example [11]. Another 2-D systolic array implementation can be found in [12, 13]. In the 1-D architecture, the current data are fed to each processing element (PE) by 16 registers, and the reference data 0 and data 1 are separately fed to each PE. Thus, the SAD value of 16  $4 \times 4$  blocks can be computed concurrently by the 16 PEs. The reference data which motion vector (0,0) needs are not the same with the motion vector (15,0). Thus, the reference data input to each PE needs to be well scheduled. It is implemented using two SRAMs with two broadcasting buses.

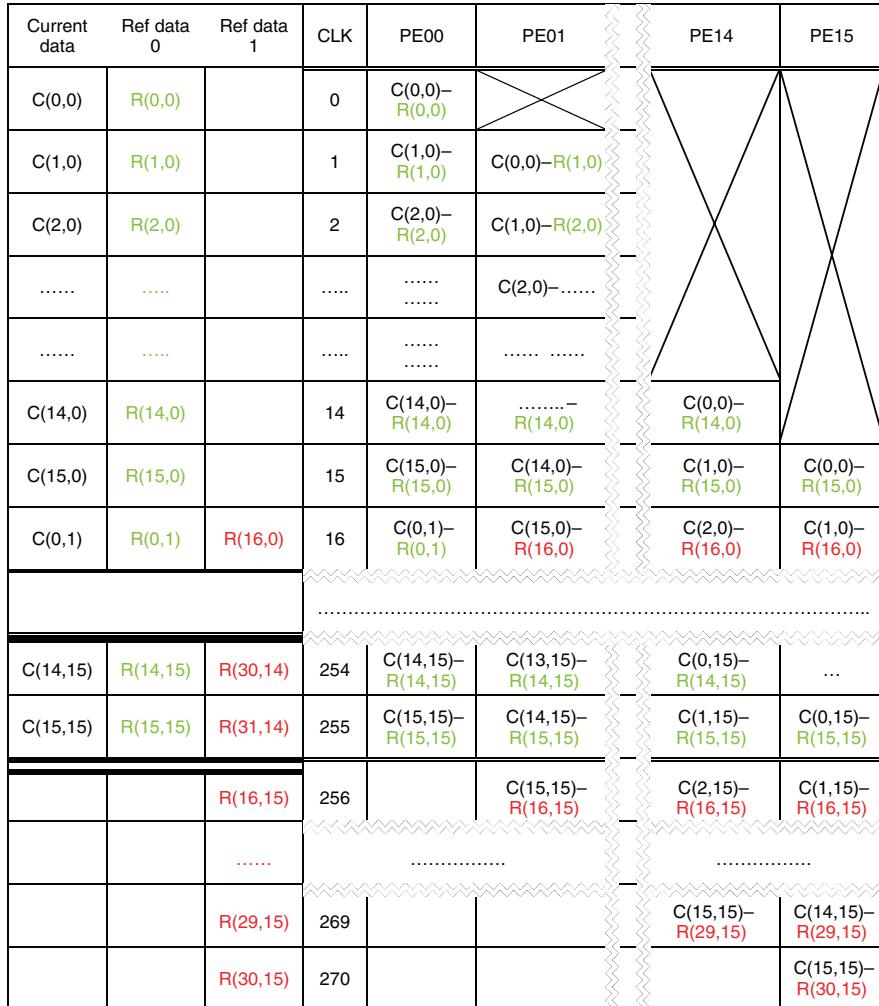

Figure 2.17 shows the schedule of data input for each PE, where C represents the current data, R represents the reference data, and vectors (0, 0) to (31, 15) represent their corresponding positions. For every PE,  $C(0, 0)$  to  $C(15, 15)$  are needed to compare the difference of every pixel in a  $16 \times 16$  current macroblock. On the contrast, the reference data of different motion vectors are not the same. For PE00, the required reference data are  $R(0, 0)$  to  $R(15, 15)$  to calculate motion vector (0, 0). For PE01, the required reference data are  $R(1, 0)$  to  $R(16, 15)$  to calculate motion vector (1, 0). We can see that many of the required reference data are the same when motion vectors (0, 0) and (1, 0) are calculated, such that we can first feed  $R(0, 0)$  to  $R(15, 0)$  in Ref data 0 at the first 16 clocks. When  $R(0, 1)$  in Ref data 0 is required by PE00 at the 17th clock,  $R(16, 0)$  is fed to Ref data 1 which is required by other PEs at the same time. In such schedule, we can compute 16 motion vectors concurrently. Every PE completely receives data in successive cycles. If the search range is  $[-8, +7]$ , we can set the PE00 to compute  $(-8, -8)$  to  $(-8, +7)$ , PE01 to

Fig. 2.16 1-D motion estimation architecture

**Fig. 2.17** Schedule of data input for each PE

compute  $(-7, -8)$  to  $(-7, +7)$ , PE02 to compute  $(-6, -8)$  to  $(-6, +7)$ , and so on, and finally PE15 to compute  $(+7, -8)$  to  $(+7, +7)$ . The motion vectors, which are computed by the same PE, are just different in  $V_y$  but the same in  $V_x$ . After the SAD of a specific motion vector is computed individually by each PE, the outputs of PEs should be compared for selecting the minimum one as the result of motion estimation. In this architecture, the comparison is implemented by 13 DFFs. The SAD values of larger block size can be composed of the 16  $4 \times 4$  blocks.

In software implementation, the purpose is to reduce search point. That will get a sub-optimal solution. It is a trade-off between computation time and compression

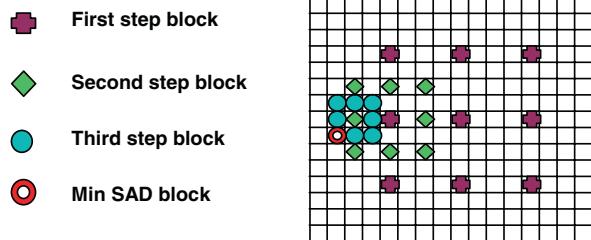

rate. Many algorithms had been introduced, including three-step search, diamond search, modified spiral search, *etc.*

Figure 2.18 shows the concept of a *three-step search*. For a search range of  $\pm 6$ , the first step searches nine  $(m, n)$  points, for  $m, n = \{0, 4, -4\}$ , then selects the point  $(m_1, n_1)$  which SAD is minimum. The second step searches the other nine  $(m_1 + a, n_1 + b)$  points, for  $a, b = \{0, 2, -2\}$  and selects the point  $(m_2, n_2)$  which SAD is minimum. The third step searches the nine  $(m_2 + c, n_2 + d)$  points, for  $c, d = \{0, 1, -1\}$ , and the point  $(m_3, n_3)$  which SAD is minimum will be the solution. Compared to the total 169 points, 85% of the computation time is saved.

**Fig. 2.18** Three-step search

### 2.3.3 Intra Prediction

*Intra prediction* is used to reduce spatial redundancies. H.264 intra coding uses values of neighbor blocks in a current picture frame to encode a coding block. It is the major reason that makes H.264 intra coding have the highest coding efficiency than any other existing video coding standards. There are two intra prediction types for luminance samples, INTRA\_4×4 and INTRA\_16×16, and one intra prediction type defined for chrominance samples, INTRA\_CHROMA.

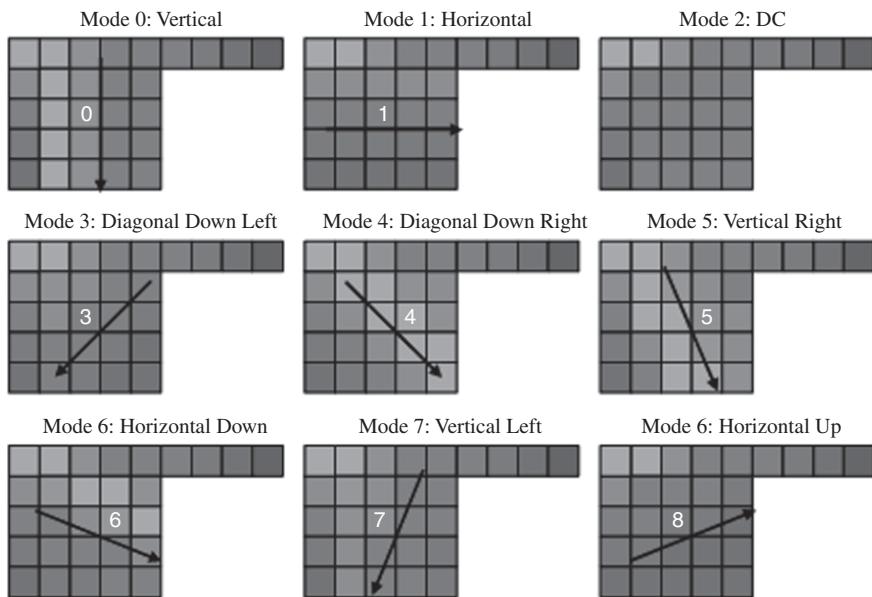

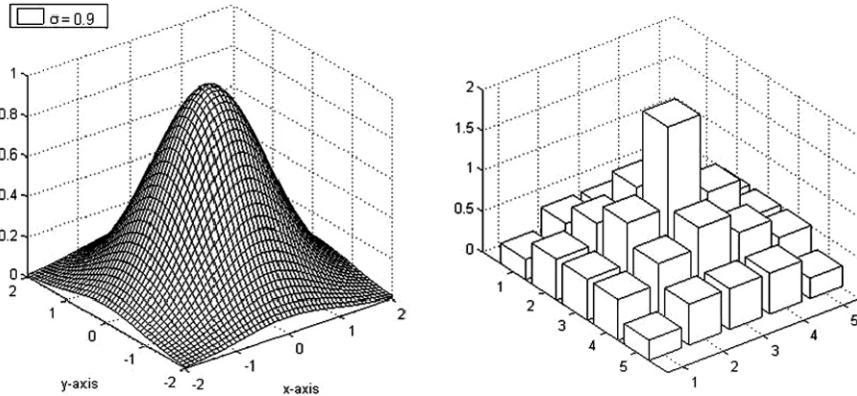

In the INTRA\_4×4 prediction type, nine prediction modes are defined. One of them is the DC mode representing the mean of neighboring pixels. Others describe the eight possible prediction directions. Each 4×4 block of a luminance sample in a MB can choose one of the nine modes. In Fig. 2.19, the luminance samples labeled as  $a$  to  $p$  in the prediction block are calculated based on the neighboring samples labeled as  $A$  to  $L$  and  $Q$ . The neighboring samples come from previously coded blocks. And they will be partitioned into four subgroups. Upper-side neighboring samples include  $A, B, C$  and  $D$ . Left-side samples include  $I, J, K$  and  $L$ . Upper-left side has only a  $Q$  sample. Upper-right side samples include  $E, F, G$  and  $H$ . If some of these neighboring samples are not available, the prediction mode using these samples will be skipped.

An illustration of nine prediction modes in INTRA\_4×4 is presented in Fig. 2.20. Mode 0 is predicted from upper neighboring samples. Mode 1 is predicted from left boundary samples. Modes 3 and 7 will be calculated when the upper and upper-right

**Fig. 2.19** INTRA\_4×4 prediction neighbors

| Q | A | B | C | D | E | F | G | H |

|---|---|---|---|---|---|---|---|---|

| I | a | b | c | d |   |   |   |   |

| J | e | f | g | h |   |   |   |   |

| K | i | j | k | l |   |   |   |   |

| L | m | n | o | p |   |   |   |   |

neighboring samples are available. Modes 4, 5 and 6 are interpolated from the upper, upper-left, and left neighboring samples. Mode 8 is a candidate of INTRA\_4×4 prediction mode when the left-side neighboring samples are available. DC prediction mode takes the average value of the available neighboring samples on the upper and left sides. If both the upper and left sides neighboring samples are not available, DC prediction will be given a prediction value of 128.

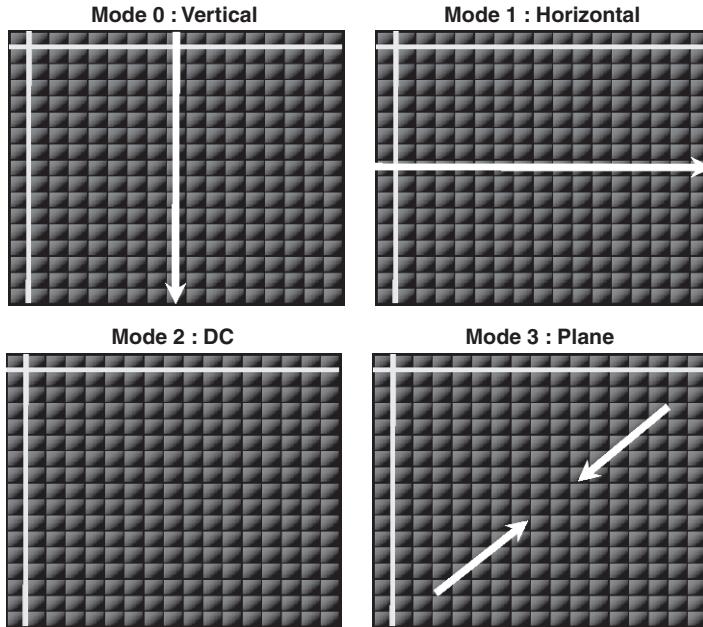

An illustration of four prediction modes in INTRA\_16×16 is presented in Fig. 2.21. Mode 0 in INTRA\_16×16 is used for vertical prediction. Mode 1 is for

**Fig. 2.20** INTRA\_4×4 prediction modes

**Fig. 2.21** INTRA<sub>16</sub>×16 prediction modes

horizontal prediction. Mode 2 is for DC prediction. And Mode 3 predicts by the average value of H and V neighboring samples.

The two chrominance components, Cb and Cr, use the same prediction mode. The INTRA\_CHROMA prediction type is like INTRA<sub>16</sub>×16, but with a block size of 8×8.

### 2.3.4 Transform and Quantization

In H.264, *transform* and *quantization* operations are designed for low hardware implementation cost. Shift, addition and subtraction are major operations adopted in H.264. And multiplication operations only appear in quantization and de-quantization stages. The division operation with high hardware implementation cost is avoided in this standard.

H.264 adopts a DCT-like integer transform instead of standards DCT transform commonly used in previously approved video coding standards. The proposed transform has an inverse transform fully defined in integer arithmetic and do not have data drift problem caused by floating-point arithmetic and rounding process. The formula of *integer forward transform* can be written as following equation where  $\otimes$  denotes element-by-element multiplication.

$$\begin{aligned}

Y &= (CXC^T) \otimes E_{forw} \\

&= \begin{bmatrix} 1 & 1 & 1 & 1 \\ 2 & 1 & -1 & -2 \\ 1 & -1 & -1 & 1 \\ 1 & -2 & 2 & -1 \end{bmatrix} \begin{bmatrix} x_{00} & x_{01} & x_{02} & x_{03} \\ x_{10} & x_{11} & x_{12} & x_{13} \\ x_{20} & x_{21} & x_{22} & x_{23} \\ x_{30} & x_{31} & x_{32} & x_{33} \end{bmatrix} \begin{bmatrix} 1 & 2 & 1 & 1 \\ 1 & 1 & -1 & -2 \\ 1 & -1 & -1 & 2 \\ 1 & -2 & 1 & -1 \end{bmatrix} \\

&\otimes \begin{bmatrix} a^2 & \frac{ab}{2} & a^2 & \frac{ab}{2} \\ \frac{ab}{2} & \frac{b^2}{4} & \frac{ab}{2} & \frac{b^2}{4} \\ a^2 & \frac{ab}{2} & a^2 & \frac{ab}{2} \\ \frac{ab}{2} & \frac{b^2}{4} & \frac{ab}{2} & \frac{b^2}{4} \end{bmatrix}

\end{aligned}$$

This equation could be divided into two parts. The first part is a butterfly-based matrix multiplication in which matrix  $C$  contains coefficients of  $\pm 1$  and  $\pm 2$  only. A multiplication by  $\pm 2$  can be implemented as a left shift and an addition/subtraction. So, the matrix multiplication does not really need a multiplier. The second part operation is to scale the result of the first part operation. There are only three scaling factors in  $E_{forw}$  which can be absorbed by quantization operation. So the final definition of forward transform in H.264 is only the first part of this equation.

The *inverse transform* is described in the following equation. The scaling matrix  $E_{inv}$  can also be merged into the de-quantization operation. The final proposed inverse transform is  $X' = C_i Y' C_i^T$  and the operations in inverse transform need only right shift and addition/subtraction.

$$\begin{aligned}

X' &= C_i (Y'' \otimes E_{inv}) C_i^T \\