Lecture Notes in Electrical Engineering 346

Khaled Khalaf Vojkan Vidojkovic Piet Wambacq John R. Long

# Data Transmission at Millimeter Waves

Exploiting the 60 GHz Band on Silicon

### Lecture Notes in Electrical Engineering

#### Volume 346

#### **Board of Series editors**

Leopoldo Angrisani, Napoli, Italy Marco Arteaga, Coyoacán, México Samarjit Chakraborty, München, Germany Jiming Chen, Hangzhou, P.R. China Tan Kay Chen, Singapore, Singapore Rüdiger Dillmann, Karlsruhe, Germany Haibin Duan, Beijing, China Gianluigi Ferrari, Parma, Italy Manuel Ferre, Madrid, Spain Sandra Hirche, München, Germany Faryar Jabbari, Irvine, USA Janusz Kacprzyk, Warsaw, Poland Alaa Khamis, New Cairo City, Egypt Torsten Kroeger, Stanford, USA Tan Cher Ming, Singapore, Singapore Wolfgang Minker, Ulm, Germany Pradeep Misra, Dayton, USA Sebastian Möller, Berlin, Germany Subhas Mukhopadyay, Palmerston, New Zealand Cun-Zheng Ning, Tempe, USA Toyoaki Nishida, Sakyo-ku, Japan Bijaya Ketan Panigrahi, New Delhi, India Federica Pascucci, Roma, Italy Tariq Samad, Minneapolis, USA Gan Woon Seng, Nanyang Avenue, Singapore Germano Veiga, Porto, Portugal Haitao Wu, Beijing, China Junjie James Zhang, Charlotte, USA

#### About this Series

"Lecture Notes in Electrical Engineering (LNEE)" is a book series which reports the latest research and developments in Electrical Engineering, namely:

- Communication, Networks, and Information Theory

- Computer Engineering

- Signal, Image, Speech and Information Processing

- Circuits and Systems

- Bioengineering

LNEE publishes authored monographs and contributed volumes which present cutting edge research information as well as new perspectives on classical fields, while maintaining Springer's high standards of academic excellence. Also considered for publication are lecture materials, proceedings, and other related materials of exceptionally high quality and interest. The subject matter should be original and timely, reporting the latest research and developments in all areas of electrical engineering.

The audience for the books in LNEE consists of advanced level students, researchers, and industry professionals working at the forefront of their fields. Much like Springer's other Lecture Notes series, LNEE will be distributed through Springer's print and electronic publishing channels.

More information about this series at http://www.springer.com/series/7818

Khaled Khalaf · Vojkan Vidojkovic Piet Wambacq · John R. Long

## Data Transmission at Millimeter Waves

Exploiting the 60 GHz Band on Silicon

Khaled Khalaf SSET-CSI IMEC Leuven Belgium

Vojkan Vidojkovic SSET-CSI IMEC Leuven Belgium Piet Wambacq SSET-CSI IMEC Leuven Belgium

John R. Long Faculty of EEMCS Delft University of Technology CD Delft The Netherlands

ISSN 1876-1100 ISSN 1876-1119 (electronic) Lecture Notes in Electrical Engineering ISBN 978-3-662-46937-8 ISBN 978-3-662-46938-5 (eBook) DOI 10.1007/978-3-662-46938-5

Library of Congress Control Number: 2015936687

Springer Heidelberg New York Dordrecht London © Springer-Verlag Berlin Heidelberg 2015

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made.

Printed on acid-free paper

Springer-Verlag GmbH Berlin Heidelberg is part of Springer Science+Business Media (www.springer.com)

## Acknowledgments

This work was fulfilled as a result of a cooperative research project between the TU Delft Electronics and IMEC wireless research groups. So, I would like to thank all those who helped me in bringing this work to life. I'd like to thank my advisors, Profs. John Long and Piet Wambacq, for their valuable guidance and discussions, and for making such cooperation possible. Special thanks to my direct supervisor, Vojkan Vidojkovic, for his constant support and continuous technical and un-technical discussions during my period at IMEC. I'd like to thank Bertrand Parvais, Kuba Raczkowski, Kristof Vaesen, Charlotte Soens, Viki Szortyka, Giovanni Mangraviti, Karen Scheir, and Julien Ryckaert for all their help, guidance, and fruitful discussions at IMEC. I'd like also to thank Roeland Vandebriel for the IO ring implementation. Thanks are extended to all who shared their thoughts and helped me in TU Delft including Yanyu Jin, Mina Danesh, Hakan Cetinkaya, and Antoon Frehe. I'd like to acknowledge all my professors at TU Delft including Leo de Vreede and Klaas Bult for their encouraging and valuable course contents, and all my classmates and friends in Delft who made it easier for me staying in that period just studying! I appreciate the efforts of all my friends in Leuven that were continuously supporting me in the good and bad times. I've to express deep thanks to my friends in Germany who actually encouraged me in continuing my postgraduate studies regardless of all the difficulties that I was facing. I'd like also to send deep regards to my bachelor staff members in Ain Shams University who guided me through such an interesting research and career path. I'd like to thank Alaa Medra for helping me finishing this book. No words can express acknowledging my family who did all what they can to help me achieving my goals, especially my wife and little kids for giving me a lot of "their" time to use in this book.

## Contents

| 1 | Intr | oduction                                  |

|---|------|-------------------------------------------|

|   | 1.1  | Motivation                                |

|   | 1.2  | 60 GHz Area Background                    |

|   |      | 1.2.1 Standards and Frequency Plan 2      |

|   |      | 1.2.2 Beamforming and System Architecture |

|   |      | 1.2.3 Enabling Technology 5               |

|   |      | 1.2.4 Applications                        |

|   | 1.3  | Book Objectives                           |

|   | 1.4  | Organization of the Following Chapters    |

|   | Refe | rences                                    |

|   |      |                                           |

| 2 | Bac  | kground                                   |

|   | 2.1  |                                           |

|   |      | 2.1.1 VCO Basics                          |

|   |      | 2.1.2 Main Parameters 11                  |

|   |      | 2.1.3 Phase Noise Origins                 |

|   |      | 2.1.4 Quadrature VCO                      |

|   | 2.2  | LO Buffer                                 |

|   | 2.3  | Frequency Divider                         |

|   |      | 2.3.1 ILFD 25                             |

|   |      | 2.3.2 Static Divider 28                   |

|   | 2.4  | LNA                                       |

|   |      | 2.4.1 NF and IIP3 31                      |

|   |      | 2.4.2 LNA Topology 33                     |

|   | 2.5  | Mixer                                     |

|   |      | 2.5.1 Main Parameters                     |

|   |      | 2.5.2 Mixer Topology                      |

|   | Refe | a co                                      |

| 3 | Desi | ign and             | I Simulation Results          |

|---|------|---------------------|-------------------------------|

|   | 3.1  | f <sub>T</sub> of t | the 90 Nm NMOS Transistor 41  |

|   | 3.2  | Passiv              | re Elements                   |

|   |      | 3.2.1               | Varactors                     |

|   |      | 3.2.2               | Transmission Lines 43         |

|   |      | 3.2.3               | Inductors                     |

|   |      | 3.2.4               | Transformers                  |

|   | 3.3  | QVCC                | D and LO Buffer 46            |

|   |      | 3.3.1               | Circuit Schematic             |

|   |      | 3.3.2               | Circuit Operation             |

|   |      | 3.3.3               | Design Guidelines             |

|   |      | 3.3.4               | Design Values                 |

|   |      | 3.3.5               | Simulation Results of P-QVCO  |

|   |      | 3.3.6               | Simulation Results of BS-QVCO |

|   |      | 3.3.7               | Performance Summary 63        |

|   | 3.4  | Divide              | er Chain                      |

|   |      | 3.4.1               | Circuit Schematic             |

|   |      | 3.4.2               | ILFD Locking Range 65         |

|   |      | 3.4.3               | Design Guidelines             |

|   |      | 3.4.4               | Design Values                 |

|   |      | 3.4.5               | Simulation Results            |

|   |      | 3.4.6               | Performance Summary 74        |

|   | 3.5  | LNA                 | and Mixer                     |

|   |      | 3.5.1               | Circuit Schematic             |

|   |      | 3.5.2               | Design Guidelines             |

|   |      | 3.5.3               | Design Values                 |

|   |      | 3.5.4               | Simulation Results            |

|   |      | 3.5.5               | Performance Summary 81        |

|   | Refe | erences             |                               |

|   |      |                     |                               |

| 4 | Тор  |                     | <b>Design</b>                 |

|   | 4.1  |                     | lete Top-Level Circuit        |

|   |      | 4.1.1               | Circuit Schematic             |

|   |      | 4.1.2               | Design Choices 83             |

|   |      | 4.1.3               | Design Values                 |

|   |      | 4.1.4               | Simulation Results            |

|   | 4.2  | QVCC                | D and Divider Sub-system8787  |

|   |      | 4.2.1               | Circuit Schematic             |

|   |      | 4.2.2               | Design Choices 87             |

|   |      | 4.2.3               | Design Values 89              |

|   |      | 4.2.4               | Simulation Results            |

|   | Refe | erence .            |                               |

| 5  | Lay   | out and Post-layout Simulations | 95  |

|----|-------|---------------------------------|-----|

|    | 5.1   | Physical Layout                 | 95  |

|    | 5.2   | Nominal Simulation Result       | 95  |

|    |       | 5.2.1 Divider                   | 97  |

|    |       | 5.2.2 QVCO and LO Buffer        | 98  |

|    | 5.3   | PVT Simulations                 | 100 |

| 6  | Con   | clusions                        | 103 |

|    | 6.1   | Summary                         | 103 |

|    | 6.2   | Future Work                     | 104 |

|    | Refe  | rence                           | 105 |

| Tr | ansfo | rmer-Coupled Buffer             | 107 |

## Figures

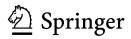

| Atmospheric propagation attenuation versus              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| frequency                                               | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

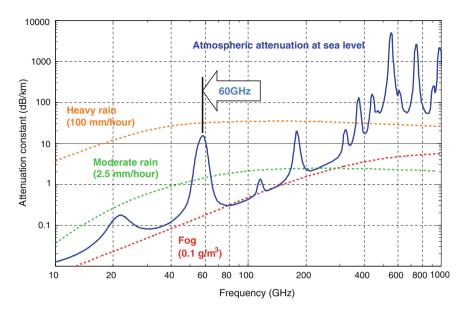

| 57-66 GHz band divided into 4 channels                  | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

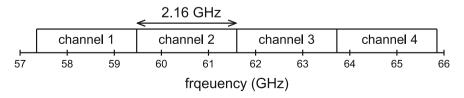

| Radiation pattern of a beamformer                       | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

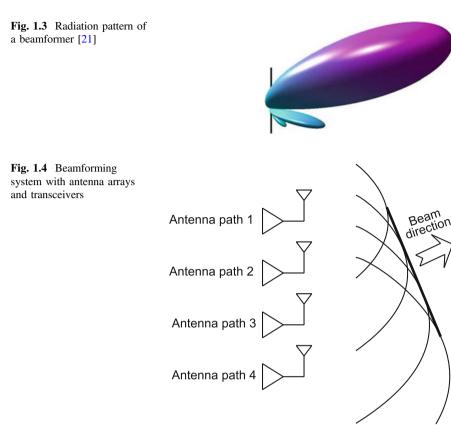

| Beamforming system with antenna arrays                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| and transceivers                                        | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

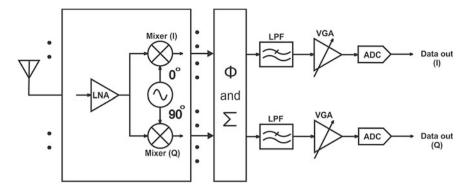

| 60 GHz receiver architecture                            | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 60 GHz potential indoor applications                    | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

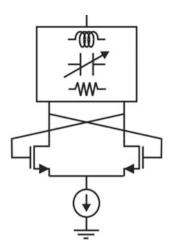

| Cross-coupled LC VCO                                    | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

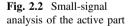

| Small-signal analysis of the active part                | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

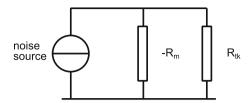

| Oscillator negative resistor model.                     | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

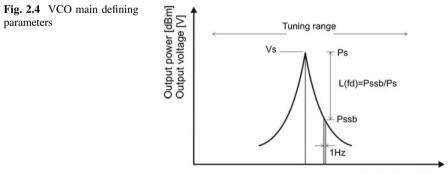

| VCO main defining parameters                            | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

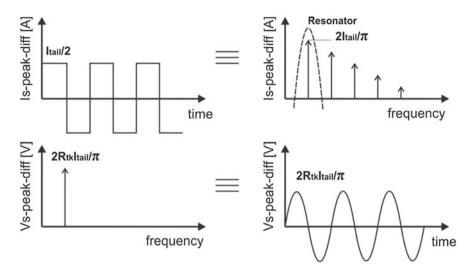

| Conversion from square wave current to sinusoidal       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| output voltage through filtering by the resonator       | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

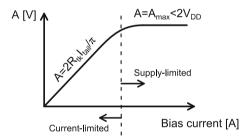

| Oscillator output differential amplitude based          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| on the operation of the tail current transistor         | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

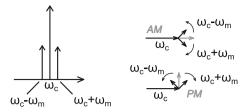

| Sidebands can be seen as AM and/or PM signals           | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Down conversion of unwanted frequency bands             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| due to oscillator spectral impurity                     | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

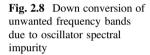

| Phase noise spectrum in dBc/Hz                          | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

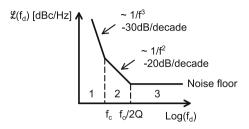

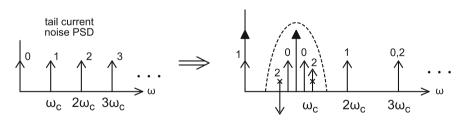

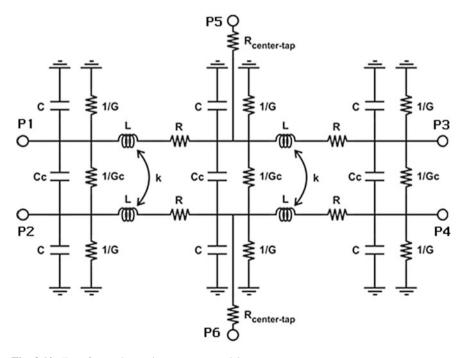

|                                                         | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Tail noise mixing with the cross-coupled pair           | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

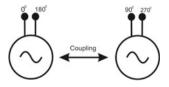

| Orthogonal signal out of the QVCO                       | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

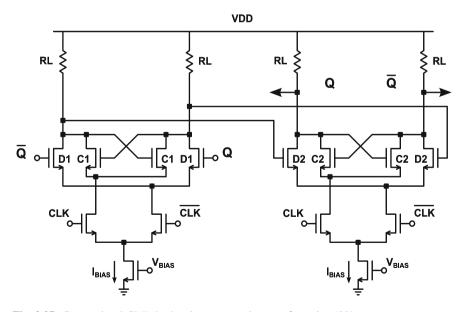

| Parallel QVCO (P-QVCO) topology                         | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| P-QVCO with gate decoupling and external bias           | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

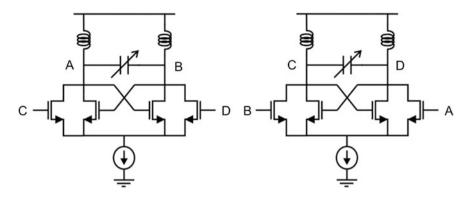

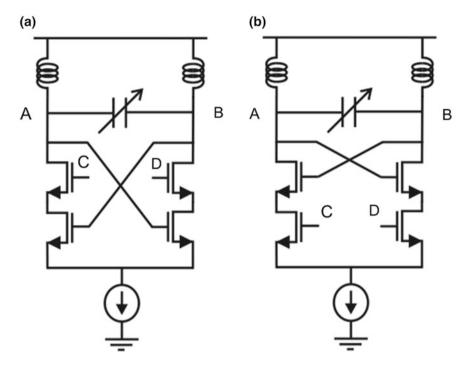

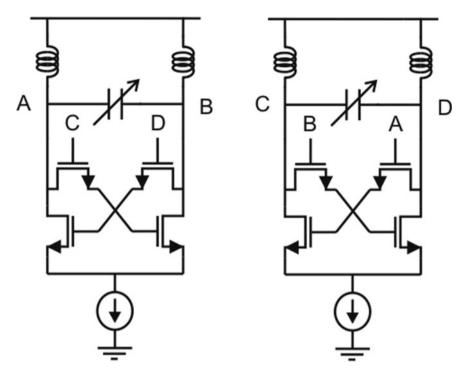

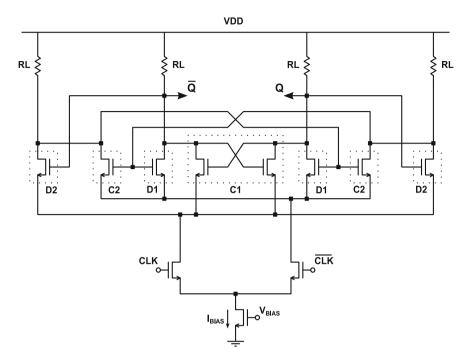

| Half-sections of series-QVCO in a top (TS-QVCO)         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| and <b>b</b> bottom (BS-QVCO) configurations            | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

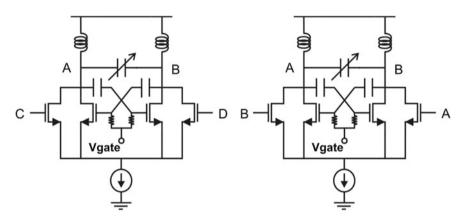

| Gate-modulated QVCO (GM-QVCO) architecture              | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

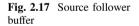

| Source follower buffer                                  | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Inductively-tuned CS differential amplifier as a buffer | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

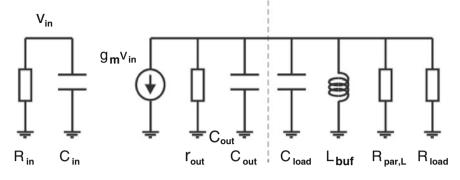

| Model of the active buffer                              | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

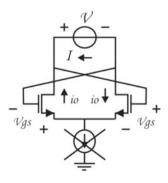

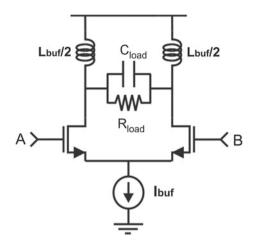

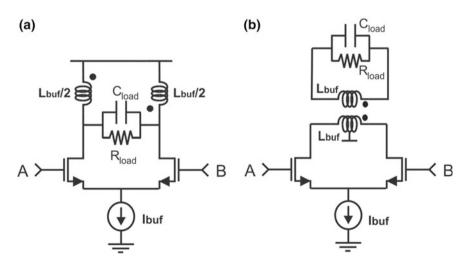

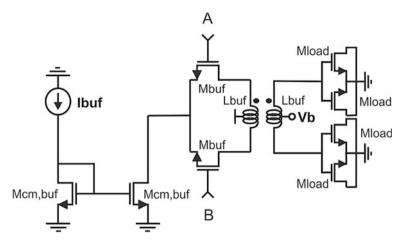

| Active buffer with transformer load a voltage           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| output <b>b</b> current output                          | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                         | 57-66 GHz band divided into 4 channels         Radiation pattern of a beamformer         Beamforming system with antenna arrays         and transceivers         60 GHz receiver architecture         60 GHz potential indoor applications         60 GHz potential indoor applications         cross-coupled LC VCO         Small-signal analysis of the active part         Oscillator negative resistor model.         VCO main defining parameters         Conversion from square wave current to sinusoidal         output voltage through filtering by the resonator         Oscillator output differential amplitude based         on the operation of the tail current transistor         Sidebands can be seen as AM and/or PM signals         Down conversion of unwanted frequency bands         due to oscillator spectral impurity         Phase noise spectrum in dBc/Hz         Noise folding due to cross-coupled pair         Tail noise mixing with the cross-coupled pair         Orthogonal signal out of the QVCO         Parallel QVCO (P-QVCO) topology         P-QVCO with gate decoupling and external bias         Half-sections of series-QVCO in <b>a</b> top (TS-QVCO)         and <b>b</b> bottom (BS-QVCO) configurations         Gate-modulated QVCO (GM-QVCO) architecture         Source follower buffer <t< td=""></t<> |

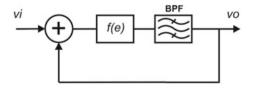

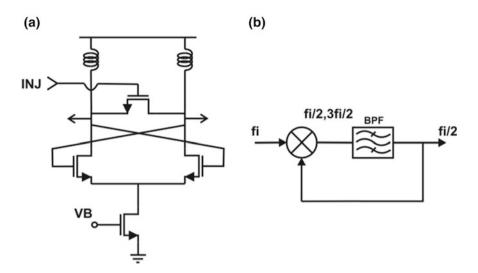

| Fig. 2.21              | Harmonic injection (injection-locked) frequency divider model         | 25       |

|------------------------|-----------------------------------------------------------------------|----------|

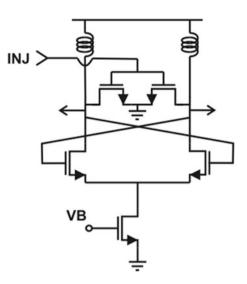

| Fig. 2.22              | Conventional ILFD                                                     | 25       |

| Fig. 2.22              | Direct ILFD <b>a</b> circuit schematic and <b>b</b> equivalent        | 20       |

| 11g. 2.23              | model                                                                 | 27       |

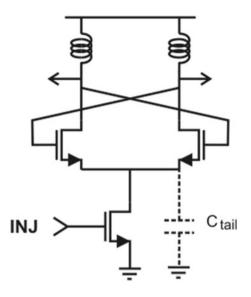

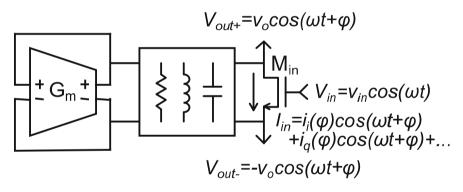

| Fig. 2.24              | Block diagram of the differential direct ILFD                         | 27       |

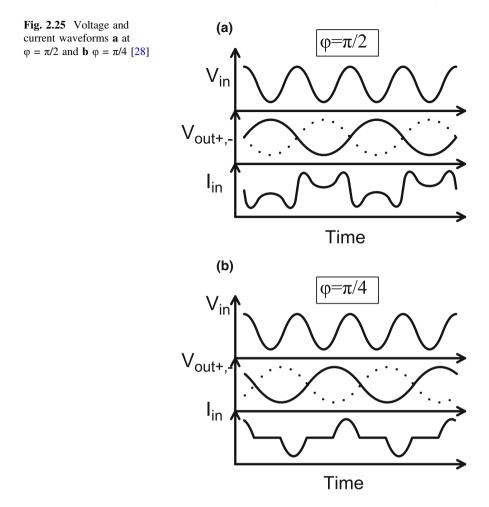

| Fig. 2.24<br>Fig. 2.25 | Voltage and current waveforms <b>a</b> at $\varphi = \pi/2$           | 21       |

| 1 lg. 2.23             | and $\mathbf{b} \ \varphi = \pi/4$                                    | 28       |

| Eia 2.26               |                                                                       | 20<br>29 |

| Fig. 2.26              | Dual-mixing direct ILFD circuit schematic                             | 29       |

| Fig. 2.27              | Conventional CML latches in a master-slave                            | 29       |

| E:= 2.29               | configuration                                                         |          |

| Fig. 2.28              | High frequency CML divider (by two)                                   | 30       |

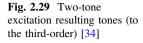

| Fig. 2.29              | Two-tone excitation resulting tones (to the                           | 22       |

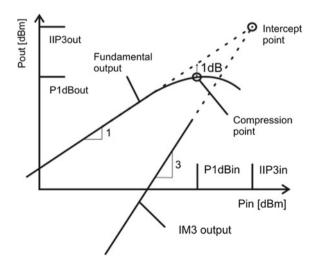

| E: 0.00                | third-order)                                                          | 32       |

| Fig. 2.30              | Definition of important linearity parameters.                         | 32       |

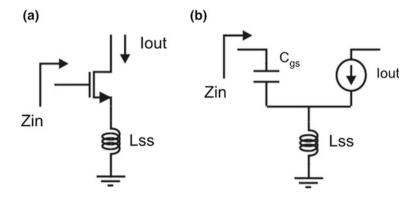

| Fig. 2.31              | a Inductively degenerated CS transistor                               | 22       |

| E: 0.00                | and <b>b</b> small-signal model                                       | 33       |

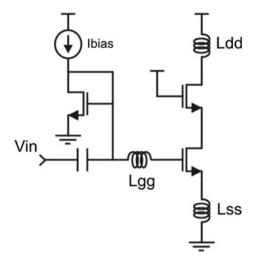

| Fig. 2.32              | Single-ended cascode LNA using inductive                              | ~ ~ ~    |

|                        | degeneration                                                          | 34       |

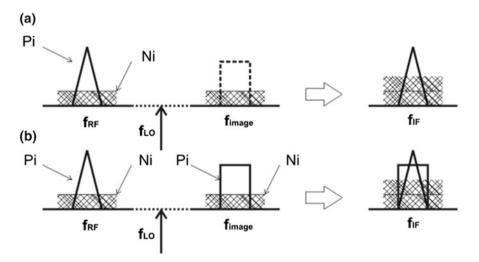

| Fig. 2.33              | Definition of a SSB versus b DSB NF                                   | 35       |

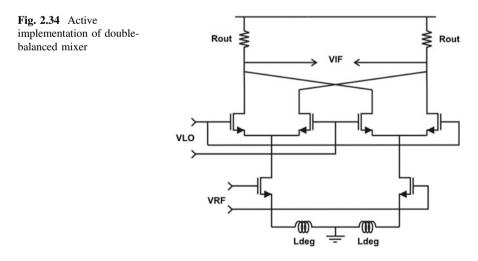

| Fig. 2.34              | Active implementation of double-balanced mixer                        | 36       |

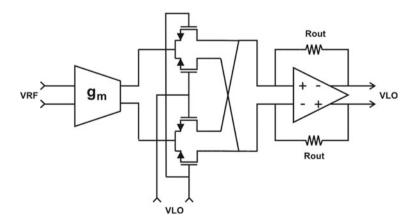

| Fig. 2.35              | Passive implementation of double-balanced mixer                       | 37       |

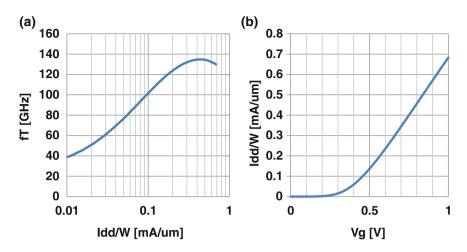

| Fig. 3.1               | a Transit frequency of the used 90 nm transistor,                     |          |

|                        | and $\mathbf{b}$ drain current density versus gate voltage            | 42       |

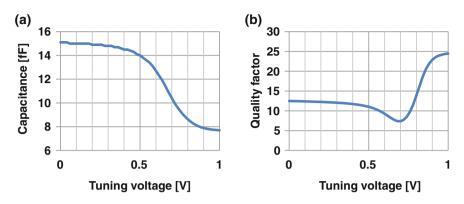

| Fig. 3.2               | a Capacitance and b quality factor for a varactor                     |          |

|                        | with $W = 1 \ \mu m$ and $M = 20 \dots \dots \dots \dots \dots \dots$ | 43       |

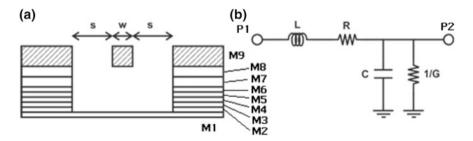

| Fig. 3.3               | Transmission line <b>a</b> cross-section and <b>b</b> RLCG model      | 43       |

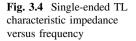

| Fig. 3.4               | Single-ended TL characteristic impedance versus                       |          |

|                        | frequency                                                             | 44       |

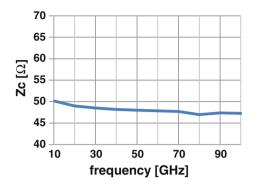

| Fig. 3.5               | <b>a</b> Inductance and <b>b</b> quality factor of the 300 pH         |          |

|                        | differential inductor                                                 | 45       |

| Fig. 3.6               | Differential inductor lumped component model                          | 45       |

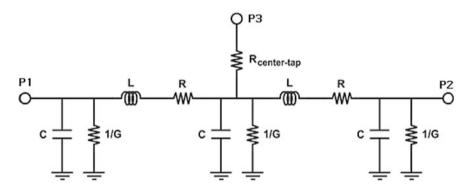

| Fig. 3.7               | Transformer implemented with 83 pH primary                            |          |

|                        | (=secondary) inductance in 90 nm process                              | 45       |

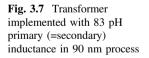

| Fig. 3.8               | Testbench used for the prediction of transformer                      |          |

|                        | parameters                                                            | 46       |

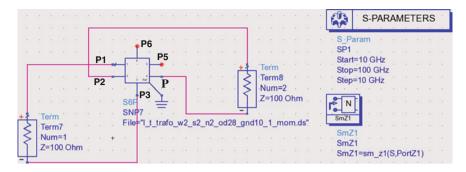

| Fig. 3.9               | a Inductance, b quality factor and c coupling                         |          |

|                        | coefficient of the 83 pH transformer                                  | 47       |

| Fig. 3.10              | Transformer lumped component model                                    | 47       |

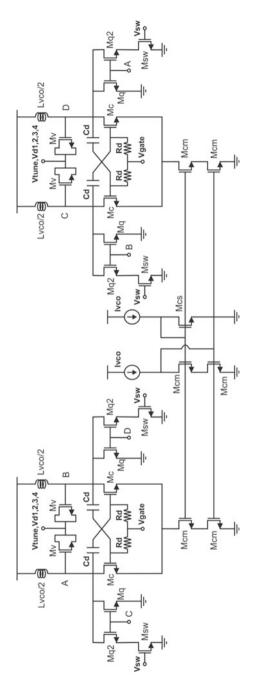

| Fig. 3.11              | Circuit schematic of the used P-QVCO                                  | 49       |

| Fig. 3.12              | Circuit schematic of the transformer-coupled                          |          |

|                        | LO buffer with output load                                            | 50       |

|                        |                                                                       |          |

#### Figures

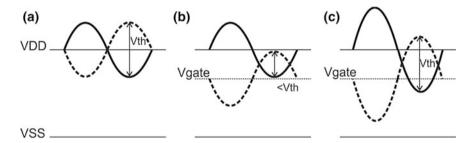

| Fig. 3.13 | QVCO <b>a</b> without <b>b</b> with external gate bias,<br>and <b>c</b> higher swing possibility without taking |    |

|-----------|-----------------------------------------------------------------------------------------------------------------|----|

|           | the cross-coupled transistors out of saturation                                                                 | 50 |

| Fig. 3.14 | Impedance points of the QVCO two oscillation                                                                    | 50 |

| C         | modes                                                                                                           | 51 |

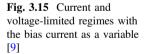

| Fig. 3.15 | Current and voltage-limited regimes with the bias                                                               |    |

| U         | current as a variable                                                                                           | 54 |

| Fig. 3.16 | a Average capacitance value and b effective                                                                     |    |

| C         | capacitance curve for a varactor in a VCO                                                                       | 55 |

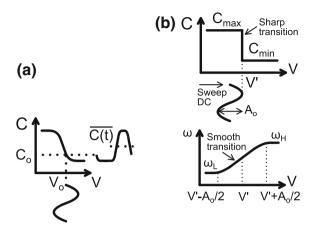

| Fig. 3.17 | Less tuning frequency with higher current due                                                                   |    |

| C         | to different effective capacitance values                                                                       |    |

|           | at different amplitudes                                                                                         | 55 |

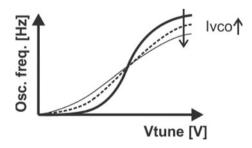

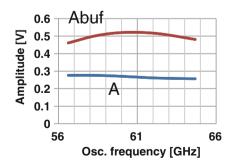

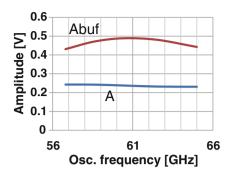

| Fig. 3.18 | P-QVCO and LO buffer amplitudes                                                                                 |    |

| C         | versus oscillation frequency.                                                                                   | 59 |

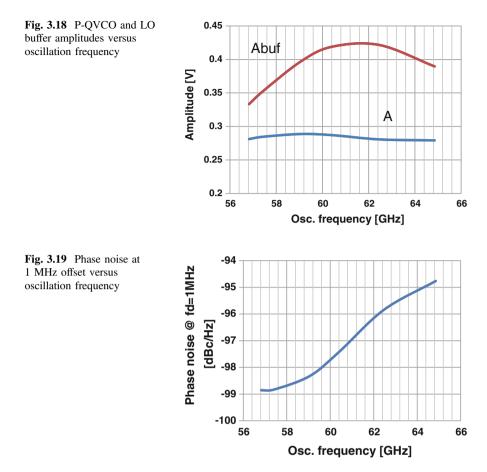

| Fig. 3.19 | Phase noise at 1 MHz offset versus oscillation                                                                  |    |

| •         | frequency                                                                                                       | 59 |

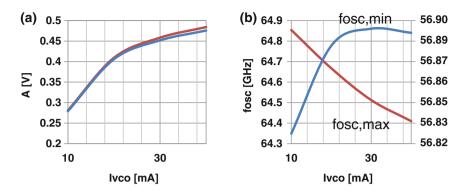

| Fig. 3.20 | <b>a</b> A at max. and min. oscillation freq. <b>b</b> Max.                                                     |    |

|           | and min. oscillation frequency variations with QVCO                                                             |    |

|           | bias current                                                                                                    | 60 |

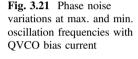

| Fig. 3.21 | Phase noise variations at max. and min. oscillation                                                             |    |

|           | frequencies with QVCO bias current                                                                              | 60 |

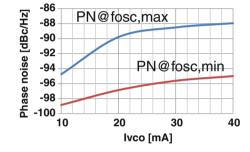

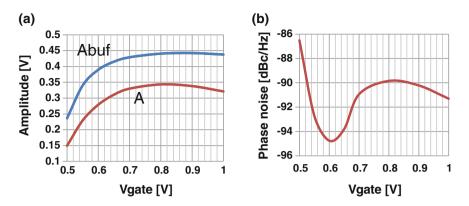

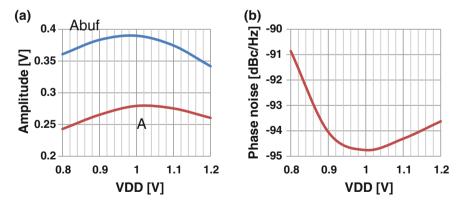

| Fig. 3.22 | a Amplitude and b phase noise variations with                                                                   |    |

|           | external gate bias at maximum oscillation frequency                                                             | 61 |

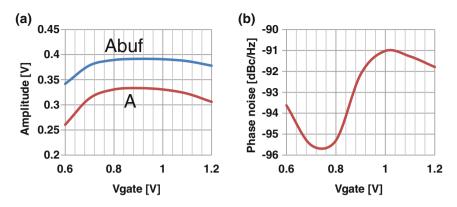

| Fig. 3.23 | a Amplitude and b phase noise variations with                                                                   |    |

|           | supply voltage at maximum oscillation frequency                                                                 | 61 |

| Fig. 3.24 | <b>a</b> Amplitude and <b>b</b> phase noise variations with                                                     |    |

|           | external gate bias at 1.2 V supply and maximum                                                                  |    |

|           | oscillation frequency                                                                                           | 62 |

| Fig. 3.25 | P-QVCO and LO buffer amplitudes versus oscillation                                                              |    |

|           | frequency at a reduced load transistor width of 24 $\mu m$                                                      | 62 |

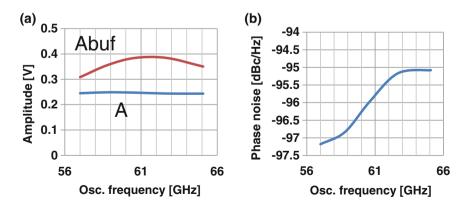

| Fig. 3.26 | BS-QVCO and LO buffer <b>a</b> amplitudes and <b>b</b> phase                                                    |    |

|           | noise over the whole tuning range                                                                               | 63 |

| Fig. 3.27 | BS-QVCO and LO buffer amplitudes versus oscillation                                                             |    |

|           | frequency at a reduced load transistor width of 24 $\mu$ m                                                      | 64 |

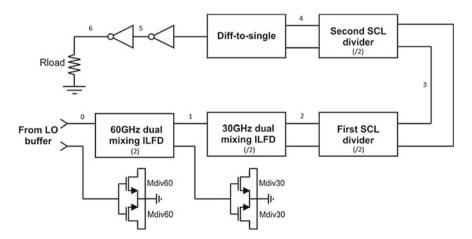

| Fig. 3.28 | Divider chain block diagram                                                                                     | 65 |

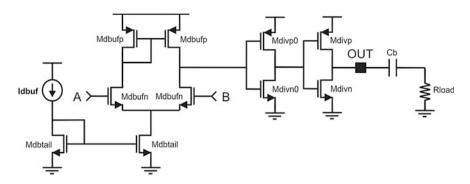

| Fig. 3.29 | Differential to single-ended stage with output buffers                                                          | 66 |

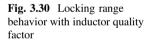

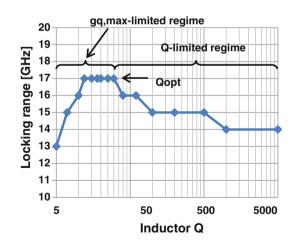

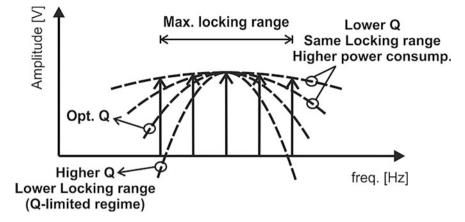

| Fig. 3.30 | Locking range behavior with inductor quality factor                                                             | 67 |

| Fig. 3.31 | Divider output spectrum with quality factor                                                                     |    |

|           | curves assuming equal output amplitude                                                                          | 68 |

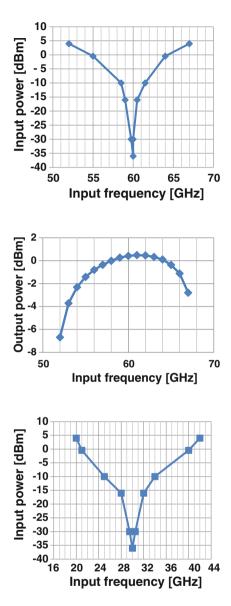

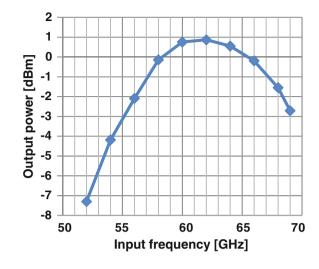

| Fig. 3.32 | 60 GHz divider input sensitivity curve                                                                          | 71 |

| Fig. 3.33 | 60 GHz divider output power at 4 dBm input signal                                                               | 71 |

| Fig. 3.34 | 30 GHz divider input sensitivity curve                                                                          | 71 |

| Fig. 3.35 | 30 GHz divider output power at 4 dBm input signal                                                               | 72 |

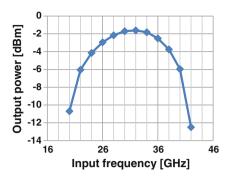

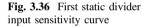

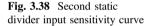

| Fig. 3.36 | First static divider input sensitivity curve                                                                    | 72 |

| Fig. 3.37  | First static divider output power at 4 dBm input signal              | 72  |

|------------|----------------------------------------------------------------------|-----|

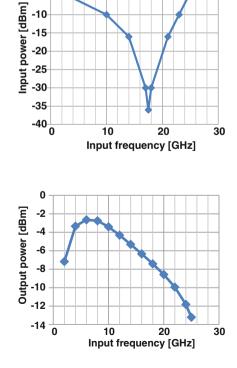

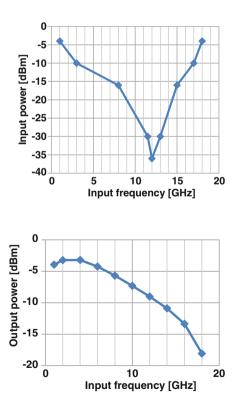

| Fig. 3.38  | Second static divider input sensitivity curve                        | 73  |

| Fig. 3.39  | Second static divider output power at 4 dBm                          |     |

| C          | input signal                                                         | 73  |

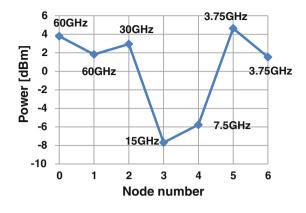

| Fig. 3.40  | Divider chain signal levels at each block                            | 74  |

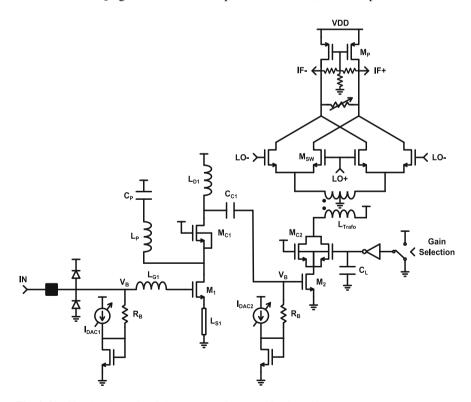

| Fig. 3.41  | Circuit schematic of the LNA + mixer                                 |     |

| 0          | combination                                                          | 75  |

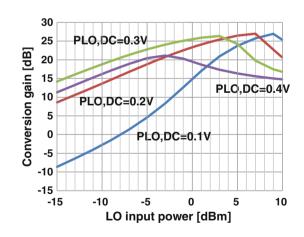

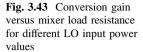

| Fig. 3.42  | Conversion gain versus LO input power                                |     |

| 0          | for RL = 1 k $\Omega$                                                | 77  |

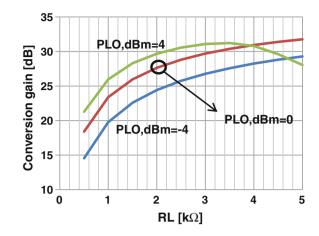

| Fig. 3.43  | Conversion gain versus mixer load resistance                         |     |

| 8          | for different LO input power values                                  | 78  |

| Fig. 3.44  | Conversion gain versus LO input power                                |     |

| 1.8.01.1   | for RL = 5 k $\Omega$                                                | 78  |

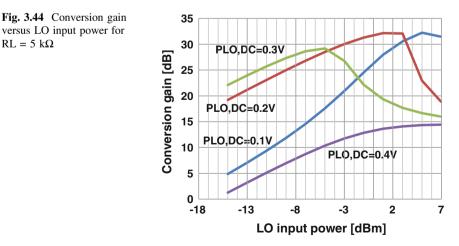

| Fig. 3.45  | Conversion gain versus RF input frequency                            | ,,, |

| 1 18. 5.15 | for RL = 1 k $\Omega$ and P <sub>LO,dBm</sub> = 4 dBm                | 79  |

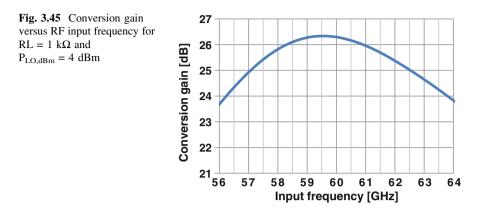

| Fig. 3.46  | <b>a</b> Noise figure versus IF output frequency,                    | .,  |

| 119. 5.10  | and <b>b</b> S11 versus RF input frequency.                          | 79  |

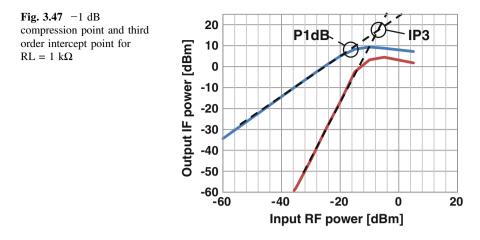

| Fig. 3.47  | -1 dB compression point and third order intercept                    | .,  |

| 118. 5.17  | point for RL = 1 k $\Omega$                                          | 80  |

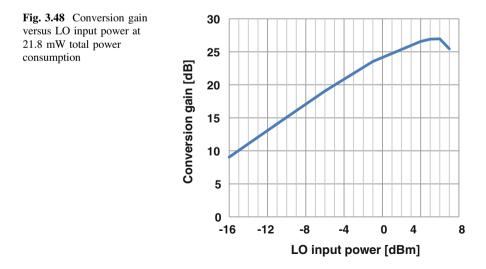

| Fig. 3.48  | Conversion gain versus LO input power                                | 00  |

| 1 19. 5.10 | at 21.8 mW total power consumption                                   | 80  |

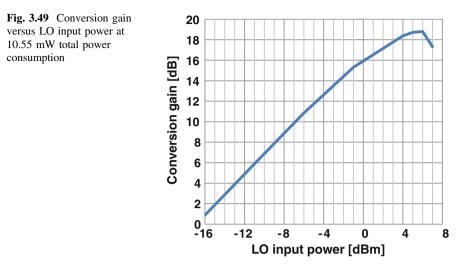

| Fig. 3.49  | Conversion gain versus LO input power                                | 00  |

| 115. 5.17  | at 10.55 mW total power consumption                                  | 81  |

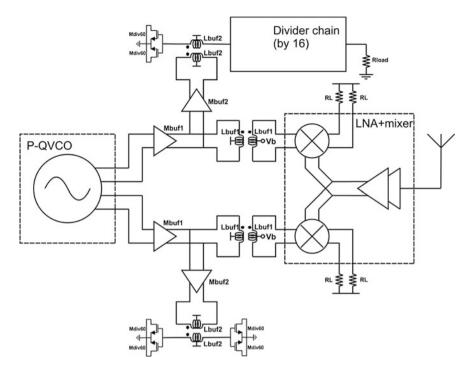

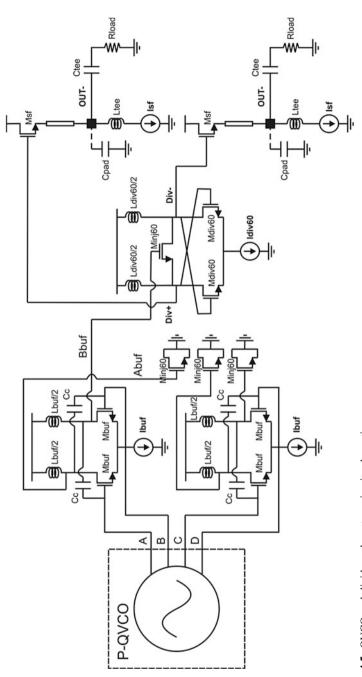

| Fig. 4.1   | Front-end top-level circuit schematic                                | 84  |

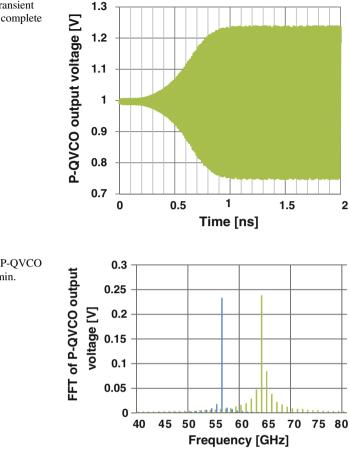

| Fig. 4.2   | P-QVCO transient output voltage in the complete                      | 04  |

| 115. 1.2   | top-level system.                                                    | 86  |

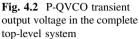

| Fig. 4.3   | FFT of the P-QVCO output at max. and min.                            | 00  |

| 118. 113   | tuning ranges                                                        | 86  |

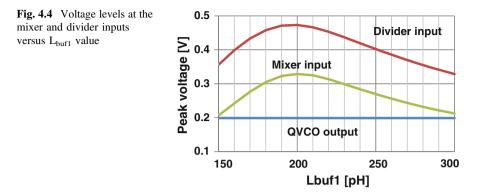

| Fig. 4.4   | Voltage levels at the mixer and divider                              | 00  |

| 115. 1.1   | inputs versus L <sub>buf1</sub> value                                | 87  |

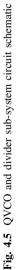

| Fig. 4.5   | QVCO and divider sub-system circuit schematic                        | 88  |

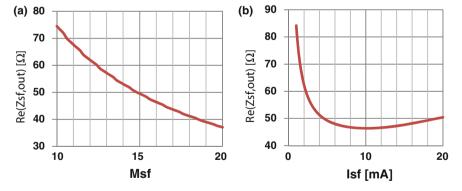

| Fig. 4.6   | Real part of the source follower output impedance                    | 00  |

| 1 15. 4.0  | a without current source, and b with current                         |     |

|            | source at Msf = $16$                                                 | 90  |

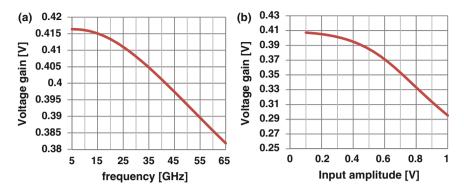

| Fig. 4.7   | <b>a</b> Small- and <b>b</b> large-signal voltage gain of the source | 70  |

| 1 15. 4.7  | follower                                                             | 91  |

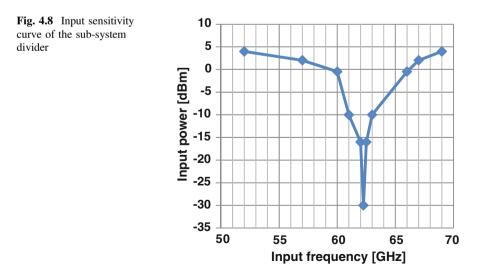

| Fig. 4.8   | Input sensitivity curve of the sub-system divider                    | 91  |

| Fig. 4.9   | Output power of the sub-system divider                               | 92  |

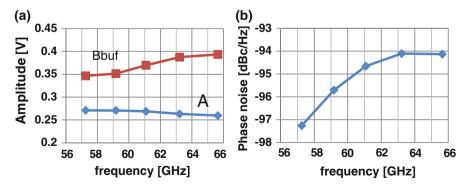

| Fig. 4.10  | a Amplitudes and b phase noise of the sub-system                     | 12  |

| 1 lg. 4.10 | QVCO and LO buffer versus tuning range without                       |     |

|            | neutralization capacitors                                            | 92  |

| Fig. 4.11  | a Amplitudes and b phase noise of the sub-system                     | 72  |

| 11g. 4.11  | QVCO and LO buffer versus tuning range                               |     |

|            |                                                                      | 02  |

|            | with neutralization capacitors.                                      | 93  |

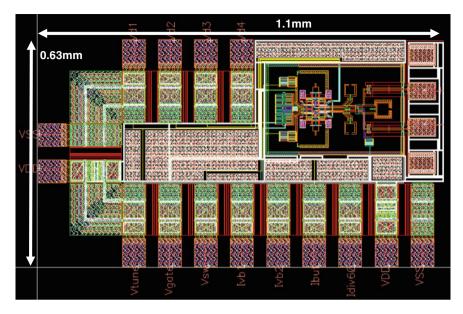

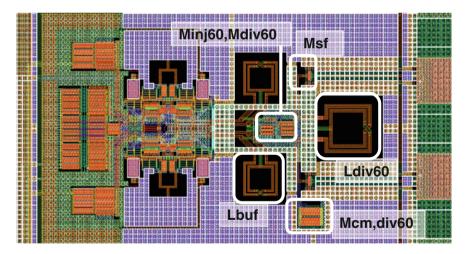

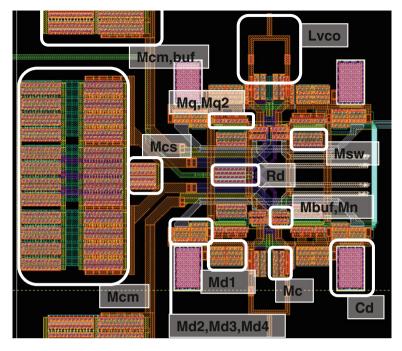

| Fig. 5.1  | Top-level circuit layout with IO ring                              | 96  |

|-----------|--------------------------------------------------------------------|-----|

| Fig. 5.2  | The circuit core including the QVCO, LO buffer,                    |     |

|           | divider and output buffer                                          | 96  |

| Fig. 5.3  | The P-QVCO, and LO buffer active elements                          |     |

|           | with the ground cells omitted                                      | 97  |

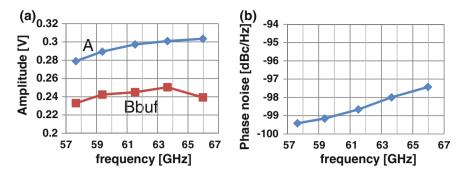

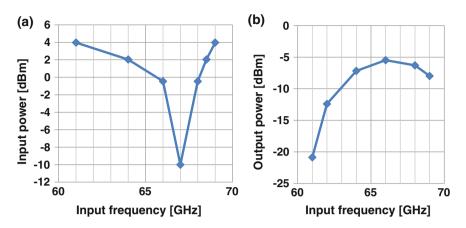

| Fig. 5.4  | Divider <b>a</b> input sensitivity curve and <b>b</b> output power |     |

|           | for a 48 µm OD inductor                                            | 98  |

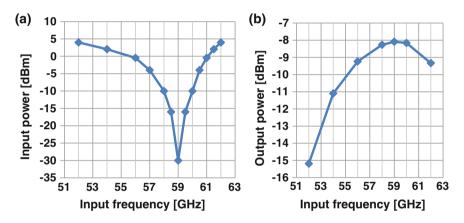

| Fig. 5.5  | Divider <b>a</b> input sensitivity curve and <b>b</b> output power |     |

|           | for a 55 µm OD inductor                                            | 98  |

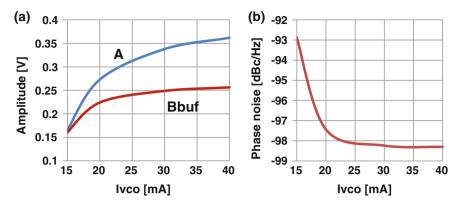

| Fig. 5.6  | Variation with QVCO bias current at V <sub>gate</sub> of 1 V       | 99  |

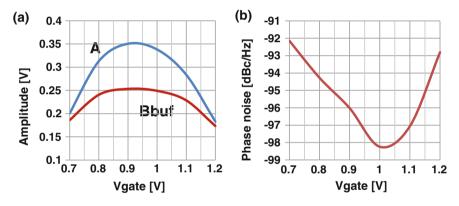

| Fig. 5.7  | Variations with gate voltage at Ivco of 30 mA                      | 99  |

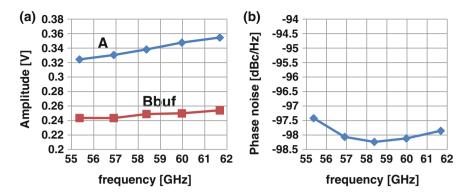

| Fig. 5.8  | Performance at V <sub>gate</sub> of 1 V and Ivco of 30 mA          |     |

|           | over the tuning range                                              | 100 |

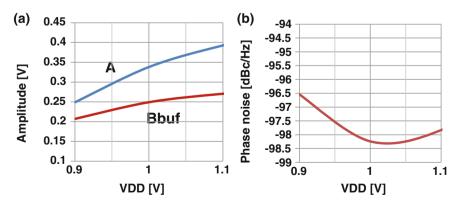

| Fig. 5.9  | Amplitude and phase noise variations of the QVCO                   |     |

|           | and LO buffer with supply voltage at $V_{gate}$ of 1 V             |     |

|           | and Ivco of 30 mA                                                  | 100 |

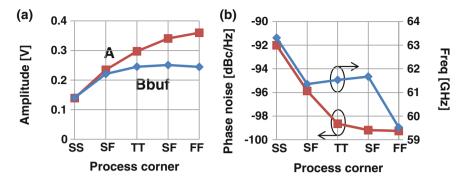

| Fig. 5.10 | a Amplitudes, b phase noise and oscillation                        |     |

|           | frequency schematic simulations versus process                     |     |

|           | corners at 27 °C                                                   | 101 |

## Tables

| Table 1.1 | Channels defined by the IEEE and ECMA standards      | 3  |

|-----------|------------------------------------------------------|----|

| Table 3.1 | QVCO and LO buffer target specifications             | 48 |

| Table 3.2 | Design values for the QVCO and LO buffer             | 58 |

| Table 3.3 | QVCO and LO buffer target specs and achieved results | 64 |

| Table 3.4 | Design values for the divider chain circuit          | 67 |

| Table 3.5 | Performance summary of each divider block            | 74 |

| Table 3.6 | Design values for the LNA and mixer                  | 77 |

| Table 3.7 | Performance summary of the LNA and mixer             |    |

|           | combination                                          | 81 |

| Table 4.1 | LO buffers design values for the complete            |    |

|           | top-level circuit                                    | 85 |

| Table 4.2 | Design values of the sub-system blocks               |    |

|           | (without the QVCO)                                   | 90 |

| Table 5.1 | Inductor parameters for the LO buffer and divider    |    |

|           | in the test chip                                     | 96 |

| Table 5.2 | Worst case PVT simulation results                    | 97 |

|           |                                                      |    |

#### Abstract