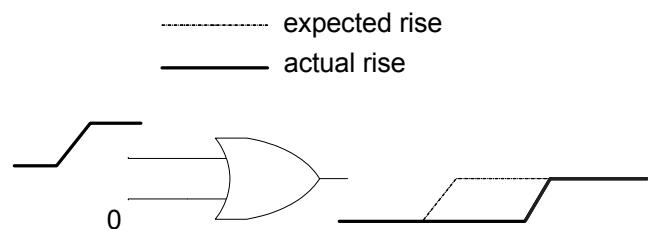

Frontiers

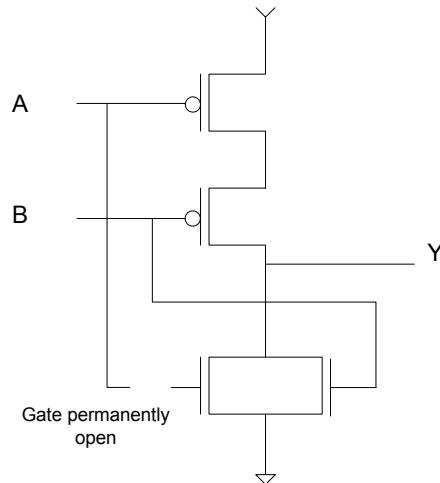

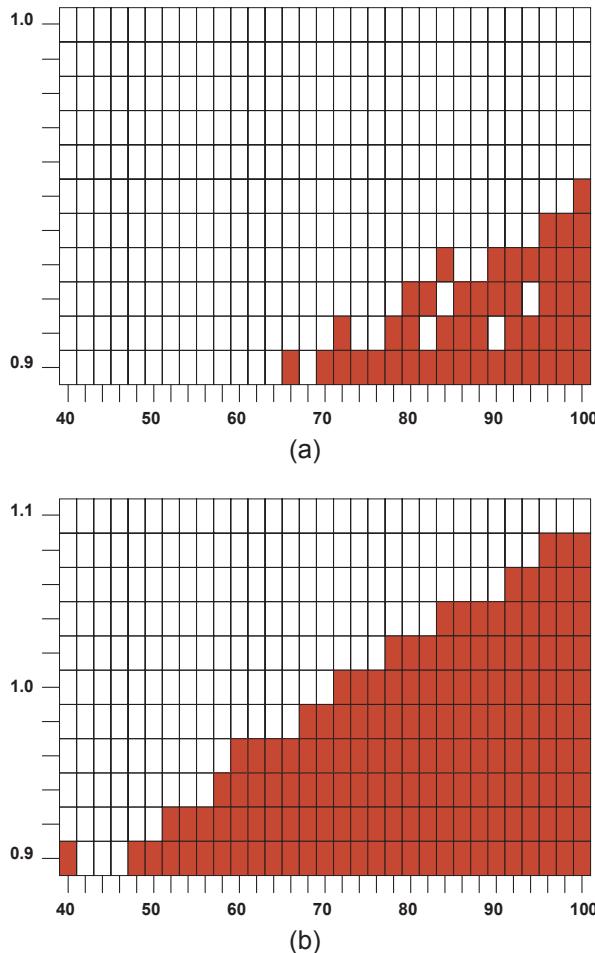

in Electronic

Testing

# Advances in Electronic Testing

Challenges and Methodologies

Edited by

**Dimitris Gizopoulos**

Springer

$\pi$   $\pi$   $\sigma$   $\alpha$   $\pi$   $\delta$   $\theta$   $\tau$   $\mu$

ADVANCES IN ELECTRONIC TESTING

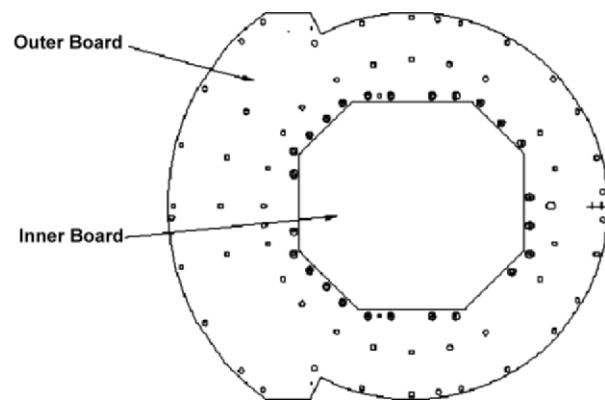

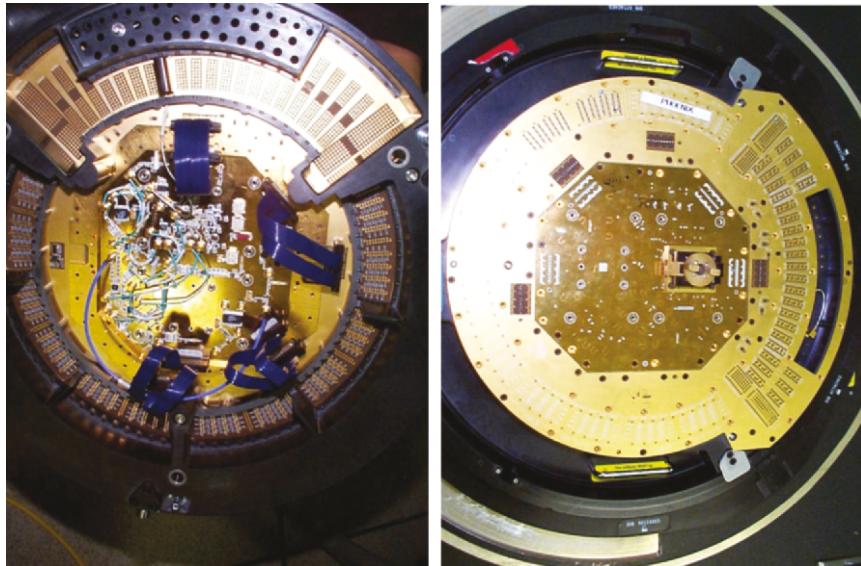

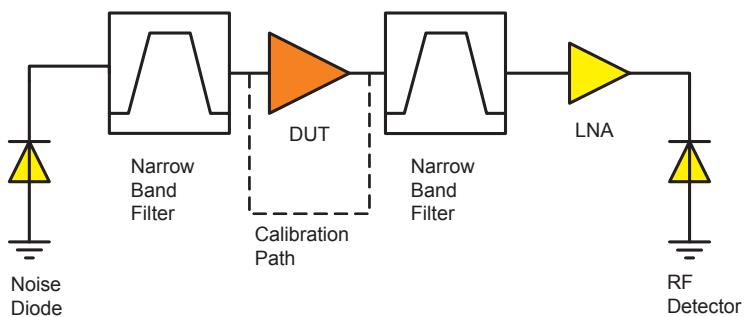

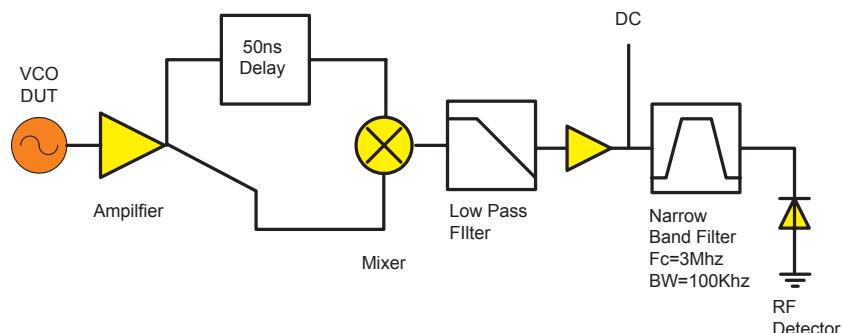

CHALLENGES AND METHODOLOGIES

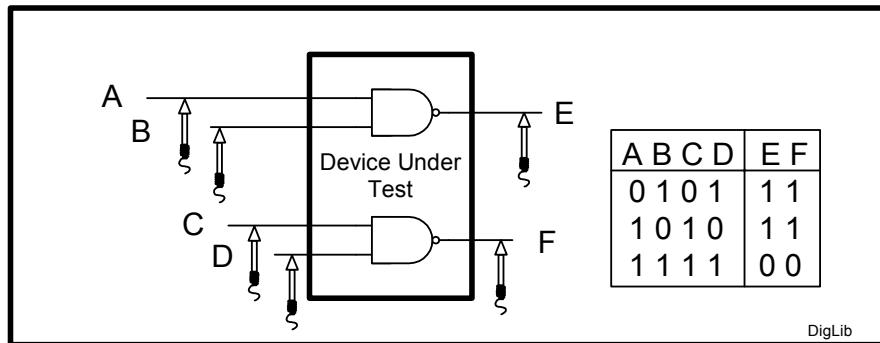

## FRONTIERS IN ELECTRONIC TESTING

*Consulting Editor*

**Vishwani D. Agrawal**

*Books in the series:*

**Introduction to Advanced System-on-Chip Test Design and Optimiz...**

Larsson, E., Vol. 29

ISBN: 1-4020-3207-2

**Embedded Processor-Based Self-Test**

Gizopoulos, D. (Ed.), Vol. 28

ISBN: 1-4020-2785-0

**Advances in Electronic Testing : Challenges and Methodologies**

Gizopoulos, D. (Ed.), Vol. 27

ISBN: 0-387-29408-2

**Testing Static Random Access Memories**

Hamdioui, S., Vol. 26,

ISBN: 1-4020-7752-1

**Verification by Error Modeling**

Radecka, K. and Zilic, Vol. 25

ISBN: 1-4020-7652-5

**Elements of STIL: Principles and Applications of IEEE Std. 1450**

Maston, G., Taylor, T. (et al.), Vol. 24

ISBN: 1-4020-7637-1

**Fault Injection Techniques and Tools for Embedded systems Reliability ...**

Benso, A., Prinetto, P. (Eds.), Vol. 23

ISBN: 1-4020-7589-8

**Power-Constrained Testing of VLSI Circuits**

Nicolici, N., Al-Hashimi, B.M., Vol. 22B

ISBN: 1-4020-7235-X

**High Performance Memory Testing**

Adams, R. Dean, Vol. 22A

ISBN: 1-4020-7255-4

**SOC (System-on-a-Chip) Testing for Plug and Play Test Automation**

Chakrabarty, K. (Ed.), Vol. 21

ISBN: 1-4020-7205-8

**Test Resource Partitioning for System-on-a-Chip**

Chakrabarty, K., Iyengar & Chandra(et al.), Vol. 20

ISBN: 1-4020-7119-1

**A Designers' Guide to Built-in Self-Test**

Stroud, C., Vol. 19

ISBN: 1-4020-7050-0

**Boundary-Scan Interconnect Diagnosis**

de Sousa, J., Cheung, P.Y.K., Vol. 18

ISBN: 0-7923-7314-6

**Essentials of Electronic Testing for Digital, Memory, and Mixed Signal VLSI Circuits**

Bushnell, M.L., Agrawal, V.D., Vol. 17

ISBN: 0-7923-7991-8

**Analog and Mixed-Signal Boundary-Scan: A Guide to the IEEE 1149.4 Test ...**

Osseiran, A. (Ed.), Vol. 16

ISBN: 0-7923-8686-8

# ADVANCES IN ELECTRONIC TESTING

## CHALLENGES AND METHODOLOGIES

Edited by

DIMITRIS GIZOPOULOS

*University of Piraeus, Greece*

A C.I.P. Catalogue record for this book is available from the Library of Congress.

---

ISBN-10 0-387-29408-2 (HB)

ISBN-13 978-0-387-29408-7 (HB)

ISBN-10 0-387-29409-0 (e-book)

ISBN-13 978-0-387-29409-4 (e-book)

---

Published by Springer,

P.O. Box 17, 3300 AA Dordrecht, The Netherlands.

*www.springeronline.com*

*Printed on acid-free paper*

All Rights Reserved

© 2006 Springer

No part of this work may be reproduced, stored in a retrieval system, or transmitted

in any form or by any means, electronic, mechanical, photocopying, microfilming, recording

or otherwise, without written permission from the Publisher, with the exception

of any material supplied specifically for the purpose of being entered

and executed on a computer system, for exclusive use by the purchaser of the work.

Printed in the Netherlands.

# Contents

## **Foreword** **xiii**

by Vishwani D. Agrawal

## **Preface** **xvii**

by Dimitris Gizopoulos

## **Contributing Authors** **xxiii**

## **Dedication** **xxv**

## **Chapter 1—Defect-Oriented Testing** **1**

by Robert C. Aitken

1.1 *History of Defect-Oriented Testing* 2

1.2 *Classic Defect Mechanisms* 4

1.2.1 Shorts 4

1.2.2 Opens 6

1.2.3 Parametric Changes 7

1.3 *Defect Mechanisms in Advanced Technologies* 8

1.3.1 Copper-related Defects 8

1.3.2 Optical Defects 10

1.3.3 Design-related Defects 12

1.4 *Defects and Faults* 14

1.4.1 Uses of Fault Models 15

1.4.2 Single Stuck-at Faults 16

1.4.3 Bridging Faults 17

1.4.4 Open Fault Models 22

1.4.5 Timing-related or Delay Faults 24

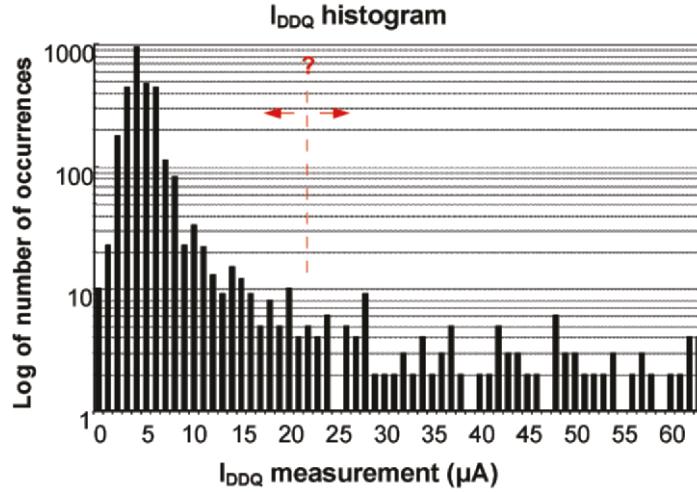

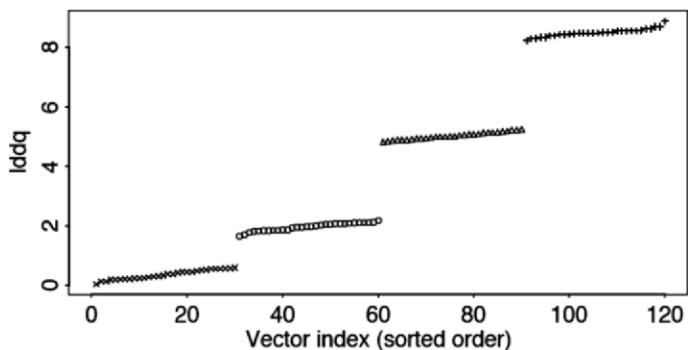

1.4.6 I<sub>DDQ</sub> Models 27

|            |                                                   |    |

|------------|---------------------------------------------------|----|

| <i>1.5</i> | <i>Defect-Oriented Test Types</i>                 | 28 |

| 1.5.1      | Logic Tests                                       | 28 |

| 1.5.2      | Current-based Tests                               | 29 |

| 1.5.3      | Delay Test                                        | 31 |

| 1.5.4      | Very Low Voltage                                  | 32 |

| 1.5.5      | Stress Testing                                    | 33 |

| <i>1.6</i> | <i>Experimental Results</i>                       | 34 |

| 1.6.1      | Fault Coverage, Scan vs. Functional               | 34 |

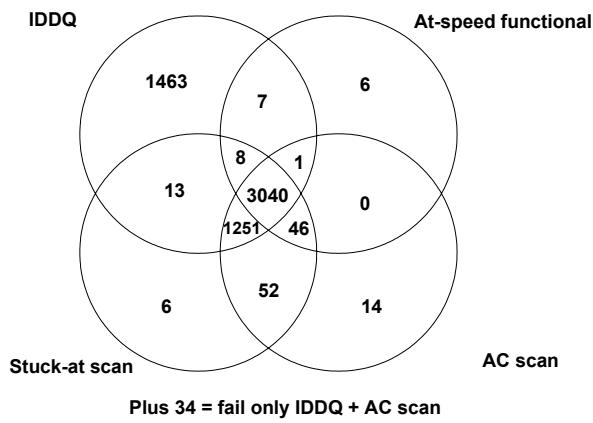

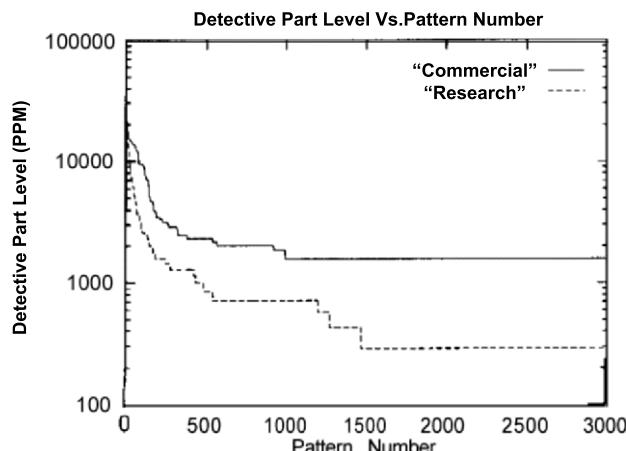

| 1.6.2      | Effectiveness of $I_{DDQ}$ , Scan, At-speed Tests | 34 |

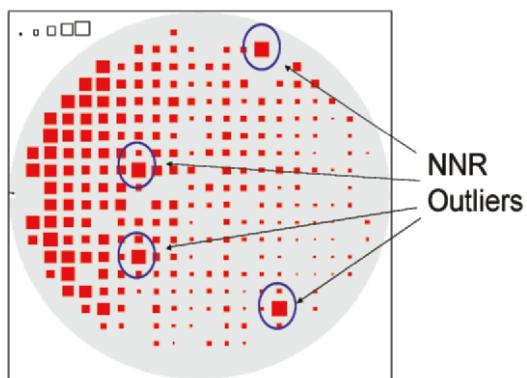

| 1.6.3      | Statistical Post Processing                       | 39 |

| <i>1.7</i> | <i>Future Trends and Conclusions</i>              | 39 |

*Acknowledgments* 40

*References* 40

## **Chapter 2—Failure Mechanisms and Testing in Nanometer Technologies 43**

by Jaume Segura, Charles Hawkins and Jerry Soden

|            |                                                |    |

|------------|------------------------------------------------|----|

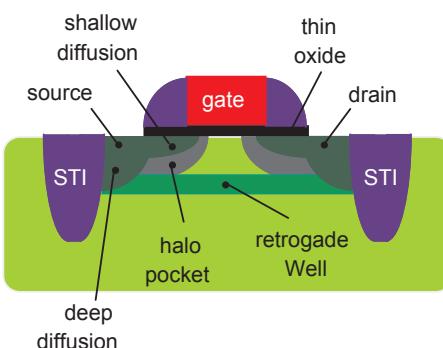

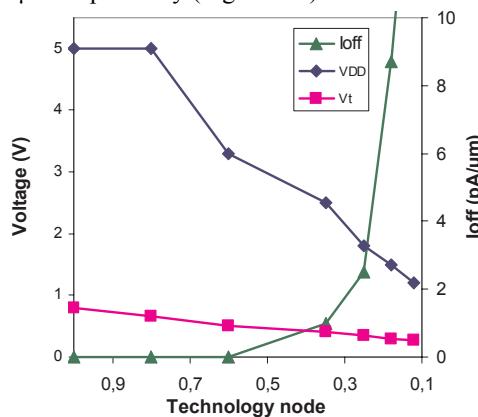

| <i>2.1</i> | <i>Scaling CMOS Technology</i>                 | 44 |

| 2.1.1      | Device Scaling                                 | 45 |

| 2.1.2      | Interconnect Scaling                           | 51 |

| 2.1.3      | Parameter Variations                           | 52 |

| 2.1.4      | Noise                                          | 55 |

| <i>2.2</i> | <i>Failure Modes in Nanometer Technologies</i> | 57 |

| 2.2.1      | Bridge Defects                                 | 57 |

| 2.2.2      | Open Circuit Defects                           | 60 |

| 2.2.3      | Parametric Failures                            | 61 |

| <i>2.3</i> | <i>Test Methods for Nanometer ICs</i>          | 65 |

| 2.3.1      | Impact of Technology Scaling on Testing        | 66 |

| 2.3.2      | Dealing with Background Current Increase       | 67 |

| 2.3.3      | Noise-tolerant Techniques                      | 68 |

| 2.3.4      | Impact of Variation on Delay                   | 72 |

| <i>2.4</i> | <i>Conclusion</i>                              | 73 |

*References* 73

## **Chapter 3—Silicon Debug 77**

by Doug Josephson and Bob Gottlieb

|            |                              |    |

|------------|------------------------------|----|

| <i>3.1</i> | <i>Introduction</i>          | 77 |

| <i>3.2</i> | <i>Silicon Debug History</i> | 79 |

| <i>3.3</i> | <i>Silicon Debug Process</i> | 80 |

| 3.3.1      | Post-silicon Validation      | 80 |

|       |                                            |     |

|-------|--------------------------------------------|-----|

| 3.4   | <i>Debug Flow</i>                          | 82  |

| 3.4.1 | Step 1: Control the Failure                | 82  |

| 3.4.2 | Step 2: Isolate the Failing Circuit        | 84  |

| 3.4.3 | Step 3: Root Cause the Failure             | 89  |

| 3.4.4 | Step 4: Try to Expand the Problem          | 91  |

| 3.5   | <i>Circuit Failures</i>                    | 92  |

| 3.5.1 | Speedpaths                                 | 92  |

| 3.5.2 | Mintime Races                              | 92  |

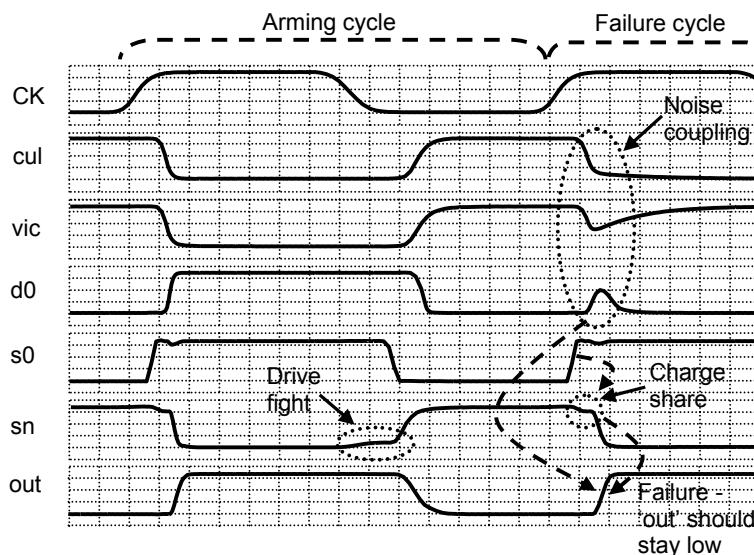

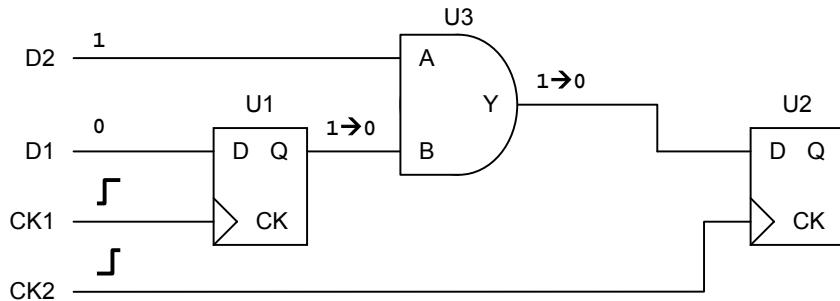

| 3.5.3 | Charge Sharing                             | 94  |

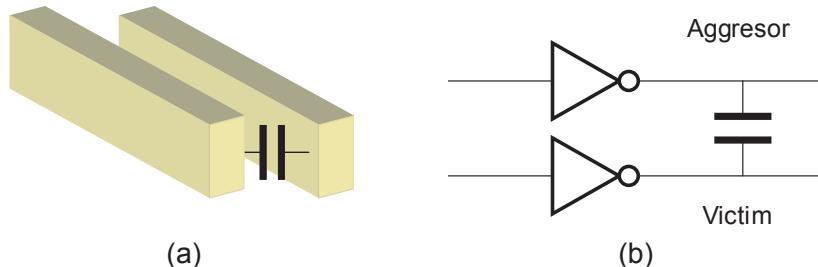

| 3.5.4 | Interconnect Noise                         | 96  |

| 3.5.5 | Leakage                                    | 98  |

| 3.5.6 | Manufacturability                          | 100 |

| 3.6   | <i>A Case Study in Silicon Debug</i>       | 101 |

| 3.7   | <i>Future Challenges for Silicon Debug</i> | 105 |

| 3.8   | <i>Conclusion</i>                          | 106 |

|       | <i>Acknowledgements</i>                    | 107 |

|       | <i>References</i>                          | 107 |

## **Chapter 4—Delay Testing 109**

by Adam Cron

|       |                                       |     |

|-------|---------------------------------------|-----|

| 4.1   | <i>Introduction</i>                   | 109 |

| 4.1.1 | Why Delay Testing                     | 109 |

| 4.1.2 | Why Now                               | 110 |

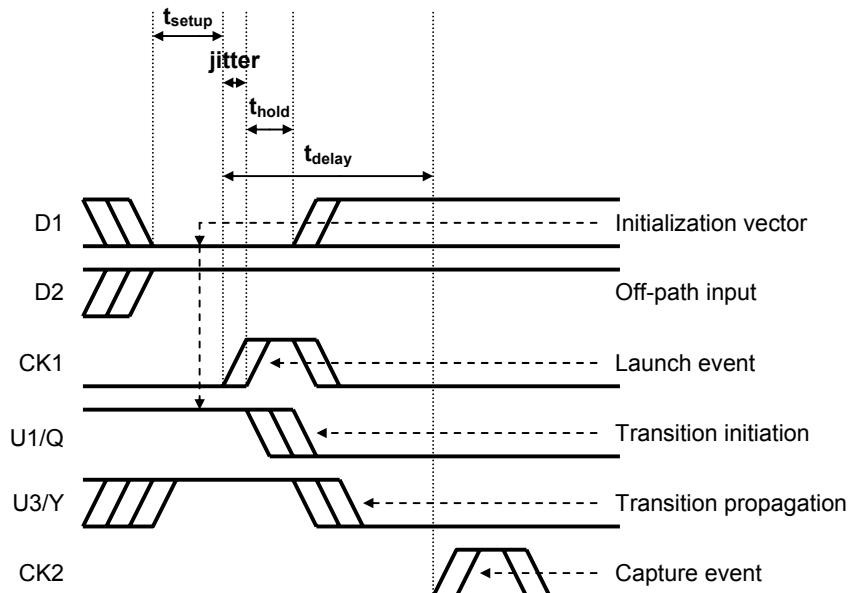

| 4.2   | <i>Delay Test Basics</i>              | 110 |

| 4.2.1 | Transition Delay Basics               | 114 |

| 4.2.2 | Path Delay Basics                     | 115 |

| 4.3   | <i>Test Application</i>               | 116 |

| 4.3.1 | Scan Architectures                    | 116 |

| 4.3.2 | Last-Shift-Launch                     | 116 |

| 4.3.3 | System-Clock-Launch                   | 118 |

| 4.3.4 | Hybrid Launch                         | 119 |

| 4.3.5 | BIST and Delay Testing                | 119 |

| 4.3.6 | Philosophy and Delay Test Application | 120 |

| 4.4   | <i>Delay Test Details</i>             | 121 |

| 4.4.1 | Clock Domain Issues                   | 121 |

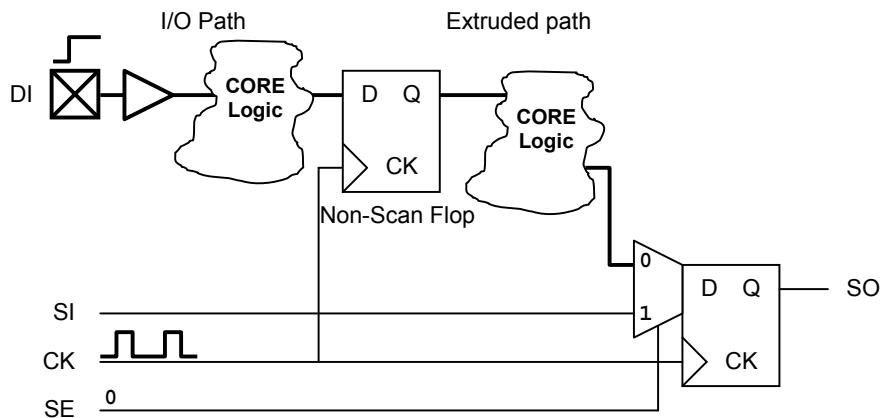

| 4.4.2 | I/O Issues                            | 124 |

| 4.5   | <i>Vector Generation</i>              | 125 |

| 4.5.1 | Last-Shift-Launch                     | 126 |

| 4.5.2 | System-Clock-Launch                   | 126 |

| 4.5.3 | Fault Model Tweaks                    | 127 |

| 4.5.4 | Selecting Faults                      | 127 |

|       |                               |     |

|-------|-------------------------------|-----|

| 4.6   | <i>Chip Design Constructs</i> | 129 |

| 4.6.1 | Phase-Locked Loops (PLLs)     | 129 |

| 4.6.2 | Core Test Support             | 130 |

| 4.6.3 | I/O Loopback                  | 132 |

|       |                         |     |

|-------|-------------------------|-----|

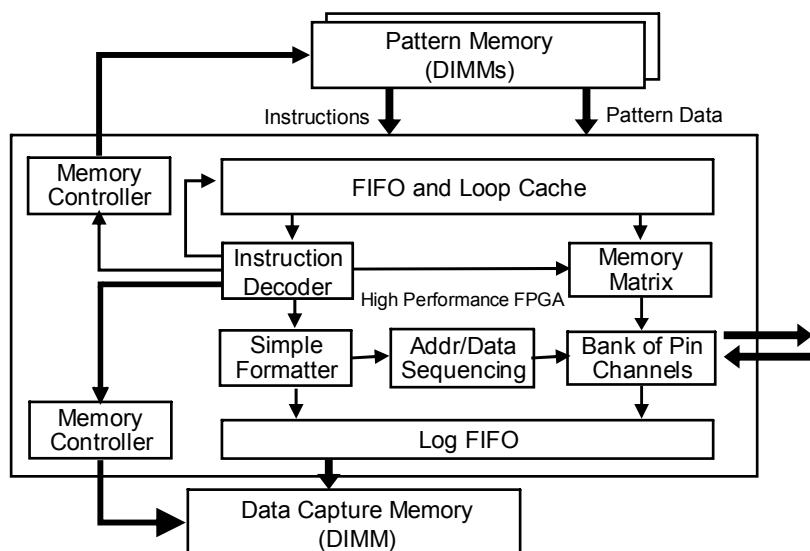

| 4.7   | <i>ATE Requirements</i> | 132 |

| 4.7.1 | I/O Requirements        | 133 |

| 4.7.2 | Speed Requirements      | 133 |

| 4.7.3 | Power Requirements      | 135 |

|     |                                       |     |

|-----|---------------------------------------|-----|

| 4.8 | <i>Conclusions: Tests vs. Defects</i> | 136 |

|-----|---------------------------------------|-----|

|  |                         |     |

|--|-------------------------|-----|

|  | <i>Acknowledgements</i> | 137 |

|--|-------------------------|-----|

|  |                   |     |

|--|-------------------|-----|

|  | <i>References</i> | 137 |

|--|-------------------|-----|

## **Chapter 5—High-Speed Digital Test Interfaces 141**

by Wolfgang Maichen

|     |                     |     |

|-----|---------------------|-----|

| 5.1 | <i>New Concepts</i> | 141 |

|-----|---------------------|-----|

|       |                    |     |

|-------|--------------------|-----|

| 5.1.1 | Introduction       | 141 |

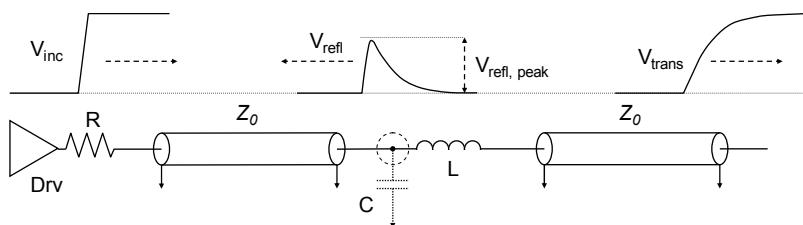

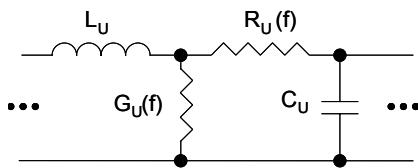

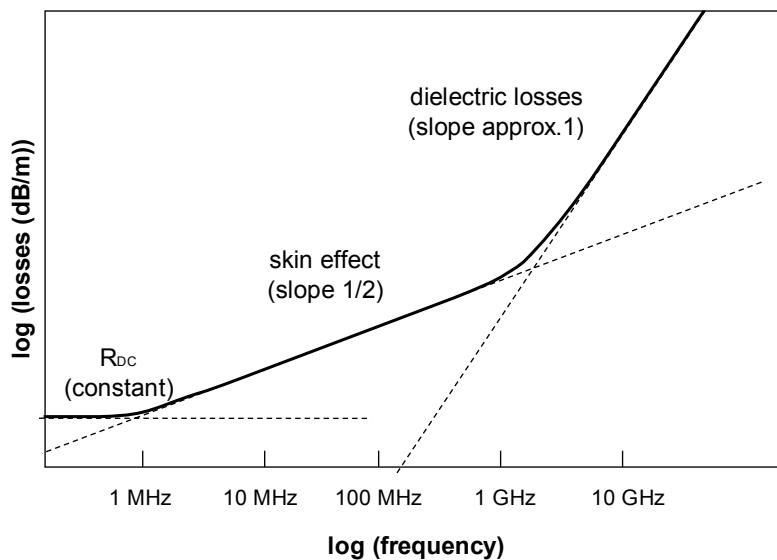

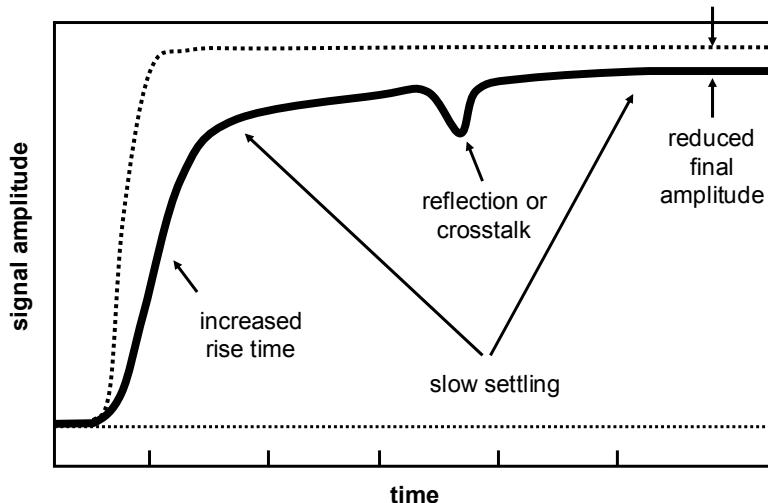

| 5.1.2 | Transmission Lines | 143 |

|     |                                         |     |

|-----|-----------------------------------------|-----|

| 5.2 | <i>Technology and Design Techniques</i> | 151 |

|-----|-----------------------------------------|-----|

|       |                             |     |

|-------|-----------------------------|-----|

| 5.2.1 | Parasitics Minimization     | 151 |

| 5.2.2 | Loss Mitigation             | 154 |

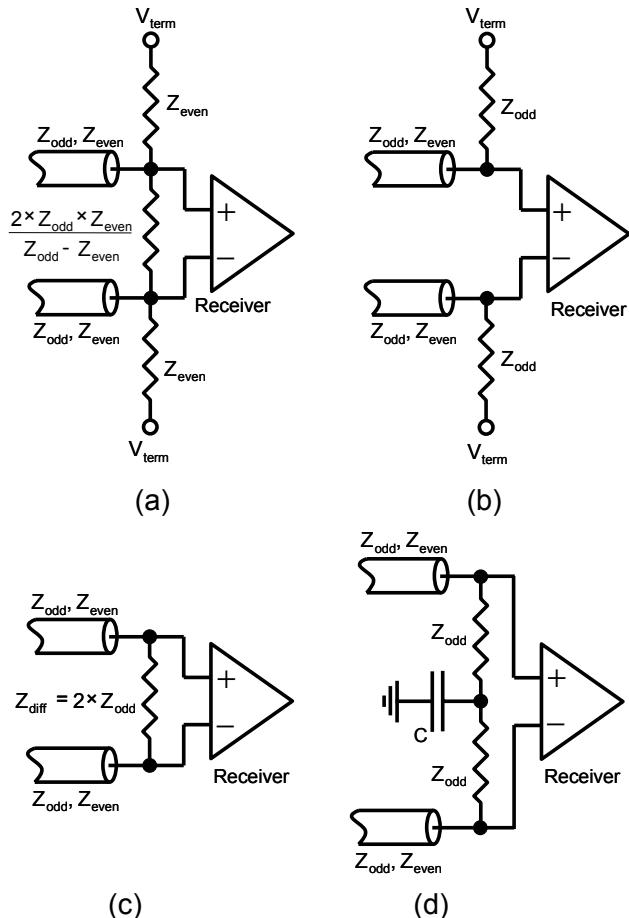

| 5.2.3 | Differential Signaling      | 157 |

| 5.2.4 | Termination                 | 160 |

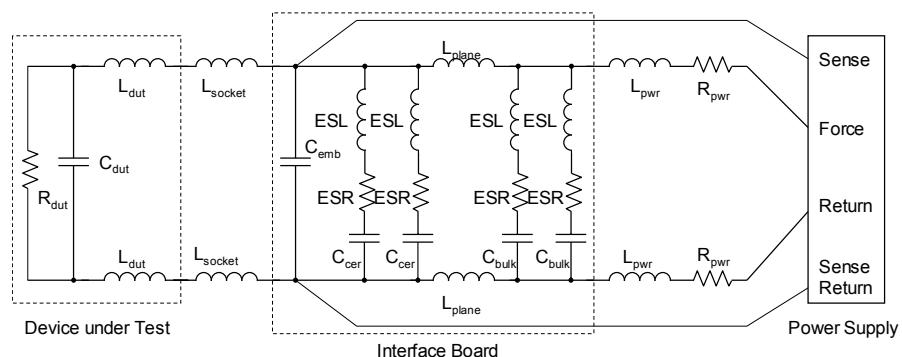

| 5.2.5 | Power Supply and Decoupling | 163 |

|     |                                      |     |

|-----|--------------------------------------|-----|

| 5.3 | <i>Characterization and Modeling</i> | 167 |

|-----|--------------------------------------|-----|

|       |                                    |     |

|-------|------------------------------------|-----|

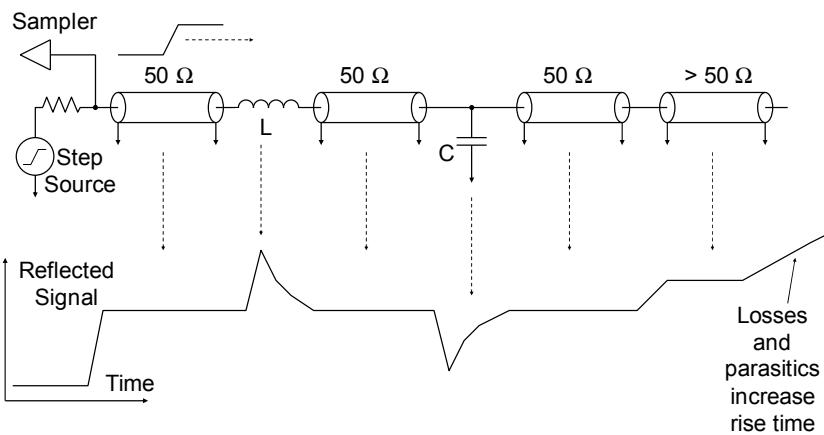

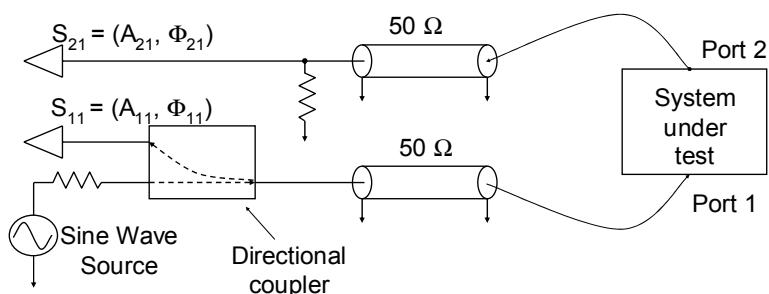

| 5.3.1 | Characterization Techniques        | 168 |

| 5.3.2 | Path Modeling                      | 172 |

| 5.3.3 | Power Distribution System Modeling | 175 |

|     |                |     |

|-----|----------------|-----|

| 5.4 | <i>Outlook</i> | 176 |

|-----|----------------|-----|

|  |                   |     |

|--|-------------------|-----|

|  | <i>References</i> | 177 |

|--|-------------------|-----|

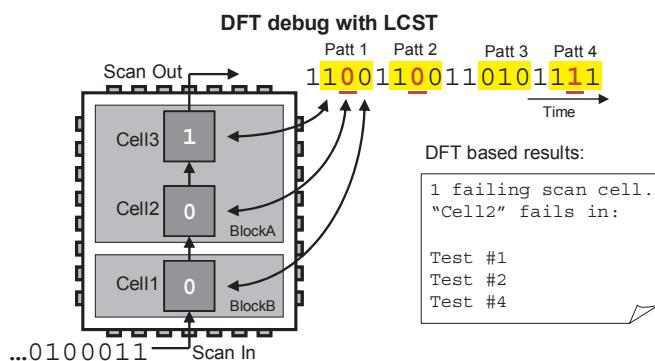

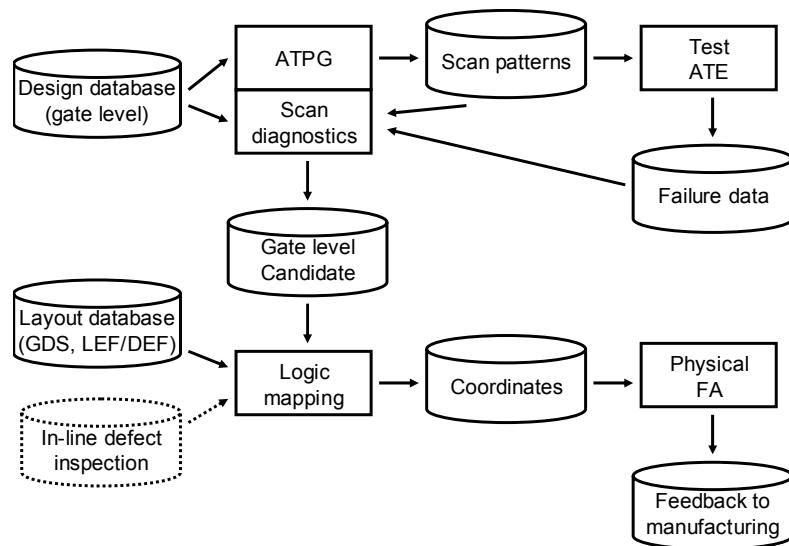

## **Chapter 6—DFT-Oriented, Low-Cost Testers 179**

by Al Crouch and Geir Eide

|     |                     |     |

|-----|---------------------|-----|

| 6.1 | <i>Introduction</i> | 180 |

|-----|---------------------|-----|

|       |                                           |     |

|-------|-------------------------------------------|-----|

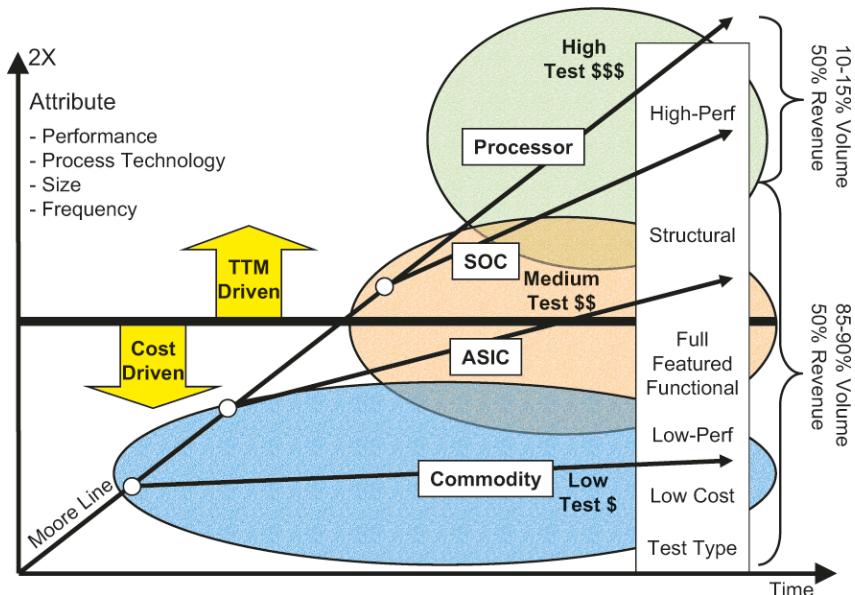

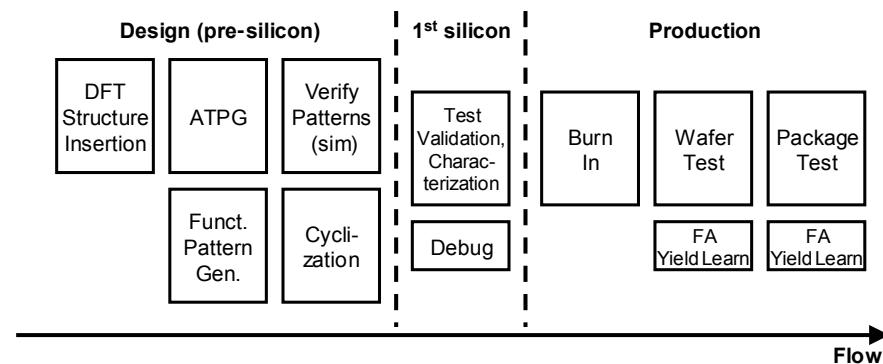

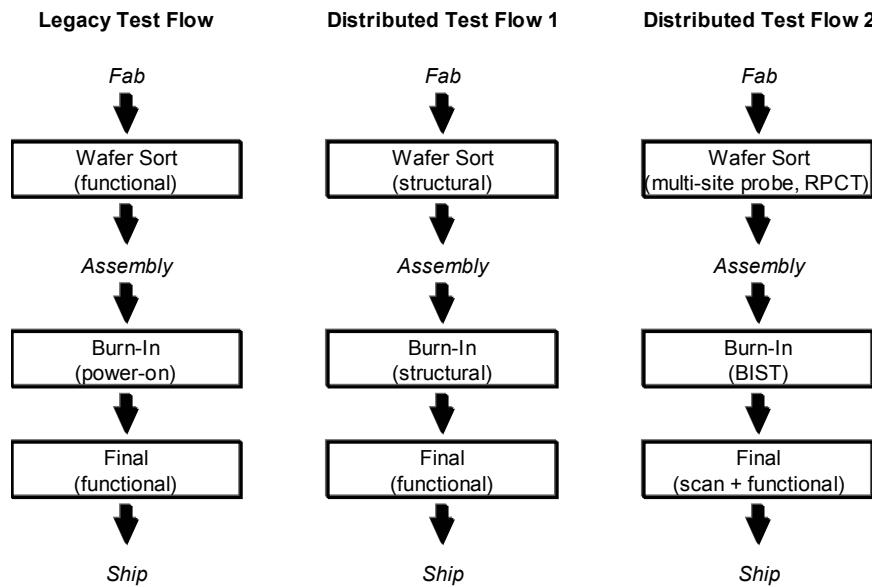

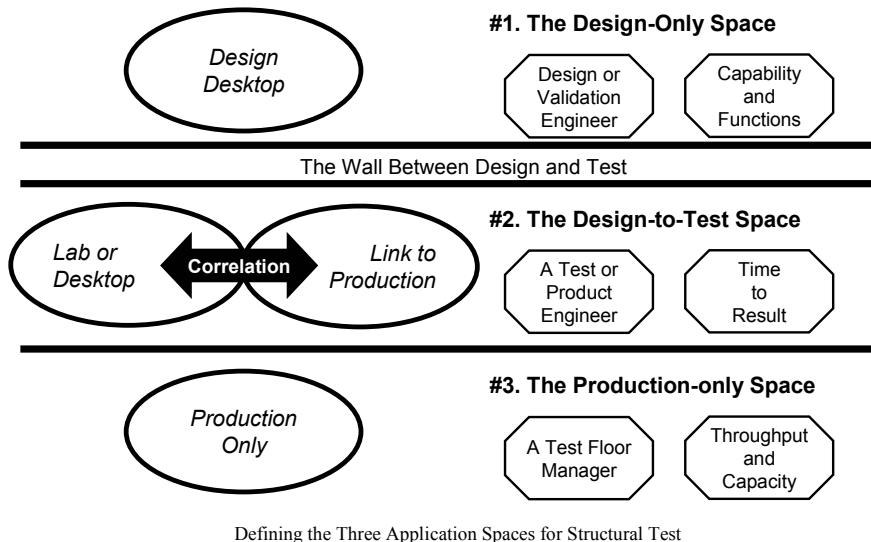

| 6.1.1 | Historical Perspective on Structural Test | 182 |

|-------|-------------------------------------------|-----|

|     |                                                        |     |

|-----|--------------------------------------------------------|-----|

| 6.2 | <i>Test Cost – the Chicken and the Low Cost Tester</i> | 184 |

|-----|--------------------------------------------------------|-----|

|       |                                            |     |

|-------|--------------------------------------------|-----|

| 6.2.1 | Schedule, Work Product, and Time-to-Market | 184 |

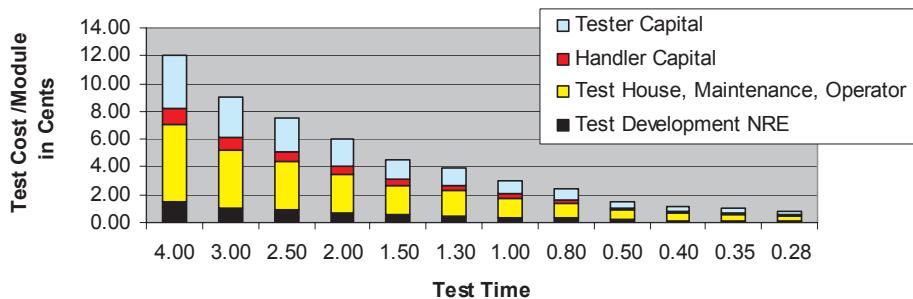

| 6.2.2 | Manufacturing Test Cost                    | 186 |

|     |                          |     |

|-----|--------------------------|-----|

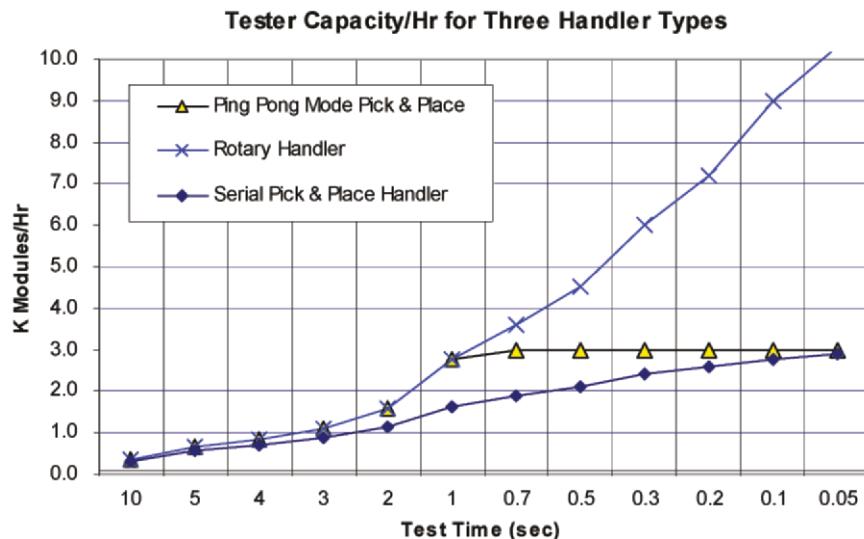

| 6.3 | <i>Tester Use Models</i> | 188 |

|-----|--------------------------|-----|

|     |                                      |     |

|-----|--------------------------------------|-----|

| 6.4 | <i>Why and When is DFT Low Cost?</i> | 190 |

|-----|--------------------------------------|-----|

|       |                                |     |

|-------|--------------------------------|-----|

| 6.4.1 | Functional vs. Structural Test | 190 |

|-------|--------------------------------|-----|

|       |                                                                   |

|-------|-------------------------------------------------------------------|

| 6.4.2 | Structural Test, DFT, and Cost 191                                |

| 6.4.3 | Test Development Automation 194                                   |

| 6.4.4 | Defect Coverage and Fault Models 196                              |

| 6.4.5 | DFT and First Silicon Validation 199                              |

| 6.4.6 | DFT and Device Characterization 201                               |

| 6.4.7 | DFT and Yield Learning 203                                        |

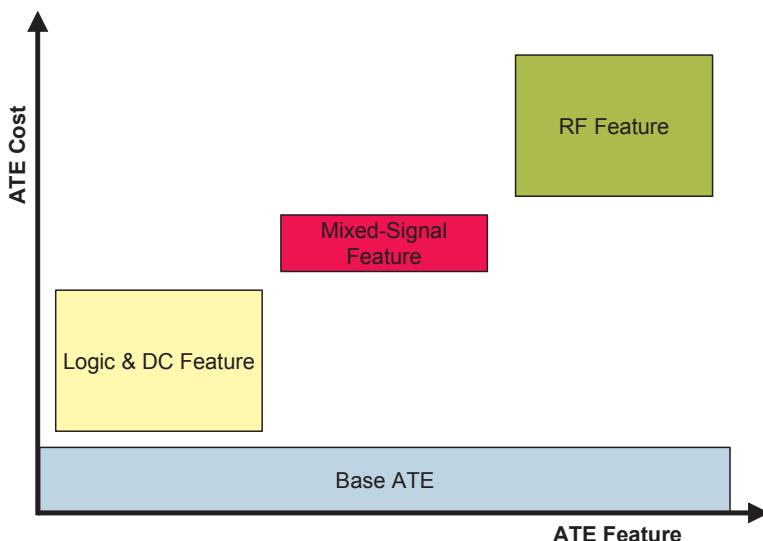

| 6.5   | <i>What does Low Cost have to do with the Tester?</i> 204         |

| 6.5.1 | What Makes a Tester Expensive? 204                                |

| 6.5.2 | Achieving Test Goals Without Precision, Accuracy, Flexibility 207 |

| 6.5.3 | The Next Step in Test Cost Reduction – the Test Interface 209     |

| 6.5.4 | The LCST is Not the Silver Bullet 212                             |

| 6.6   | <i>Life, the Universe, and Everything</i> 213                     |

|       | <i>References</i> 215                                             |

|       | <i>Recommended Reading</i> 216                                    |

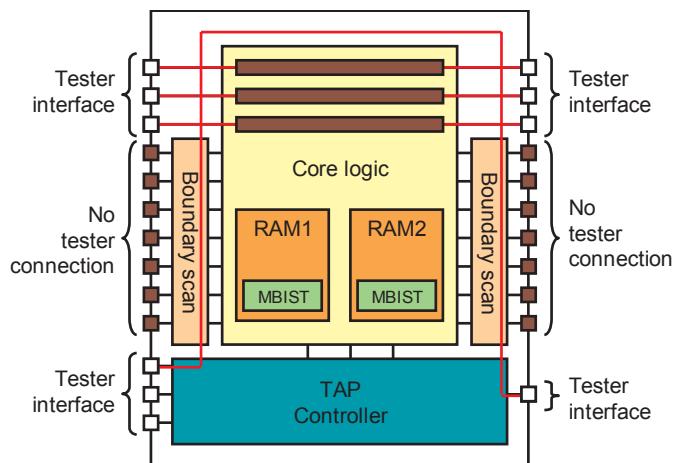

## **Chapter 7—Embedded Cores and System-on-Chip Testing 217**

by Rubin Parekhji

|       |                                                         |

|-------|---------------------------------------------------------|

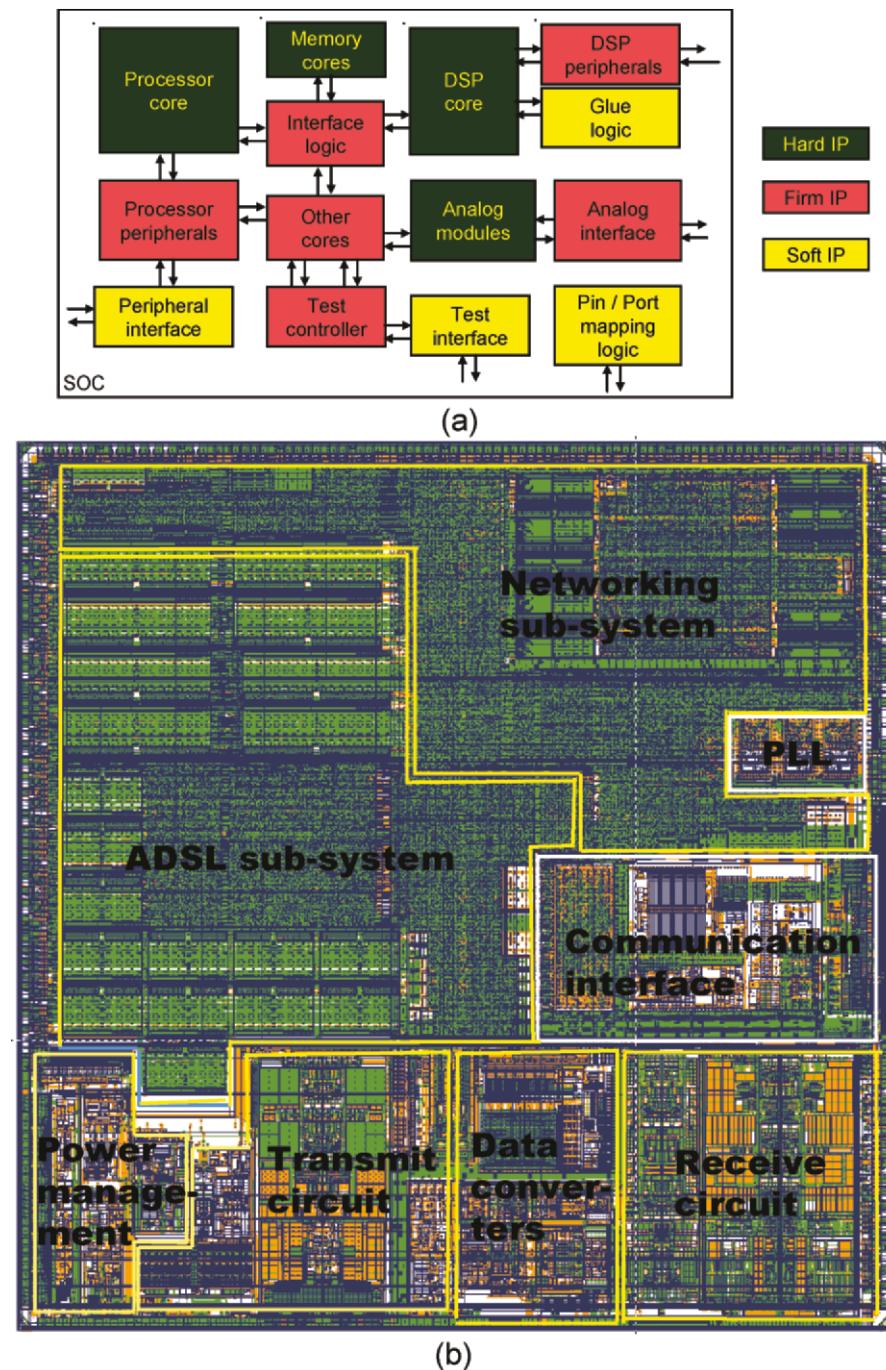

| 7.1   | <i>Embedded Cores and SOCs</i> 218                      |

| 7.2   | <i>Design and Test Paradigm with Cores and SOCs</i> 219 |

| 7.2.1 | Classification and Use of Embedded Cores 219            |

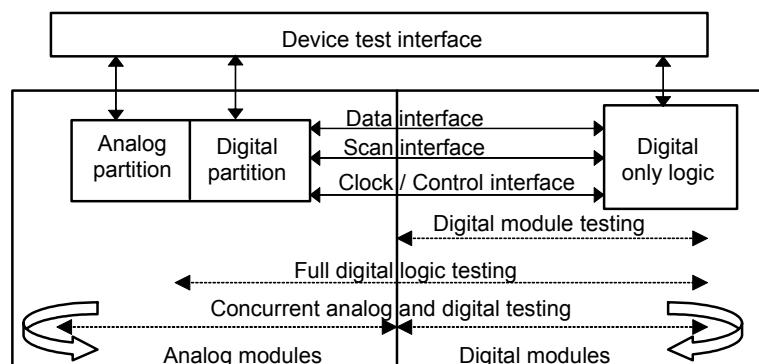

| 7.2.2 | Components of an SOC 220                                |

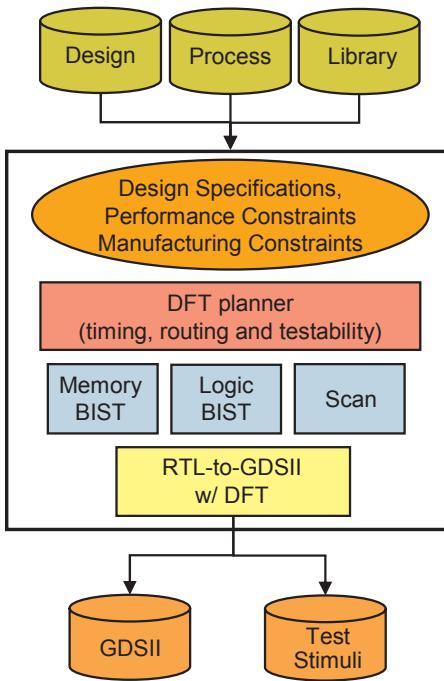

| 7.3   | <i>DFT for Embedded Cores and SOCs</i> 222              |

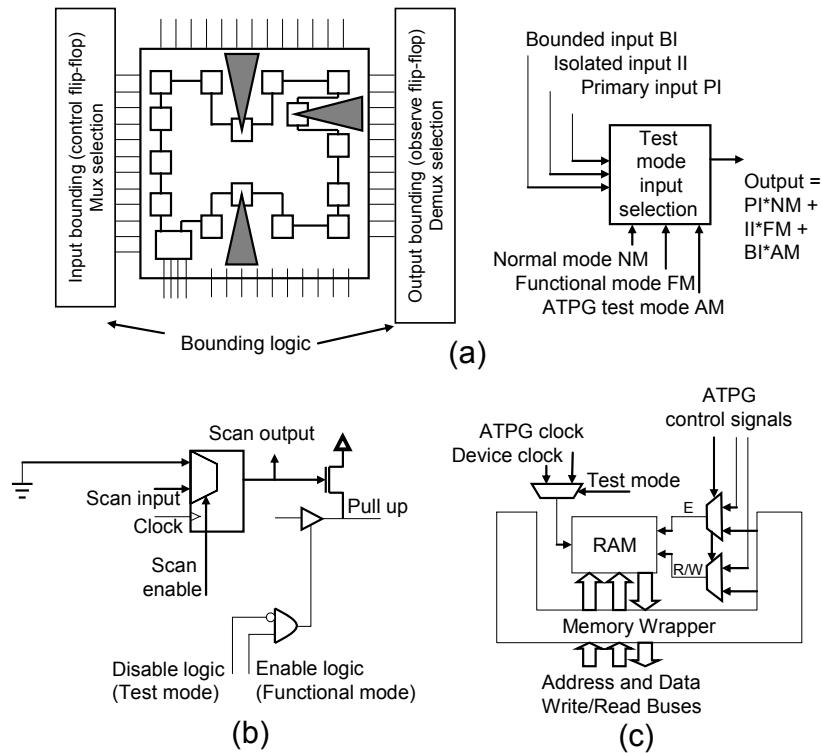

| 7.3.1 | Conventional DFT Techniques 222                         |

| 7.3.2 | DFT for Embedded Cores 223                              |

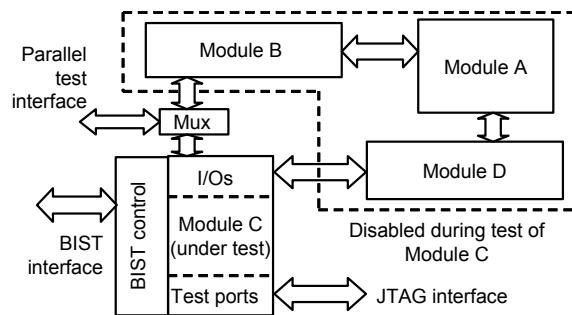

| 7.3.3 | DFT for SOCs 226                                        |

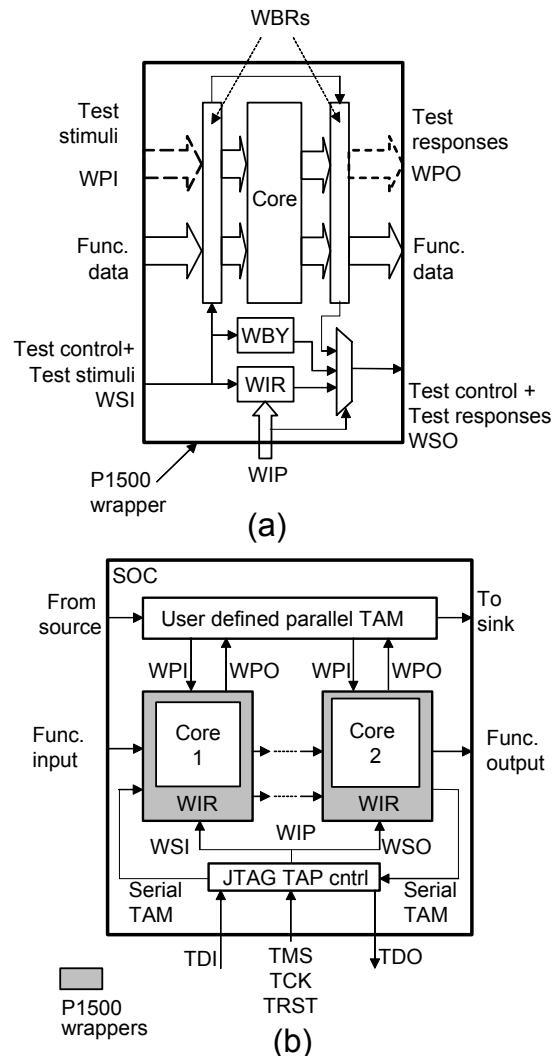

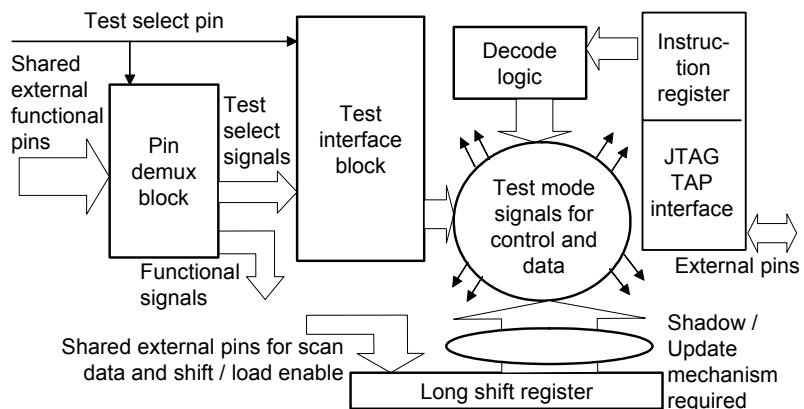

| 7.4   | <i>Test Access Mechanisms</i> 228                       |

| 7.4.1 | Test Interface Control Requirements 228                 |

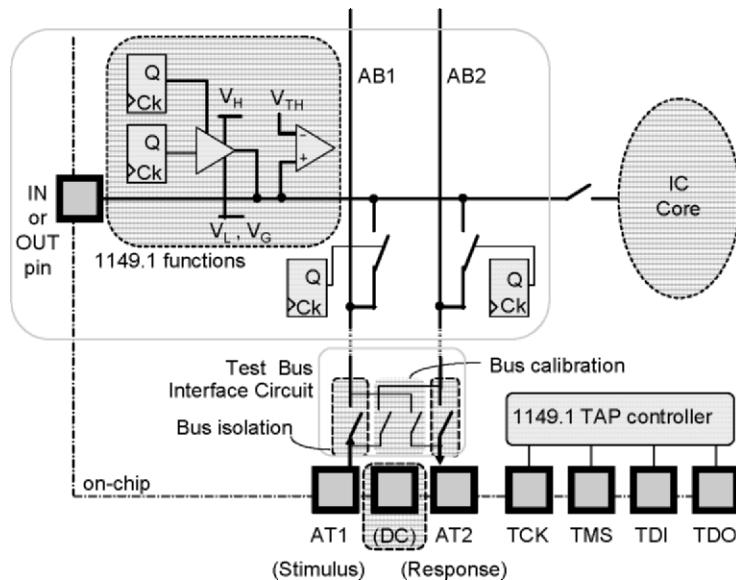

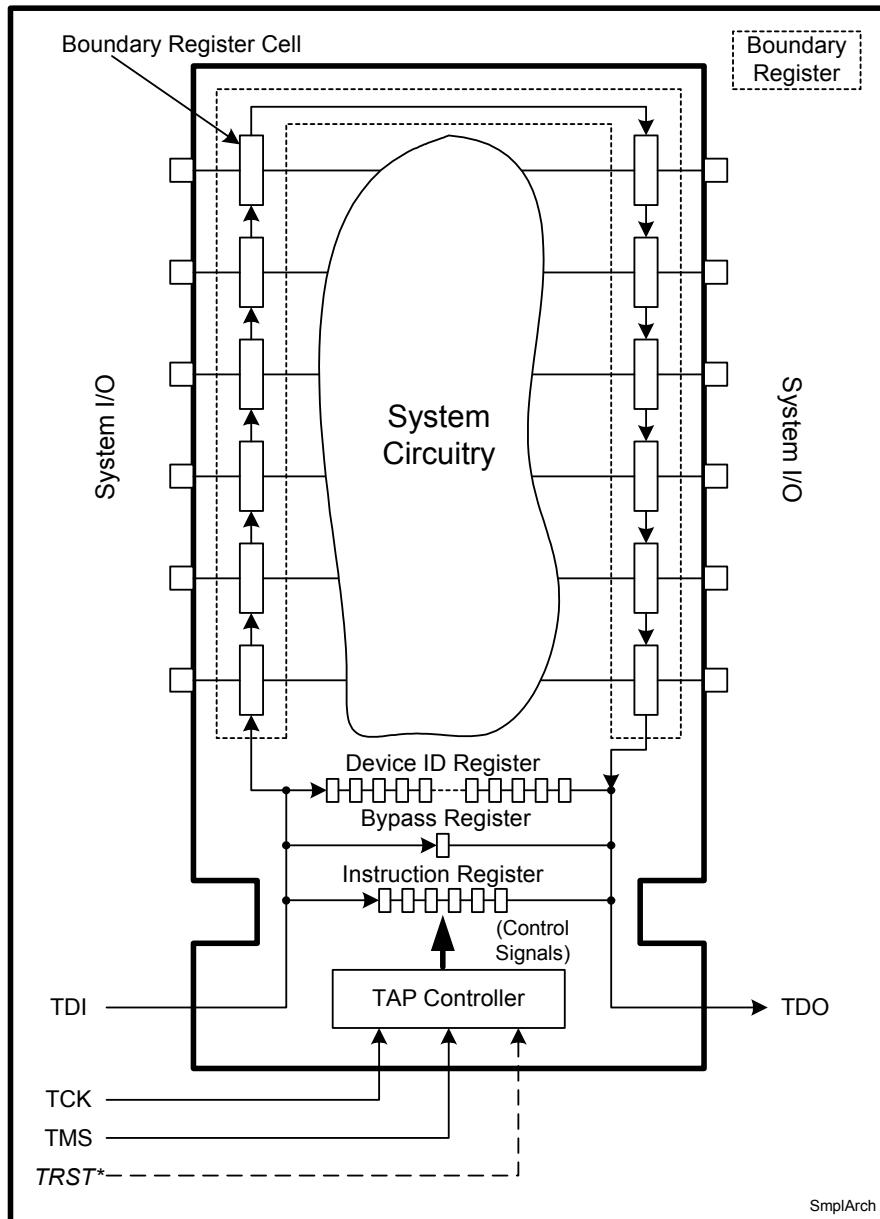

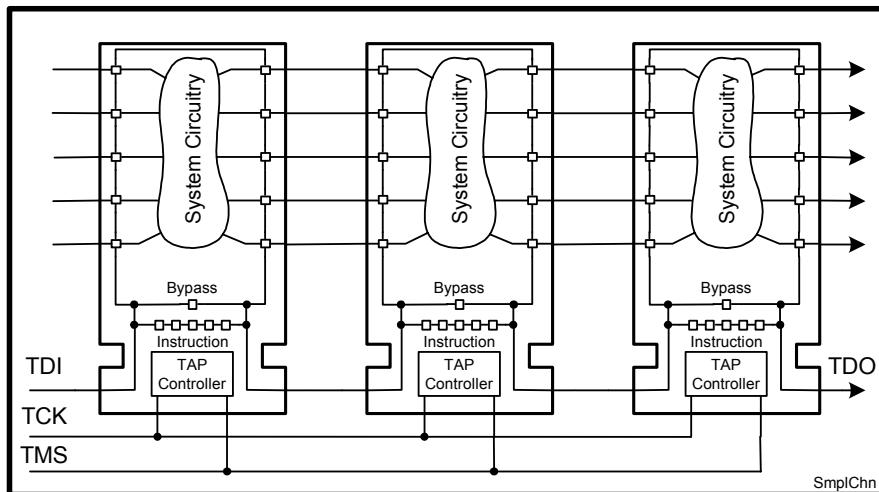

| 7.4.2 | 1149.1 JTAG TAP Interface 229                           |

| 7.4.3 | IEEE 1500 Standard Test Interface 230                   |

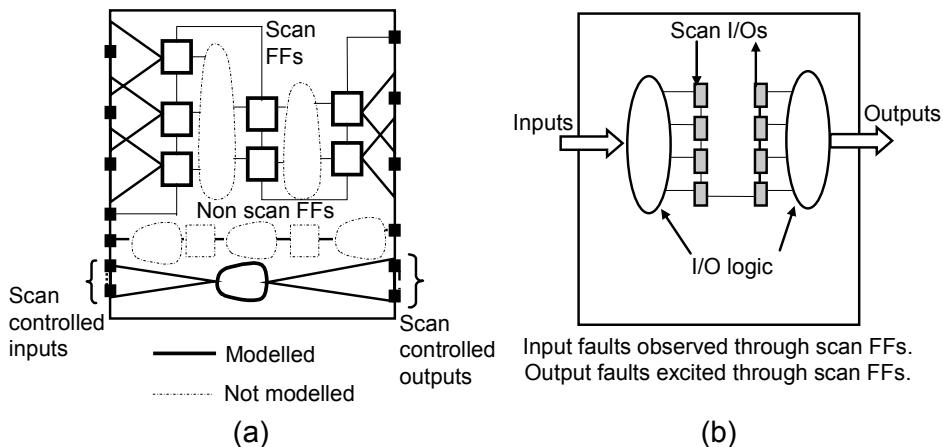

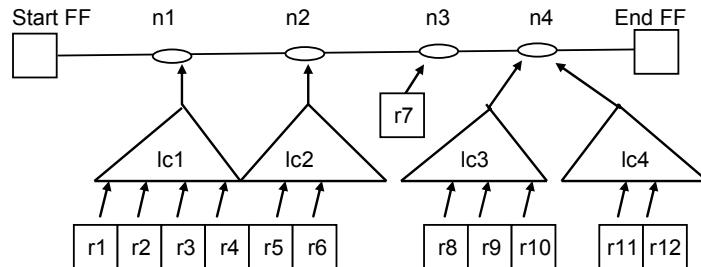

| 7.5   | <i>ATPG for Embedded Cores and SOCs</i> 232             |

| 7.5.1 | Limitations of Conventional ATPG 232                    |

| 7.5.2 | Use of Scan Models 233                                  |

| 7.5.3 | SOC Test Coverage Estimation 235                        |

| 7.6   | <i>SOC Test Modes</i> 236                               |

| 7.6.1 | Role of Test Modes 236                                  |

| 7.6.2 | Design and Categories of Test Modes 237                 |

| 7.6.3 | Test Pin Requirements 239                               |

| 7.6.4 | Test Mode Selection Mechanisms 239                      |

| 7.6.5 | Examples of Complex Test Modes 240                      |

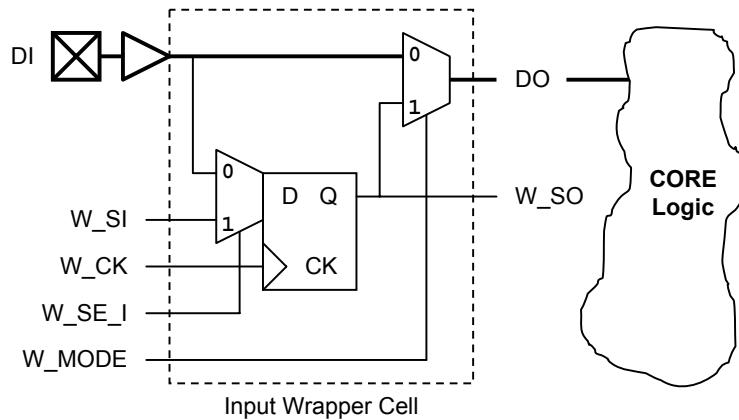

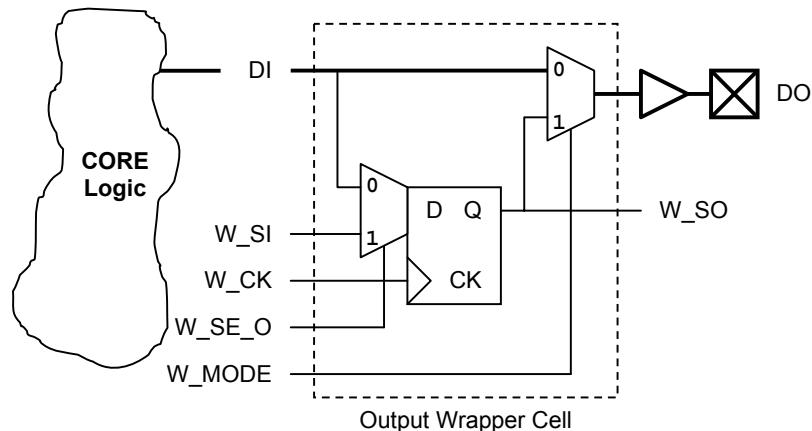

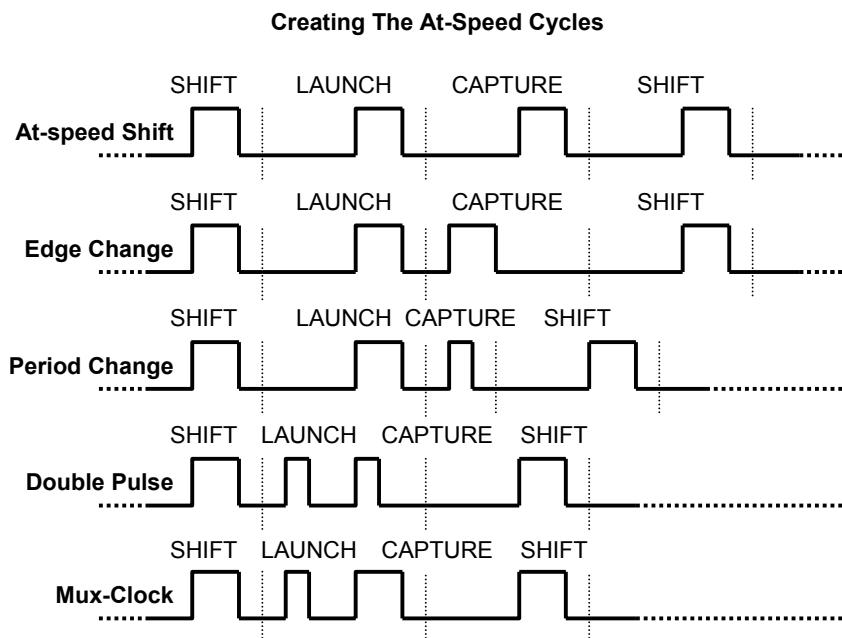

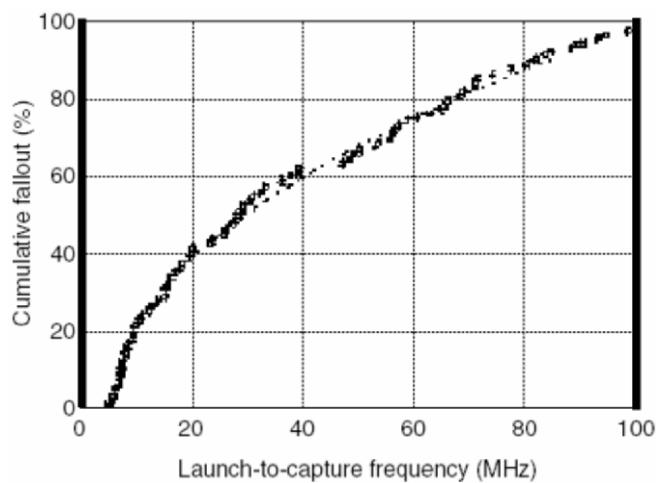

| 7.7   | <i>Design for At-speed Testing</i> 241                  |

| 7.7.1 | Need for At-speed Testing 241                           |

|                             |                                         |     |

|-----------------------------|-----------------------------------------|-----|

| 7.7.2                       | Requirements for SOC At-speed Test      | 242 |

| 7.7.3                       | Functional Tests for At-speed Testing   | 243 |

| 7.7.4                       | Scan Design and Scan Control            | 244 |

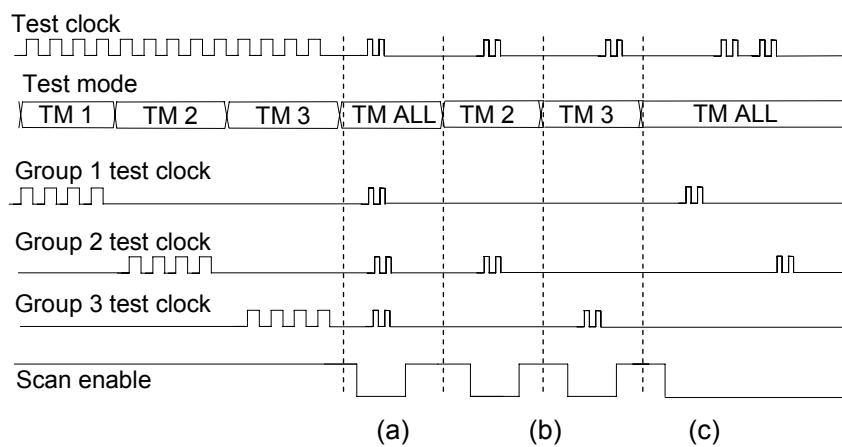

| 7.7.5                       | Clock Control for At-speed Testing      | 244 |

| 7.7.6                       | Handling Violating Paths                | 246 |

| 7.7.7                       | Test Control Through I/Os               | 247 |

| 7.7.8                       | Pattern Generation Techniques           | 247 |

| 7.8                         | <i>Design for Memory and Logic BIST</i> | 248 |

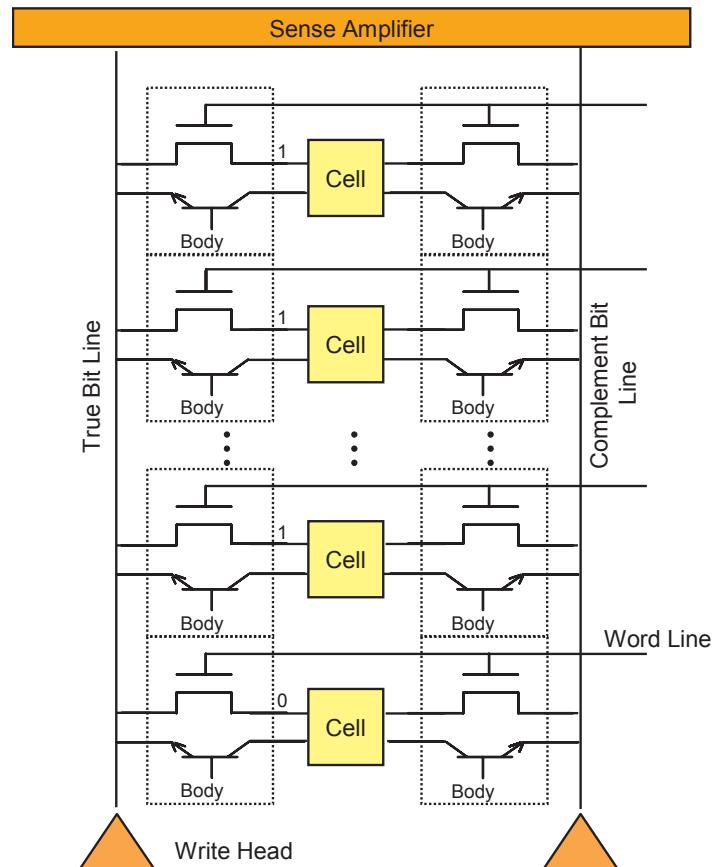

| 7.8.1                       | BIST Overview                           | 248 |

| 7.8.2                       | Design Techniques for Memory BIST       | 249 |

| 7.8.3                       | Design Techniques for Logic BIST        | 252 |

| 7.8.4                       | Functional BIST                         | 255 |

| 7.8.5                       | SOC BIST Architecture                   | 257 |

| 7.9                         | <i>Conclusion</i>                       | 257 |

| <i>Acknowledgements</i> 259 |                                         |     |

| <i>References</i> 259       |                                         |     |

## **Chapter 8—Embedded Memory Testing 263**

by R. Dean Adams

|                       |                                             |     |

|-----------------------|---------------------------------------------|-----|

| 8.1                   | <i>Introduction</i>                         | 263 |

| 8.2                   | <i>The Memory Design Under Test</i>         | 267 |

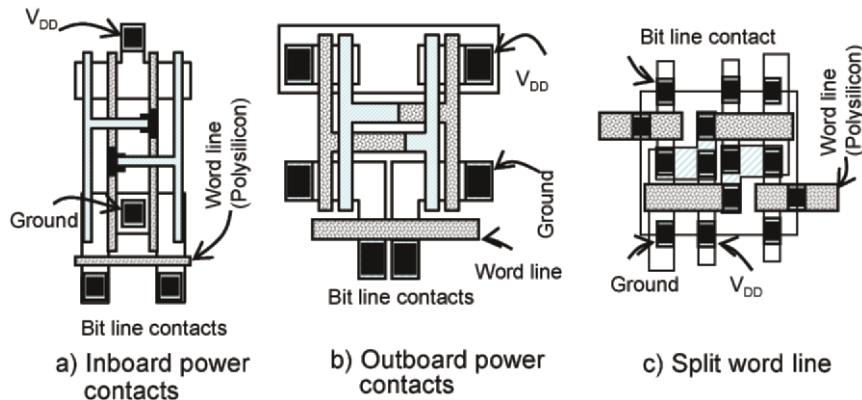

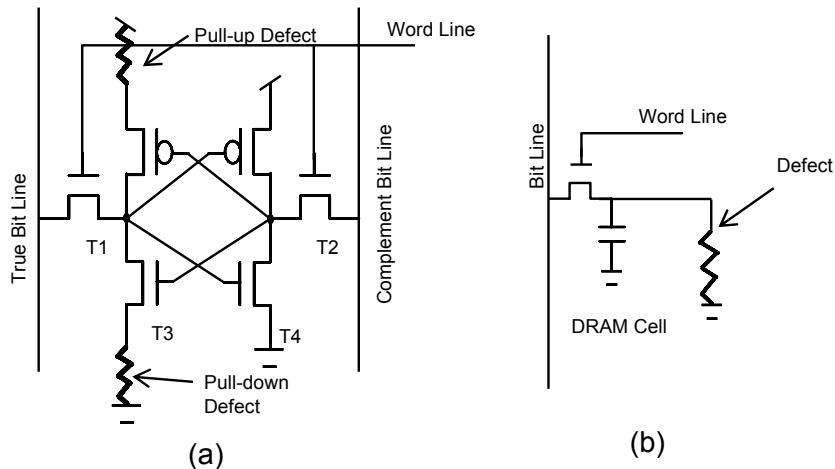

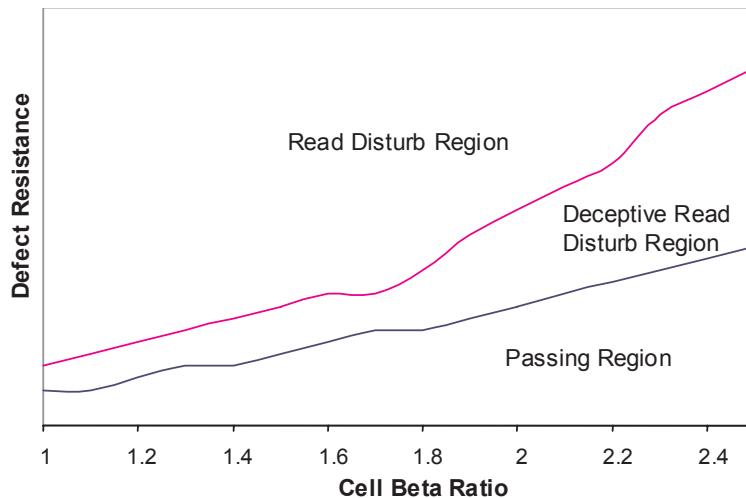

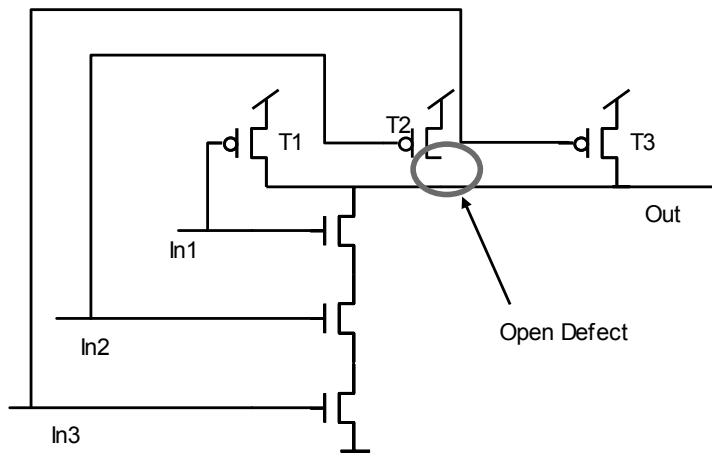

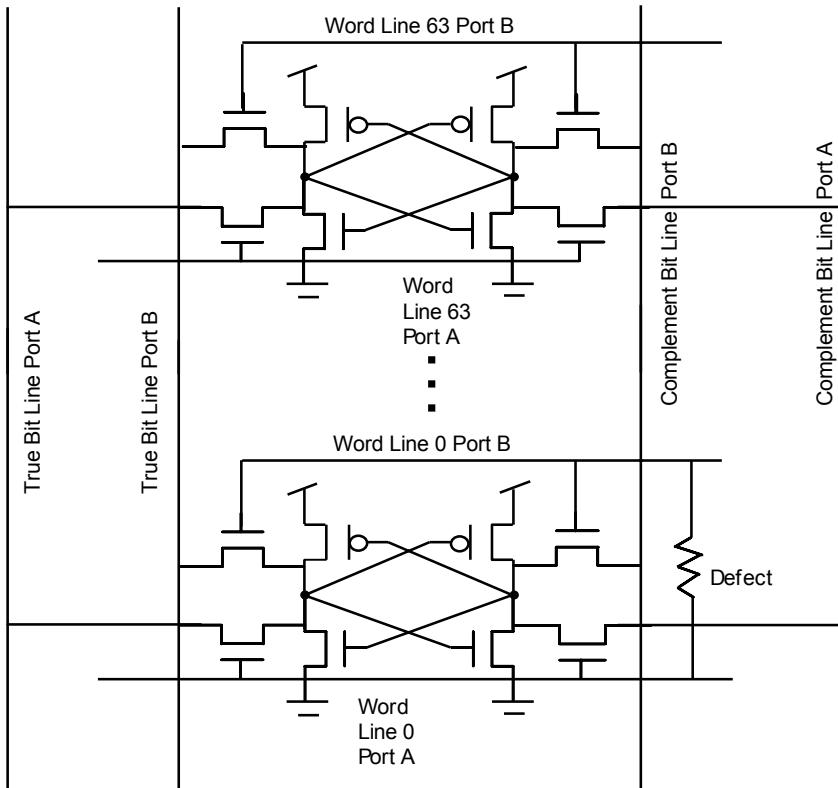

| 8.2.1                 | Static Memory                               | 268 |

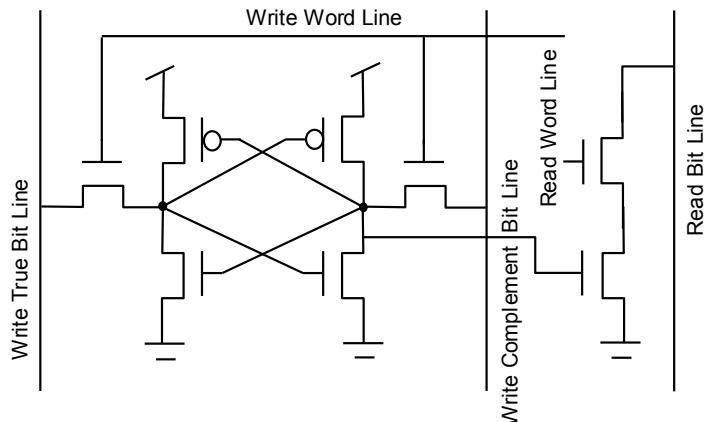

| 8.2.2                 | Register Files                              | 271 |

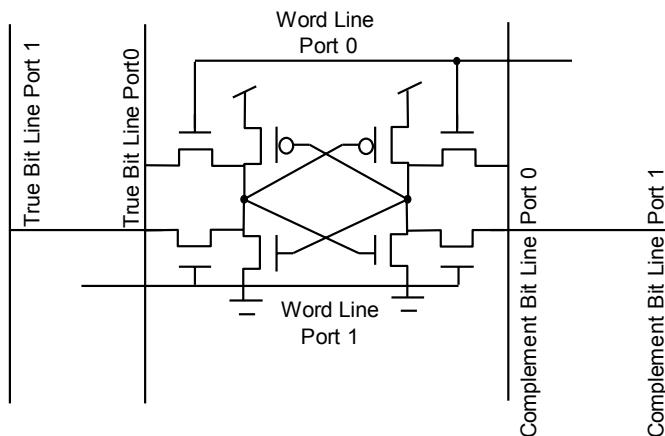

| 8.2.3                 | Dual Port Memories                          | 272 |

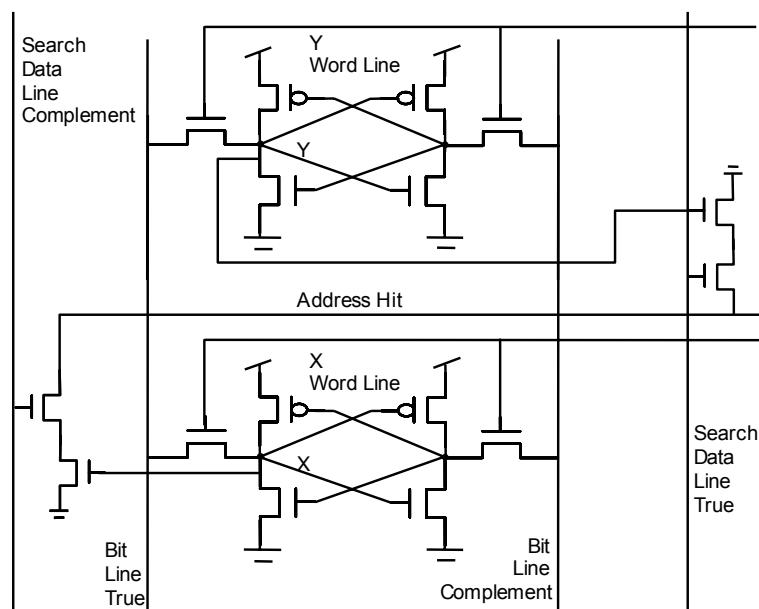

| 8.2.4                 | Content Addressable Memories                | 274 |

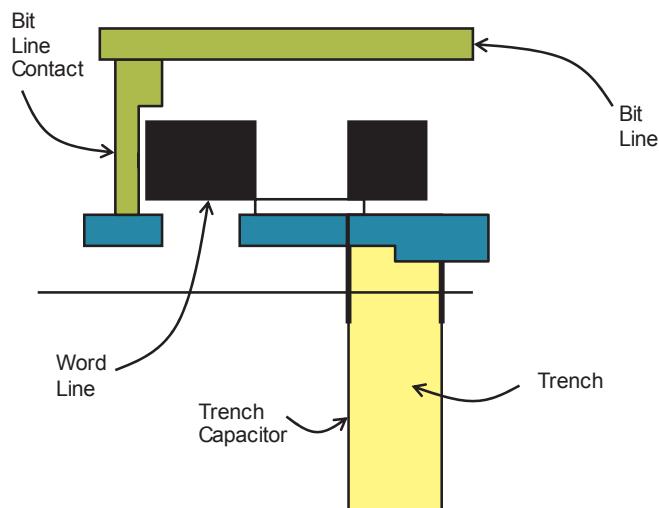

| 8.2.5                 | Dynamic Random Access Memories              | 274 |

| 8.3                   | <i>Memory Faults</i>                        | 276 |

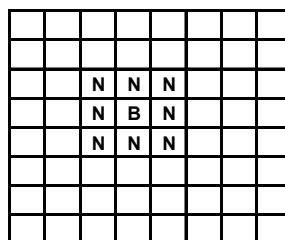

| 8.4                   | <i>Memory Test Patterns</i>                 | 282 |

| 8.4.1                 | Pattern Nomenclature                        | 283 |

| 8.4.2                 | Key March Patterns                          | 284 |

| 8.4.3                 | Memory Data Backgrounds                     | 287 |

| 8.4.4                 | CAM Test Patterns                           | 289 |

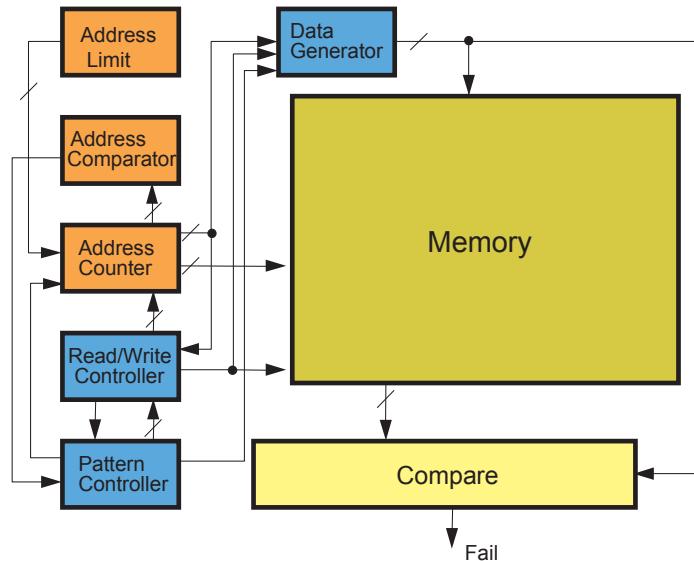

| 8.5                   | <i>Self Test</i>                            | 290 |

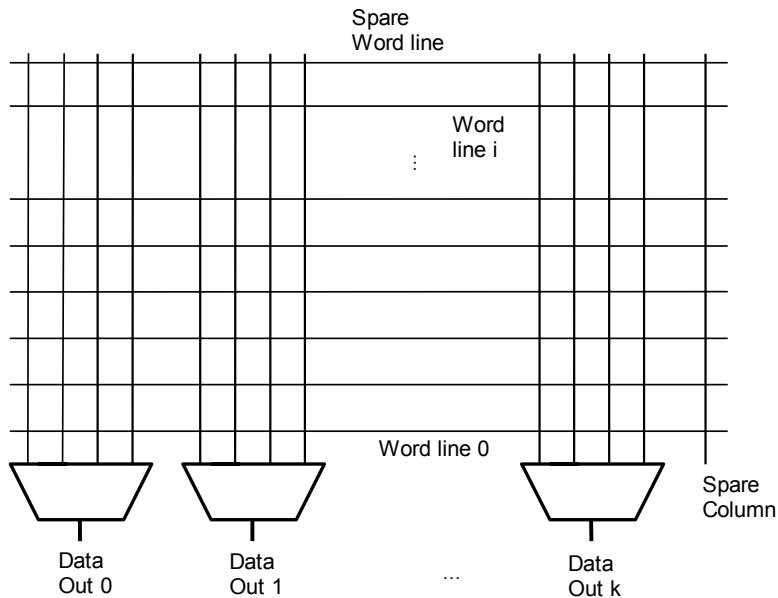

| 8.6                   | <i>Advanced Memories &amp; Technologies</i> | 295 |

| 8.7                   | <i>Conclusions</i>                          | 298 |

| <i>References</i> 298 |                                             |     |

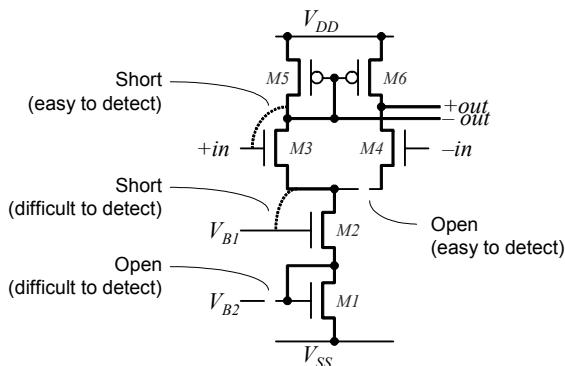

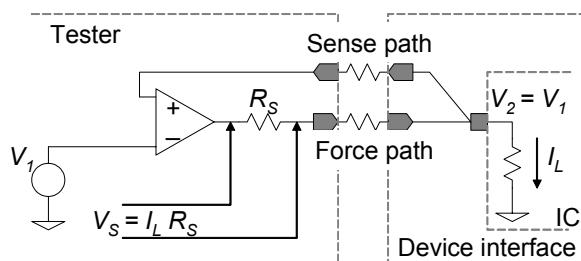

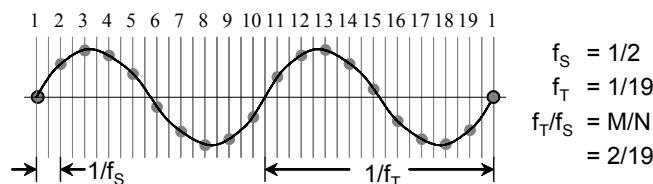

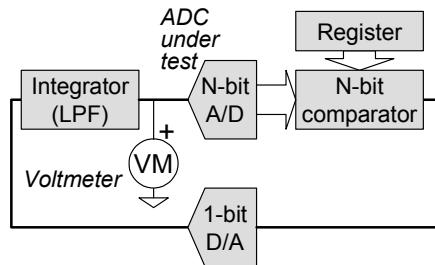

## **Chapter 9—Mixed-Signal Testing and DfT 301**

by Stephen Sunter

|       |                                |     |

|-------|--------------------------------|-----|

| 9.1   | <i>A Brief History</i>         | 302 |

| 9.1.1 | Functional vs. Structural Test | 303 |

|       |                                               |

|-------|-----------------------------------------------|

| 9.1.2 | Testing 304                                   |

| 9.1.3 | Design-for-Test 305                           |

| 9.1.4 | Fault Modeling 307                            |

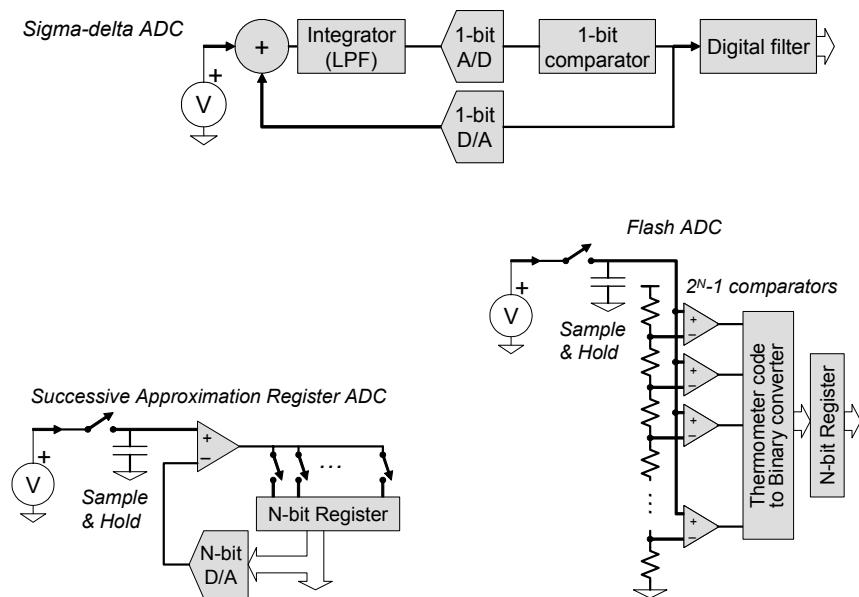

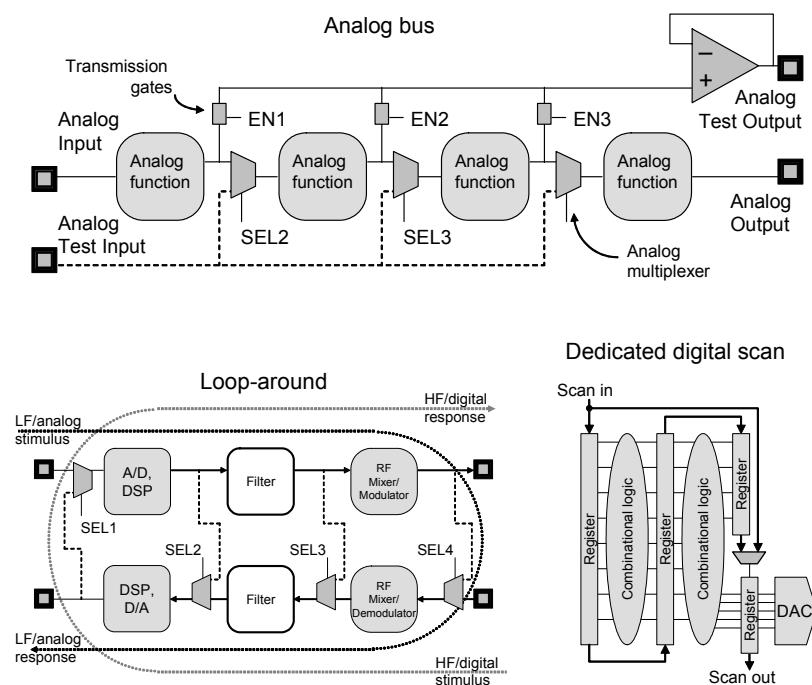

| 9.2   | <i>The State of the Art</i> 310               |

| 9.2.1 | Testing 311                                   |

| 9.2.2 | DfT 318                                       |

| 9.2.3 | Fault Modeling 320                            |

| 9.3   | <i>Advances in the Last 10 Years</i> 321      |

| 9.3.1 | Testing 322                                   |

| 9.3.2 | DfT 323                                       |

| 9.3.3 | Fault Modeling 329                            |

| 9.4   | <i>Emerging Techniques and Directions</i> 329 |

| 9.4.1 | Testing 330                                   |

| 9.4.2 | DfT 330                                       |

| 9.5   | <i>EDA Tools for Mixed-Signal Testing</i> 331 |

| 9.5.1 | Testing 331                                   |

| 9.5.2 | DfT 332                                       |

| 9.5.3 | Fault Modeling 332                            |

| 9.6   | <i>Future Directions</i> 332                  |

|       | <i>References</i> 334                         |

## **Chapter 10—RF Testing 337**

by Randy Wolf, Mustapha Slamani, John Ferrario and Jayendra Bhagat

|        |                                            |

|--------|--------------------------------------------|

| 10.1   | <i>Introduction</i> 337                    |

| 10.2   | <i>Testing RF ICs</i> 339                  |

| 10.2.1 | RF IC Categories 339                       |

| 10.2.2 | RF Test Challenges 340                     |

| 10.3   | <i>RF Test Cost Reduction Factors</i> 341  |

| 10.3.1 | Resources and Test Time Cost 342           |

| 10.3.2 | Handler 344                                |

| 10.4   | <i>Test Hardware</i> 346                   |

| 10.4.1 | Universal Test Board 347                   |

| 10.4.2 | RF Test Function Sub-Circuit Design 348    |

| 10.4.3 | Complete Test Architecture 353             |

| 10.5   | <i>Hardware Development Process</i> 356    |

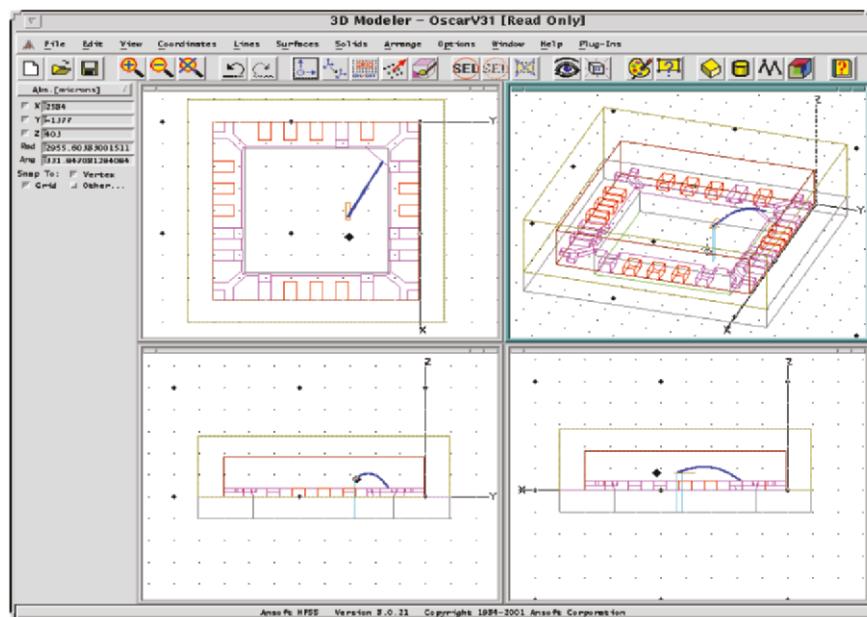

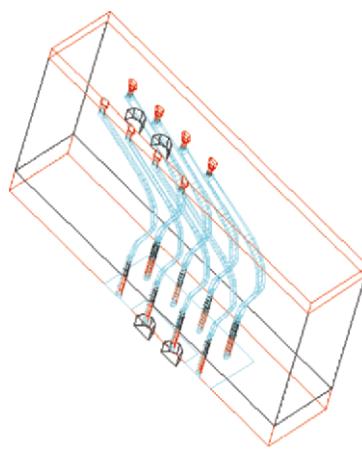

| 10.6   | <i>High Frequency Simulation Tools</i> 359 |

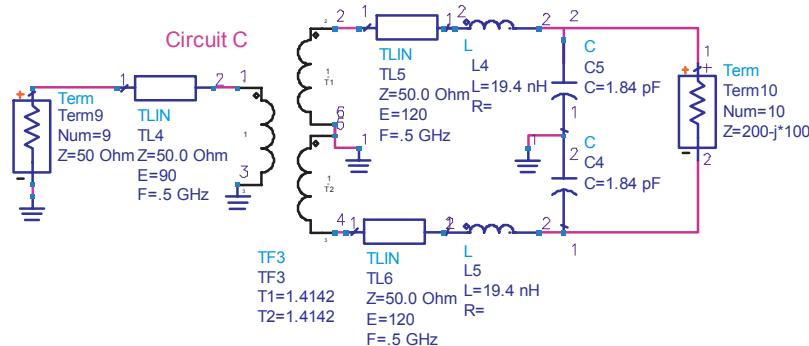

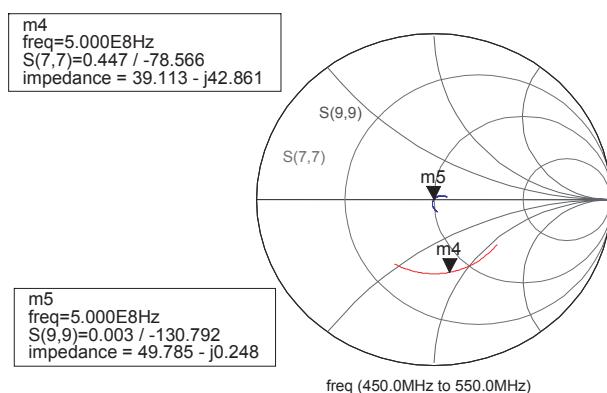

| 10.6.1 | Schematic Simulation 359                   |

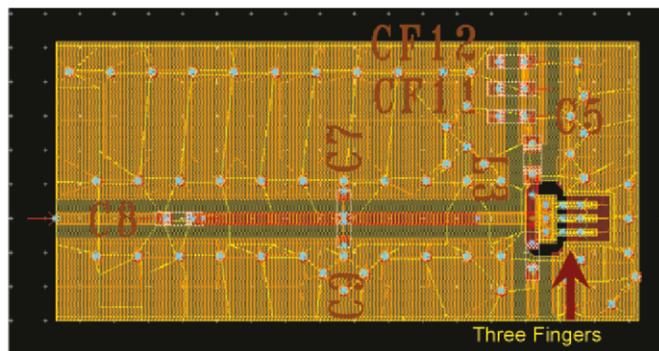

| 10.6.2 | 2.5D RF Board Simulation 362               |

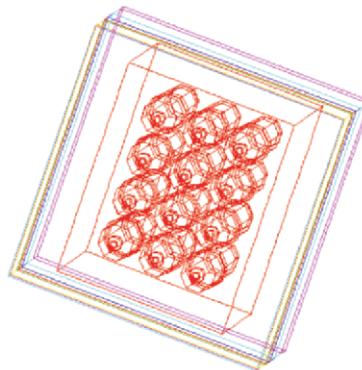

| 10.6.3 | 3D RF Socket and Package Modeling 365      |

*10.7 Device Under Test Interface 367*

10.7.1 Sockets 367

10.7.2 Wafer Probes 367

*10.8 Conclusions 368**Acknowledgements 368**References 368***Chapter 11—Loaded Board Testing 371**

by Kenneth P. Parker

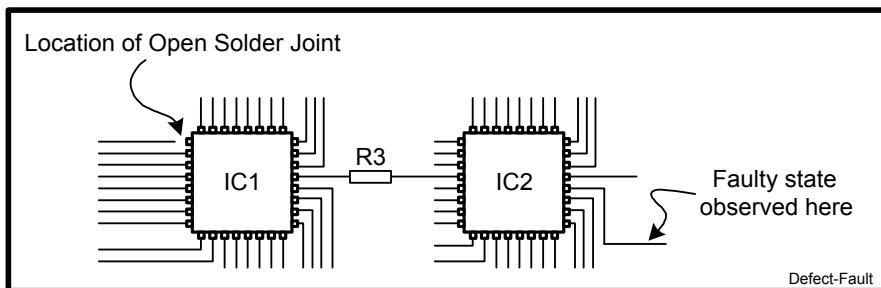

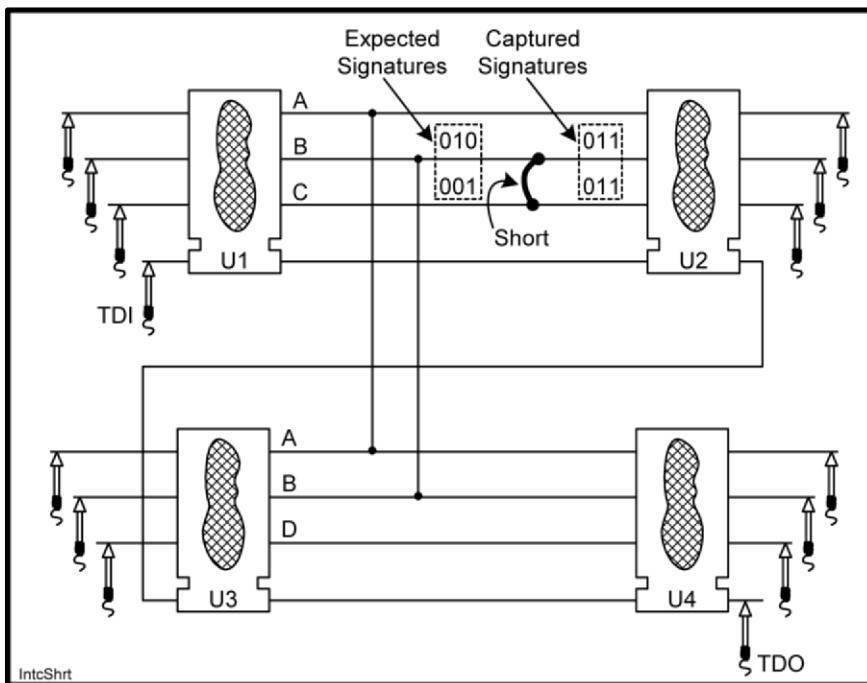

*11.1 The Defect Space at Board Test 372*

11.1.1 What is a “Defect”? 372

11.1.2 What is a “Fault”? 373

11.1.3 The “PCOLA/SOQ” Model 374

11.1.4 Test Coverage 376

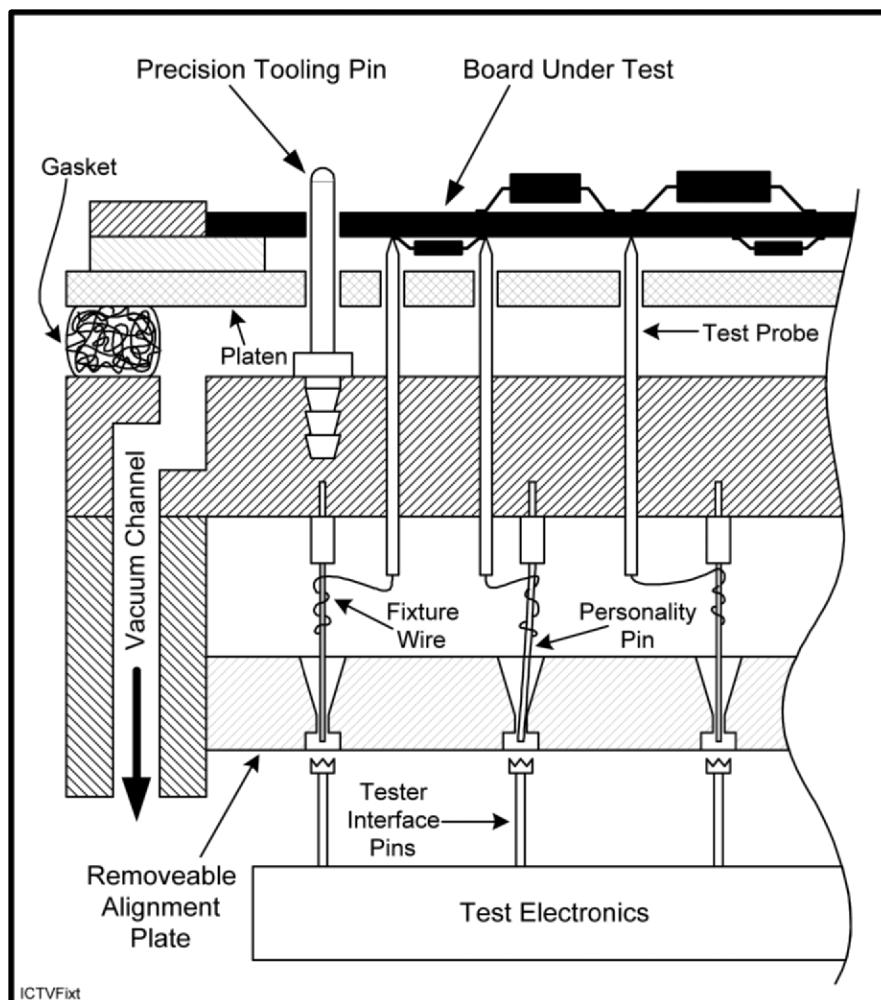

*11.2 In-Circuit Test (ICT) 378*

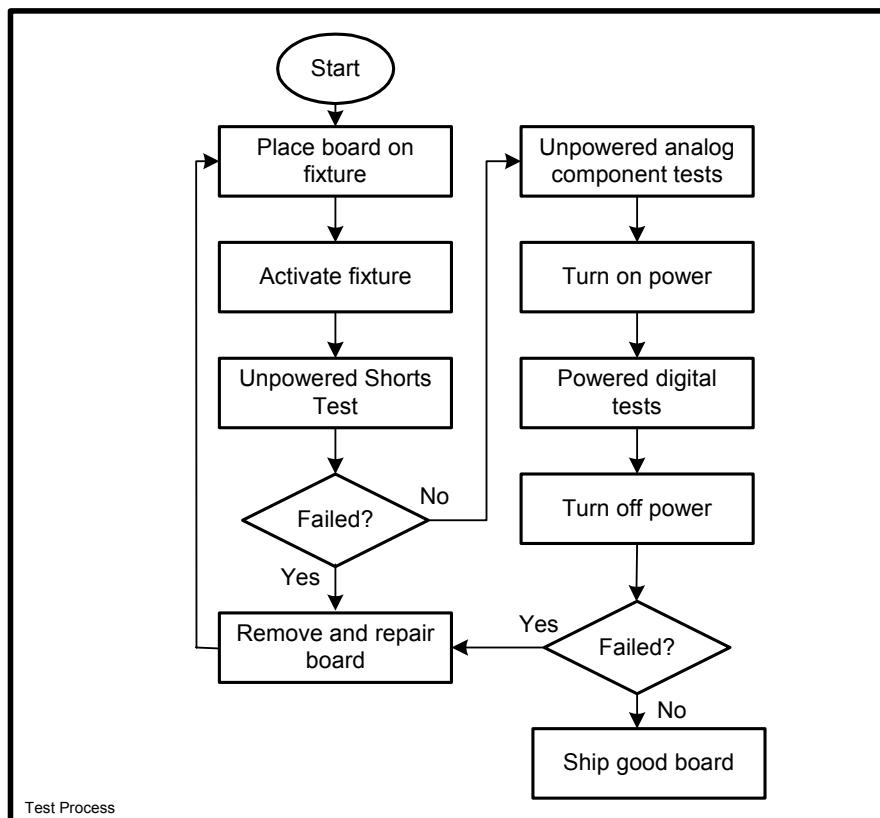

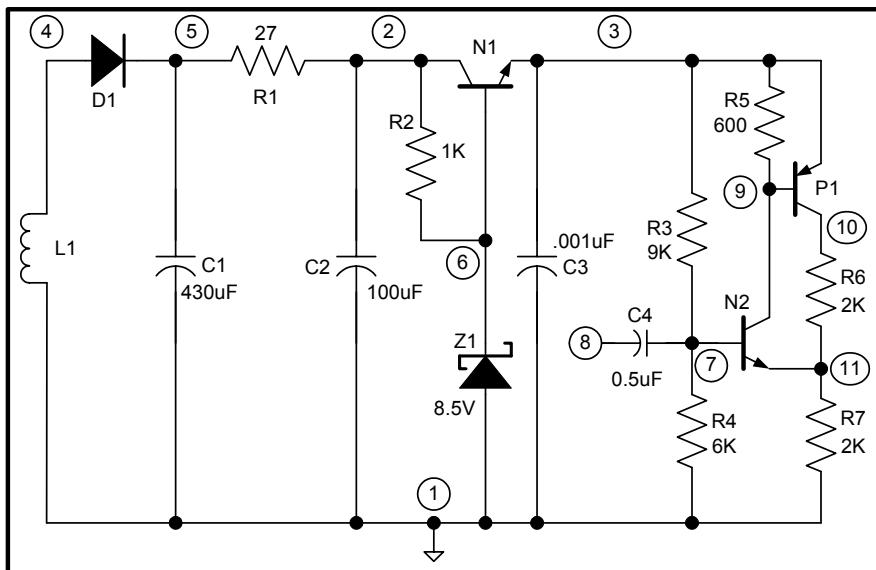

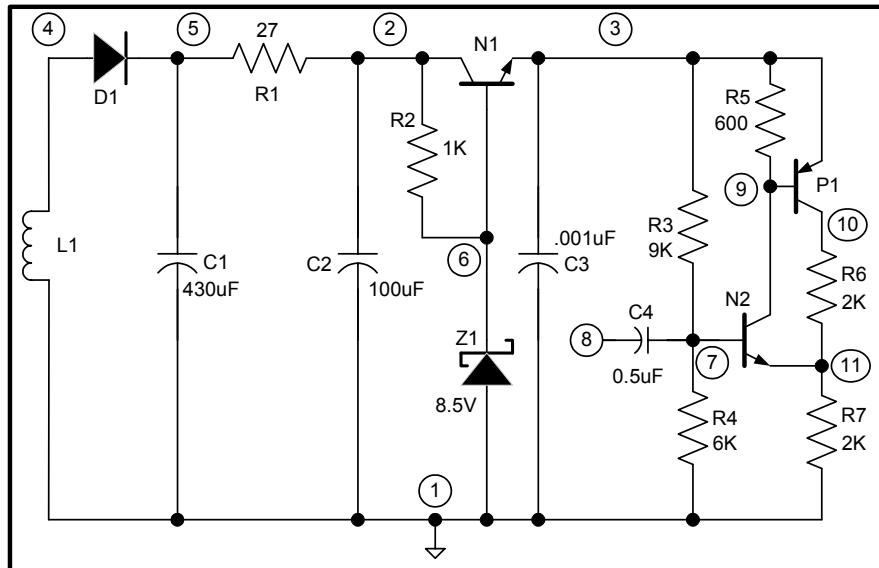

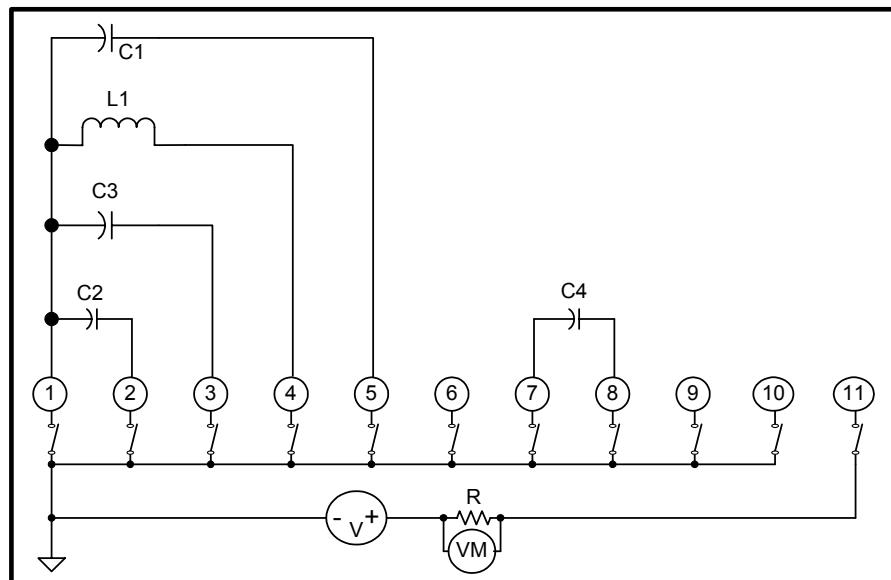

11.2.1 Unpowered Shorts Tests 380

11.2.2 Unpowered Analog Tests 384

11.2.3 Powered In-Circuit Digital Tests 391

11.2.4 Boundary-Scan Tests 394

11.2.5 Powered Mixed-Signal Tests 397

11.2.6 Pros and Cons of ICT 398

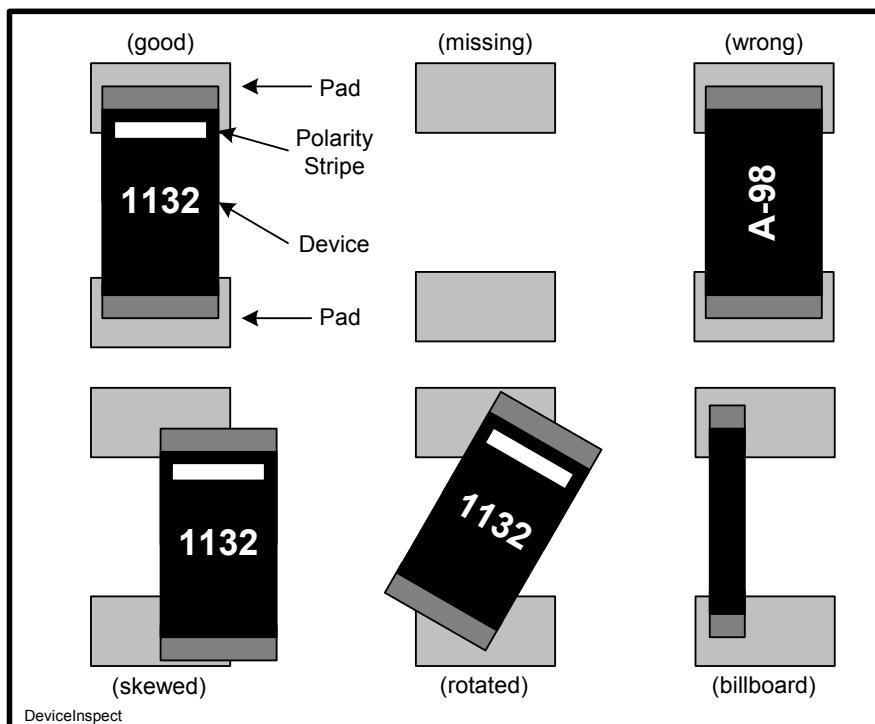

*11.3 Loaded Board Inspection Systems 399*

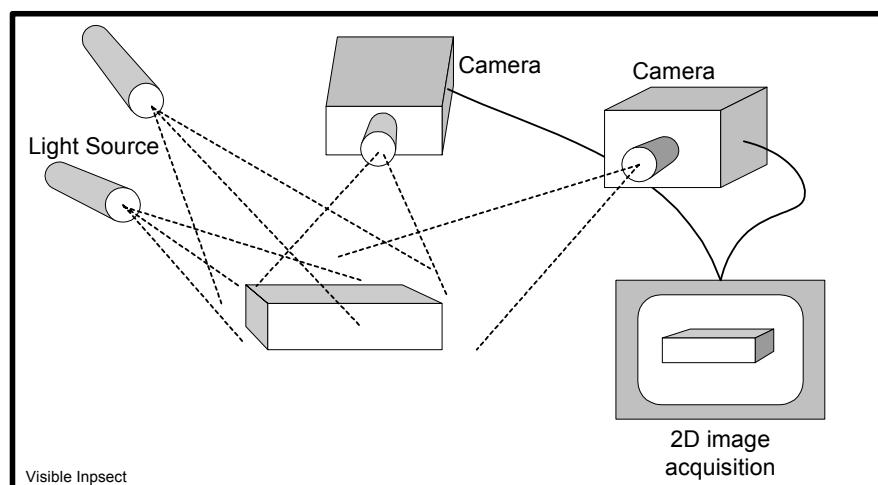

11.3.1 Automatic Optical Inspection (AOI) 400

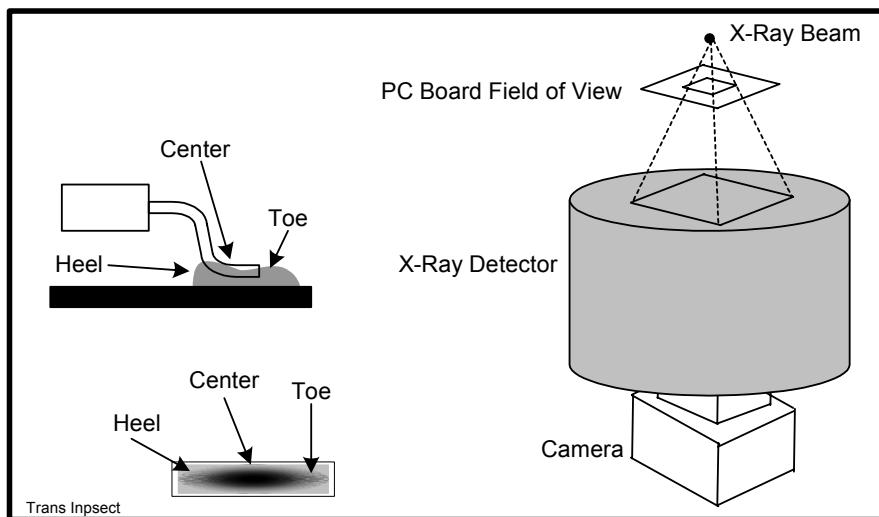

11.3.2 Automatic X-Ray Inspection (AXI) 402

11.3.3 Pros and Cons of Inspection 404

*11.4 The Future of Board Test 405**References 406***Index 407**

# Foreword

by Vishwani D. Agrawal

About five years ago, I was engaged in co-authoring a text-book on electronic testing for the *Frontiers in Electronic Testing* Book Series. We had to make some difficult decisions about what to include and what not to include. A text-book must contain all or most of the essentials of the established practices, and should not exceed a convenient, somewhat “standard,” size. Those requirements do not leave room for what are the needs of the future and many of the groundbreaking developments. As a result, stuck-at tests win over delay tests, conventional analog tests are selected while radio frequency testing is ignored, and defect-oriented testing of nanometer devices is barely mentioned. So, no sooner the text-book was completed, I developed a feeling of discomfort about leaving out a vast amount of material on testing that could have been included.

What I have said about the text-book in the *Frontiers Series* applies to other text-books as well. As years go by the gap between those text-books and what is considered up-to-date has been widening. There is a definite need for documenting the advances in testing. It is for these reasons that I find the work of this edited volume by Dimitris Gizopoulos and his team of authors to be significant and timely.

The field of modern electronic testing can be regarded as about half a century old. Two things are obvious. First, the field has gained maturity. We have well established conferences and workshops all over the world organized by IEEE

Computer Society's Test Technology Technical Council. The attendance at these meeting remained quite steady even through down turns of the semiconductor industry. There is an over ten years old *Journal of Electronic Testing: Theory and Applications* that is entirely devoted to testing. The IEEE Computer Society has been publishing the *IEEE Design & Test of Computers* magazine for over two decades. Clearly, the field of electronic testing has developed a core but, and this is my second point, the field of testing now has a divergence of specializations. It is this divergence that an advanced book like this one captures.

While no one argues that the idea of an advanced book is good, there are problems with its implementation. Specialization demands experts and no single expert feels competent to write about all areas. Dimitris Gizopoulos has gathered a team of experts to write this book. Hence, the book provides, besides novel test methodologies, a collective insight into the emerging aspects of testing. This, I think, is beneficial to practicing engineers and researchers both of whom must stay at the forefront of technology.

Let me share a few of these insights with the reader. In Chapter 1, Rob Aiken states a theme, “*Defect-oriented tests for digital logic typically include comprehensive structural logic tests, a current test ... and at-speed tests. All these tests share the property that they measure some aspect of circuit behavior that is directly affected by defects,...*” before expanding on it.

In Chapter 2, Jaume Segura, Charles Hawkins and Jerry Soden give a motivation for statistical test methods by saying, “*Deep submicron structures don't affect test and diagnosis just because they are small. They primarily impact test because the manufacturing parameters are not tightly controlled as they were in the past.*”

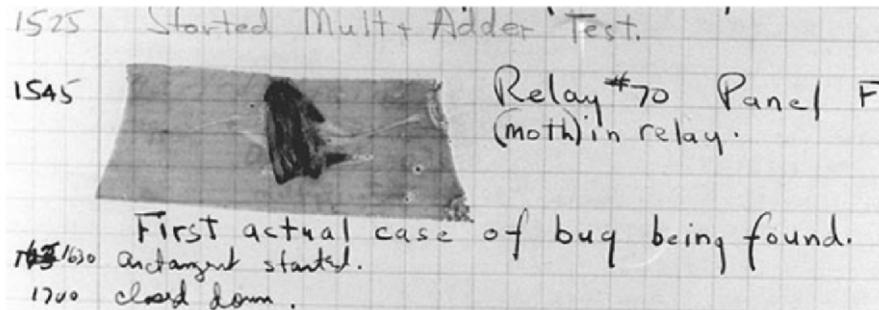

Doug Josephson and Bob Gottlieb share their insights on silicon debug in Chapter 3. According to them, “*... test cases that are interesting for electrical validation are likely very different from those that are interesting for functional validation. For the ALU example, a CMOS dynamic circuit implementation may perform differently electrically if there are two add instructions executed in consecutive clock cycles than it would if there was a long period of inactivity between the add instructions ... from a functional validation point of view, these cases would be identical.*” Besides, I was fascinated with, “*An interesting example of “debugging” was in 1945 when a computer failure was traced down to a moth that was caught in a relay between contacts (Figure 3-1).*”

Discussing delay testing in Chapter 4, Adam Cron candidly admits, “*Much of this “information” about the prominent defect types is from informal discussions with engineers and researchers “in the trenches” .*”

Continuing on the theme of high-speed test in Chapter 5, Wolfgang Maichen points out, “*... any chain is only as strong as its weakest link. In this case it means that even the best performing, highest bandwidth, most accurate tester will fail to reliably sort good devices from bad ones or give accurate characterization results if the connection between tester and device – i.e. the interface – does not perform equally well ...*”

Chapter 6 on low-cost testers, written by Al Crouch and Geir Eide, is particularly timely in view of the rising costs of testing and the test equipment. This subject is almost always found missing from the usual text-books.

Today, it is unthinkable that a VLSI chip will be designed without embedded cores. In Chapter 7, Rubin Parekhji points out the problems with applying the conventional test methodology to core-based System-on-Chip (SOC). He goes on to provide test solutions that use the conventional test methods and the IEEE standards like 1149.1 and 1500.

A majority of the embedded cores are memories. Dean Adams, the author of Chapter 8, describes the design for test structures and test methods in detail. The following sentence in that chapter very well represents the nature of the memory test problem and its solution: *“All of the testing and redundancy calculation must be performed by built-in self-test logic embedded on chip around the memory structures. The BIST must be implemented and integrated on the chip through the use of EDA tools which understand the memories, the process, and the physical constraints of the chip.”*

It is often said that testing of 10% analog circuitry of a mixed-signal device may contribute to 90% of the total test cost. Clearly, analog testing cannot be ignored. In Chapter 9, Stephen Sunter gives a complete coverage of analog test methodologies, fault modeling, design for testability including the IEEE 1149.4 test bus standard, and test tools.

For many digital test professionals radio frequency (RF) testing, mostly neglected during education, remains an unavoidable mystery. The wireless communication systems of today require SOCs that contain RF components. What I said above about the cost of analog testing is even more applicable to RF testing. Chapter 10 by Randy Wolf, Mustapha Slamani, John Ferrario and Jayendra Bhagat contains a comprehensive discussion on RF testing methods and tools that very few books on testing can boast of.

If we consider the varieties and the total number of printed circuit boards (PCB) manufactured in the world it will immediately become evident that the PCB test problem is no less important than the semiconductor device test problem. In Chapter 11, Kenneth Parker gives a detailed account of the PCB test methods oriented toward the board-specific defects, the conventional in-circuit testing (ICT), and the modern IEEE 1149.1 boundary-scan testing.

Considering that the eleven chapters of this book were written by different authors, the tasks of technical coordination and that of providing a uniform formatting and flow are not easy ones. I thank Dimitris Gizopoulos for his untiring effort on getting all chapters together and an excellent technical editing. This latest addition to the *Frontiers Series* is destined to serve an important role. However, “*Advances*” in the title of the book suggests that we keep track of the test technology as it advances. It is my hope that we will bring out future volumes of this type.

Vishwani D. Agrawal

*Consulting Editor*

*Frontiers in Electronic Testing Book Series*

September 2005

# Preface

*Electronic circuits testing* has always been a very vibrant area of scientific research and development. The engineering adventure of discovering whether an integrated circuit has been properly manufactured and operates in accordance with its specifications advanced significantly over the last few decades. Every new manufacturing technology generation—already supporting feature sizes of a few tens of nanometers today—brings with it enhanced functionality, more transistors per unit area, elevated performance and reduced power consumption at lower costs per circuit unit. On the other hand, each shrinking manufacturing process also carries new types of failure mechanisms and defects which were either unknown or of less importance in previous generations of larger geometries and lower operating frequencies. Each integrated circuit generation packs more modules of improved or completely new functionality (digital logic, memories, analog and mixed-signal as well as radio frequency components) into half or even less of the space; as a consequence, improved or completely new testing techniques are necessary for them. To make matters worse, the rising instance count and shrinking pin-to-gate ratio exacerbate the difficulties of controlling and observing the internal nodes of the circuit.

The definitions of *test quality* and *test cost* have never been more complex than they are today. Electronic testing methodologies should be able to detect the new types of failure modes in modern manufacturing technologies. The population of

integrated circuit physical defects that are not accurately modeled by traditional fault models is rapidly increasing. Moreover, the majority of defects can only be detected when the circuit operates at its regular, full-speed frequency. This can only be guaranteed if the performance and accuracy of test application and response capturing are extremely high. The volume of test data (stimuli and responses) that should be applied to each manufactured circuit to provide high levels of confidence of it being correctly implemented, along with the need of applying tests at very high performance, precision and accuracy have launched the costs of capable test equipment alarmingly upwards. Reducing the cost of automatic test equipment while maintaining the ability to perform high performance, precise and accurate testing has been and will continue to be a major concern: careful embedding of test-related mechanisms on the chip itself, and communicating this information to the tester has shown a promising path to reach this cost and quality goal.

If new defect types are not given special consideration, integrated circuits released to the market, mounted in boards, and connected in their final system have an increased probability of malfunctioning. Conversely, if testing the manufactured circuit takes too long and/or costs too much (in an effort to exhaustively deal with new defect types) the price of testing will severely affect product development costs and the resulting delayed entry to the market will jeopardize product success. If testing is not performed with accurate measurement techniques, the product development cost will also be severely affected due to yield loss: fault-free devices will be rejected only because of inaccuracies in high-speed test measurements.

The major *challenge* of test technology researchers and practitioners today is to define and apply electronic testing methodologies that keep a *balance* between quality and cost. This fundamental test technology challenge is an essential component of a key term of modern electronics: *manufacturability*—the extent to which a new product can be easily and effectively manufactured at minimum cost and with maximum quality and reliability meeting customer expectations. Production of high quality electronic circuits at profitable yield levels requires carefully implemented testing strategies.

For the majority of electronic circuits today, it is crucial that the appropriate test budget (in terms of time or allocated expenses—these are usually directly related) must be utilized, no more, no less. All the *advances* of the last decades in electronic circuits test technology have led us to a maturity point that can make this happen. *Methodologies* and *practices* of the near future should take advantage of this knowledge base to effectively answer today's *challenges* of test cost and test quality; all that needs to be done is to understand and focus on these challenges. This is the motivation and inspiration behind this book: to provide a comprehensive text that focuses on the advances of the research and development community in key test technology topics, records today's industrial practices and new needs, elaborates on the challenges that emerging testing methodologies have to deal with, and provides a vision for the near future of this amazing journey. Hopefully, the book provides the necessary information to understand and assess the tradeoffs to achieve the ideal balance of meeting the appropriate test budget.

## PURPOSE AND CONTENT OF THIS BOOK

This edited volume is a unique compilation of chapters on many electronic testing topics of importance today and in the foreseeable future. The topics discussed are those on which the vast majority of the research and development community in test technology works today; topics where the electronic circuits industry needs effective answers, methodologies and practices that can be applied in the short term.

Every chapter of the book includes the following pieces of information for the reader:

- *Insight* about the *importance* of the chapter topic today. Unless improved or new methodologies and solutions are devised in the topic, electronic testing will either lead to poor test quality or unacceptable test costs. This part of the chapters gives the *motivation* for further research and development in each topic.

- Detailed snapshot of the *state-of-the-art* in the topic and recent *advances* and *industry practices* related to it. The chapter authors allocated a significant portion of their efforts in distilling the literature and providing a comprehensive set of references that represent significant recent research in the topic and can be used as a compass for further in-depth study of each area.

- Identification of the *challenges* in the topic today. Challenges in a topic are either due to the topic being in its infancy and the lack of effective methodologies providing solutions, or due to new problems that emerging manufacturing technologies or product needs have introduced to mature topics. Both types of challenges are discussed in this book along with *vision* and *forecasting* about the near future as well as *guidelines* for the focus of emerging testing methodologies.

Chapter authors provide all this information based on their long experience in the corresponding topic, lots of industrial success and failure cases, supported by a deep understanding of what test quality and test cost mean today for the electronics market. The entire book has a strong industrial and practical orientation. Each chapter is written in a unique way corresponding to the specifics of the topic and representing the authors' background, experience, and way of addressing challenges, problems and solutions. There are several interconnecting relationships among the chapters of the book: chapters touch on the topics of each other, and the reader of one piece can refer to other locations in the book where more specialized elaboration can be found. The matched pieces of this puzzle give the entire picture of *Advances in Electronic Testing: Challenges and Methodologies*.

This book serves a different and unique purpose compared to the comprehensive list of test technology books in the *Frontiers in Electronic Testing* series—a series that continues to support the education of the international test technology community and has done so for the past ten years. This book is neither an introductory book in test technology nor a detailed and specialized study of a single research topic. These two purposes are very successfully served by the other books of the series. *Advances in Electronic Testing: Challenges and Methodologies*

enriches the series with a new type of edited volume on *recent advances* in modern electronic circuits testing. The book focuses on a carefully selected and broad set of topics among those in which intensive research and development takes place today and is expected to continue attracting the interest of researchers and practitioners in the near future.

The intention of this edited volume is to be an advanced textbook and valuable reference point for senior undergraduate students, graduate students in MSc or PhD tracks, researchers and professors conducting research in the electronic testing domain; this book can support orientation of their research plans. The book is also for industry engineers and managers seeking a global view and understanding of test technology and a dense elaboration on test technology issues they deal with in their development projects.

The book chapters are organized in a coherent sequence covering several aspects of electronic testing: failures, defects, bugs, fault models, test interfaces, tester-related considerations, circuit-specific aspects (cores, Systems-on-Chips, memories, mixed-signal and radio frequency circuits) as well as loaded boards testing. The list of chapters and contributing authors is as follows.

| Chapter                                                  | Author(s)                                                          |

|----------------------------------------------------------|--------------------------------------------------------------------|

| Defect-Oriented Testing                                  | Robert C. Aitken                                                   |

| Failure Mechanisms and Testing in Nanometer Technologies | Jaume Segura<br>Charles Hawkins<br>Jerry Soden                     |

| Silicon Debug                                            | Doug Josephson<br>Bob Gottlieb                                     |

| Delay Testing                                            | Adam Cron                                                          |

| High-Speed Digital Test Interfaces                       | Wolfgang Maichen                                                   |

| DFT-Oriented, Low-Cost Testers                           | Al Crouch<br>Geir Eide                                             |

| Embedded Cores and System-on-Chip Testing                | Rubin Parekhji                                                     |

| Embedded Memory Testing                                  | R. Dean Adams                                                      |

| Mixed-Signal Testing and DfT                             | Stephen K. Sunter                                                  |

| RF Testing                                               | Randy Wolf<br>Mustapha Slamani<br>John Ferrario<br>Jayendra Bhagat |

| Loaded Board Testing                                     | Kenneth P. Parker                                                  |

## ACKNOWLEDGEMENTS

The authors of the book chapters have devoted several hours in putting together the material of this volume and presenting it in an as useful as possible way to the reader sharing their knowledge and experience in test technology. The most difficult task we faced during the writing of this book was to squeeze so much technical information in a topic in just a few pages; this took several revisions, lots of disk space and hundreds of emails. I want to warmly thank all authors for their

contribution to this volume and for having the patience to revise the chapters several times. Rob, Jaume, Chuck, Jerry, Doug, Bob, Adam, Wolfgang, Al, Geir, Rubin, Dean, Steve, Randy, Mustapha, John, Jayendra, Ken, it has been a pleasure working with you for this book.

I would like to acknowledge the continuous support and useful suggestions of Prof. Vishwani D. Agrawal, the Consulting Editor of *Frontiers in Electronic Testing* book series. It is my honor to have the Foreword of this volume written by him.

I also want to thank Mark de Jongh, Springer's Senior Publishing Editor, Cindy Zitter, Senior Assistant as well as Springer's production staff for the excellent collaboration.

Several corrections and improvements are due to the help of Mihalis Psarakis who did a thorough review of the entire book. Dimitris Kostakis saved many hours of work by providing valuable hints and answers for the formatting of the book. Ken Parker provided a great help since the beginning with his advises and hints on the structure and layout of the book. Many people have provided inputs and reviews to the authors of the chapters and are separately acknowledged in each chapter.

Dimitris Gizopoulos

September 2005

# Contributing Authors

## **Chapter 1**

**Robert C. Aitken** ARM, Inc. [Physical IP, Sunnyvale, CA, USA]

## **Chapter 2**

**Jaume Segura** Univ. Illes Balears [Dept. Fisica, Palma de Mallorca, Spain]

**Charles F. Hawkins** Univ. New Mexico [EECE Dept., Albuquerque, NM, USA]

**Jerry M. Soden** Sandia Natl. Labs [Failure Analysis Dept., Albuquerque, NM, USA]

## **Chapter 3**

**Doug Josephson** Intel Corp. [Digital Enterprise Group, Fort Collins, CO, USA]

**Bob Gottlieb** Intel Corp. [Digital Enterprise Group, Santa Clara, CA, USA]

## **Chapter 4**

**Adam Cron** Synopsys, Inc. [Test Automation, Mountain View, CA, USA]

## **Chapter 5**

**Wolfgang Maichen** Teradyne, Inc. [IC Enabling Technology, Agoura Hills, CA, USA]

## **Chapter 6**

**Alfred L. Crouch** Inovys Corp. [Research and Development, Austin, TX, USA]

**Geir Eide** Mentor Graphics Corp. [Design Verif. & Test Div., Wilsonville, OR, USA]

## **Chapter 7**

**Rubin Parekhji** Texas Instruments Pvt. Ltd. [SOC Design Techn., Bangalore, India]

## **Chapter 8**

**R. Dean Adams** Magma Design Automation [DFT, Santa Clara, CA, USA]

## **Chapter 9**

**Stephen Sunter** LogicVision (Canada), Inc. [Ottawa, Ontario, Canada]

## **Chapter 10**

**Randy Wolf, Mustapha Slamani, John Ferrario, Jayendra Bhagat**

IBM [RF & Analog Test Group, Essex Junction, VT, USA]

## **Chapter 11**

**Kenneth P. Parker** Agilent Techn. [Manufacturing Systems Div., Loveland, CO, USA]

## Dedication

This book is dedicated to the moments when

one becomes two, two become three and ten become eleven.

# Chapter 1

## Defect-Oriented Testing

Robert C. Aitken

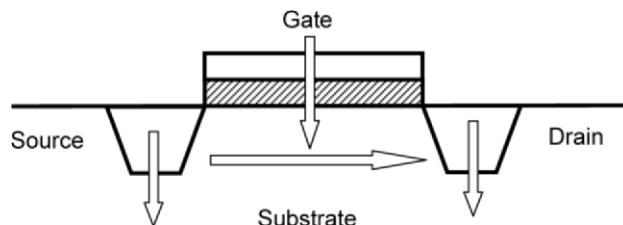

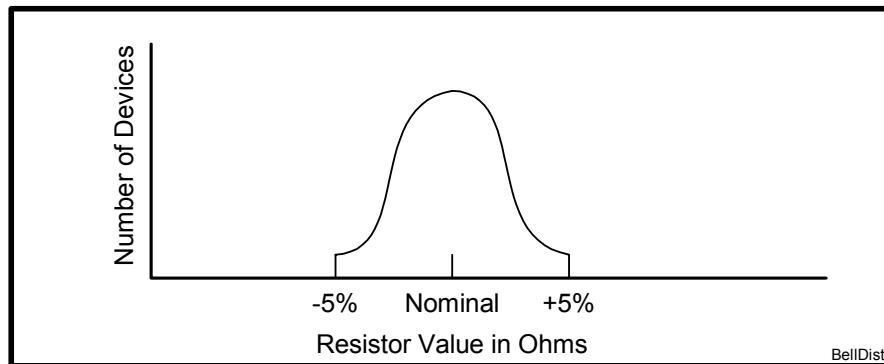

The integrated circuit manufacturing process is imperfect, and as a result defects are introduced into some of the fabricated chips. Defects take a wide variety of forms, from localized spot defects, typically extra or missing material caused by contamination, to defects affecting much larger areas, such as transistor changes caused by implantation variation.

Some defects affect circuit behavior. Testing is used to find these before products are shipped, in order to ensure high quality. Defect-oriented testing is a way to improve the efficiency of testing by targeting tests directly at the defects that cause incorrect circuit operation.

Defects occur in random places and can have unpredictable effects. The processes that cause them are continuous over a wide range of variables. In order to simplify the problem of identifying defective circuits, this infinite defect space is approximated by a finite set of faults. A fault is a deterministic, discrete change in circuit behavior. Faults are often thought of as being localized within a circuit (e.g. a particular gate is broken), but they may also be modeled mathematically as transformations that change the Boolean function implemented by a circuit. Many fault models are time-independent; some use an arbitrary form of time progression,

while a few include time behavior explicitly. The fault effects associated with fault models can be as simple as replacing a subcircuit function with a constant value or be so complex as to require SPICE simulation to evaluate. The choice of fault model depends on its intended use (e.g. test generation, manufacturing quality prediction, defect diagnosis, characterization for defect tolerance, etc.)

This chapter provides an overview of the Defect-Oriented test approach, beginning with a brief history of the subject, an overview of defect mechanisms, with special emphasis on advanced technologies. This is followed by a discussion of how these change the behavior of circuits (fault models). Next is a catalog of the types of tests used in Defect-Oriented test, and a survey of relevant published experimental results on the effectiveness of Defect-Oriented test approaches. Finally, some thoughts on future directions are given as part of the conclusions.

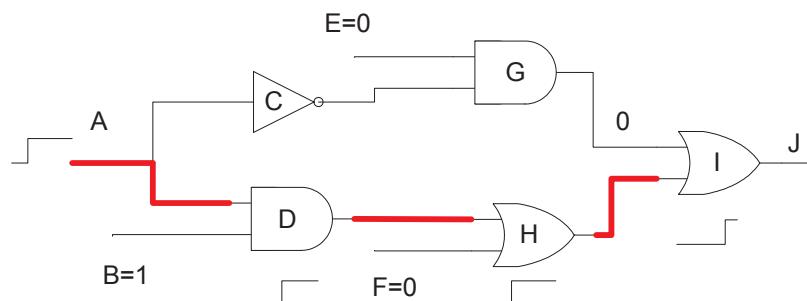

## 1.1 HISTORY OF DEFECT-ORIENTED TESTING

Historically, all testing was functional, and asked the question “Does the device do what it is supposed to?” Functional tests are primarily defined logically (outputs are a function of the inputs). For digital logic, functional tests became too expensive to develop, due partly to the amount of manual effort required to write the tests, but more to the complexity required to translate verification testbenches and tests from a simulation or characterization environment into an ATE environment. As a result, functional tests in production have largely (but not completely) been replaced by structural tests. Structural tests changed the basic questions being asked by test, and expanded the “Does it work?” question into a new question and a syllogism: “Are all circuit elements present and working? If so, and the design is correct, then it must work”. This approach is the basis of scan testing. *Defect-Oriented testing* takes a step beyond structural testing to ask, “What could go wrong with this design, how would the design’s behavior change if this happened, and how can that be measured?” Any measurable circuit property could be affected: logical values, timing, current consumption, etc., whether part of the specification or not. Defect-Oriented tests for digital logic typically include comprehensive structural logic tests, a current test (typically a variant of  $I_{DDQ}$  test<sup>1</sup>), and at-speed tests. All these tests share the property that they measure some aspect of circuit behavior that is directly affected by defects, regardless of their direct applicability to normal circuit functionality.

A key aspect of Defect-Oriented Testing is measurability, and measurability involves overcoming multiple sources of error or variability, including:

1. Defect-dependent variation, since defects can change circuit behavior in a variety of ways.

2. Circuit-dependent variation, including manufacturing process related variation (e.g. gate length, oxide thickness, etc.).

---

<sup>1</sup>  $I_{DDQ}$  testing measures the quiescent (Q) current ( $I_{DD}$ ) consumed by a device. In standard CMOS circuits, the defect-free current is mainly transistor leakage. Many defects raise the level of this current enough to be measured in production test.

3. Environment-dependent variation, since many circuit behaviors change depending on temperature and voltage.

4. Equipment-dependent variation, due to limitations in resolution, repeatability of measurement equipment, as well as drift over time and other machine-dependent variations.

A defect detection method is not useful unless it consistently separates defect-dependent variation from circuit- and environment-dependent variation in the context of equipment variation. We will concentrate mainly on the first two sources of variation in this chapter.

An interesting question is whether we can separate defect behavior from circuit variation. A given flaw, such as a resistive via, can have a range of resistance values. Some of these will cause the circuit to fail logically, others will cause timing failures under some operating conditions, and others will never fail. Defect-Oriented Testing needs to work with the design margin process in order to effectively distinguish between these cases.

Defect-Oriented test requires information exchange between design, test development, process R&D, wafer manufacturing and manufacturing test to be successful. Historically, all these elements have been present inside vertically organized companies, and this is still true today in many cases. In these cases, information exchange between various entities is relatively straightforward, since all are motivated to action by the ultimate financial success of the company. Most published success stories in Defect-Oriented Testing originate within vertically integrated companies.

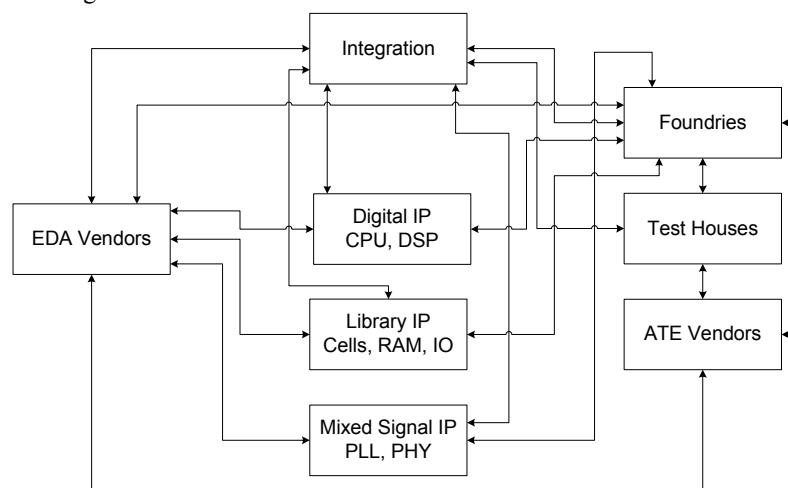

However, the semiconductor industry has substantially disaggregated, allowing chip designers the freedom to select from a number of IP providers, wafer foundries, packaging and test houses, among others. Some of these complex relationships are shown in Figure 1-1.

**Figure 1-1: Value chain relationships in semiconductor industry.**

In this situation, information exchange is not guaranteed, and in some cases may be hindered, based on economic interests of the various parties involved. To succeed in this context, a Defect-Oriented test methodology must provide some form of value to all companies involved. This constrains the problem significantly from the original vertically integrated case, but successful partnership approaches are possible, since all parties benefit from successful silicon.

This new format of the semiconductor industry should still be able to implement Defect-Oriented Testing, although in a modified form. For instance, in a single company, process engineers, library design engineers, and test engineers could easily collaborate on the best approach to designing a defect-robust scan flip-flop. In the disaggregated model, each of these three could belong to a different organization, different even from the design integrator and end customer. In such a model, the library design engineers need to develop flip-flop architectures that were robust across a variety of foundries, when used with standard EDA tools in standard ways. Similarly, the test house would need to be prepared for a variety of approaches. In each case, an effective flow can be established through standardization, through a robust methodology that can account for a variety of implementation techniques, or through a specific cooperative effort between organizations.

## 1.2 CLASSIC DEFECT MECHANISMS

The causes and manifestations of CMOS failures are many, but they have historically been lumped into two broad categories: Shorts, where conduction occurs when none is desired, and opens, where desired conduction does not occur. In aluminum processes, shorts have been more common and more problematic than opens, and so most research has focused on them [1]. Both shorts and opens have standard electrical properties. Of these, the most commonly studied has been resistance. Failure mechanisms will be discussed in detail in Chapter 2 of this book, but are introduced in brief here since they are key to understanding Defect-Oriented test.

### 1.2.1 Shorts

Shorts can be caused both by extra conducting material and by missing insulating material. Examples include:

- Photolithographic printing error

- Conductive particle contamination

- Incomplete etch

- Incomplete metal polish

- Crack in the insulator

- Gate oxide defect causing pinhole

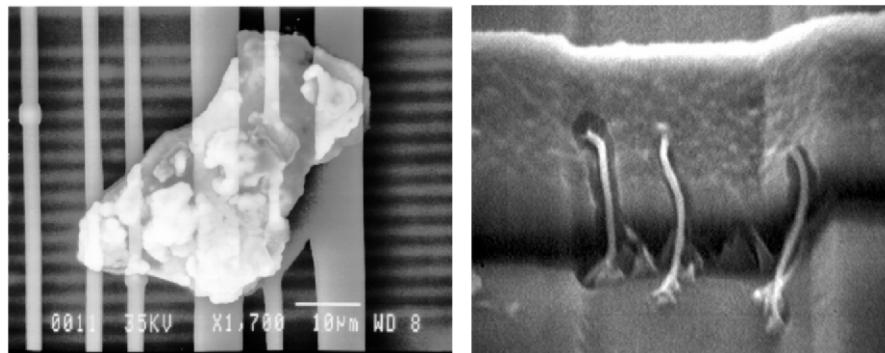

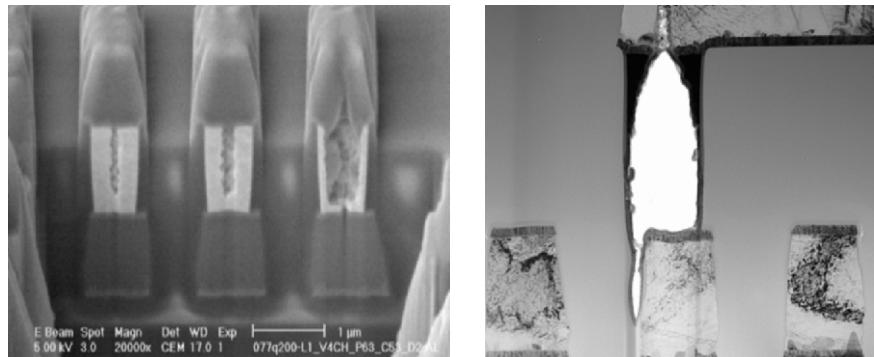

For a comprehensive list, see Chapter 2 of this book. An example metal short by a conductive particle and gate oxide short are shown in Figure 1-2.

**Figure 1-2: Particle and gate oxide shorts.**

The electrical behavior of a short is determined by where it lies in a circuit. Shorts at the diffusion level often involve only the terminals of a single transistor. Shorts in poly or metal 1 affect the internals of one or more standard cells. Shorts in higher levels of metal interconnect typically involve gate outputs, power, and /or ground.

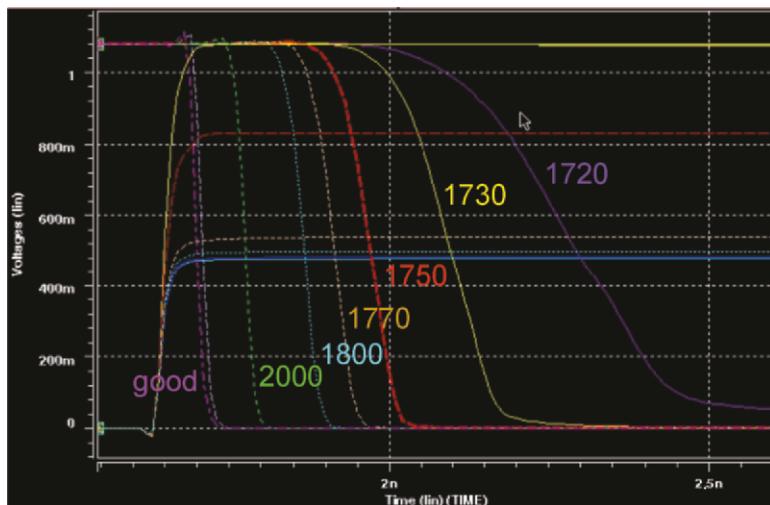

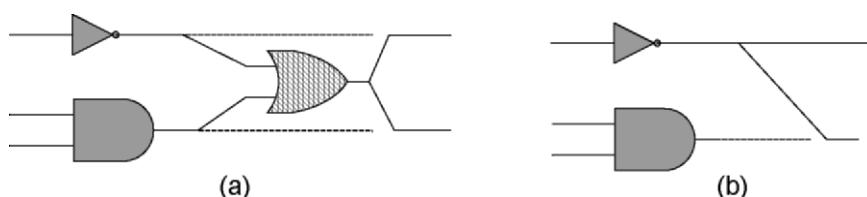

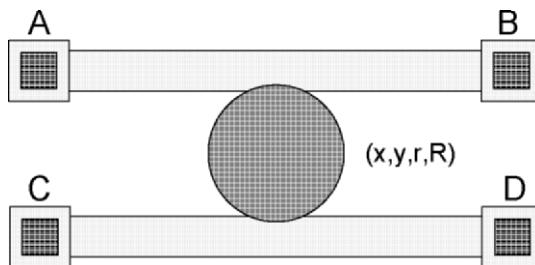

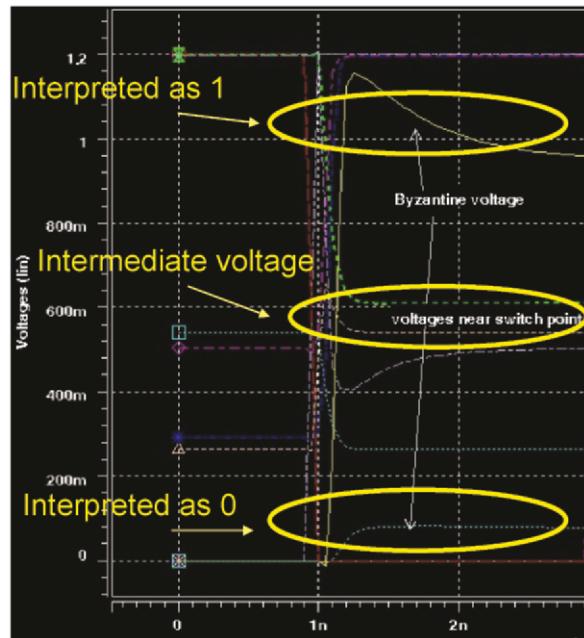

Shorts are active when the two nodes involved are driven to opposite values. A conducting path is formed from the power supply through active P transistors through the short (modeled as a resistance) through active N transistors to ground. The shorter (less resistive) the short, the more likely this conducting path will disrupt circuit operation. This basic idea can be extended to the concept of a “critical resistance” [2] below which the short “wins” and the circuit operates incorrectly, and above which the circuit “wins” and continues to operate correctly. There are actually multiple critical resistances for any short, as shown by Table 1-1 below, which lists delays associated with a bridge between an inverter output and ground in 0.13um technology. The waveforms associated with this Table can be seen in Figure 1-3. There is a logical critical resistance, where the circuit will fail under all circumstances (below about 1700 ohms), a set of timing critical resistances (e.g. at 1800 ohms, a delay of about 150ps results), where the critical resistance depends on required timing and also on operating environment, and finally, a set of  $I_{DDQ}$  critical resistance, where the defect will cause a significant enough increase in  $I_{DDQ}$  to be observed. An  $I_{DDQ}$  technique with 100uA resolution will be able to identify this short at 1.0V for resistances below 10kohms.

| Resistance ( $\Omega$ ) | 1700 | 1720  | 1730  | 1750  | 1800  | 2000 | 3000  |

|-------------------------|------|-------|-------|-------|-------|------|-------|

| Delay                   | SA0  | 600ps | 400ps | 250ps | 150ps | 70ps | <10ps |

**Table 1-1: Resistance and delay for short in 0.13um technology [3].**

**Figure 1-3: Resistance delay curves for a short in 0.13um technology.**

Actual bridge resistance has been studied experimentally, and a wide distribution has been reported [4]. As technology advances, critical resistance is tending to rise, because timing requirements are tighter. Slack times – the difference between the required arrival of a signal and its actual arrival – are shrinking to the order of 100ps or less. At the same time, better synthesis algorithms are making more timing paths critical or near critical. So with more paths having less slack, even high resistance shorts are able to disturb circuit behavior enough to cause a fault.

### 1.2.2    Opens

Opens are caused by missing conducting material or extra insulating material. Examples of these include:

- Photolithographic printing error

- Step coverage

- Incompletely filled via

- Electromigration

- Silicide agglomeration

- Incomplete via etch or via foreign material

- Insulating particle contamination

As with shorts, the behavior of an open is determined by where it is located, whether in the transistor structure (diffusion, poly or metal 1) or in the interconnect between transistors (higher level metal). Logically, opens can be within a cell, or between cells. In many cases, a complete open results in a node that is electrically isolated from its surroundings. Charge stored on this node during fabrication can

affect its subsequent operation. For small opens, Fowler-Nordheim tunneling<sup>2</sup> can occur, resulting in a circuit that operates more slowly than expected. Many complex open behaviors have been postulated (see Chapter 2 of this book for details), but some of these have proven difficult to identify in practice. High levels of leakage and mutual capacitance in modern processes mean that open behavior will likely be more deterministic in future, in that stored charge will bleed away, or nodes will follow their neighbors.

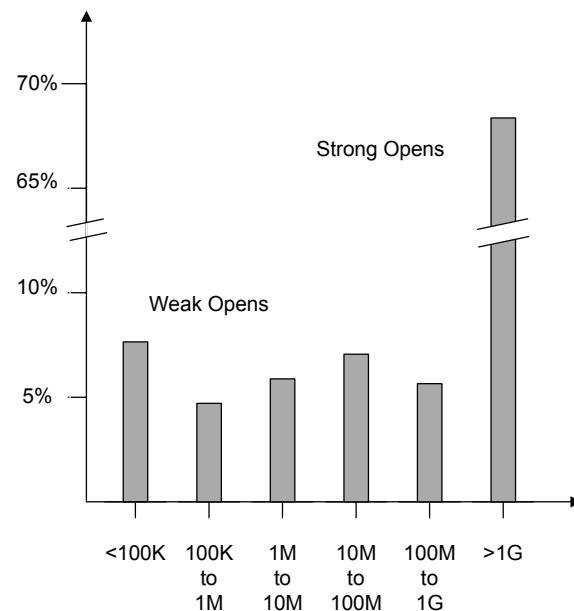

In practice, many opens are partial or “almost opens”. Such opens are challenging to detect and will be addressed later in this chapter. An experimental analysis of resistances was made in [5] and is given in Figure 1-4.

**Figure 1-4: Resistance distribution for opens [5].**

### 1.2.3 Parametric Changes

Defective behavior is not always caused by a single isolated problem such as a short or an open. Sometimes a circuit parameter is out of specification across a wide area, and this can cause a failure, or an increased susceptibility to other problems (e.g. temperature effects, crosstalk, etc.). These problems will also be discussed later in the chapter. Parametric variation begins with a physical change (e.g. variation in printed transistor gate length) and affects the circuit via electrical change (e.g. transistors that are faster and leakier than expected). In addition to gate length, other

<sup>2</sup> Fowler-Nordheim tunneling is the process by which an electron is able to “tunnel” under the potential barrier represented by the physical break in conducting material. As a result, current is still able to flow across a physically small open.

parameters of interest include dopant concentration (device mobility, capacitance), metal thickness (resistance, capacitance), oxide thickness (leakage, performance). Some variation is expected, and design must accommodate it, but at some point variation will exceed the tolerance or margin in the design, and it becomes a defect.

## 1.3 DEFECT MECHANISMS IN ADVANCED TECHNOLOGIES

This section covers some defect mechanisms that are becoming increasingly common in manufacturing processes at the 130nm node and below, and which need to provide the basis for ongoing efforts in Defect-Oriented test.

### 1.3.1 Copper-related Defects

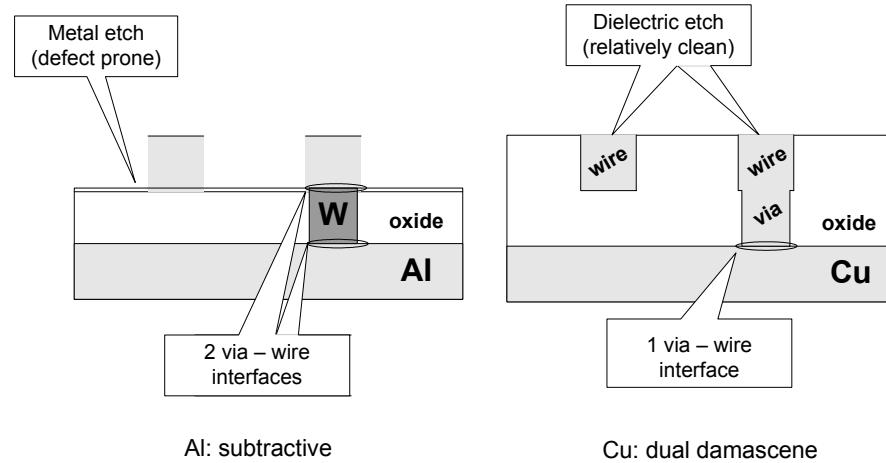

For most of the history of CMOS, metal has meant aluminum. Since 130nm, however, copper has become the metal of choice, and this means that changes must be made in the way metal defects are considered. Aluminum metallization is a subtractive process: an entire layer of metal is deposited, a mask is applied and unwanted metal is etched away. This metal etch is inherently “dirty” and results in many particles being present, some of which lead to shorts. The etching process has led to shorts being far more common faults than opens in CMOS processes for many years.

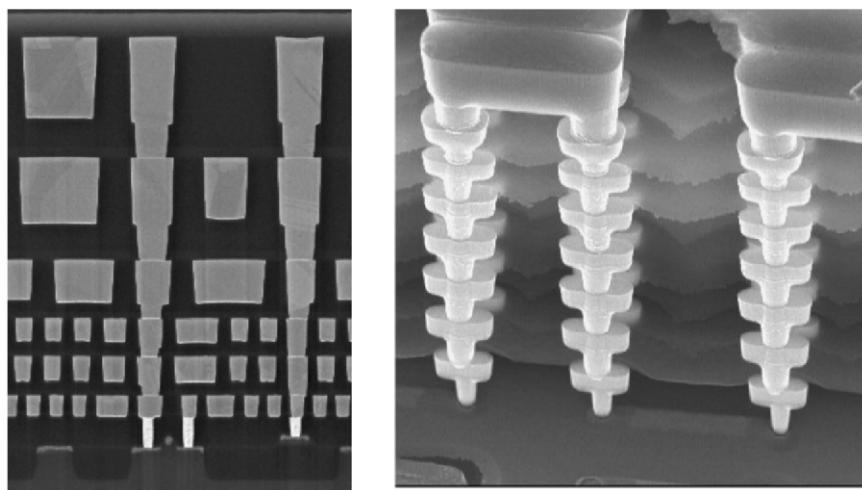

Copper, on the other hand, uses a dual *damascene*<sup>3</sup> process. A layer of insulator is applied to the wafer. Next troughs for wires are etched (first damascene step). Next additional troughs for vias are etched. A layer of copper is electroplated into the trenches (on top of a small tantalum barrier/seed layer). Finally, excess copper is removed via *chemical/mechanical polishing (CMP)*. There is no metal etch to provide a slurry of particles. As a result, additional defect mechanisms become important. Figure 1-5 summarizes the processing differences. Note that the process is highly simplified when copper is used.

In addition to a metal etch, aluminum processing also features two via/wire interfaces (tungsten to aluminum). Copper has only a single via/wire interface, since both vias and wires are deposited together. The absence of the metal etch and the reduced number of interfaces can result in a lower defect level for copper metallization than aluminum. However, there are some specific new defect mechanisms associated with copper. These were particularly troublesome in the early days of copper processing, but are now at more acceptable levels.

---

<sup>3</sup> The term “damascene” comes from metal inlaid with gold or silver, an intricate craft associated with the city of Damascus.

**Figure 1-5: Comparison of Al and Cu processing.**

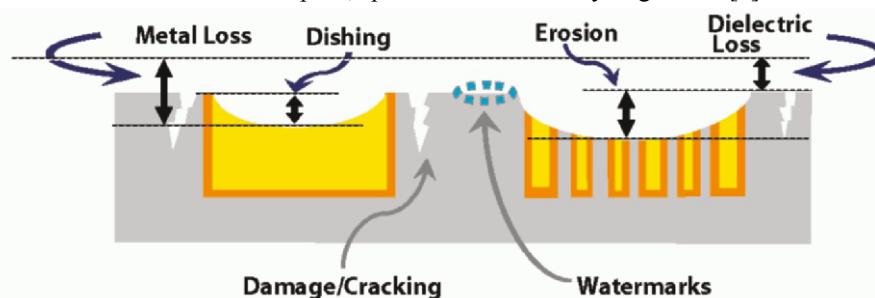

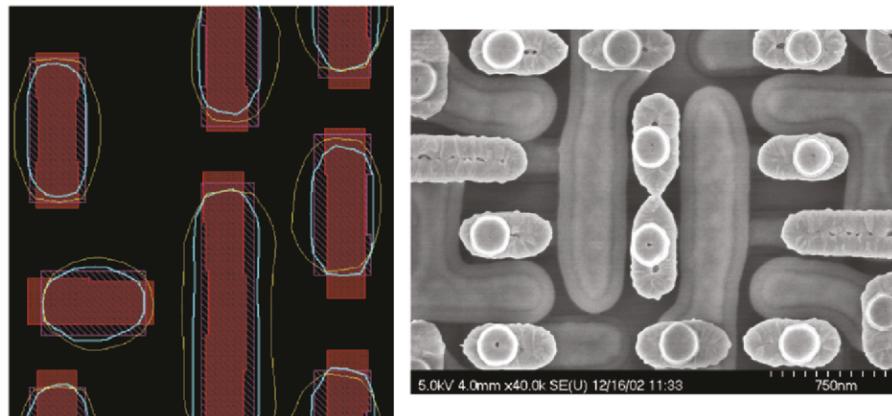

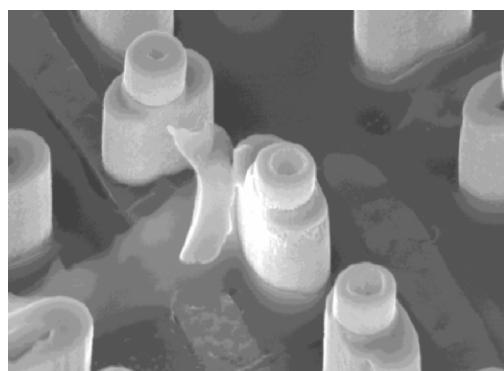

The polishing process for copper leads to four major defect mechanisms: *under polishing*, which leaves copper or slurry remaining where it is not wanted, which can lead to shorts, *dishing*, where over polishing has occurred, and *erosion*, where insulator has been polished as well as copper (see Figure 1-6). In each case, the defect leaves a surface that is poorly planarized and susceptible to defects at higher levels (e.g. wide metal dishing on one layer can cause shorts in the layer above as wires fold in on each other). The fourth mechanism, *scratches*, result in combinations of shorts and opens, spread across relatively large areas [6].

**Figure 1-6: Dishing and Erosion (courtesy Applied Materials).**

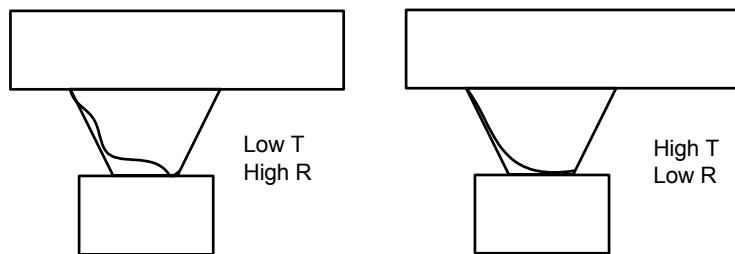

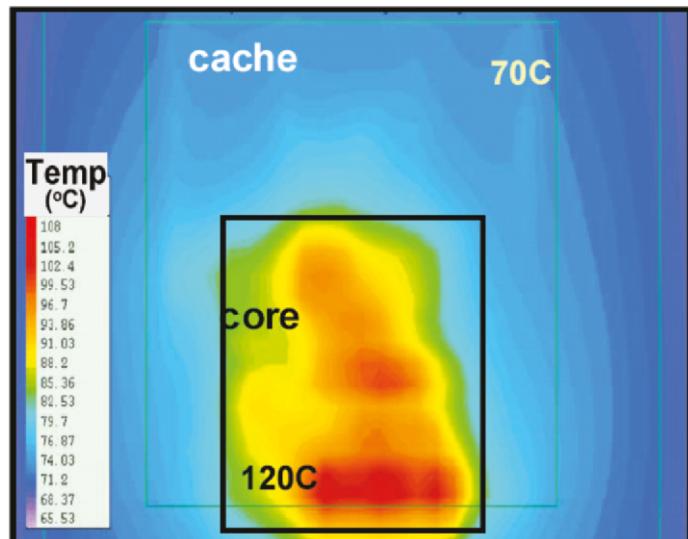

In addition to CMP-induced defects, *voids*<sup>4</sup> (also known as partial opens) are another major defect mechanism. These defects often have an easily recognizable signature: delay faults at low temperatures. This happens because of thermal expansion of the copper into the void. As temperature increases, the void shrinks and the two metals make better contact, as shown in Figure 1-7. Cold temperature delay

<sup>4</sup> Voids are empty spaces in the metal left by incomplete copper deposition.

mechanisms exist in aluminum processes as well (voids, via contamination, and silicide cracks, for example), but they are more common in copper processes.

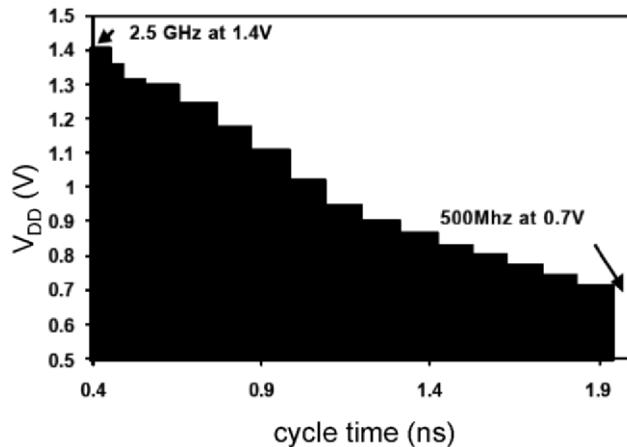

The copper void defect mechanism shows that while high temperatures are the worst operating condition for defect-free circuits, defective circuits may have worst-case behavior at room temperature, or even lower. If possible, delay tests should be applied at two temperatures to account for void defects and process variation at tolerance limits.

**Figure 1-7: Temperature dependence for copper voids (T=temperature, R=resistance).**

Automatic Test Pattern Generation (ATPG) for void-related defects should emphasize via crossings, especially those where only a single via has been used (redundant vias are the standard design-for-manufacturability – DFM – approach to via voids, since the spare vias can carry the required current if voids are present).

### 1.3.2 Optical Defects

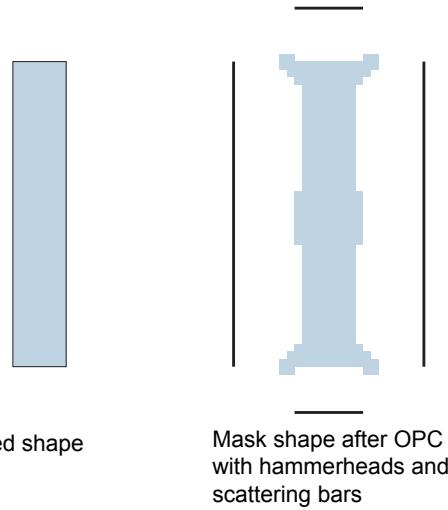

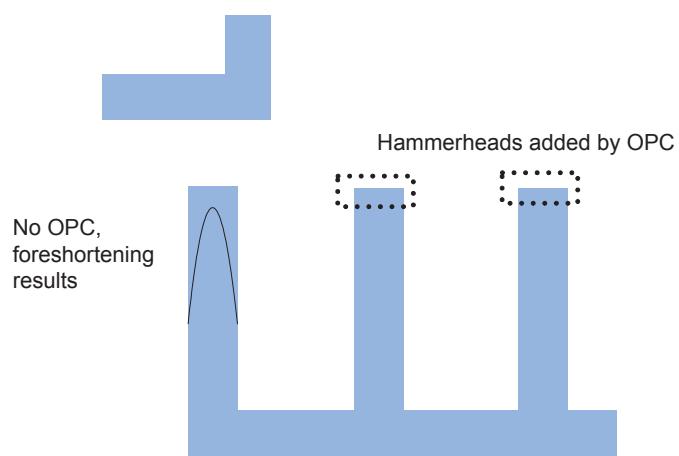

At 130nm and below, many features of a layout are now below the wavelength of light used during photolithography (typically 248nm or 193nm). As a result, *optical proximity correction (OPC)* is applied to masks to ensure accurate printing. In many ways, OPC is similar to the use of serif fonts in conventional printing, which developed to ensure adequate ink coverage (e.g. “X” versus “X”). OPC can add additional features (e.g. hammerheads or outriggers) or shrink features.

OPC leads to two major classes of defect: *mask errors* and *Design Rule Checking (DRC) escapes*. In a mask error<sup>5</sup> (see Figure 1-8), OPC fixes result in a short or open when features interfere with one another. In general, mask defects are catastrophic and result in 100% yield loss simply because all chips manufactured using the bad masks will be faulty. Reticle inspection helps reduce the number of these, but inspection programs have been confused by OPC features that look like defects but are legitimately needed for the design [7].

<sup>5</sup> A mask error is present on the masks used for photolithography. This error is then printed instead of the desired circuit.

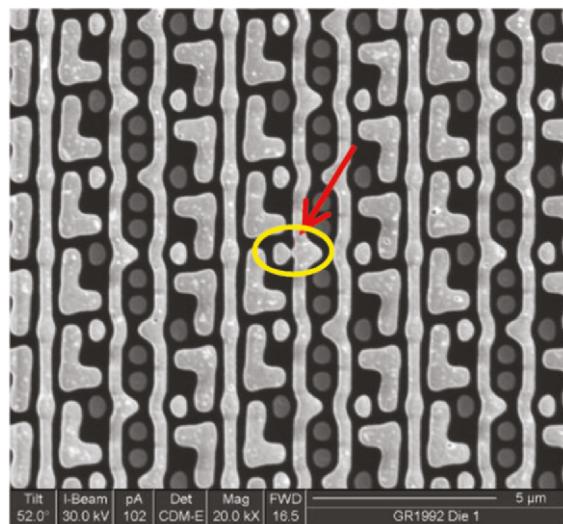

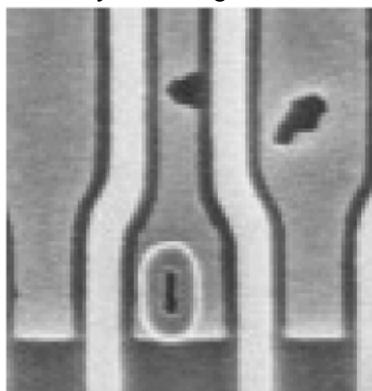

**Figure 1-8: Mask error after OPC.**

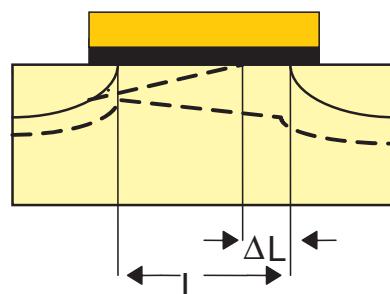

In a DRC escape, OPC is meant to fix a particular feature, but can't, due to neighboring circuitry. Consider the layout of Figure 1-9 where hammerheads should be added to each gate, but nearby circuitry prevents this from being possible on the leftmost gate. As a result, the gate is foreshortened. In some cases, catastrophic failure will result, but often only weaker than usual gates will be formed. The resulting channel is shorter in on portion and narrower as well. This defect will typically behave as a delay fault, and can often be detected by transition fault tests.

**Figure 1-9: OPC limited by nearby layout.**

### 1.3.3 Design-related Defects

While process technology is the main driving force between new defect types, the impact of design methodology should not be ignored. At the most obvious level, decisions made by routing tools determine which wires are likely to short and which aren't. Even adjacent wire spacing can be controlled. This section explores two more subtle mechanisms, both relating to low power design and thus appearing in advanced manufacturing technologies. Additional discussion of design related defects is available in [3], [8].

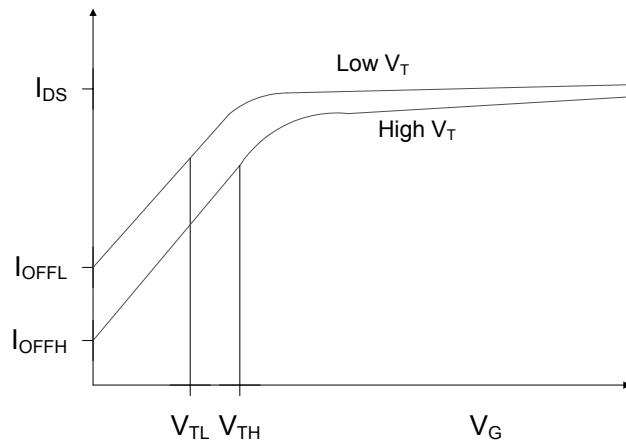

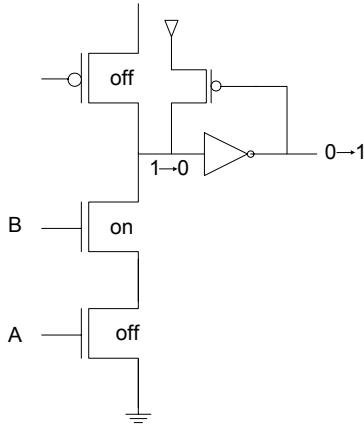

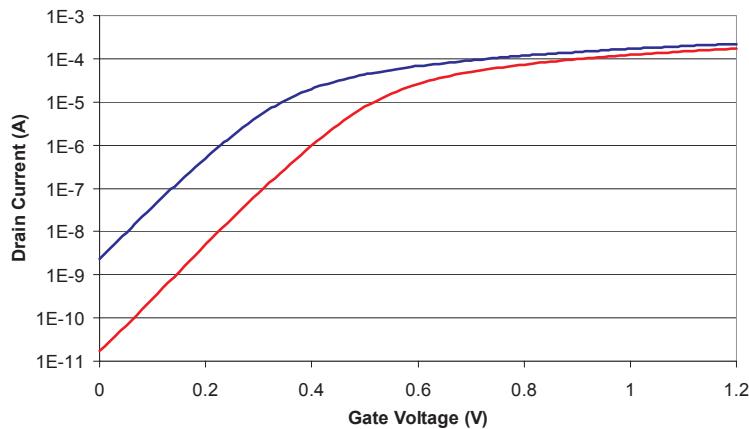

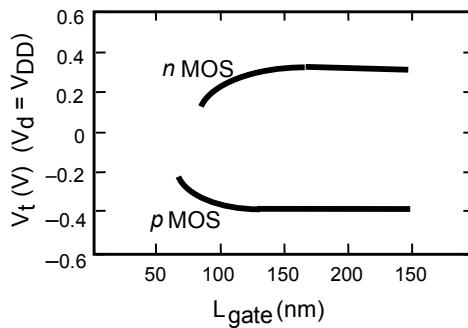

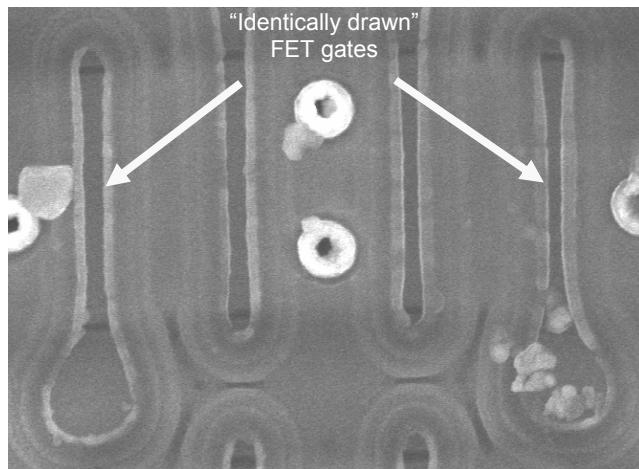

#### **Multi- $V_T$ Libraries**

Transistor off current and drive current both depend on threshold voltage, as shown in Figure 1-10. A low threshold device has somewhat higher saturation current and thus higher performance, but at the cost of substantially higher off current. By using both high and low  $V_T$  transistors in a design, leakage and performance can be traded off more finely than by using exclusively one or the other. For consistency, we will use “ $HV_T$ ” for the high threshold voltage devices and “ $RV_T$ ” for the regular threshold voltage ( $V_T$ ) devices. A common approach to get the reduced leakage of  $HV_T$  devices with the performance of  $RV_T$  devices is to mix them at the gate level – some gates will use each type [9]. Typically, the critical path and near critical paths are implemented with  $RV_T$  gates, and the rest with  $HV_T$ . Making this work easily in a tool path requires that the  $HV_T$  and  $RV_T$  gates be artwork compatible (same cell height, routing pitch, etc.). Ideally, they should be the same artwork with different implants, in order to allow drop-in substitution after placement. Using these techniques can save 70-80% of leakage power, even for high performance designs [10]. Two-variant processes are discussed here, but processes supporting 4 or 5 variants are currently available at 90nm technology in foundries such as TSMC and IBM.

**Figure 1-10: Relationship between off current, drive current and threshold voltage [11].**

Multi- $V_T$  cells can increase the chances of “Byzantine Generals” behavior (see section 1.4.3) of bridging faults because of varying thresholds among gates and varying drive currents.  $HV_T$  devices tend to have higher variability, and their weaker drive currents give them higher critical resistances than  $RV_T$  devices.

### **Multiple Voltage Domains**

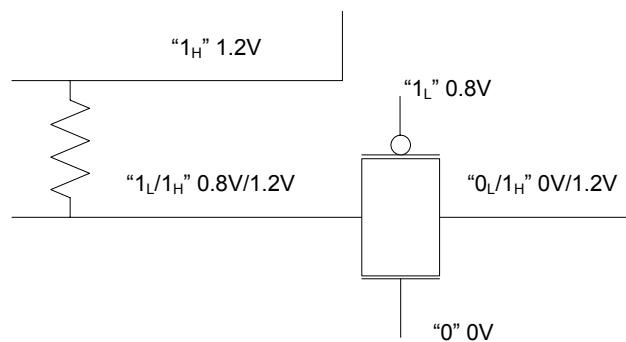

Power consumption varies as the square of voltage. Low power design approaches, especially for battery-powered applications, are increasingly using variable power supply voltages. Two basic approaches are possible: open loop, where voltage levels are predetermined based on characterization and expected power consumption, and closed loop, where the system dynamically adjusts its voltage to the lowest level able to sustain its present level of activity (i.e. embedded CPU voltage will be higher during peak activity times, such as displaying an MPEG video, and will be reduced during lower activity times such as voice transmission), and can be reduced even further or even shut off during sleep modes [12].

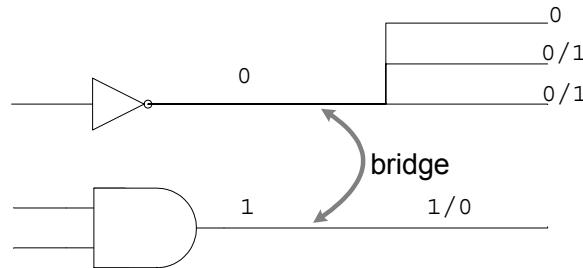

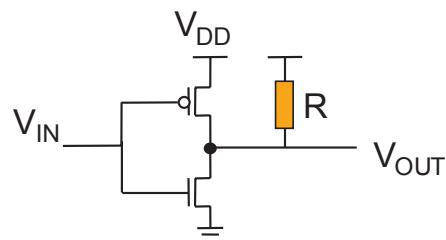

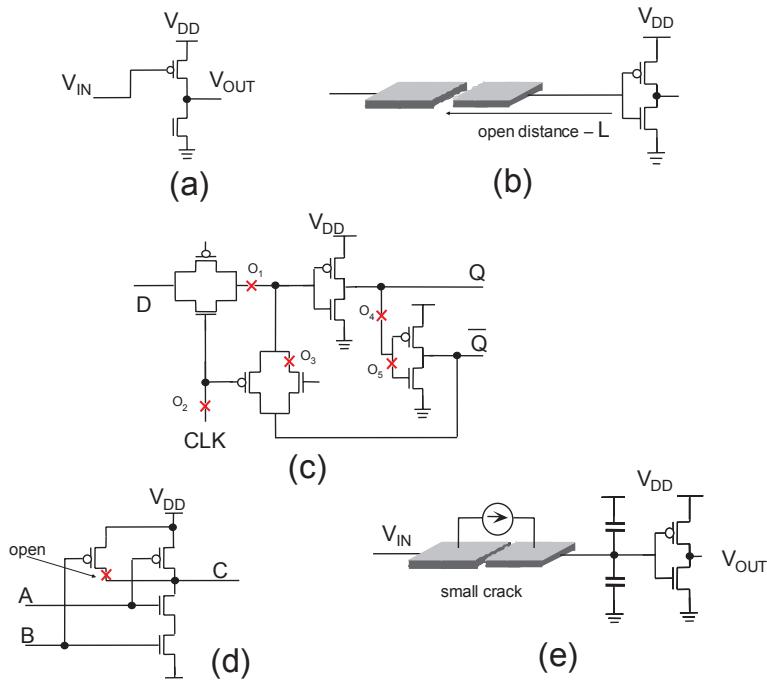

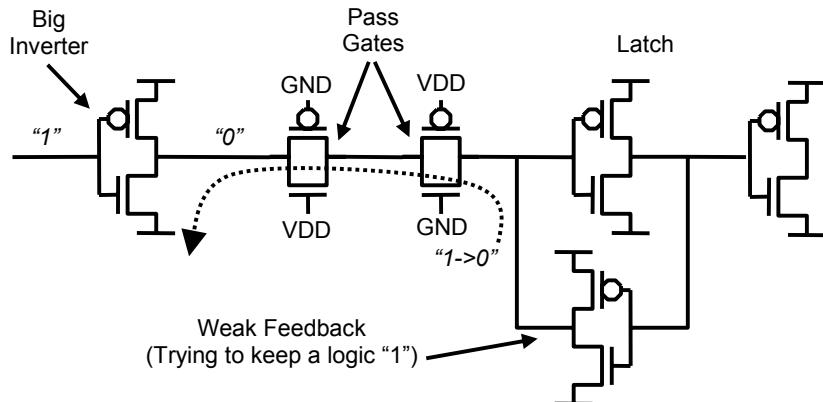

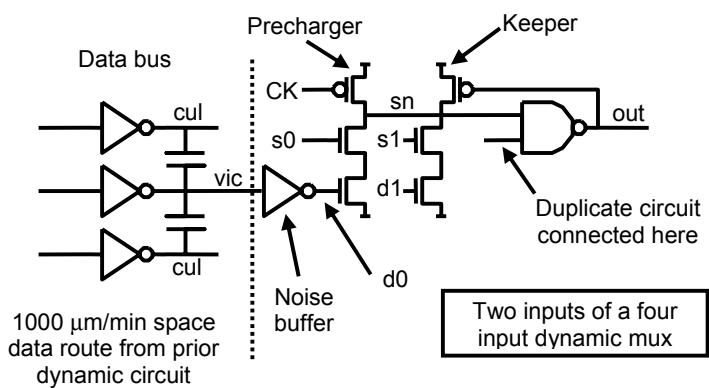

Keeping voltage domains separate is best accomplished by using physical isolation together with level shifting circuitry, but when they interact new defect behavior is possible. For example, bridging fault models usually make the simplifying assumption that a bridging fault is not activated if the involved nodes are at the same logic value. However, consider the circuit in Figure 1-11. The P transistor in the transmission gate has both its gate and source at logic 1 in the low voltage domain ( $1_L$ ), so the gate is off in the fault free case. A short (or even capacitive coupling) with the higher voltage domain leads to a voltage on the source above the  $V_{DD}$  value of  $1_L$ , denoted by  $1_H$ . This causes the difference between the gate and source voltages of the transistor to be greater than its threshold value ( $V_{sg} > V_{th}$ ), turning the transistor on. The faulty value is now free to propagate as any with other fault. Physical isolation of level shifters can help reduce this problem, but will not totally eliminate it. These shorts will be more of a concern for diagnosis than for bridging ATPG, which should try to sensitize them the conventional way (opposite values).

**Figure 1-11: Faulty behavior with multiple  $V_{DD}$  values bridged.**

Defects in the level shifters themselves cannot be avoided, but careful attention needs to be paid in layout in order to ensure that they result in catastrophic (easily measurable) failures, rather than subtle problems that might escape detection during manufacturing test.

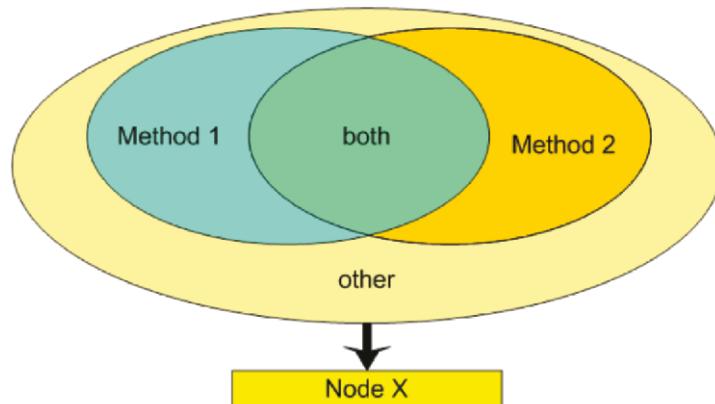

## 1.4 DEFECTS AND FAULTS

Defects manifest themselves in a variety of ways. At any given circuit node X, some will be detectable only by test method 1, others by test method 2, and others by both (see Figure 1-12). A fourth category will not be detectable by either 1 or 2, but could be detected by another approach. Ideally, it would be desirable to model defects directly and independently from the methods used to detect them, but realistically defect behavior must be extrapolated and simplified into *fault models*<sup>6</sup>. The factors affecting fault modeling in nanometer technologies can be divided into three broad categories: increasing circuit size, increasing defect subtlety, and decreasing numbers of manufacturing processes. Each of these has major implications on the nature of faults that will be targeted in future designs.

**Figure 1-12: Relationship between defects and test methods.**

As transistor manufacturing cost has declined over time, chip producers have largely responded by including more functionality on chip, rather than producing cheaper chips. This explosive growth in transistor counts means that fault models and defect analysis must be tractable on ever-increasing circuit size. At the same time, increasing defect subtlety is being observed. The primary concern of manufacturing testing in the past has been the identification of permanent, deterministic, defective behavior, so-called “hard faults”. The fault models and associated tools developed reflect this. Test generation tools strive for completeness: generating a test which detects a fault, or proving that the fault is untestable. There is no middle ground. Defects, of course, follow no such rules. In order to account for

<sup>6</sup> A fault model is an abstraction of defect behavior. To be useful, a fault model must help in the development or evaluation of tests, or in yield improvement.

their behavior correctly, fault modeling will need to move from the discrete to the continuous domain.

As the cost of developing CMOS manufacturing technology skyrockets, the number of independent efforts is declining. Bringing a new process technology to market already costs multiple billions of dollars, and this cost is rising with every process generation. With these sorts of up-front costs, more and more companies are forming joint ventures and working to co-develop technology, or are simply dropping out of the manufacturing business altogether and contracting wafer manufacturing to others. As this happens, the number of *different* technologies will drop with every process generation; perhaps until only a handful remain<sup>7</sup>. Fewer processes means greater opportunity to amortize high model development cost, and thus has several beneficial side effects.

In order to see more concretely the effects described above, it is worthwhile to consider some specific fault models in common use today and see where they are likely to be headed. First, recall the main uses of fault models.

### 1.4.1    **Uses of Fault Models**

#### **Test Generation**

A fault model accomplishes two purposes during test generation. First, it provides a measure of completeness (how much work remains to be done). In an explicit fault model<sup>8</sup>, keeping track of the faults for which test generation has been attempted will suffice for this task. The second role is test effectiveness. By calculating both the fraction of faults detected (fault coverage), and the fraction of faults which cannot be detected (untestable faults), a test generator can demonstrate that it has achieved complete fault efficiency; i.e. it has developed a test for all the faults it can develop a test for and has proven the rest untestable.

#### **Fault Simulation**

Fault simulation requires a fault model, primarily for coverage measurement. Except for a few trivial cases (such as stuck-at coverage in combinational circuits with 20 or fewer inputs), fault simulation cannot prove that a fault is untestable, but it can evaluate tests and determine their coverage. A simulator may work in conjunction with a test generator, as a check for a test generator, or as a means of evaluating tests from some other source.

#### **Quality Prediction**

The ultimate purpose of fault coverage metrics is to provide a means of ensuring that tests developed for a chip will allow it to meet its necessary quality goals. Of course,

---

<sup>7</sup> Note that this does not involve the number of fabs producing wafers, or the number of transistor types available within these fabs' processes, only the number of different manufacturing processes used by these fabs.

<sup>8</sup> An explicit fault model is one where the faults can be enumerated.

quality is always measured in terms of defects, while coverage can only be measured in terms of faults. But how do defects and faults relate to one another? It is sometimes desirable to use a simple model as a “surrogate” for a more complex model in order to quantify this relationship [13].

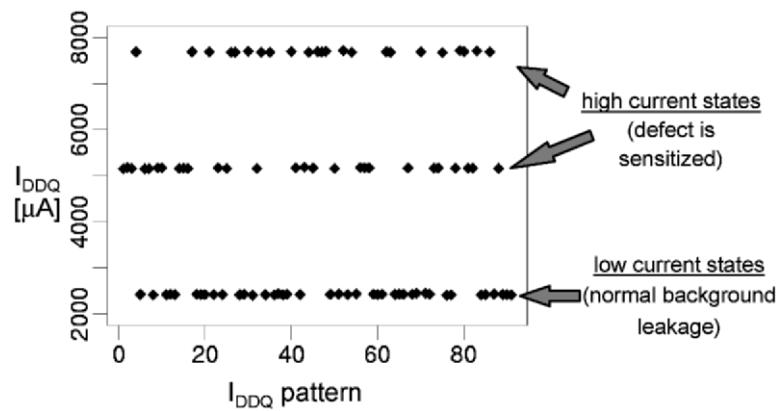

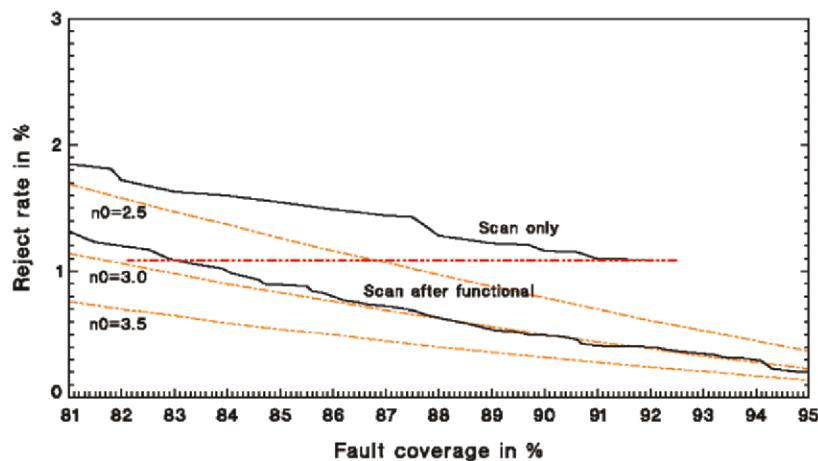

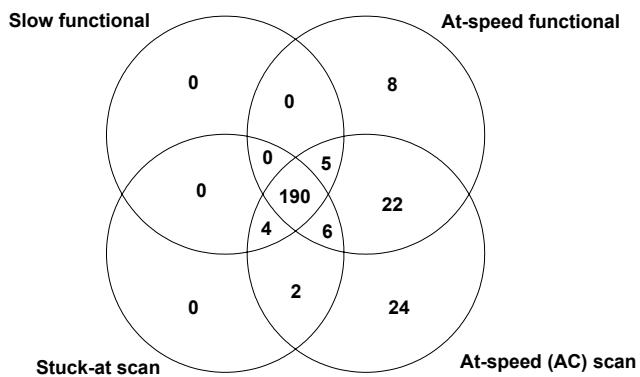

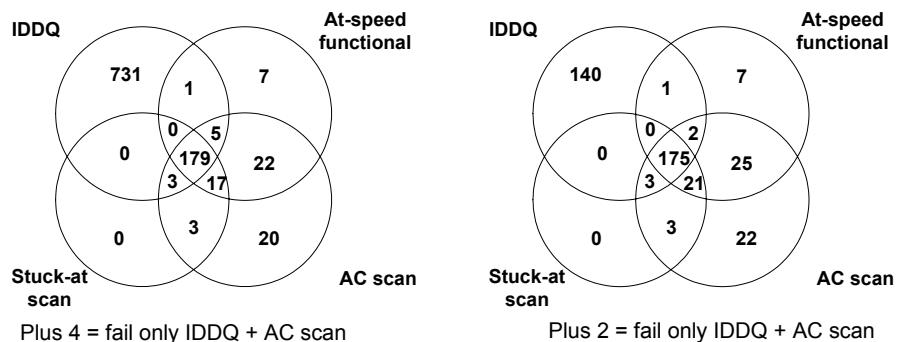

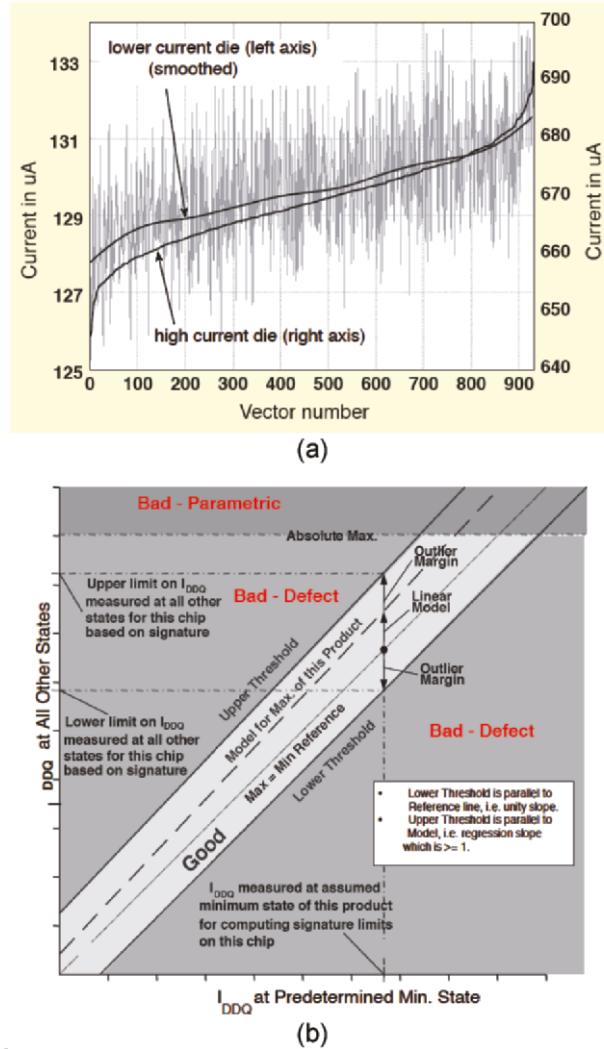

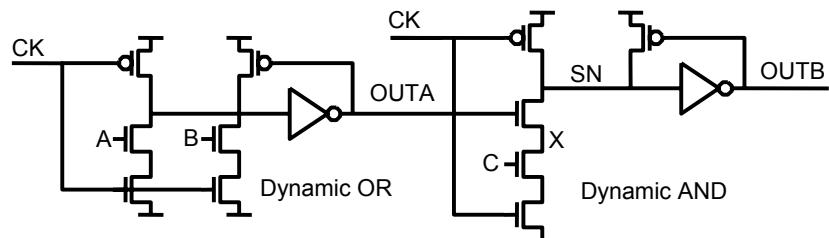

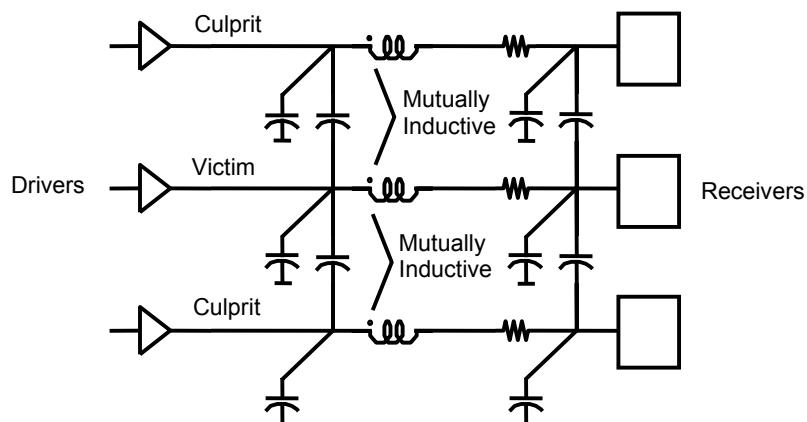

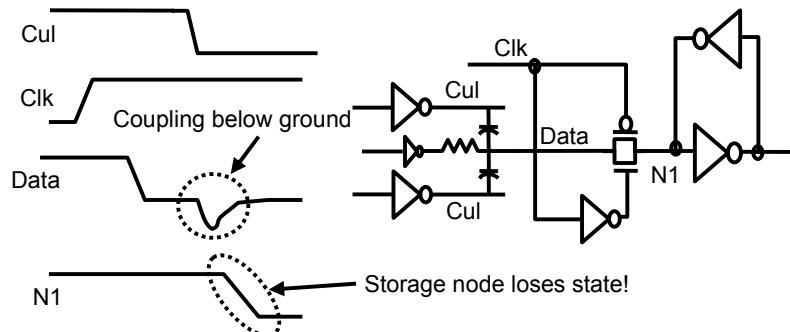

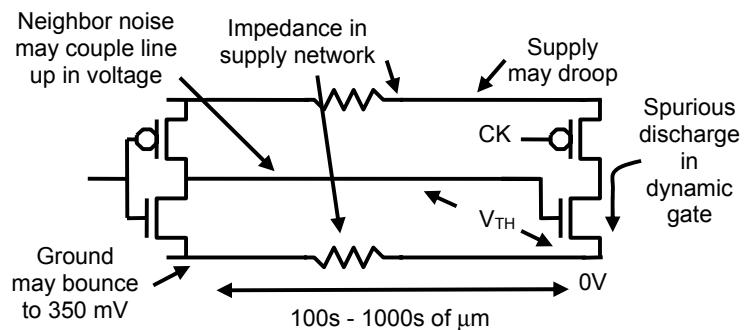

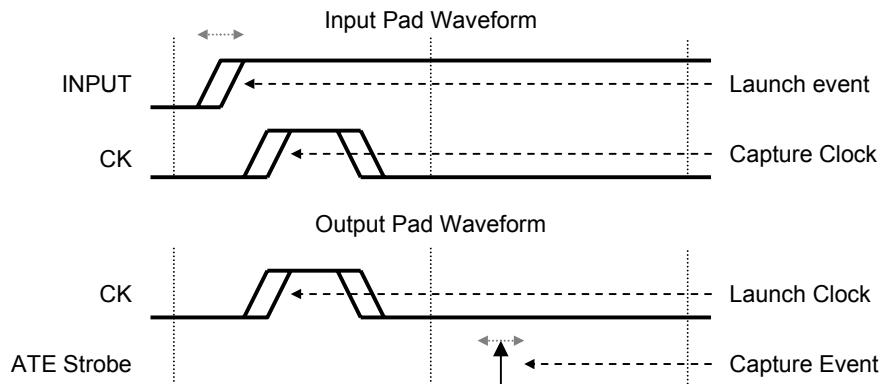

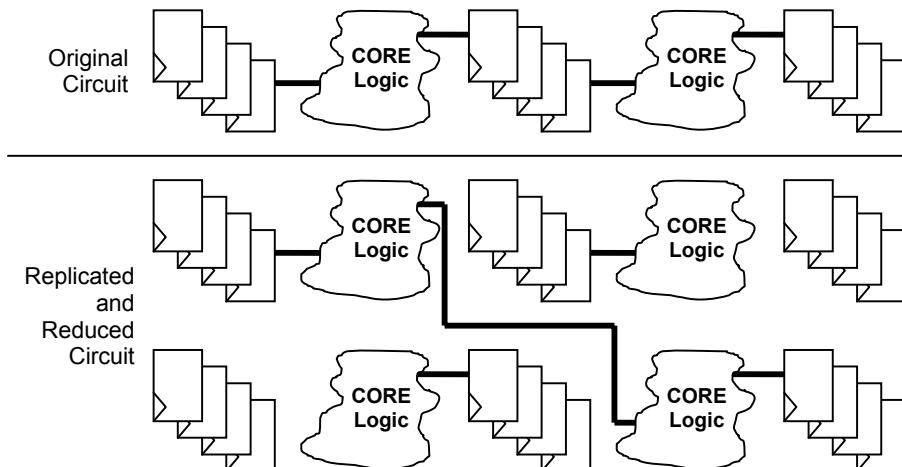

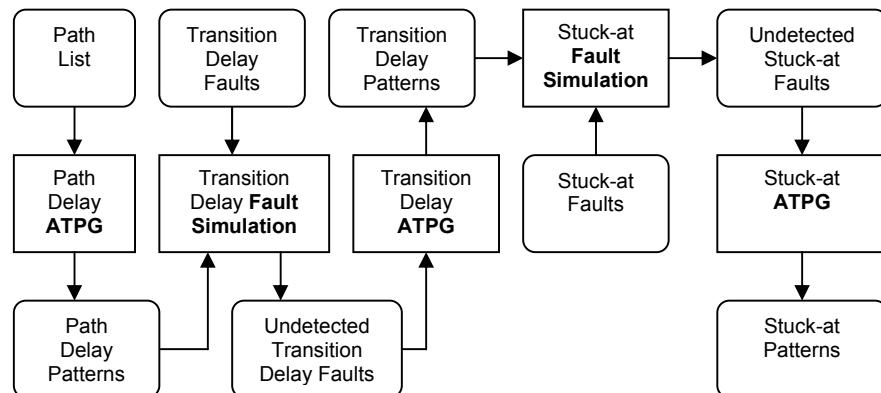

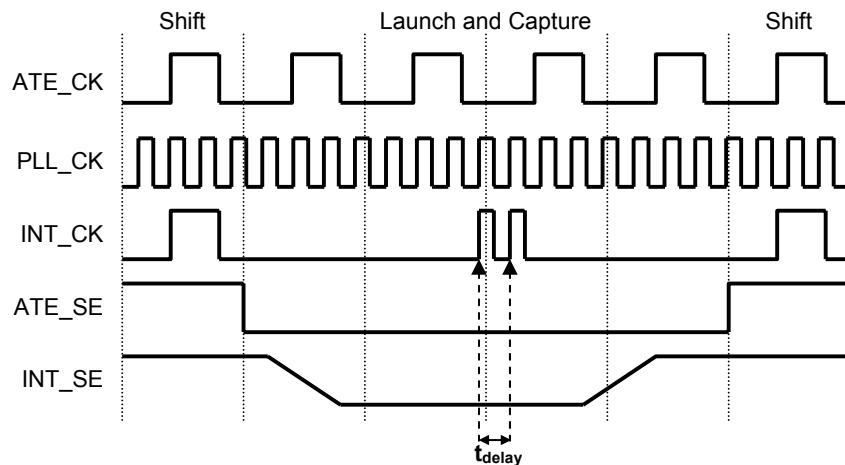

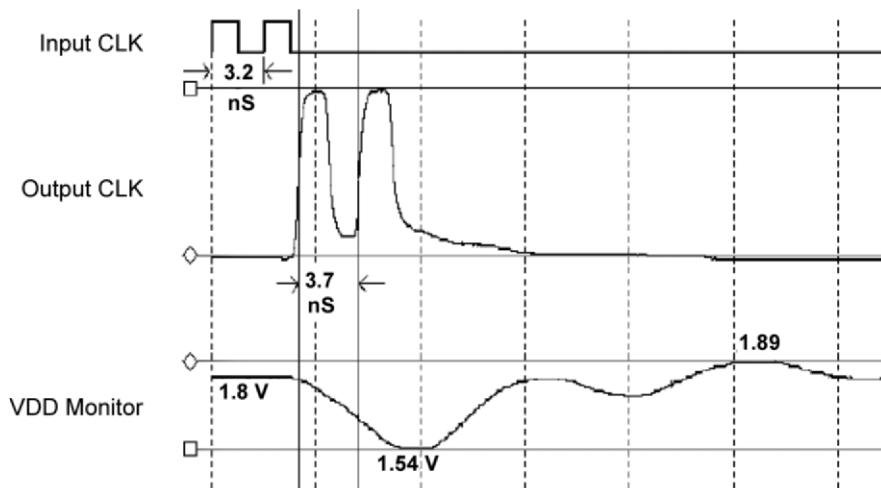

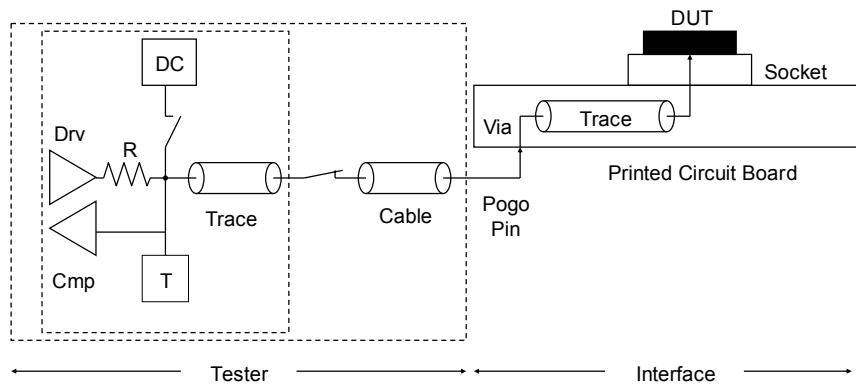

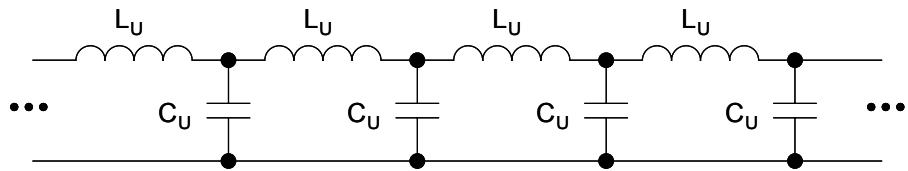

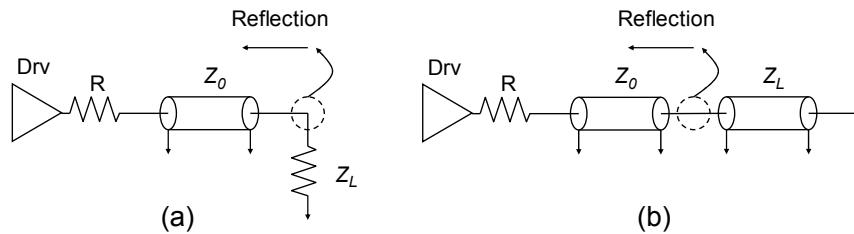

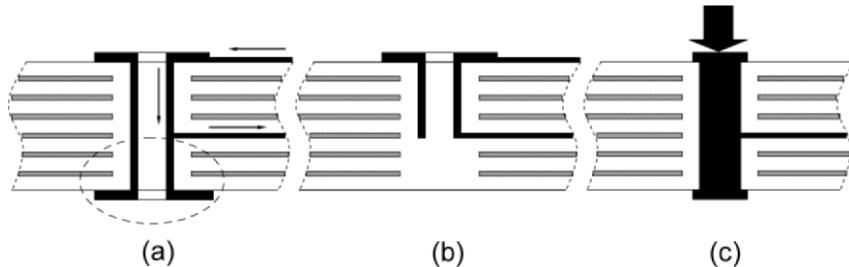

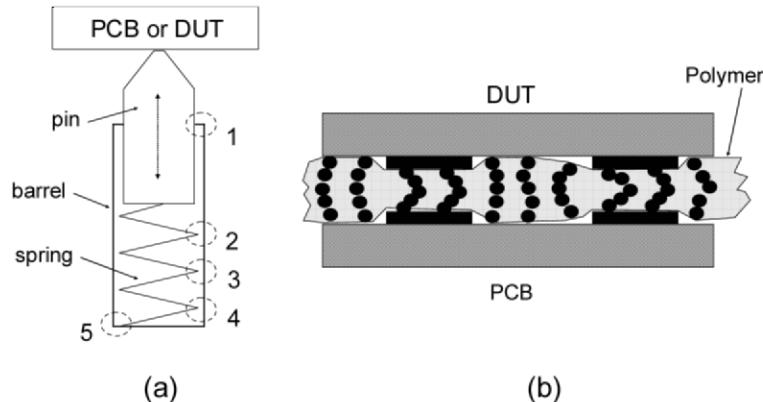

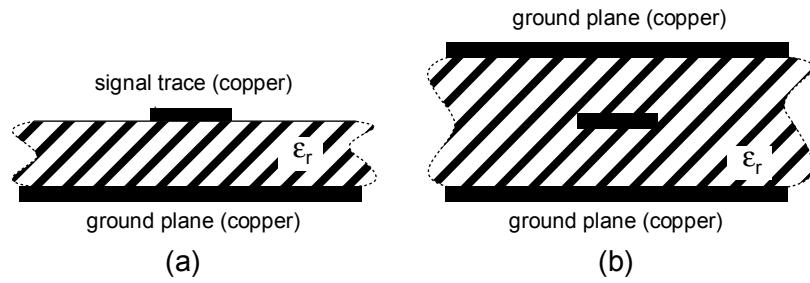

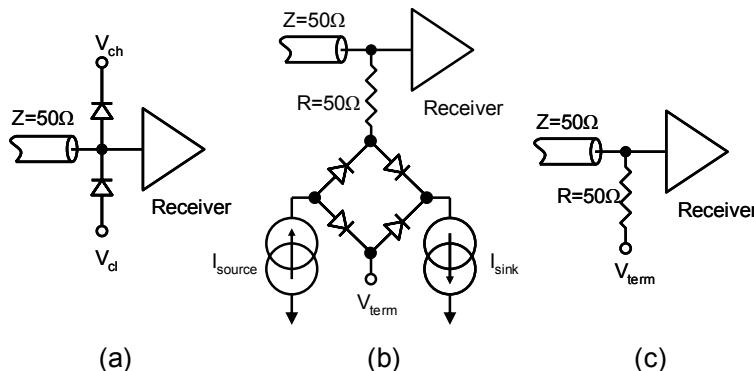

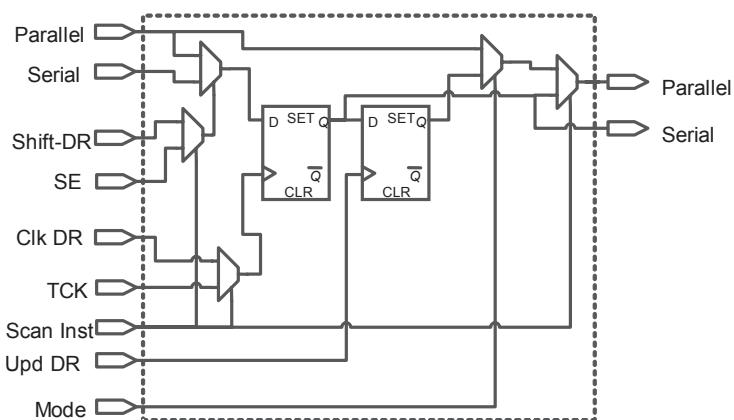

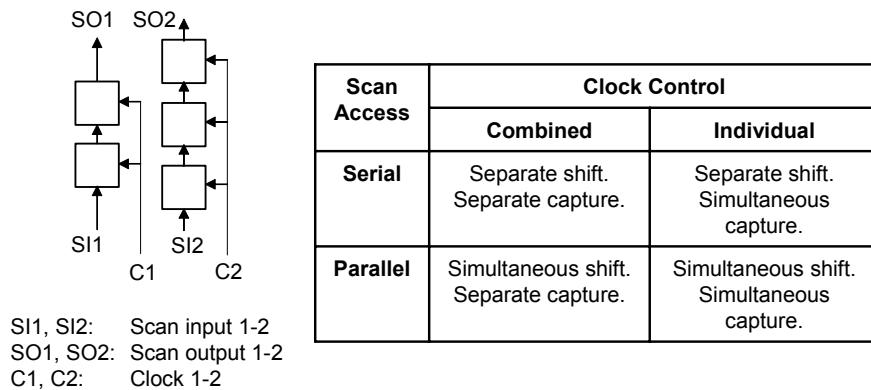

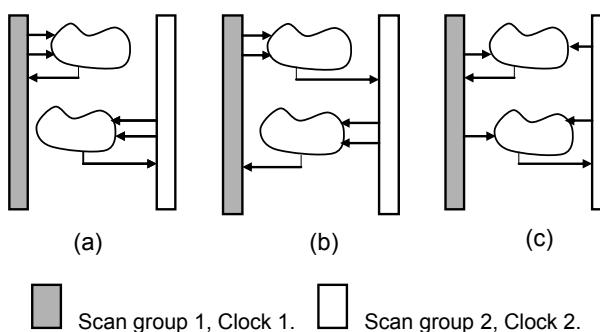

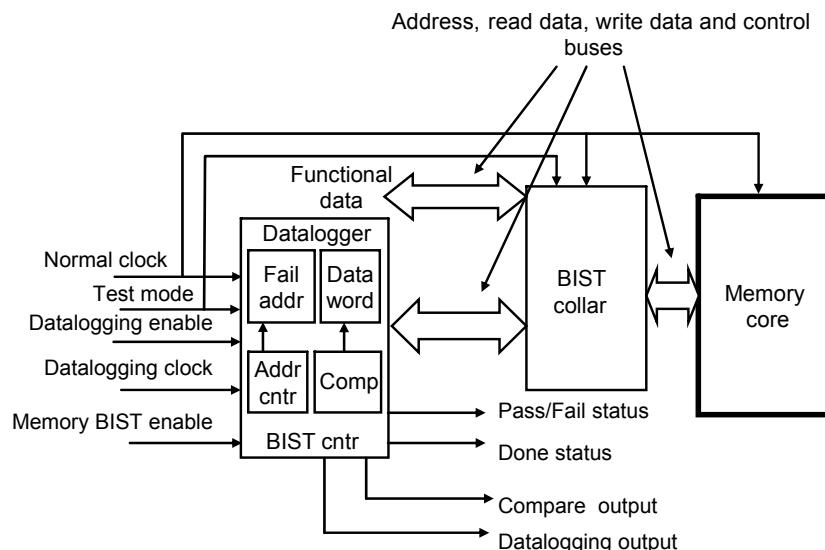

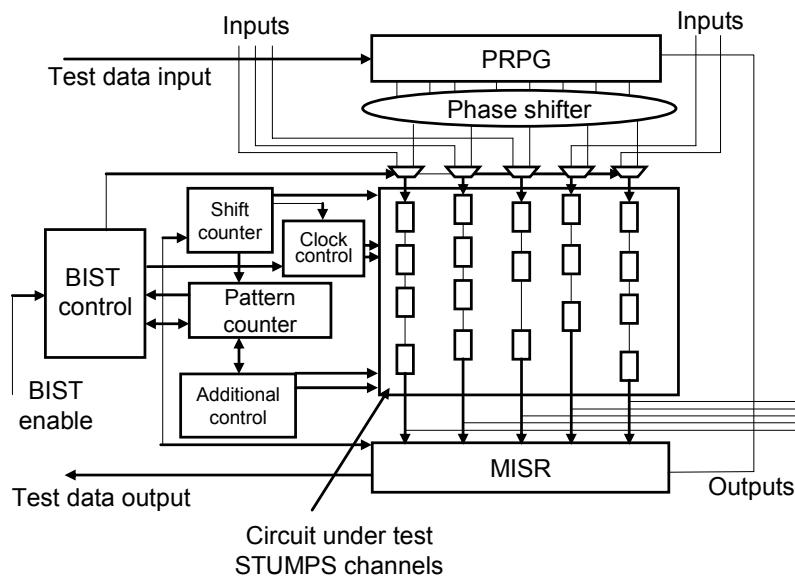

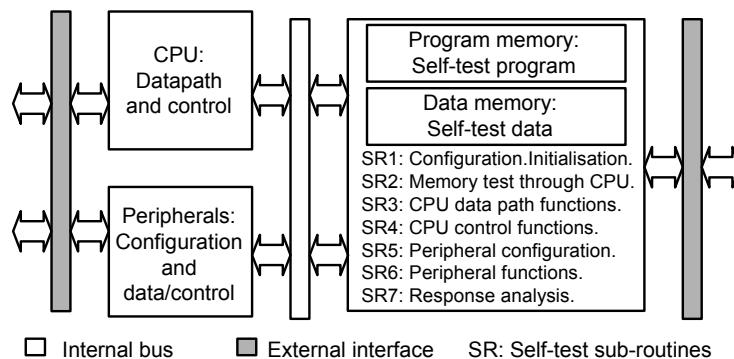

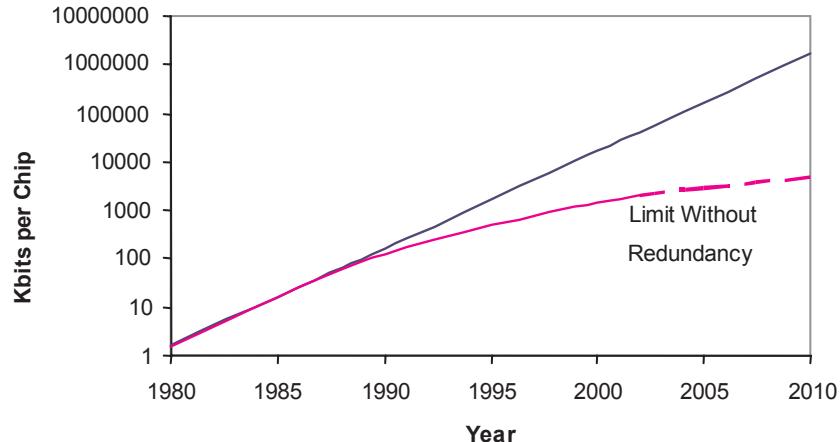

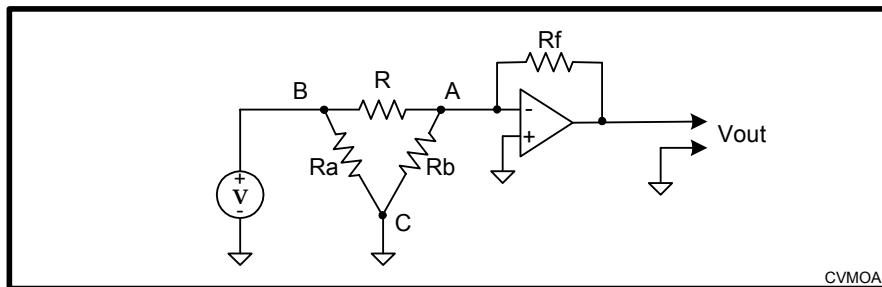

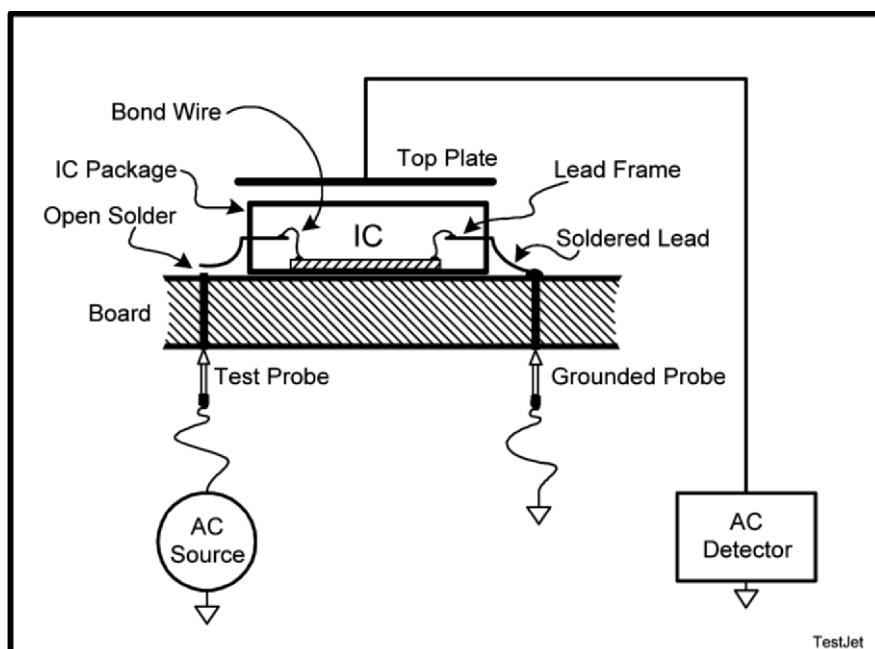

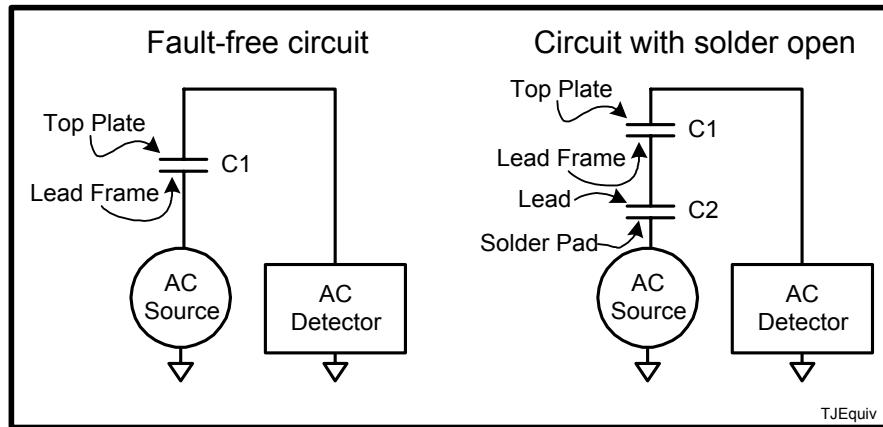

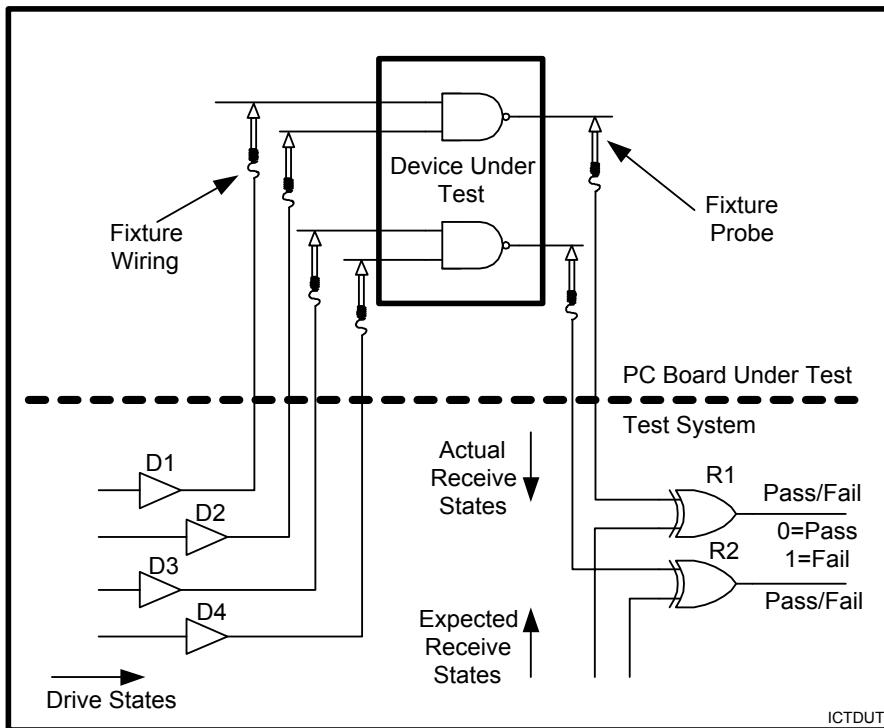

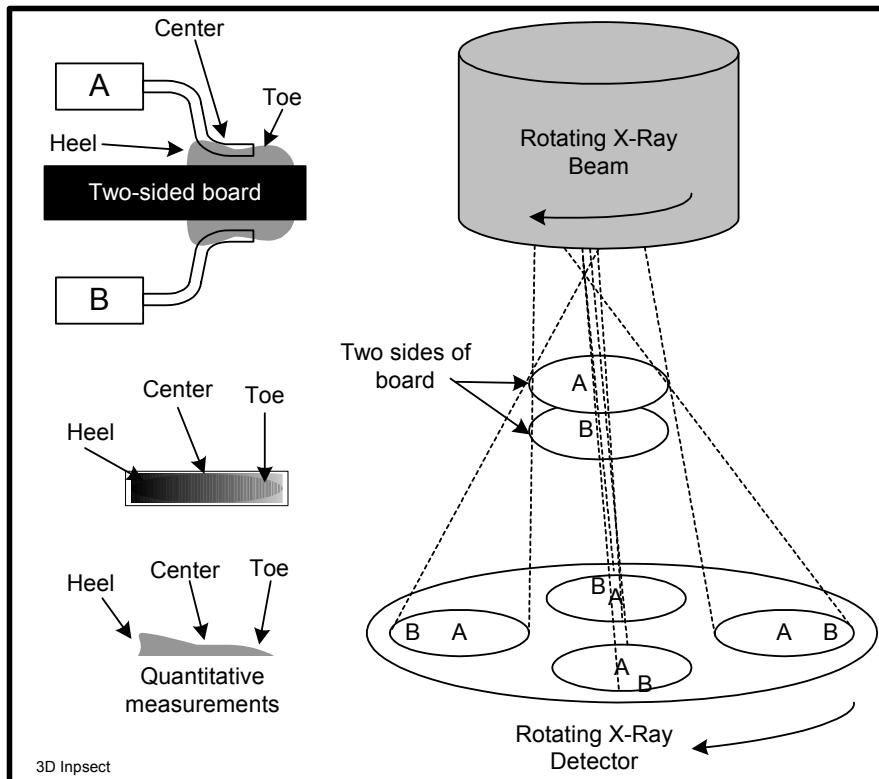

### **Fault Diagnosis**