SPRINGER BRIEFS IN

ELECTRICAL AND COMPUTER ENGINEERING

Silvian Spiridon

# Toward 5G Software Defined Radio Receiver Front-Ends

Springer

# SpringerBriefs in Electrical and Computer Engineering

More information about this series at <http://www.springer.com/series/10059>

Silvian Spiridon

# Toward 5G Software Defined Radio Receiver Front-Ends

Springer

Silvian Spiridon

Tustin, CA, USA

ISSN 2191-8112                   ISSN 2191-8120 (electronic)

SpringerBriefs in Electrical and Computer Engineering

ISBN 978-3-319-32758-7       ISBN 978-3-319-32759-4 (eBook)

DOI 10.1007/978-3-319-32759-4

Library of Congress Control Number: 2016943312

© Springer International Publishing Switzerland 2016

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made.

Printed on acid-free paper

This Springer imprint is published by Springer Nature

The registered company is Springer International Publishing AG Switzerland

*To my family*

*Motto: Simplicity is complexity resolved*

Constantin Brincusi

# Foreword

The first GSM telephone conversation took place in July 1991. This achievement was the result of a herculean R&D collaboration between major telecom industry manufacturers from 13 European countries. And it took us 10 years to develop. The task was huge, involving various engineering disciplines for defining the network architecture, protocols, modulation schemes, and digital signal processing algorithms, for designing integrated circuits, and for organizing the handover between different telecom operators. And all this happened in a political context with conflicting national interests and language barriers.

And yet, looking in retrospect, GSM was relatively easy. It involved only one type of modulation (GMSK) and only one multiplexing scheme (TDMA). Initially, there was only one frequency band allocated for this new communications medium (around 900 MHz), and all communications used the same channel bandwidth (200 kHz).

By the time that the GSM technology became mature and the sales figures reached their height, the successor technology was already available: In 2001, exactly 10 years after the GSM launch, the first 3G networks came into operation. The new technology offered a 30-fold data rate increase, compared with the original GSM technology. Therefore, it came just at the right moment to grasp the wave of Internet explosion. And again, it took us 9 years of R&D efforts to develop. But by that time, European manufacturers had already lost their lead to companies in the USA and Far East.

The 3G air interface is less “unified” than its 2G counterpart: although the 3GPP standard clearly defines the channels (5 MHz) and the modulation scheme (WCDMA), there are 31 frequency bands ranging from 850 MHz to 3.5 GHz. This renders the design of a radio front end more complex and calls for some “programmability” of the radio center frequency.

After 3G came 4G: in response to customer demand for increasing data rates, a new radio technology was introduced, based on orthogonal frequency-division modulation. Although, initially, there were two competing standards named WiMax (introduced for the first time by Sprint in 2007 and heavily backed by Intel) and LTE (backed by the 3GPP consortium and implemented in a commercial phone for the first time in 2011), only the LTE system survived. And again, 10 years of R&D efforts passed between the first WiMax specification and the first LTE phone.

From a radio front-end perspective, LTE is even less unified: not only are there more than 20 frequency bands allocated, the channel bandwidth itself can vary according to the needs of the customer and to the signal-to-noise ratio of the radio channel. This calls for programmability of the cutoff frequencies of all filters in radio receiver and transmitter.

I know that it starts to be boring, but after 4G comes 5G: resulting from the ever-increasing need for higher-speed data communications and more network capacity (to serve the Internet of Everything), it is forecasted that the 4G networks will run out of steam. If we extrapolate the history (2G in 1991, 3G in 2001, 4G in 2011), 5G would arrive in 2021. And again from a historical extrapolation, it will take us 10 years of R&D efforts to develop it. Hence, by now, we should be very busy designing integrated circuits for this new technology. But unfortunately, this is not the reality. At present, it is unclear what 5G will be. It is unclear what user scenarios will be served. It is unclear what modulation schemes, what antenna techniques, what radio frequencies, or what bandwidths will be used. However, one thing is certain: 5G will not exploit a single air interface. It will be a combination of multiple standards, to be used for different user scenarios and for different network conditions. One might expect a combination of low-power standards such as ZigBee for low-rate applications (e.g., readout of electricity meters or other sensor interfaces), of millimeter-wave high-bandwidth radio standards exploiting multiple-antenna technologies for high-speed data communications in urban areas, of dedicated radio technologies for communications between cars or between wearable devices, and of legacy backup technologies for rural areas where the cost of new deployments is not justified. Furthermore, since radio spectrum is scarce, there will be no unique worldwide frequency band available. Hence, the number of different allocated frequency bands can only increase.

Another lesson from history shows us that customers want the benefits from new technologies, *at zero additional cost*. For an early-adopter 5G phone, cost will be less important. But in time, it will be of prime importance that we are able to build such a complex multi-standard 5G phone in a cost-effective way. Therefore, it will be necessary that multiple communications protocols share the same radio receiver and transmitter circuits.

As a result, for the first time, 5G will require programmability, not only of the radio center frequency and the channel bandwidth but also *of the modulation*

*scheme itself.* This means that the circuits will have to allow for varying, under software control, of such aspects as the signal gain partitioning, the filter roll-off, the selectivity, the transmitter out-of-band noise, and, most important, the power consumption.

This book therefore arrives exactly in time.

Leuven, Belgium, 2016

Dr. Frank Op 't Eynde

RFIC consultant

# Preface

The advent of wireless communications of the last decades has spun an exponential increase in the number of users, hardware, and data rates. On the brink of the fifth wave of wireless system development (5G), it is forecasted that the world will become even more interconnected at ever-growing speeds. The radio front-end circuit designer needs to be prepared to handle this imminent wave. This translates to the designer being ready to interpret quickly any wireless standard.

This book brings to light a new approach aimed at finding the optimal design path for next-gen software-defined radio receiver front-ends (SDRXs): a standard-independent structured design methodology, which is setting the receiver architecture and electrical specifications and meets the submicron CMOS transistor-level implementation constraints that drive the topologies of the SDRX building blocks.

In my opinion, in today's design world, the main design challenges reside at system level, as significant progress has been made to improve the key RF and mixed-signal circuits performance.

First, I find a lack of a systematic approach in the system-level analysis of SDRXs and create a standard-independent, systematic methodology to help derive the receiver key electrical specifications. The novelty consists in the fact that the developed methodology empowers the designer to tackle the multi-standard environment in a parallel way rather than serially, as is the case with previous published works. This is a critical feature for any design methodology targeting 5G circuits and systems. The methodology is based on manual analysis that suits best an intuitive understanding, as this is the most efficient way for a designer to have the grasp on the design process.

Throughout the book, the SDRX design follows the key wireless standards of the moment (i.e., GSM, WCDMA, LTE, Bluetooth, WLAN), since a receiver compatible with these standards is the most likely candidate for the first design iteration in a 5G deployment. Thus, a multi-standard SDRX is constructed. Due to the newly developed standard-independent system-driven design methodology, the designer is enabled to handle efficiently the large amount of information provided in the wireless standards and to remain in control of the system being designed. Moreover,

this methodology has the advantage in that it can be used very effectively in the case of the new, soon-to-be-developed, wireless standards of the 5G wave.

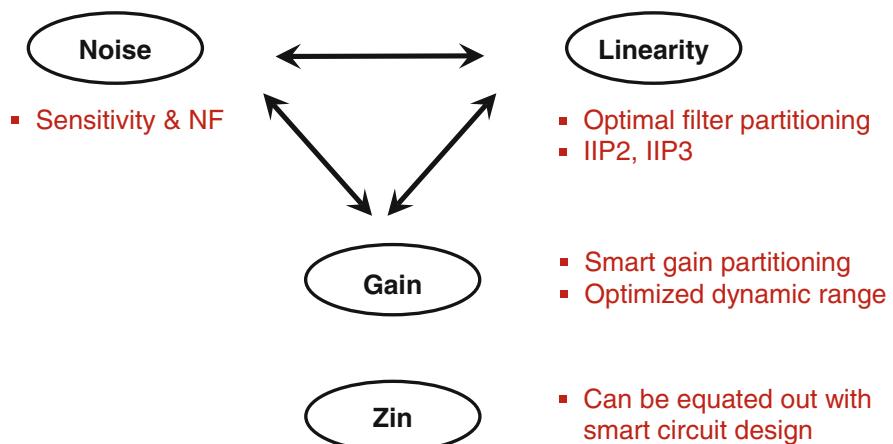

Hence it is shown that direct conversion architecture is the most suited choice for the SDRX. Further on, I demonstrate the fundamental choice the designer has to make is the optimal channel selection: how much of the blockers/interferers will be filtered in the analog domain and how much will remain to be filtered in the digital domain. Also this opened the path for the novel “smart” gain–noise–linearity partitioning tailored toward SDRXs that optimally leverages the extreme reception conditions specific to the wireless environment.

With the new analysis methodology, this book lays down a concept in creating standardized tools for tomorrow’s SDRX designers. Basically, these tools represent the compass used to explore the SDRX domain map.

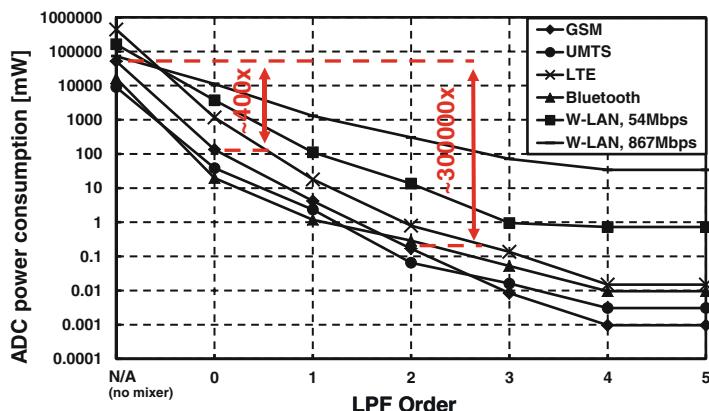

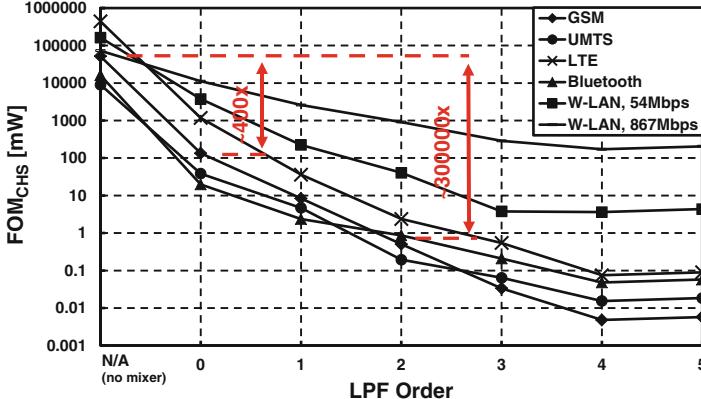

The introduction of the new and efficient tool *the generic blockers diagram*, together with the newly defined figure of merit (FOM)  $FOM_{CHS}$ , enabled the proper evaluation of the key trade-off that shapes the receiver design: the trade-off between the receiver low pass filter (LPF) area and its analog-to-digital converter (ADC) power consumption; thus, the optimum filter partitioning between the SDRX baseband analog LPF and the digital filter following the ADC is found in one single plot.

One of the key features of the developed system-level analysis is that the direct sampling architecture is treated as a particular case of mixer-based direct conversion architecture. Thus, given a power consumption budget, one can evaluate specifically, by considering the ADC performance characteristics and the corresponding blocker diagram, how much filtering is required on the receive path.

Finally, I would like to take this opportunity to acknowledge Dr. Frank Op’t Eynde for our countless technical discussions that consolidated the research revealed in this book and Dr. Klaas Bult for his always-present insightful technical observations that were of great aid in understanding the art of IC design. Also I would like to express my sincere gratitude to my Ph.D. advisor and mentor Prof. Mircea Bodea.

Tustin, CA

Silvian Spiridon

# Contents

|          |                                                                                  |           |

|----------|----------------------------------------------------------------------------------|-----------|

| <b>1</b> | <b>Overview of Wireless Communication in the Internet Age . . . . .</b>          | <b>1</b>  |

| 1.1      | Software Defined Radios . . . . .                                                | 1         |

| 1.1.1    | Digital Communications of the Internet Age . . . . .                             | 3         |

| 1.1.2    | The Need for Software Defined Radios . . . . .                                   | 6         |

| 1.1.3    | The Software Defined Radio RF Front-End . . . . .                                | 8         |

| 1.2      | Goals . . . . .                                                                  | 9         |

| 1.3      | Overview . . . . .                                                               | 10        |

|          | References . . . . .                                                             | 11        |

| <b>2</b> | <b>Defining the Optimal Architecture . . . . .</b>                               | <b>13</b> |

| 2.1      | Introduction . . . . .                                                           | 13        |

| 2.2      | Overview of Receiver Architectures: Following<br>the Image Rejection . . . . .   | 14        |

| 2.2.1    | Superheterodyne Receivers . . . . .                                              | 14        |

| 2.2.2    | Image Rejection Receivers . . . . .                                              | 17        |

| 2.2.3    | Direct Conversion Receivers . . . . .                                            | 18        |

| 2.2.4    | Low-IF Receivers . . . . .                                                       | 20        |

| 2.3      | Final Decision: w/ IF vs. w/o IF (Zero-IF) . . . . .                             | 20        |

| 2.3.1    | Receiver Block Schematic . . . . .                                               | 22        |

| 2.4      | Making Direct Conversion Receivers Ready for Monolithic<br>Integration . . . . . | 23        |

| 2.4.1    | Key Issues . . . . .                                                             | 23        |

| 2.4.2    | DC Offset Compensation . . . . .                                                 | 24        |

| 2.4.3    | Reducing Self-Mixing . . . . .                                                   | 26        |

| 2.4.4    | Enhanced Receiver Schematic . . . . .                                            | 26        |

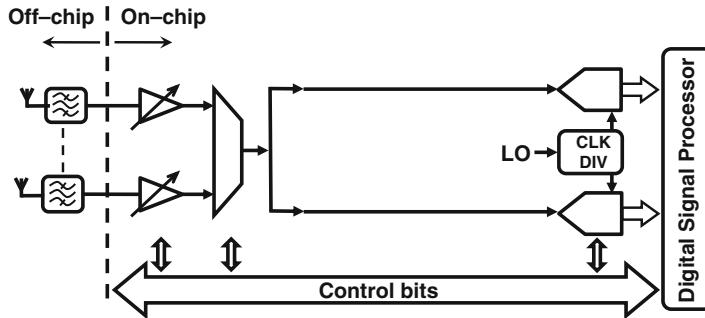

| 2.4.5    | Architectural Evolutions: Filter-Less and Mixer-Less<br>Front-Ends . . . . .     | 27        |

| 2.5      | Conclusions . . . . .                                                            | 28        |

|          | References . . . . .                                                             | 29        |

|                                                                                                                                      |    |

|--------------------------------------------------------------------------------------------------------------------------------------|----|

| <b>3 From High-Level Standard Requirements to Circuit-Level Electrical Specifications: A Standard-Independent Approach . . . . .</b> | 31 |

| 3.1 Multi-standard Environment Impact on the SDRX Building                                                                           |    |

| Block Features . . . . .                                                                                                             | 31 |

| 3.1.1 Multiple Frequency Bands . . . . .                                                                                             | 31 |

| 3.1.2 Variable Channel Bandwidths . . . . .                                                                                          | 31 |

| 3.1.3 Different Burst Durations . . . . .                                                                                            | 33 |

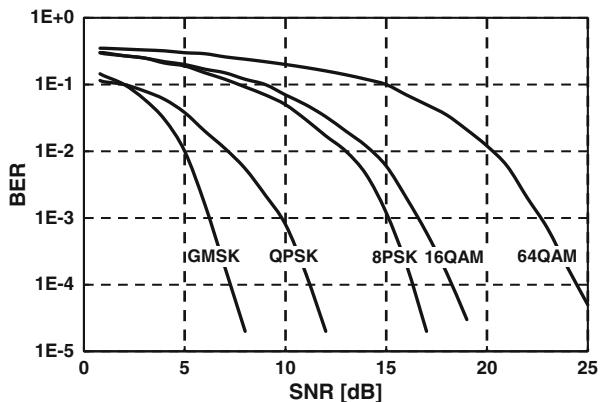

| 3.1.4 Different Modulation Schemes and Techniques . . . . .                                                                          | 33 |

| 3.2 Introducing the Minimum SNR for Proper Signal Demodulation . . . . .                                                             | 33 |

| 3.3 Deriving the SDRX Noise Figure . . . . .                                                                                         | 36 |

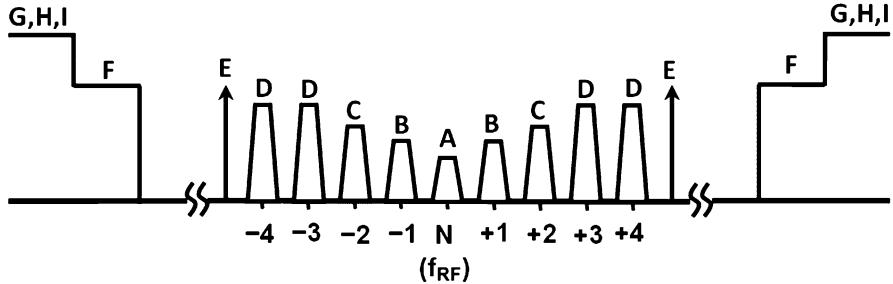

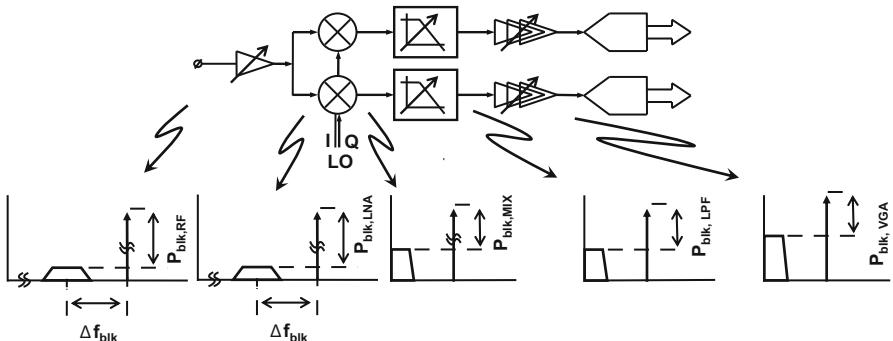

| 3.4 Generic Blocker Diagram . . . . .                                                                                                | 36 |

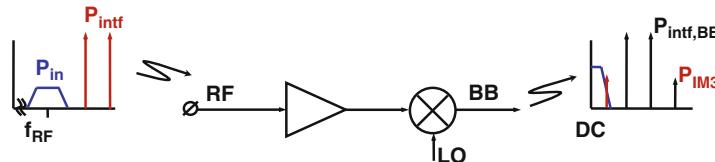

| 3.5 Blocker and Interferer Impact on the SDRX Linearity . . . . .                                                                    | 37 |

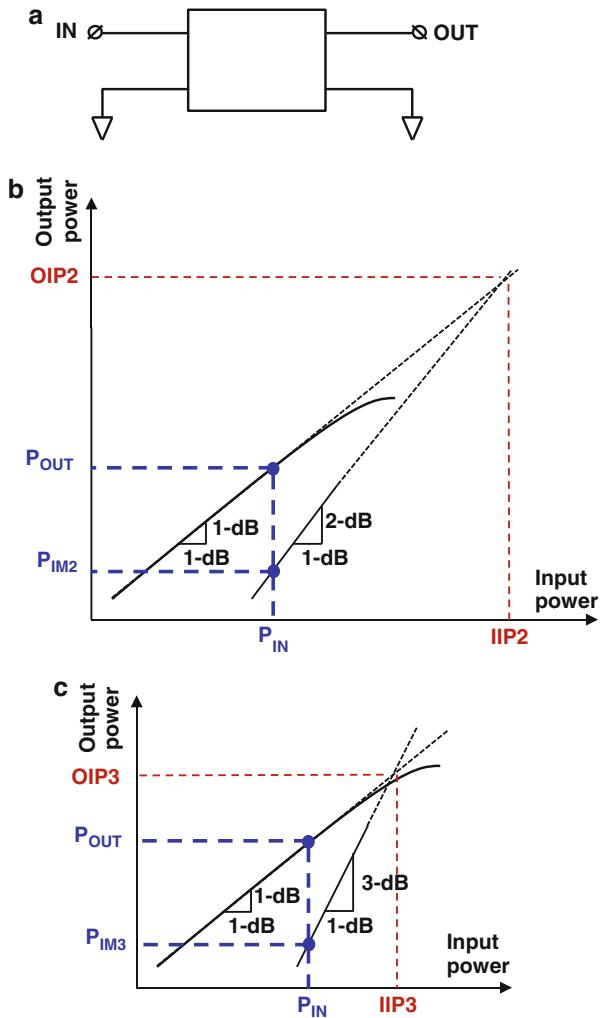

| 3.5.1 Finding the SDRX IIP2 . . . . .                                                                                                | 39 |

| 3.5.2 Finding the SDRX IIP3 . . . . .                                                                                                | 41 |

| 3.6 LO Phase Noise Impact on the Receiver . . . . .                                                                                  | 42 |

| 3.7 Conclusion . . . . .                                                                                                             | 43 |

| References . . . . .                                                                                                                 | 44 |

| <b>4 Optimal Filter Partitioning . . . . .</b>                                                                                       | 45 |

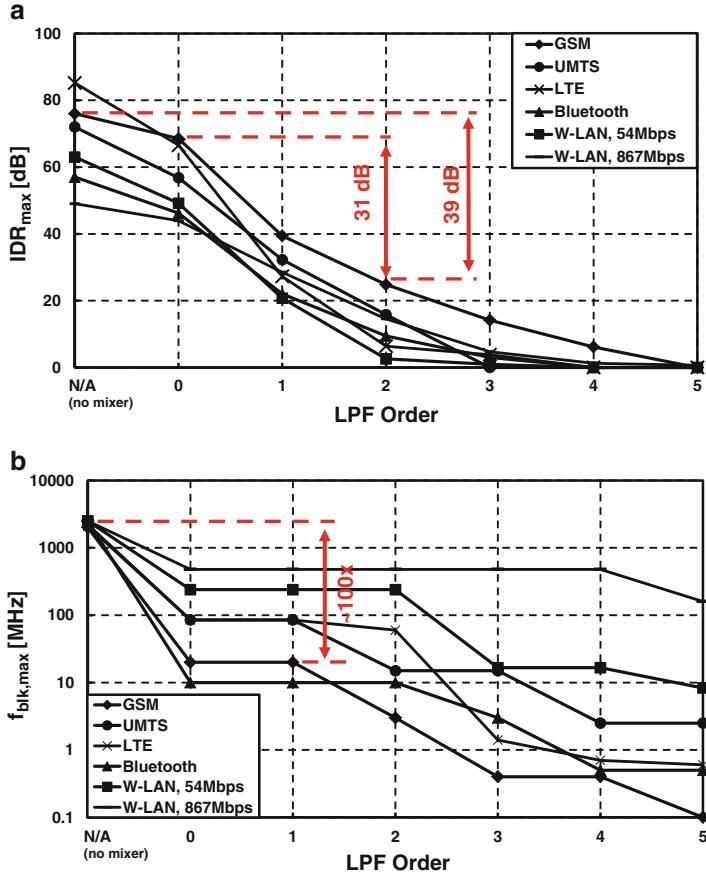

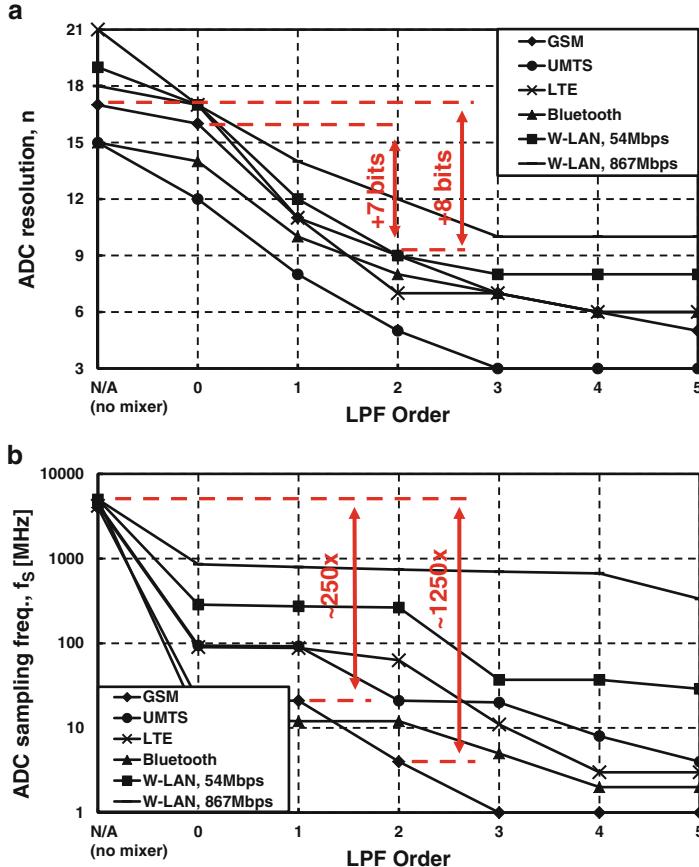

| 4.1 Defining the Channel Selection Strategy . . . . .                                                                                | 45 |

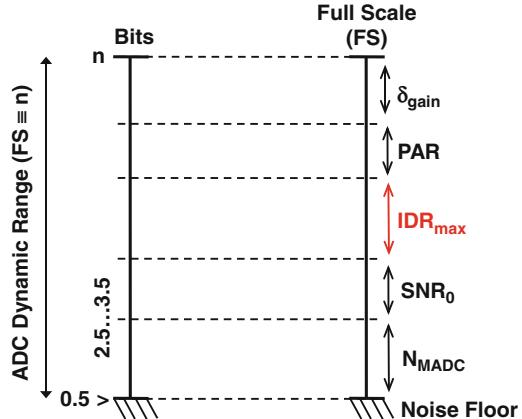

| 4.2 Deriving the ADC Specifications . . . . .                                                                                        | 46 |

| 4.3 The Optimal Trade-Off Between LPF Order and ADC Specifications . . . . .                                                         | 50 |

| 4.4 Conclusion . . . . .                                                                                                             | 53 |

| References . . . . .                                                                                                                 | 54 |

| <b>5 Smart Gain Partitioning for Noise: Linearity Trade-Off Optimization . . . . .</b>                                               | 55 |

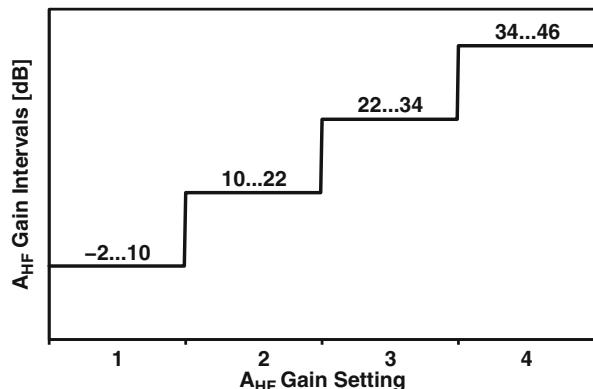

| 5.1 Proposed Gain–Noise–Linearity Partitioning Strategy . . . . .                                                                    | 56 |

| 5.2 Defining the SDRX Gain Settings . . . . .                                                                                        | 58 |

| 5.3 Proposed Gain Partitioning Algorithm . . . . .                                                                                   | 61 |

| 5.4 The Automated Gain Control Loop . . . . .                                                                                        | 63 |

| 5.5 Conclusion . . . . .                                                                                                             | 63 |

| Reference . . . . .                                                                                                                  | 64 |

| <b>6 SDRX Electrical Specifications . . . . .</b>                                                                                    | 65 |

| 6.1 Electrical Specifications . . . . .                                                                                              | 65 |

| 6.2 Noise Partitioning . . . . .                                                                                                     | 65 |

| 6.3 Linearity Partitioning . . . . .                                                                                                 | 68 |

| 6.4 Conclusion . . . . .                                                                                                             | 70 |

| Reference . . . . .                                                                                                                  | 70 |

|                                                                             |    |

|-----------------------------------------------------------------------------|----|

| <b>7 A System-Level Perspective of Modern Receiver</b>                      |    |

| <b>Building Blocks</b>                                                      | 71 |

| 7.1 SDRX HF Part Building Blocks                                            | 71 |

| 7.1.1 The Wideband Low-Noise Amplifier                                      | 71 |

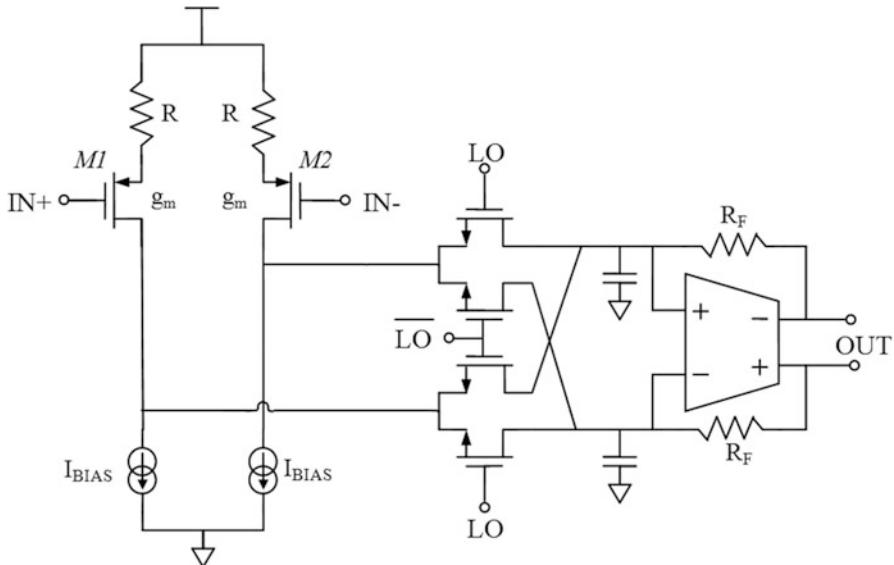

| 7.1.2 The Highly Linear Downconversion Mixer                                | 73 |

| 7.2 SDRX LF Part Building Blocks                                            | 75 |

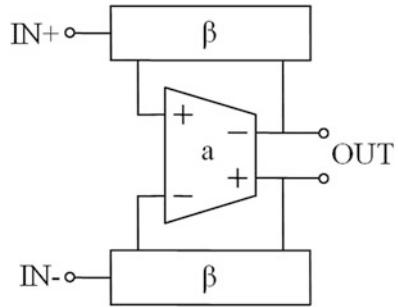

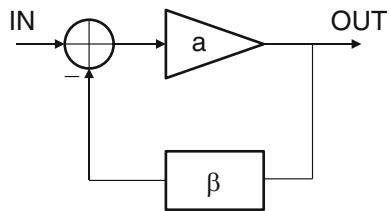

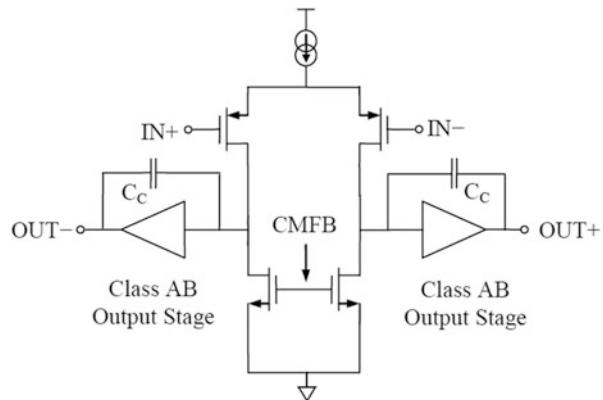

| 7.2.1 The LF Part Building Brick: The Fully Differential Feedback Amplifier | 75 |

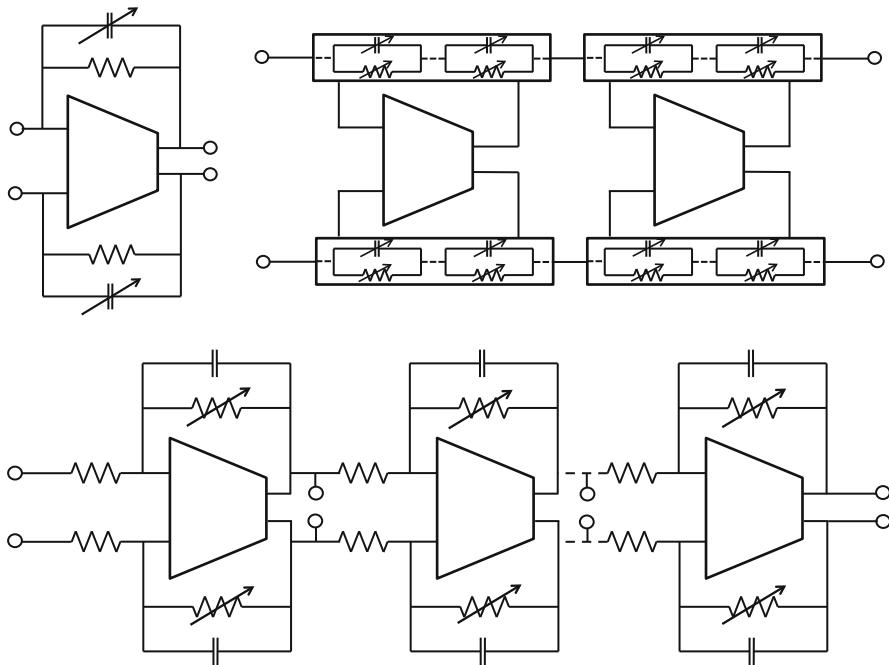

| 7.2.2 LF Part Modular Architecture                                          | 77 |

| 7.2.3 FDFA Power Optimization                                               | 78 |

| 7.2.4 FDFA Opamp Generic Topology                                           | 80 |

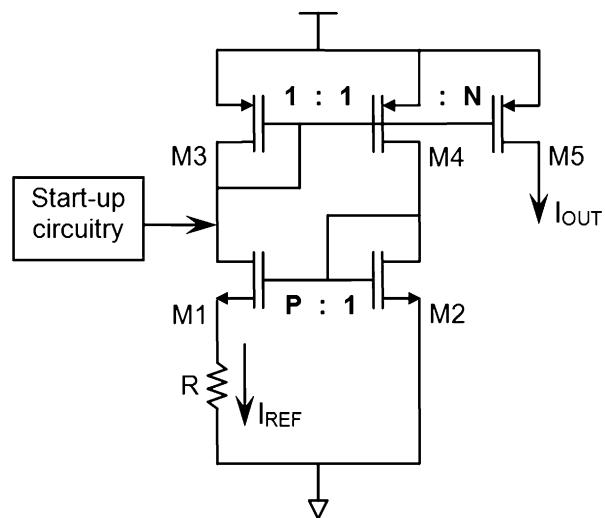

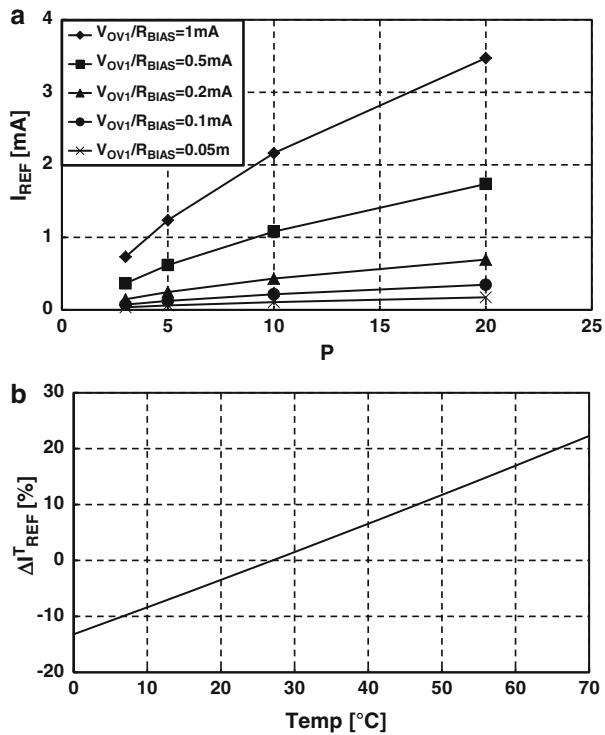

| 7.3 SDRX Bias Block                                                         | 81 |

| 7.4 Baseband Noise Partitioning                                             | 83 |

| 7.4.1 Noise Excess Factor                                                   | 83 |

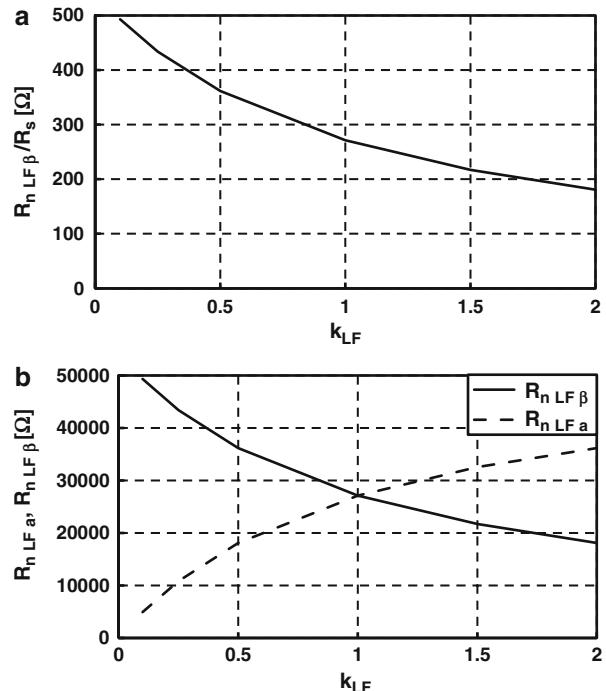

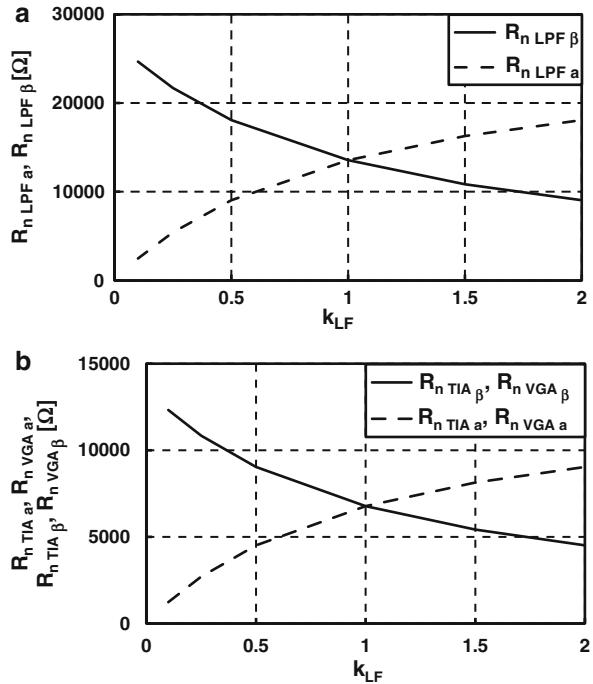

| 7.4.2 The Trade-Off Between LF Part Power Consumption and Area              | 85 |

| 7.4.3 Noise Partitioning                                                    | 86 |

| 7.5 Conclusion                                                              | 87 |

| References                                                                  | 88 |

| <b>8 Conclusions and Future Developments</b>                                | 91 |

| 8.1 Conclusions                                                             | 91 |

| 8.2 Future Developments                                                     | 94 |

| References                                                                  | 95 |

# Chapter 1

## Overview of Wireless Communication in the Internet Age

### 1.1 Software Defined Radios

Communication is an intrinsic part of the human nature. Through communication information is conveyed. The simplest model of a communication system requires the presence of a transmitter and a receiver. The communication process takes place between receiver(s) and transmitter(s) over the communication medium or channel.

The first communication system, in a relaxed interpretation, was the postal service. The first well-documented postal service was organized in Rome during the times of Augustus Cesar, around 50 BC. The common information conveyed through this service were letters, and given the high service cost and the low level of literacy, only few people could make use of it. Since then its evolution was fairly slow, as the service was based on the horse powered couriers for almost two millennia.

It wasn't until late nineteenth century when a real breakthrough happened: the invention of the telegraph by Carl Friedrich Gauss and Wilhelm Weber in 1833. The telegraph allowed long distance communications through copper wires, giving birth to the terminology of wired communications. By 1866, the telegraph had opened the era of instant transatlantic communication that would shape the century to come.

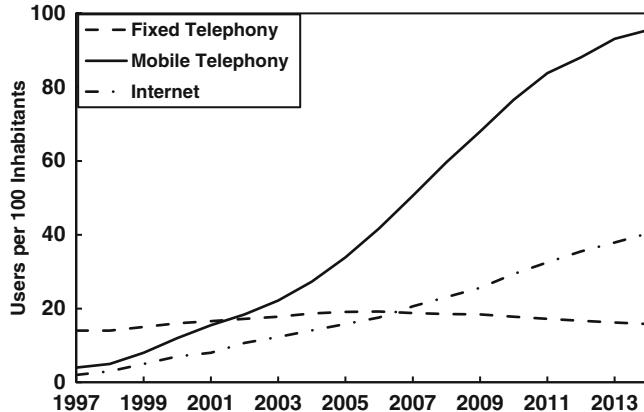

The next important milestone in the communication history is the patent awarded to Alexander Graham Bell for the electric telephone by the United States Patent and Trademark Office (USPTO) in March 1876. This milestone represents the birth date of the fixed telephony service. Since then the service expanded continuously to peak at about 19 fixed telephone lines per 100 inhabitants in 2006, see Fig. 1.1 [1].

Following the experiments of Hertz, which targeted to prove Maxwell's equations, Gugliemo Marconi has managed to develop a wireless telegraph system by 1895, opening the realm of wireless communications. In 1909, he was awarded the Nobel Prize, shared with Karl Ferdinand Braun, in recognition of his contributions to the development of wireless telegraphy.

**Fig. 1.1** Internet usage—the driving force behind the need for SDRs

Originally radio communications served mainly military and broadcasting services. It was until 1973, when the first hand-held wireless devices were available for the large public.

Moving closer to present times, if in the beginning of the twentieth century, the analog fixed telephony was just introduced, by the end of the same century the wireless revolution conquered the planet. By the beginning of the year 2015, the mobile telephony growth reached an astonishing peak of 96 subscribers per 100 inhabitants worldwide [1].

Two very important milestones for the development of the communication sector were the invention of what is known today as the “Internet” in 1969 in the USA, and the development of the Personal Computer (PC). The PC was also introduced for the first time in the USA by Apple in 1976. By allowing all PCs to be connected into a world wide web, the Internet opened the market for broad-band personal connections.

The Internet foundations were laid in 1960s by the USA military research projects aimed at building distributed computer networks. The internet mass global spread was delayed due to lack of networking infrastructure and limited number of PC users. However, in mid-1980s the PC market boomed due to IBMs Personal Computer based on Intel 80286 microprocessor and operated by Microsoft’s Disk Operating System (MS-DOS). This combination formed the template for all PC developers and vendors. Hence, during the 1990s, it was estimated that the number of Internet users doubled each year, with a brief period of explosive growth in 1996 and 1997. By end of 2014, the Internet reached about 41 users per 100 inhabitants worldwide, see Fig. 1.1 [1].

In order to show the strong relation between the IT industry and the communication sector, Fig. 1.1 plots the number of worldwide subscribers of fixed and mobile telephone networks and Internet users. The Internet access connects the two sectors.

In the early 1990s, the Internet used the long established fixed telephony infrastructure to reach the large audience. The latest trends show the communication sector is strongly going mobile, as today the mobile subscribers number surpasses the fixed telephony one by a factor of more than 5. This translated to the development of a market of mobile personal broad-band Internet access perfectly suited for the new set of electronic equipment, the “smart” mobile phone.

### ***1.1.1 Digital Communications of the Internet Age***

All the communication systems developed in the last two centuries are based on Maxwell’s equations [2]. The information is conveyed through the medium, either wired or wireless, in the form of electromagnetic waves or photons.

The Figure of Merit (FOM) for the information transfer is the data rate, defined as the amount of conveyed information divided by the amount of time required for it to be transferred between participants.

In 1949, Claude Shannon has calculated the maximum capacity, or data rate, of a communication channel characterized by Gaussian noise ( $N$ ) as a function of its bandwidth ( $BW$ ) and of the signal power ( $S$ ) at the receive side [3]:

$$\text{Channel Maximum Data Rate} = BW \log_2 \left( 1 + \frac{S}{N} \right) \quad (1.1)$$

Equation (1.1) comprises the key trade-off in digital communications: the trade-off between Signal-to-Noise Ratio (SNR) and channel bandwidth, or equivalently, between the modulation scheme complexity and BW. In the last 50 years the need of faster and faster Internet access led to the continuous increase in the maximum data rate, as detailed in this section.

The increase of the communication data rate was driven by: (a) the increase in bandwidth (if and where it was possible) and (b) the increase in the modulation scheme complexity.

The Internet was initially developed as a “wired” network. There are four ways to get Internet access through a wired network, depending on the infrastructure available:

- Using fixed telephony network

- Through the cable TV infrastructure

- Via the power lines

- Optical fiber

The third option, although available in a large number of countries, is not so popular at present, due to the very hostile signal perturbations and impedance variations present on the medium.

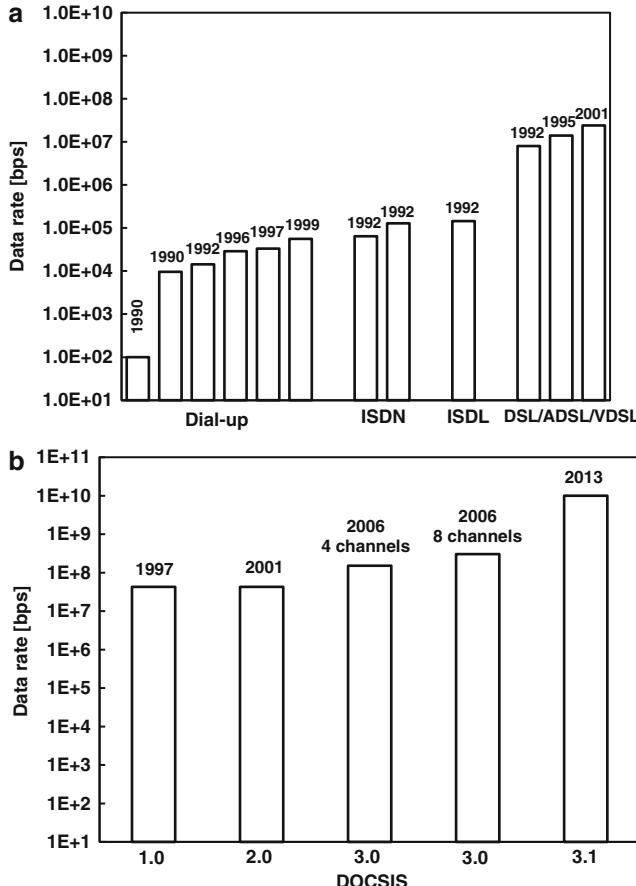

The evolution of the most popular Internet access methods over a wired copper cable over the past 20 years is presented in Fig. 1.2.

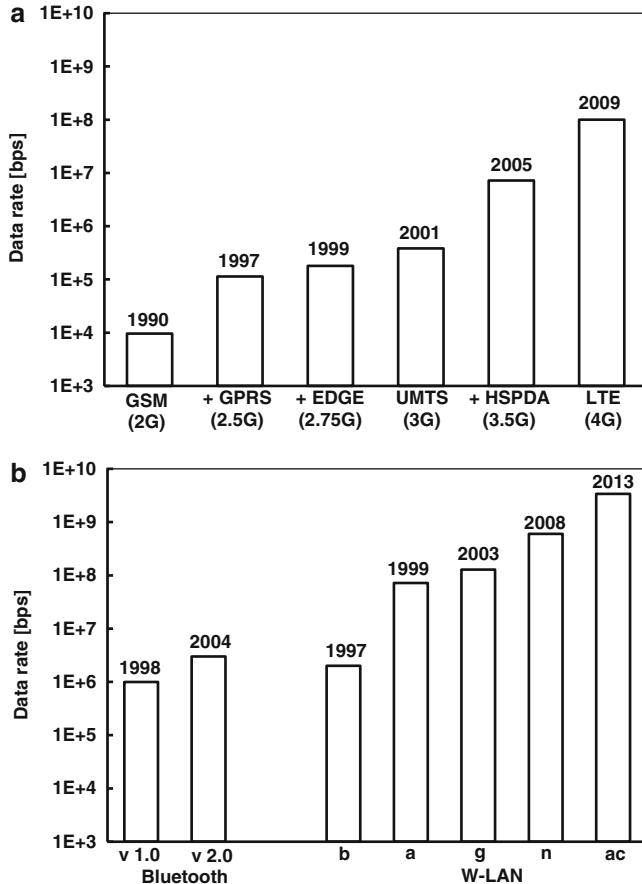

Given the latest trends revealed by Fig. 1.1, mobile Internet access became available. In the *wireless* communication sector, the most popular standard is by far the Global System for Mobile Communications or GSM [4] as it is estimated that 80% of the global market uses the standard. The first GSM standard has been introduced in 1990 and by the end of 1993 over a million subscribers were using GSM networks being operated by 70 carriers across 48 countries; in 2011, about 1.5 billion people across more than 212 countries and territories are using a mobile terminal under the GSM standard.

GSM is a long-range standard based on a cellular network architecture, with a cell having a maximum coverage range of 120 km. GSM represents the second generation (2G) wireless telephone technology, as its communication frame is digital as opposed to the first generation (1G) networks which implemented analog communication. Alongside the main voice service, due to the digital nature of its communication frame, GSM introduced the low-cost alternative of the Short Messaging Service (SMS). The Internet could be accessed over GSM networks through an equivalent dial-up service. Though, low data rates were possible (max. 9.6 kbit/s) as only one communication channel could have been used. Nevertheless, the information technology revolution empowered by the Internet expansion led to the extension of GSM to allow simultaneous voice and data communications and higher data transfer rates: in 1997, the General Packet Radio Service (GPRS) has been introduced and provided data rates of 56–114 kbps. GPRS consists in allocating more than one of the multiplexed time slots for a given communication. The embedding of GPRS into a 2G GSM network represented an intermediate step (2.5G) before the third generation (3G) wireless network. By 1999, even higher data rates could be achieved as Enhanced Data Rates for GSM Evolution (EDGE) GSM extension (2.75G) was able to allow 180 kbps. EDGE is an extension of GPRS whereby the classical 1-bit-per-symbol GMSK modulation is replaced by an 8-phase modulation scheme.

Further on the development of the standard led to the birth of the 3G wireless telephony networks: Universal Mobile Telecommunications System (UMTS) [5]. UMTS data transfer can reach 384 kbps. If the 3G UMTS network implements the High-Speed Downlink Packet Access (HSDPA), this combination being considered the 3.5G, it can reach a downlink data rate of 7.2 Mbit/s. The Long Term Evolution (LTE) [6] project upgrades UMTS to 4G. 4G systems are providing data rates in the range of 100 Mbit/s. The continuous increase in the data rate from 2G to 4G networks is due to the permanent enhancement of the implemented modulation schemes/techniques, to the channel bandwidth increase and to the enhancement of multiple access methods. Furthermore, the data rate is foreseen to increase to Gbit/s when 5G systems will be deployed.

Given the large number of world-wide users, GSM-UMTS-LTE are by far the standards driving the world of wireless mobile communication. However, also short-range standards have been created to allow broadband Internet access and

to enhance wireless interoperability of mobile terminals. Amongst them, the most popular at present are W-LAN and Bluetooth.

A wireless local area network (W-LAN) connects various devices through a wireless distribution method [7]. Although originally developed for interconnecting standalone desktop PCs, the standard became popular, given the success of notebook computers. Nowadays, W-LAN compatibility is also a key feature of the most advanced mobile terminals, or smart phones. The W-LAN protocol is regulated by the IEEE 802.11 family of standards [7–12]. The original standard introduced in 1997 specified two data rates of 1 and 2 Mbit/s. When first updated (to revision a) in 1999, it allowed a gross bit rate of 54 Mbit/s. By 2003, the new g flavor was able to provide 128 Mbit/s when the BW was increased from the normal 20 to 40 MHz. By 2009, the next W-LAN amendment, the version n, is able to offer an astonishing data rate of up to 600 Mbit/s, by exploiting MiMo techniques. And, the latest addition, the ac version, can deliver up to 3.39 Gbit/s due to the channel bandwidth increase to 160 MHz and the use of four antennas.

Bluetooth is a wireless protocol for exchanging data over short distances. Introduced in 1998, the version 1.2 has a data rate of 1 Mbit/s. By 2004, the protocol was updated to version 2.0 that allows 3 Mbit/s [13]. In 2009, the third version included a high-speed feature that used the collocated W-LAN link to transmit data with rates up to 24 Mbit/s [14]. And, the fourth version, in 2010, added features for low power operation [15].

Figure 1.3 plots the evolution of the maximum data rate of both long-range wireless standards and short-range ones.

In order to simplify the communication, the latest wireless standards converge towards a “one size fits all” solution, e.g., IEEE 802.16m or WiMAX mobile [16]. The standard, introduced in 2007 and updated in 2009, embeds the feature of both long- and short-range communication standards by using almost all modulation schemes and by enforcing a variable channel bandwidth.

Hence, depending on the wireless link SNR, the WiMAX network can adjust dynamically its data rate, from a minimum of a few kbps to maximum of 100 Mbit/s. The 3GPP Long Term Evolution (LTE) standard introduced by the Mobile Communications operators is the competitor for WiMax. Although LTE and WiMax use comparable technologies and offer a comparable user experience, LTE won the battle.

In conclusion, all the wireless digital communication of the future will have to embed the main features of LTE, features that make the standard fit perfectly the drive to reach both higher data rates and cover a longer distance, as it results for (1.1):

- Compatibility with a large number of modulation schemes/techniques

- The ability to handle multiple RF frequency bands and variable baseband channel bandwidths

Finally, by comparing the plots from Figs. 1.2 and 1.3, we can clearly state that the wireless communication is catching-up fast with the wired communication data rate.

**Fig. 1.2** Internet access data rate of copper wire networks: (a) Fixed telephony; (b) Cable TV

### 1.1.2 The Need for Software Defined Radios

One of the major problems in the mobile communication systems of today is that every standard requires a particular set of hardware equipment to allow a compatible dialogue. On top of it, because implementation details differ from network operator to network operator, even the same standard requires different hardware depending on the continent of deployment. The most prominent example is LTE that can be found worldwide on 44 frequency bands (see Table 3.1).

A similar issue characterized the early beginnings of the IT industry in 1980s. There was no compatibility in between different Personal Computers (PCs) available on the market. The major differences that impeached the development of the overall sector were the lack of uniformity in both data storage and data

management. The natural solution to these issues turned out to be the “WINTEL” monopoly, an Intel-based PC run by a Microsoft Operating System (OS). Basically, all the divergent trends in the IT sector converged to making the “WINTEL” platform the dominant desktop and laptop computer architecture.

For the mobile communication sector the development was completely different to allow a similar monopoly to be formed. The globalization allowed various players to enter the geographically different markets at about the same time, thus fairly dividing the market share. Also, in terms of frequency band allocation, the various independent national/federal/continental organizations allocated different bands for the same particular standard.

The present business environment is a global one, requiring constant travel. Not only that, but also, leisure activities (like tourism) fit the same profile. Since, unifying various communications standards is not a real possibility, given the huge number of users dedicated to a given wireless standard there is a request of mobile equipment that needs to ensure compatibility over a wide variety of environments.

On top of it the current mobile devices evolved into real portable PCs. A 2015 handset includes an FM radio, MP3 player, MPEG4 media player, backed by a multi-core processor. All these hardware features are coordinated via an operating system: the most popular ones are the iOS, Microsoft, and Android. Hence, purely on the communication side, the present mobile equipment requires compatibility with all the standards maximizing its interaction capabilities: GSM/GPRS, UMTS, LTE, Bluetooth, Wireless LAN. Further on, considering the 5G deployment, the mobile terminal needs to cope with new standards enhancing its connectivity, by also providing backwards compatibility.

The first obvious solution was to incorporate for each standard a separate dedicated IC or ASIC (Application Specific Integrated Circuit) into the mobile device. One still has to have in mind that the first Nokia mass production GSM mobile phone, the Nokia 1011 developed in the early 1990s, was built from more than a two dozen separate ICs and weighted about half a kilo, while by mid-2000s, solutions offering fully integrated quad-band GSM SoCs were already available.

A first step in cost reduction was allowed by CMOS technology scaling: It opened the possibility of building “combo” ASICs, combining two or more SoCs on the same IC. However, these circuits still contain one RF front-end per communications standard.

So, in order to reduce cost even further, another step must be taken. In the IT world of the late 1970s this step came naturally, as INTEL developed what it turned out to be a general-purpose microprocessor. This approach allowed the hardware manufacturer to grasp almost all the consumer market, as its microprocessor turned out to be used in almost all commercial applications. Given the historical differences between the IT industry and the mobile communication sector development, such a scenario did not occur in the latter domain.

Building a reconfigurable ASIC, able to ensure compatibility with the wide array of communication standards in use today, is efficient from two main reasons:

- One “universal” design is required; thus design, packaging, and testing costs are minimized.

- As the “universal” ASIC is compatible with a wide array of wireless communication standards, the previous various ASICs can be merged; thus the overall area of ASICs comprised in a mobile terminal is minimized.

In the “digital” realm, the first step on this track is the development of the new multi-core DSP architectures. Such processors optimally leverage the power consumption with the cost, or equivalently occupied die area. The idea is to enforce as much parallel processing as possible to maintain a maximum “usage” of the chip die area during operation.

In this context, it is required to develop a transceiver capable to interface such a DSP. The transceiver must have a versatile architecture, able to change its characteristics dynamically, given the wireless standard and communication burst it has to handle.

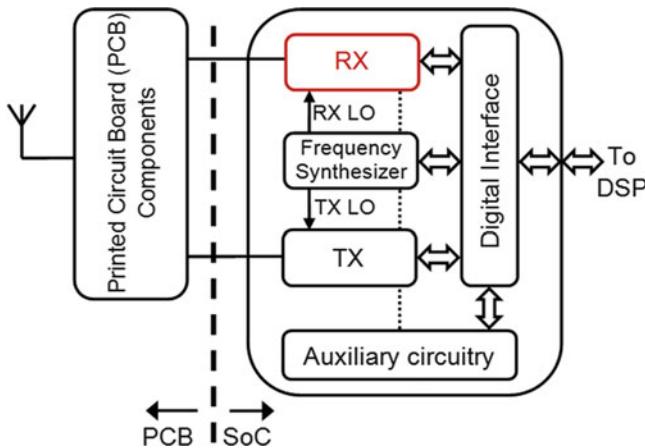

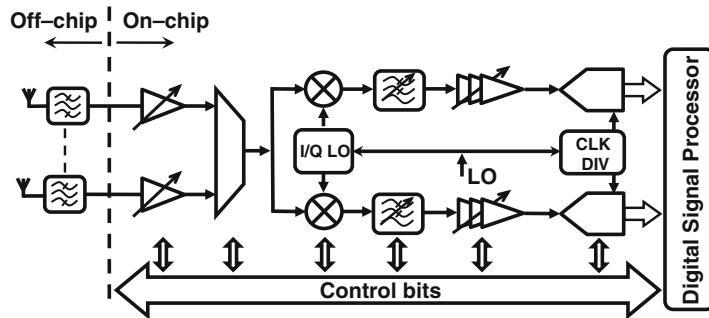

The optimal design of a re-configurable receiver front-end embedded in a software-driven System-on-a-Chip (SoC) represents the target of this book. The block schematic of the system is depicted in Fig. 1.4.

### 1.1.3 *The Software Defined Radio RF Front-End*

The three main blocks comprising the SDRX transceiver front-end of Fig. 1.3 are:

- The frequency synthesizer (FS), made out of a Phase Locked Loop (PLL) and a wide-band frequency divider (DIV)

- The receiver (RX)

- The transmitter (TX)

The transceiver acts as an analog signal conditioning block. It either prepares the received signal for digital demodulation or it shapes the digitally modulated signal for the wireless transmission. The digital signal processor (DSP), also known as the baseband processor, represents the digital back-end processing block. The DSP drives the analog front-end via the digital interface.

By dynamically changing the transceiver settings, its performance can be adjusted depending on the requirements (e.g., noise or linearity performance, output power level) of the particular communication burst.

The FS is the transceiver core. Its beat is represented by the generation of the local oscillator (LO) signals which drive the receiver, respectively the transmitter chain mixer.

The task of any wireless receiver is to ensure the received signal analog signal conditioning allows its correct digital demodulation.

Oppositely to the RX, the TX chain must ensure the up-conversion on the RF frequency of the digitally modulated baseband signal. In the transmitter case the accent is placed on (1) avoiding the disturbance of adjacent radio frequencies and (2) maintaining a good signal integrity. This implies the whole process of

**Fig. 1.3** Maximum Internet access data rates for the most popular commercial wireless standards: (a) Long range; (b) Short range

up-converting the wanted informational signal, from baseband to the RF carrier frequency, (1) dispenses almost all the transmitted energy into the allocated bandwidth in (2) a linear way.

## 1.2 Goals

The book is focused on the RF and analog signal conditioning part of the receiver of the System on Chip (SoC) in Fig. 1.3 and has the following four main goals:

1. The identification of the *most suited architecture for the Software Defined Radio Receiver* (SDRX), in the deep sub-micron era of CMOS processes

**Fig. 1.4** Software Defined Radio transceiver block schematic

2. *The development of new tools, based on simple and efficient models suited for manual analysis that enable the designer to handle efficiently the large amount of information comprised in the wireless standards.* In other words, the SDRR domain map is explored using these new tools as a compass

3. *The development of a new standard independent, system level driven design methodology that permits the identification of the optimal circuit solution in term of power and area saving*

4. *Using the newly developed system-to-circuit level design methodology to derive the key electrical specifications for the first design iteration of a general-purpose SDRX*

### 1.3 Overview

1. The book first goal, the identification of the most suited architecture for the SDRX, is discussed at large in Chap. 2.

Based on the analysis and evaluation of figures of merit of existing radio receiver architectures, the direct conversion topology was selected for the SDRX architecture. The key issues of direct conversion receivers, like offset, 1/f noise, and self-mixing, are presented and solutions are proposed to make this architecture ready for monolithic integration.

2. Once the architecture is set, the multi-standard environment is evaluated, as a first step in deriving the electrical specifications for the receiver. *A first order, system level, standard independent analysis methodology* was developed in Chap. 3 to enable the designer to handle efficiently the large amount of information provided in the envisaged wireless standards. Based on this new methodology, the designer is able to attack in parallel the wireless standards when

deriving the SDRX specifications. Thus, the key SDRX electrical specifications (i.e., NF and IIP3) are derived in a standard independent way.

3. Moreover, a new and efficient tool is introduced: *the generic blockers diagram*. This represents an exhaustive blocker map, which enables the designer to determine the worst case scenarios for blocker tests. Being thus prepared, the designer is now ready to properly address the optimal filtering partitioning between the analog LPF and the digital filter following the ADC in conformity with Chap. 4 explanations. *Through the introduction of a new Figure of Merit (FOM), the trade-off between the analog LPF area and ADC power consumption is evaluated in one single plot.* This new FOM represents another efficient design tool that empowers the designer to choose the optimal SDRX filtering configuration, the key feature for the SDRX implementation.

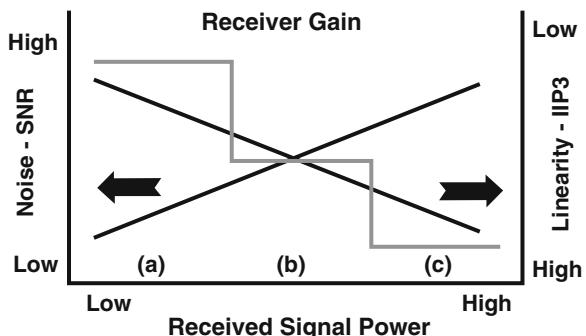

4. Further on, in Chap. 5, the analysis focuses on another key trade-off in wireless receiver design: the trade-off between its noise and linearity performance. Based on the presented analysis, a novel gain partitioning strategy is introduced. The strategy is tailored towards multi-standard radio receivers and optimally mitigates the extreme reception conditions specific to the wireless environment.

By allowing the receiver gain, noise and linearity performance to scale with the useful input signal level variation, the SDRX is empowered to optimize its output SNR, given the particularities of each reception burst. This concept represents the “smart” receiver gain partitioning.

5. Chapter 6 starts by presenting the SDRX electrical specifications that should be considered as a first design iteration towards building a general-purpose SDRX suited for the 5G deployment. Moreover, the chapter details the noise and linearity partitioning between the SDRX high-frequency part and its low-frequency part.

6. Chapter 7 overviews the modern receiver’s building blocks and presents the most suited bias block that will ensure minimal variation of the key design parameters. Also, the low-frequency part noise breakdown is presented.

7. Chapter 8 concludes the book and gives a sneak-peak into the future developments.

## References

1. International Telecommunication Union—Telecommunication Sector Statistics, Available on-line at: <http://www.itu.int/ITU-D/ICTEYE/Indicators/Indicators.aspx>

2. C. Maxwell, *Treatise on Electricity and Magnetism* (Oxford, 1904), Available on-line at: <http://rack1.ul.cs.cmu.edu/is/maxwell1/>

3. C. E. Shannon, W. Weaver, *The Mathematical Theory of Communication* (Urbana University of Illinois Press, Urbana, 1949) (reprinted 1998)

4. ETS 300 577, *GSM: Digital Cellular Telecommunications System (Phase 2); Radio Transmission and Reception* (European Telecommunication Standard Institute (ETSI), 1997)

5. Third Generation Partnership Project (2015). Available on-line at: <http://www.3gpp.org>

6. LTE (Long Term Evolution), 3GPP TS 36.101, version 10.3.0, release 10 (2011)

7. IEEE 802.11-1997: Wireless LAN Medium Access Control (MAC) and Physical Layer (PHY) Specifications (IEEE Computer Society, 1997).

8. IEEE 802.11n-2009 Amendment 5: Enhancements for Higher Throughput (IEEE Computer Society, 2009)

9. IEEE 802.11a-1999 High-speed Physical Layer in the 5 GHz Band (IEEE Computer Society, 1999)

10. IEEE 802.11b-1999 High-speed Physical Layer Extension in the 2.4 GHz Band (IEEE Computer Society, 1999)

11. IEEE Std 802.11g-2003 (IEEE Computer Society, 2003)

12. IEEE Std 802.11ac-2013 (IEEE Computer Society, 2013). Available on-line at: <http://standards.ieee.org/getieee802/download/802.11ac-2013.pdf>

13. Bluetooth® Core Specification Version 2.0 + HS, 2004. Available on-line: [https://www.bluetooth.org/DocMan/handlers/DownloadDoc.ashx?doc\\_id=40560](https://www.bluetooth.org/DocMan/handlers/DownloadDoc.ashx?doc_id=40560)

14. Bluetooth® Core Specification Version 3.0 + HS, 2009. Available on-line: [https://www.bluetooth.org/DocMan/handlers/DownloadDoc.ashx?doc\\_id=174214](https://www.bluetooth.org/DocMan/handlers/DownloadDoc.ashx?doc_id=174214)

15. Bluetooth® Core Specification Version 4.0, 2010. Available on-line: [https://www.bluetooth.org/DocMan/handlers/DownloadDoc.ashx?doc\\_id=174214](https://www.bluetooth.org/DocMan/handlers/DownloadDoc.ashx?doc_id=174214)

16. IEEE 802.16-2009 Local and Metropolitan Area Network Standards (IEEE Computer Society, 2009)

# Chapter 2

## Defining the Optimal Architecture

### 2.1 Introduction

The basic modern communication system comprises a large array of mobile equipment into a wireless network. The communication between all these equipment is regulated by various communication standards, depending on the type of wireless network in which they are connected.

In order to maximize the potential of wireless communications, the latest wireless standards converge towards a “one size fits all” solution. As an example, the W-LAN standard, IEEE 802.11ac, uses almost all basic digital modulation schemes (i.e., BPSK, QPSK, 16-QAM, 64-QAM, 256-QAM, and 1024-QAM) on OFDMA carrier support with variable modulation depths, while it still maintains compatibility with the earlier IEEE 802.11 lower data rate standards.

Hence, the latest developments in standardization point to a software re-configurable hardware solution for the radio front-end as the best way to trade-off backwards compatibility with future trends. This observation is critical as we move on towards the 5G deployment.

The main target of this chapter is to determine the optimum architecture choice suited for the SDRX. The analysis starts with an overview of the standard receiver architectures in Sect. 2.2 and, subsequently in Sect. 2.3, and determines the quadrature direct conversion topology suits best the envisaged purpose. For such receiver architectures, regardless of the communication wireless standards, the received signal is downconverted directly to baseband and the digital signal processor (DSP) software demodulation scheme is changed accordingly such as it can handle it. Hence, the possibility of implementing a “universal receiver” is revealed [1].

The chapter continues, in Sect. 2.4, by constructing the solutions that make direct conversion receivers ready for monolithic integration. *The presented solutions are realized without introducing particular analog tricks to satisfy the needs of only one of the standards, as the SDRX must represent a “universal receiver,”*

and not be turned into a “multi-standard Application Specific Integrated Circuit (ASIC).”

Further on, Sect. 2.4 presents the natural architectural evolutions due to the increased power consumption efficiency of modern ADCs.

## 2.2 Overview of Receiver Architectures: Following the Image Rejection

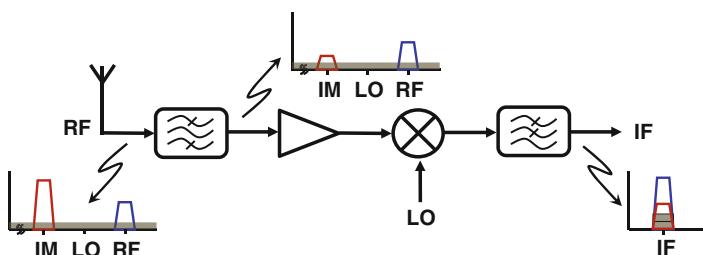

### 2.2.1 Superheterodyne Receivers

#### Single Conversion

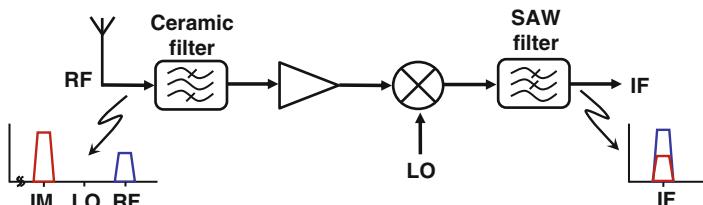

The superheterodyne architecture was developed in 1918 by Edwin Armstrong as a viable alternative to the regenerative receiver with respect to the technical issues of vacuum tubes implementation [1]. The basic block schematic of this concept is depicted in Fig. 2.1. The original superheterodyne uses only one downconverter mixer, *single conversion* superheterodyne, and mixes the Radio Frequency, RF, input signal with the Local Oscillator, LO, signal.

The resulting signal frequency is shifted down to an Intermediate Frequency, IF, equal to the difference between the RF carrier and LO signal frequencies.

Intrinsically the mixing process will render at the mixer output also the sum frequency component. For most applications this component represents an unwanted signal and is filtered by the band-pass filter following the mixer and/or in the mixer output stage.

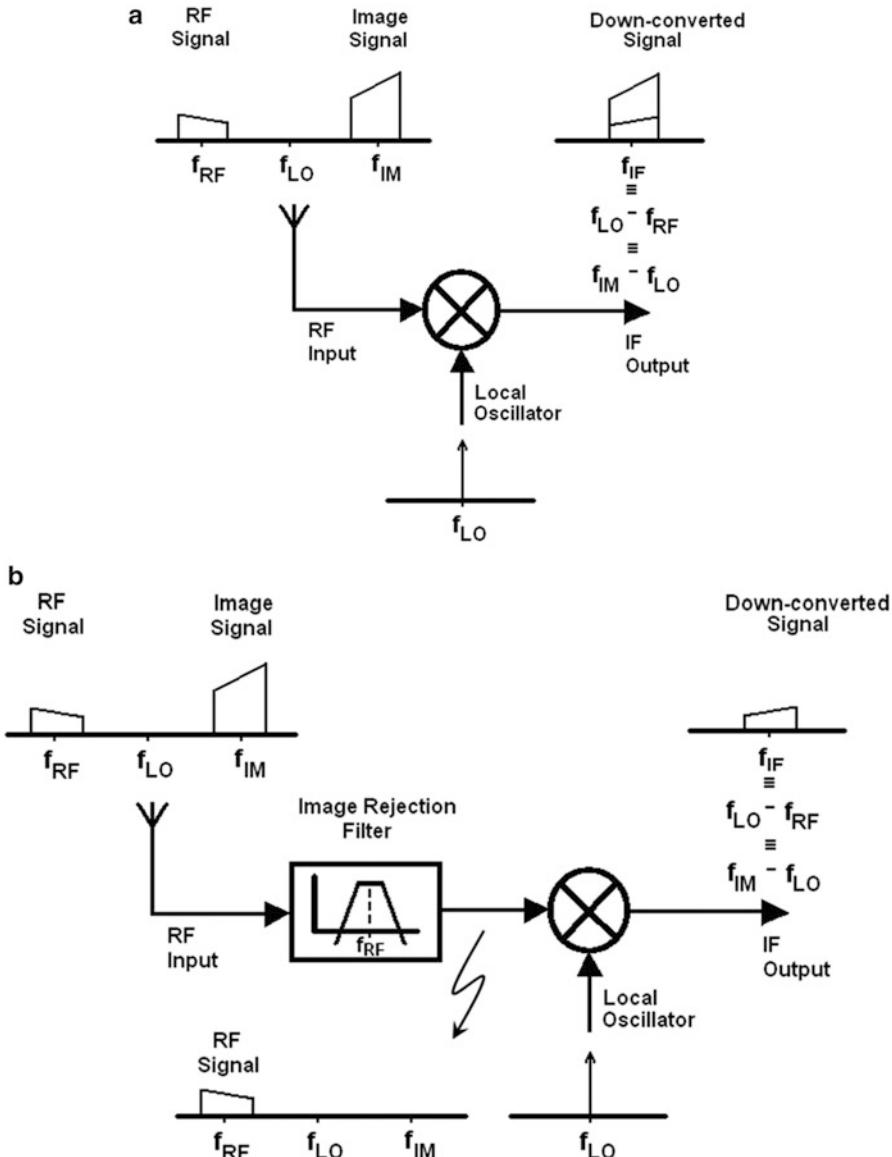

The major issue of superheterodyne topology is the image frequency rejection. The problem resides in the fact two symmetrical signals with frequencies spaced apart by twice the IF frequency are downconverted by LO mixing to the same IF frequency, as shown in Fig. 2.2.

If the communication is dual sideband, meaning both RF signals convey the same useful information, there is no problem, since spectrum overlapping in the IF band is beneficial. However, this is not the case for the vast majority of applications, which are employing single side band communication. Thus, the unwanted image signal rejection becomes critical.

Fig. 2.1 Single conversion superheterodyne receiver block schematic

**Fig. 2.2** Downconversion: (a) without Image Rejection and (b) with Image Rejection

The superheterodyne architecture solves the issue by filtering the image signal before it enters the mixer, or more precisely, immediately after the antenna. The image rejection filter specifications depend on the IF value and they are more relaxed as the image frequency is larger, respectively, as the distance between the RF carrier and its image is larger.

Signal conditioning constraints, set by the channel selection filter—the second band-pass filter of Fig. 2.1, prevent the choice of a very large IF, thus toughening image filtering requirements. In practice, ceramic filters satisfy the constraints, although they possess two major drawbacks: they are quite expensive and by far not compatible with monolithic integration.

Channel selection is also demanding, as for many applications channel bandwidth is fairly small compared with IF. In such context, bandpass Surface Acoustic Wave (SAW) filters are used for analog channel selection. However, these types of filters are unattractive to SoC ICs for the same two reasons as the ceramic antenna filters: incompatibility with monolithic integration and high cost.

In conclusion, single conversion superheterodyne receiver design is driven by the trade-off between antenna and channel filtering, which imposes the optimum IF frequency.

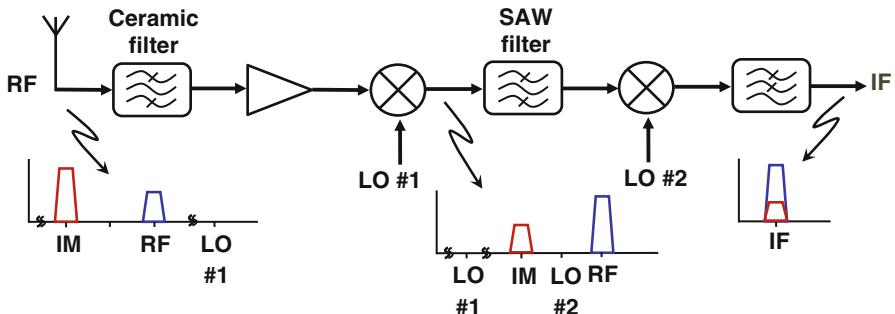

## Dual or Double Conversion

For *Single Conversion* superheterodyne, the choice of a low IF leads to tough specifications for the antenna filter but does not affect the ones for the channel filter, while a high IF constraints the channel filtering and relaxes the antenna filter specifications. Either way, for most wireless applications, the antenna filtering requirements lead to choosing a cumbersome ceramic filter as the image filter and the IF filtering requirements impose a SAW filter for analog channel selection.

The *Dual Conversion* superheterodyne, which principle schematic is depicted in Fig. 2.3, uses two IFs to ease the image filtering and channel selection, respectively, to relax the antenna and channel filters specifications. The idea is to first up-convert the incoming RF signal to a high IF, relaxing image filtering requirements, while the downconversion mixing is made to a low IF, simplifying channel selection. Still, for most applications, the antenna and image filters will require implementation by ceramic filters.

**Fig. 2.3** Dual conversion superheterodyne receiver block schematic

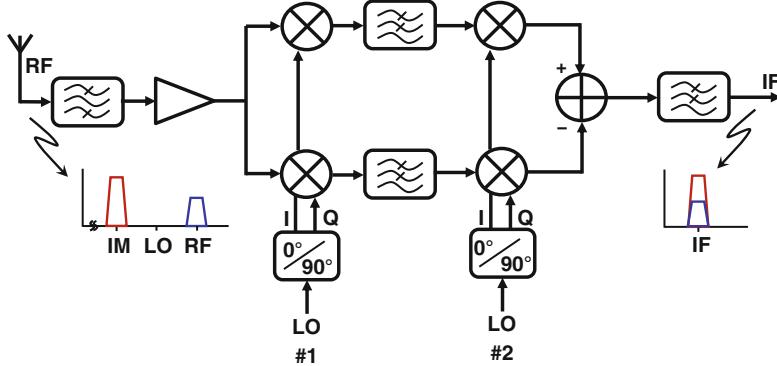

Fig. 2.4 Image rejection receiver

*Hence, superheterodyne architectures cannot solve the image rejection problem monolithically.*

### 2.2.2 Image Rejection Receivers

So far, the design of superheterodyne receivers has been optimized to alleviate image rejection rather than optimizing RF performance.

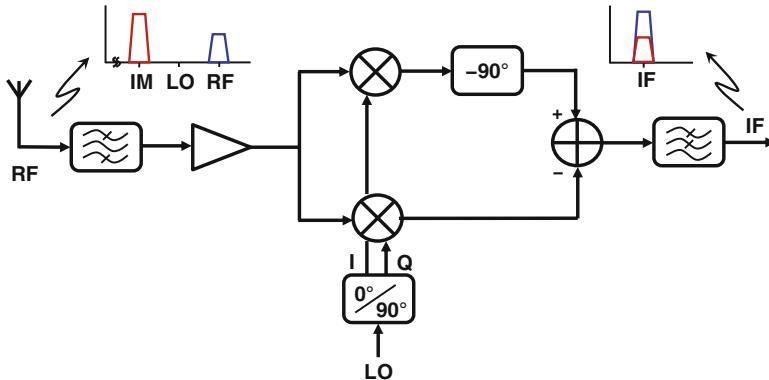

An image rejection receiver uses a “*complex*” mixer to cancel out the unwanted image signal, removing the lock on architecture and allowing the system design to optimize RF performance. The principle schematic of such a receiver is depicted in Fig. 2.4.

The “*complex*” mixer is made out of two mixers which share the same RF input, while the LO port is controlled by two quadrature signals. By adding a  $90^\circ$  delay line in one signal path, the downconverted image signals will be in-phase, while the useful signals will be  $180^\circ$  delayed. Hence, by considering the difference between the two paths the image signal is cancelled, while the useful signal is added.

The major advantage of this approach is the antenna filtering becomes less critical. Thus, the use of expensive and bulky, external (off-chip), ceramic filters is no longer required. On the other hand, the image rejection now depends on the quadrature accuracy of both gain and phase of the LO and IF paths. If the two LO signals exhibit exactly  $90^\circ$  phase delay and have the same amplitude, while the gain of the two paths are perfectly matched, the unwanted image signal is completely rejected.

Hence, image rejection receivers cancel out the image signals by subtracting two potentially very large signals, and resulting in a difference that is theoretically equal to zero. However, any gain or phase error between the two signal paths will result in incomplete cancellation of the image signal. Thus, the image rejection is given by [2]:

Fig. 2.5 Weaver receiver

$$\text{Image Rejection} = -20\log\left\{\frac{1}{2}\left[\frac{Gain_{I-Q\ err}}{Gain} + \tan(\text{Phase}_{I-Q\ err})\right]\right\} \text{ [dBc]} \quad (2.1)$$

where *Gain* represents the receiver's gain,  $Gain_{I-Q\ err}$  is the I-Q gain mismatch, and  $\text{Phase}_{I-Q\ err}$  is the I-Q phase mismatch.

Since accurate wide-band quadrature phase shifters are difficult to design, Weaver receivers of Fig. 2.5 are preferred. To cancel the need for  $90^\circ$  phase shifter on signal path, an extra pair of mixers and quadrature LO signals are required.

Still, the LO signals quadrature accuracy, of both gain and phase, and the gain matching of the quadrature downconverted channels set the image rejection performance as described by (2.1).

For both image rejection approaches, if a low IF is chosen then the IF filtering requirements are relaxed, as well as subsequent A/D conversion or baseband processing. The image rejection can typically be lowered to about  $-35$  dB with quadrature generators like Poly Phase Filters or divide-by-2 Johnson Counters.

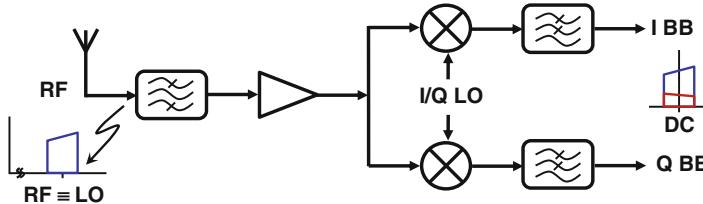

### 2.2.3 Direct Conversion Receivers

All receiver architectures presented so far have to fight image rejection. In general, a signal and its image are spaced apart by twice the Intermediate Frequency (IF). To reject the image, superheterodyne receivers require the use of expensive off-chip SAW filters, while dual-conversion architectures trade-off the SAW filter for a standard, but still bulky and expensive, ceramic filter, at the expense of an extra up-converter mixer.

In Fig. 2.6 the typical block schematic of a quadrature direct conversion receiver is depicted. Quadrature LO drive enables the receiver to demodulate the RF signal regardless of the phase relation between the LO and incoming RF signals [1].

Fig. 2.6 Quadrature direct conversion receiver

In direct conversion receivers, also known as homodyne or zero-IF, the IF frequency is zero. Hence, the useful signal is its own image. *Therefore, in a zero-IF system the image signal has an amplitude comparable to the useful signal, and thus, image rejection requirements are drastically relaxed.* Furthermore, all baseband processing, like analog baseband signal conditioning, analog-to-digital conversion and the digital demodulation, take place at the lowest possible frequency.

These features make the direct conversion receiver an ideal candidate for monolithic integration and open the possibility of creating a “universal” receiver, compatible with all wireless standards. However, although direct conversion receivers monolithic integration seems straightforward, there are several drawbacks to this approach.

First of all, the zero-IF architecture is extremely sensitive to DC offset and  $1/f$  noise. As the signal is directly converted to baseband, receiver noise figure is affected by  $1/f$  noise and its output risks of being overloaded even for small values of the DC offset, in the order of a few tens of  $\mu\text{V}$ . Such low DC offset, or  $1/f$  noise, values are not easily achievable in practice. Regular AC coupling will not be solving the issue, as receiver settling will be severely affected by a low cutoff frequency, in the order of a few hundred Hz.

Some of these problems have been already addressed at protocol level, as the latest wireless standards tend to use modulation schemes that minimize the baseband signal low frequency spectral energy. Also, for Time Division Multiple Access (TDMA) systems, a dedicated time slot for calibration is foreseen: the guard band. Hence, static offset cancelation is possible before each actual receive burst.

The second major issue of direct conversion architecture is that even-order distortions generate a signal-dependent DC offset. Handling dynamic offset, to the extent required by almost all commercial wireless standards, implies the usage of a differential architecture for the whole receiver chain, starting with its Low Noise Amplifier (LNA).

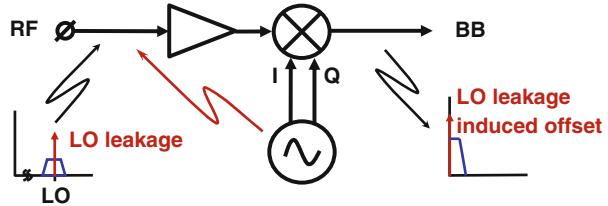

Another issue of such architecture is self-mixing. The LO signal, which in most cases is orders of magnitude larger than the RF signal, leaks to the RF port of the mixer and is mixed down to baseband. If the LO leaking signal is phase shifted with respect to the real LO, this almost always being the case in practice, the DC offset caused by self-mixing dominates the mixer output. Hence, very good isolation between RF and LO mixer ports is required for good receiver performance.

Fig. 2.7 Low-IF receivers

Also, because the large gain of the direct conversion receiver is focused at one frequency, the isolation between input and output of the receiver is critical, as any parasitic feedback loop may lead to system instability.

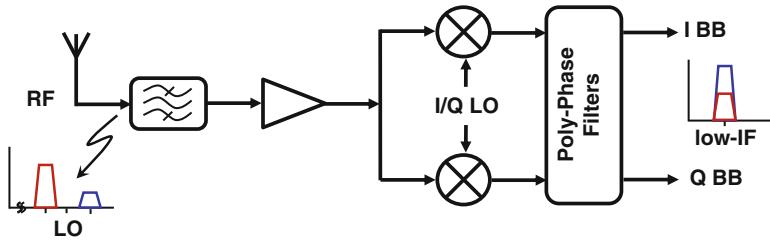

#### 2.2.4 Low-IF Receivers

Finally, although direct conversion architecture has very relaxed image rejection specifications, it has to fight with DC offset, 1/f noise, and self-mixing.

Hence, the low-IF architectures (see Fig. 2.7) become attractive. Essentially, the RF signal will now be downconverted to a low-IF frequency (i.e., up to a few hundred kHz) and thus, the issues of direct conversion receivers are alleviated.

However, the image rejection requirements are again heavily constricted. This stresses the implementation of the active poly-phase filter that follows the complex mixer and is used for image rejection and channel selection.

### 2.3 Final Decision: w/ IF vs. w/o IF (Zero-IF)

The main features of a SDRX must be a versatile architecture and the ability to be reconfigured on-the-fly as the communication burst requires.

From the perspective of SoCs, the optimization of the chip power dissipation and die area is mandatory. As the SDRX will be embedded in an SoC, this trade-off must be the main guideline in sizing the SDRX design, as well as in choosing its architecture, as a first and, very important, starting point. *The SDR architectures of choice are superheterodyne (w/ IF), either single or dual conversion, low IF (w/ IF) or direct conversion (w/o IF).*

From area perspective the cumbersome image rejection filters of superheterodyne topology are not so attractive for monolithic integration. On the other hand, for direct conversion the image rejection requirements are much smaller than for any other receiver architecture.

Furthermore, the IF selection for superheterodyne architectures is fairly cumbersome and cannot be extrapolated in a systematic way to all standards, as it would be required for a true SDRX [3]. Basically, the IF should be chosen to avoid the in-band downconversion of strong interferers. In most applications the nearest strong interferers are located three channels apart from the RF carrier. As the channel bandwidth differs even within the same wireless standard, it is not possible to select intermediate frequencies which will lead to reuse of same image filters for a multi-bandwidth environment compatible receiver.

From the power consumption perspective, the direct conversion topology has even more advantages.

First of all, the baseband signal processing takes place at the lowest possible frequency.

Secondly, this topology is not tributary to the 3 dB noise penalty of superheterodyne architectures [2]. Basically, direct conversion quadrature receivers are using the information from both sidebands, as the image is actually the useful signal. While, for most commercial applications, the superheterodyne receivers are using only one sideband, as the image signal is not a useful signal (see Fig. 2.8).

By using an additional bandpass ceramic filter after the LNA, the single sideband superheterodyne receivers noise penalty is reduced. However, this makes the overall system even more unattractive for monolithic integration.

So far the zero-IF architecture had presented overwhelming advantages to the heterodyne approach, including also here the low-IF architecture, in terms of image rejection, and thus, for monolithic integration purposes.

It is true that the direct conversion has some issues with DC offset and 1/f noise that the low-IF architecture can overcome. However, these issues can be overcome as discussed in detail in Sect. 2.4, whereas the low-IF systems still have to fight very tough image rejection specifications.

Hence, it becomes clear that direct conversion receivers are the only ones capable of satisfying the requirements of a true SDRX.

Table 2.1 summarizes the advantages and disadvantages of the three architectures with respect to monolithic integration in a SDRX SoC.

Fig. 2.8 Superheterodyne 3-dB noise penalty

**Table 2.1** Heterodyne and low-IF vs. direct conversion receivers comparison regarding SoC integration—PROs and CONs

| Superheterodyne                                    |                                                                         | Low IF                                                               |                                                                         | Direct conversion                                                      |                                                  |  |  |

|----------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------|--------------------------------------------------|--|--|

| PROs                                               | CONs                                                                    | PROs                                                                 | CONs                                                                    | PROs                                                                   | CONs                                             |  |  |

| <span style="color: #800000;">⊕</span> Well known  | <span style="color: #800000;">⊕</span> High image rejection requirement | <span style="color: #800000;">⊕</span> No DC Offset                  | <span style="color: #800000;">⊕</span> High image rejection requirement | <span style="color: #800000;">⊕</span> Low image rejection requirement | <span style="color: #800000;">⊕</span> DC Offset |  |  |

|                                                    | SAW Filter                                                              | <span style="color: #800000;">⊕</span> Reduced 1/f noise             | <span style="color: #800000;">⊕</span> Reduced self-mixing              | SAW Filter                                                             | No SAW Filter                                    |  |  |

|                                                    | <span style="color: #800000;">⊕</span> IF selection                     | <span style="color: #800000;">⊕</span> Image is wanted signal mirror |                                                                         | <span style="color: #800000;">⊕</span> 1/f noise                       |                                                  |  |  |

|                                                    | Difficult to mitigate the multi-standard environment                    | Mirror signal is not a strong interferer                             |                                                                         |                                                                        |                                                  |  |  |

|                                                    | <span style="color: #800000;">⊕</span> Power consumption                | <span style="color: #800000;">⊕</span> Power consumption             |                                                                         |                                                                        |                                                  |  |  |

|                                                    | Baseband signal conditioning is done at IF                              | Baseband signal conditioning is done at lowest frequency             |                                                                         |                                                                        |                                                  |  |  |

|                                                    | <span style="color: #800000;">⊕</span> 3 dB noise penalty               | <span style="color: #800000;">⊕</span> No 3 dB noise penalty         |                                                                         |                                                                        |                                                  |  |  |

| Image frequency band degrades receiver SNR by 3 dB |                                                                         |                                                                      |                                                                         |                                                                        |                                                  |  |  |

|                                                    |                                                                         |                                                                      |                                                                         |                                                                        |                                                  |  |  |

**Fig. 2.9** SDRX block diagram

### 2.3.1 Receiver Block Schematic

The block schematic of a true multi-standard re-configurable receiver, including the final ADC, is depicted in Fig. 2.9.

The main tasks of a radio receiver consist in isolating the wanted, useful signal from other electromagnetic signals arriving at the antenna, amplifying and converting it from a (high) radio frequency (RF) to baseband (BB).

The incoming RF signal is picked up by the receiver's antenna and is amplified by one of its LNAs. Multiple LNAs can be integrated, depending on the envisaged use.

The *amplified* RF signal is then converted to current in the mixer input gm-stage and downconverted directly to baseband by mixing with a local oscillator signal of equal frequency. Hence, at the mixing stage output the signal has a spectrum spanning from DC to a maximum frequency that is dependent on the wireless communication standard, as detailed in Sect. 3.1.

After mixing, the signal is conditioned by a low-pass filter (LPF) and a variable gain amplifier (VGA), before its conversion to digital spectrum by an ADC.

*Through digital control the SDRR blocks main characteristics (e.g., bandwidth, noise, and linearity) can be changed dynamically depending on the particular standard requirements or even on the particular communication burst necessities.*

Basically, the receiver chain of Fig. 2.9 is split into a high-frequency (HF) part, comprised by the LNA and the gm stage of the downconverter and a remaining baseband low-frequency (LF) part, following the mixer's switching stage.

The receiver design is a result of noise-linearity trade-offs under power consumption constraints. The key trade-off shaping its design is the one between the LPF order and ADC power consumption, as detailed in Chap. 4. The receiver's high-frequency part is shaped mainly by noise requirements, while its baseband blocks must enforce a linear channel selection to prevent the RF useful signal distortion, as is detailed in Chap. 5.

## 2.4 Making Direct Conversion Receivers Ready for Monolithic Integration

### 2.4.1 Key Issues

As detailed in Sect. 2.2 and in-depth analyzed in [4], due to intrinsic operation of zero-IF systems, they exhibit a large sensitivity to DC offset, either static or dynamic, and 1/f noise. Also, self-mixing issues can dramatically reduce performance of receivers implemented with direct conversion architectures.

First of all, direct conversion architecture is extremely sensitive to static DC offsets and 1/f noise. As the signal is directly converted to baseband, receiver noise figure is affected by 1/f noise. Generally the mixer output is DC coupled to the LPF, since a major part of the received signal baseband spectral energy is located at low frequency (i.e., the GSM standard). Regular AC coupling will not solve the issue, as receiver settling will be severely affected by a low cutoff frequency in the order of a few hundred Hz. Also, given the large VGA gain, usually larger than 60 dB, the receiver output risks of being overloaded even for small values of the DC offset, in the order of a few hundred  $\mu$ V.

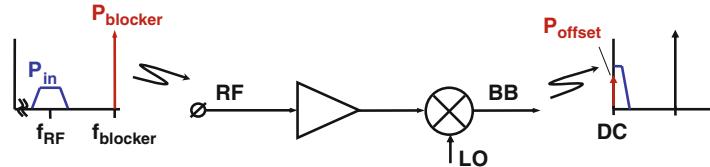

The second major issue of the zero-IF receiver architecture is even-order distortions generate a signal-dependent DC offset. As the received input power can change dynamically, since other transmitters may start to communicate, a dynamic offset component is generated due to the receiver second-order nonlinearity.

Also, the self-mixing process, determined by the LO mixing with the LO signal leaking from the Voltage Controlled Oscillator (VCO) to the receiver input, can generate a large DC offset overloading the receiver output.

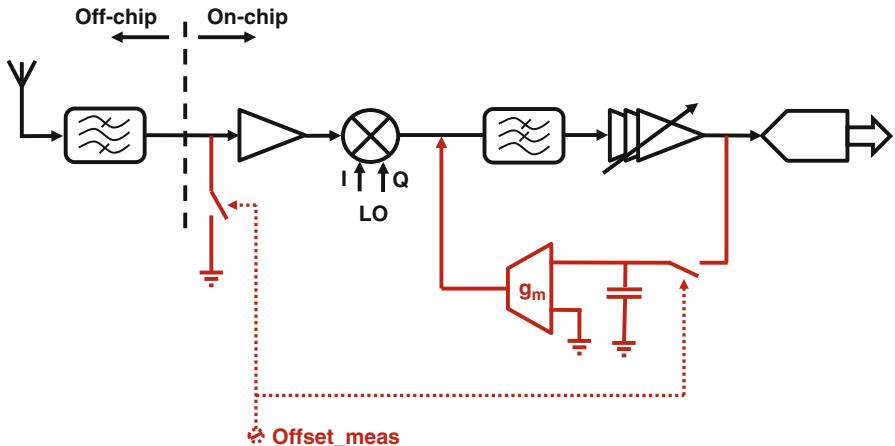

The section main goal is to determine the architectural changes in Fig. 2.9 receiver, required to compensate the abovementioned issues. Section 2.4.2 covers the architecture sensitivity to static DC offsets and  $1/f$  noise and explains the dynamic offset generation in the presence of second-order distortions. In Sect. 2.4.3, the best method to avoid self-mixing process is presented. Finally, Sect. 2.4.4 presents the updated SDRX block schematic, while Sect. 2.4.5 presents the natural evolution of Fig. 2.9 receiver.

## 2.4.2 DC Offset Compensation

### Static Offset Removal

Low DC offset and  $1/f$  noise values are required for proper signal demodulation during the receiving phase. In practice these low values are not easy to get without calibration.

Wireless communications are burst communications and a dedicated time slot for calibration is foreseen: the guard band. Thus, static offset cancelation is possible before each actual receive burst.

While the LNA is AC coupled to the mixer, the mixer output is DC coupled to the baseband part of Fig. 2.9 receiver. One of the possibilities to calibrate the receiver static DC offset is the use of the correlated double sampling technique [5]. This offset compensation technique is preferred to chopper stabilization [6] as there is no risk of spurs overwhelming the receiver output spectrum.

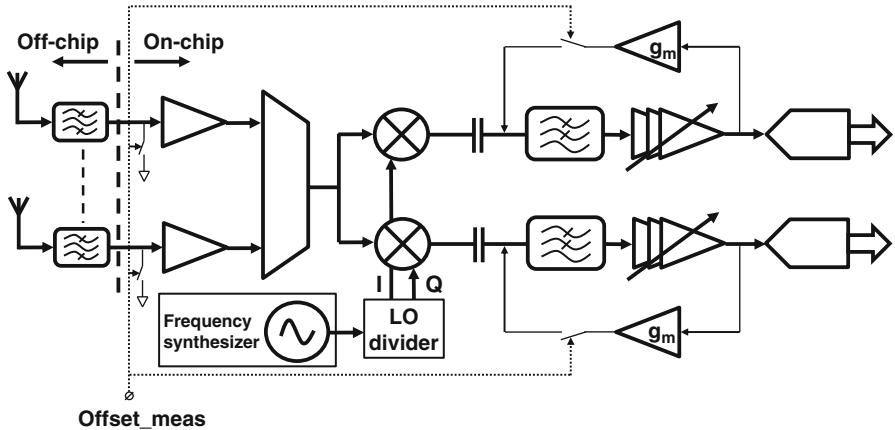

This analog technique, described by Fig. 2.10, implies in a first phase (i.e., *Offset\_meas* control signal @ “High”—switches closed) sampling the baseband chain DC offset on a capacitor, via the additional transimpedance amplifier, while the antenna input is shorted to ground [7].

During normal operation, the second phase (i.e., *Offset\_meas* @ “Low”—switches open), the RF input is connected again to the antenna and the signal flows through the receiver, while the DC offset is inherently cancelled out. The frequency of two phases alternation is set by the baseband signal bandwidth: the smaller the baseband signal bandwidth, the higher is the duration of the DC offset sampling (see Table 3.1).

The advantage of this technique is the  $1/f$  noise is also reduced, next to the static offset cancelation; the drawback is the white noise level doubling because of the aliasing. Hence, in order to reduce the increase of the wideband noise, for standards

**Fig. 2.10** Receiver block schematic with analog offset compensation (only one baseband channel is shown)

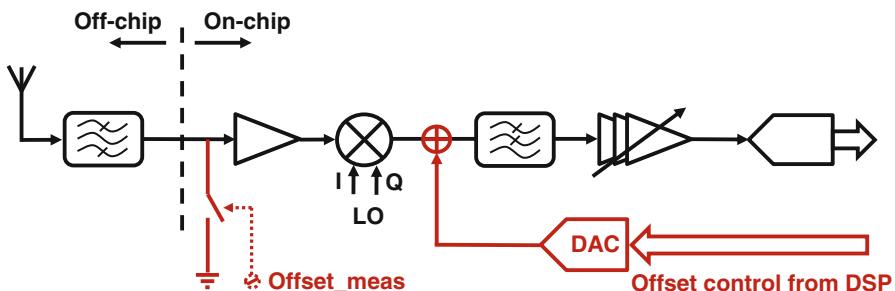

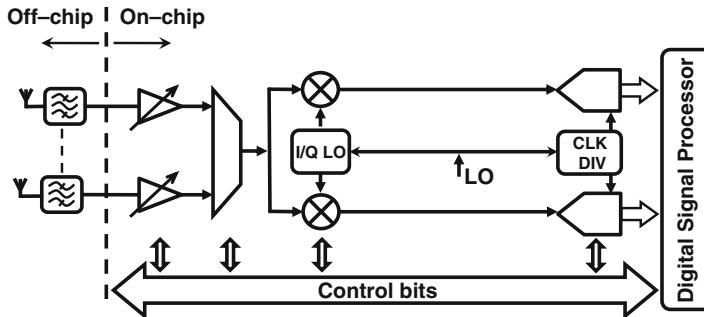

**Fig. 2.11** Receiver block schematic with digital offset compensation (only one baseband channel is shown)

with a larger baseband bandwidth, regular AC coupling can be used for the LPF, while the DC offset compensation can be applied only to the VGA.

Another possibility for offset compensation is to measure the offset in the digital domain, and then correct it in the analog domain through a digital-to-analog converter (DAC). An example is shown in Fig. 2.11.

### Handling Dynamic Offset

During the receiving period, the RF input power may change significantly, as the other transmitters in the receiver's neighborhood begin to transmit. The receiver's even-order distortions will change the received signal DC offset component. This *dynamic offset* effect disturbs the received signals demodulation, especially if the

**Fig. 2.12** DC offset generation due to self-mixing

envisioned modulation concentrates a large part of the symbol spectral power at low frequency.

Although the latest wireless standards use modulation schemes that do not require the preservation of the signal DC energy, this is not the case for older standards (i.e., GSM). Hence, handling dynamic offset implies the receiver must embed a fully differential signal conditioning chain that offers a high second-order input intercept point ( $IIP2_{RX}$ ). The worst case scenario is met for the GSM standard which requires an  $IIP2_{RX}$  of +46 dBm.

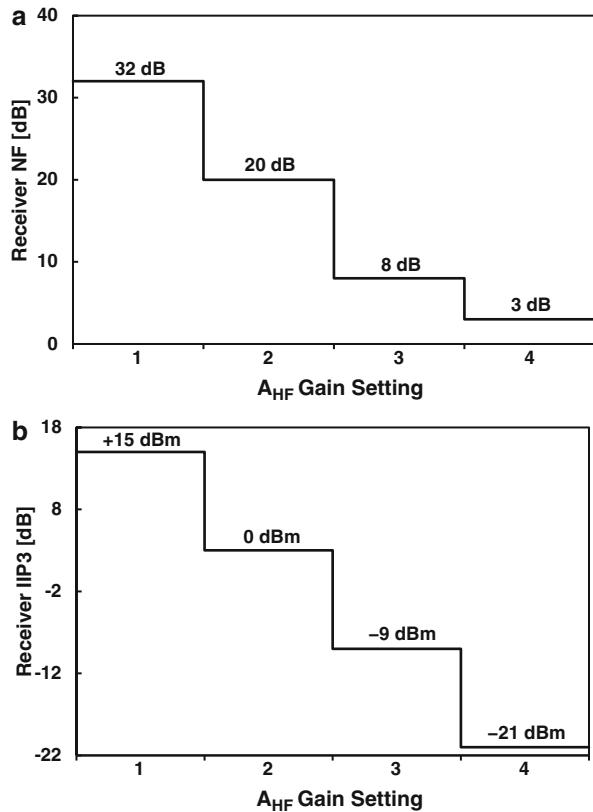

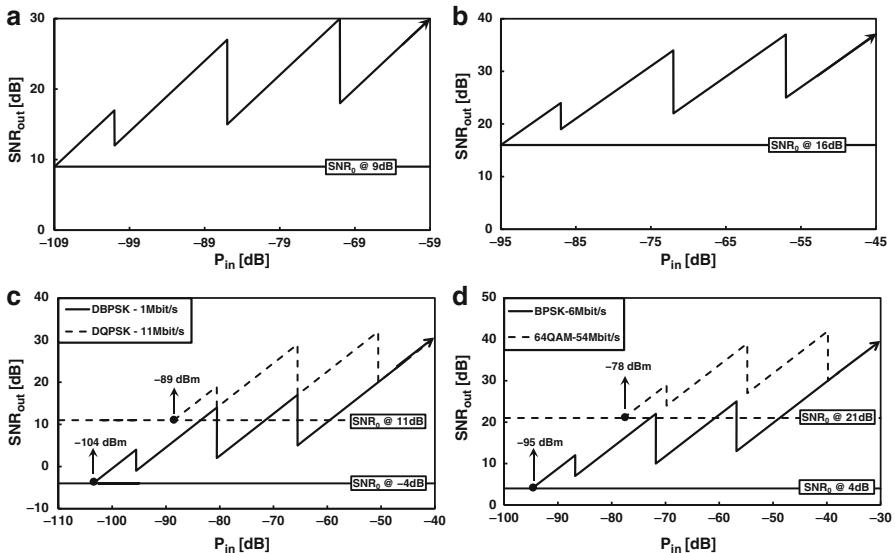

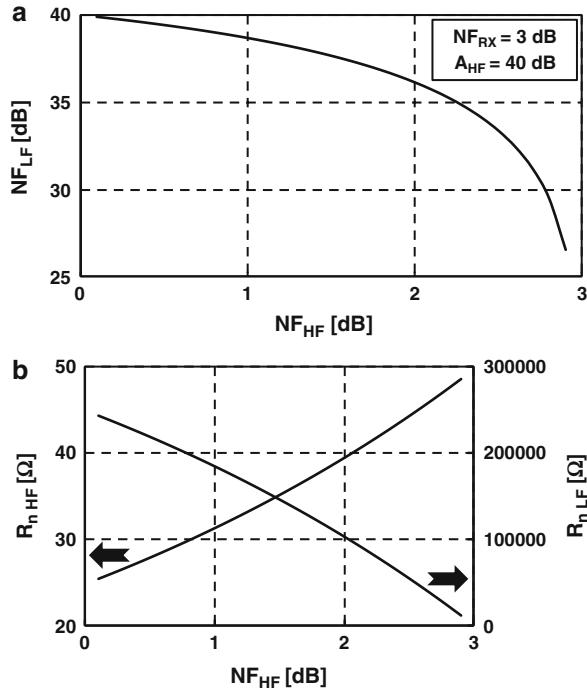

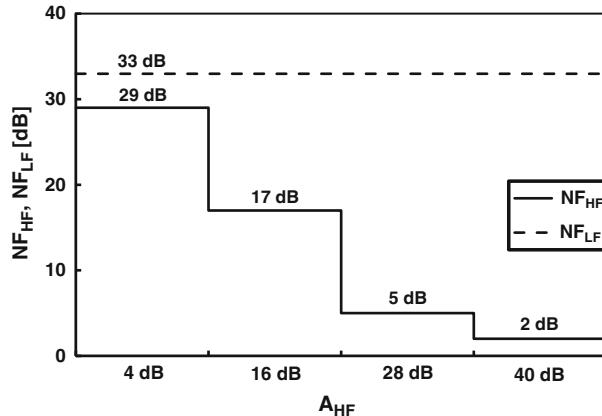

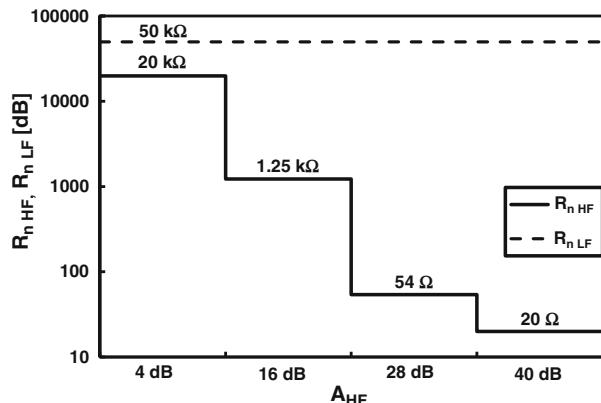

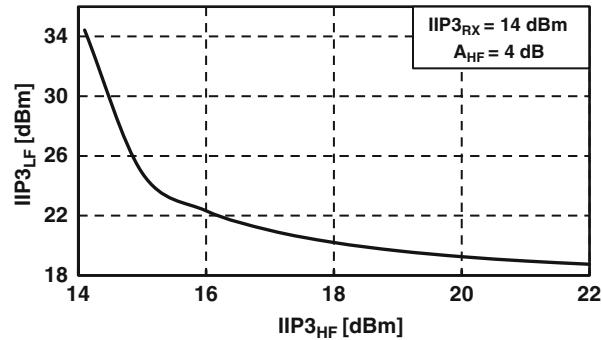

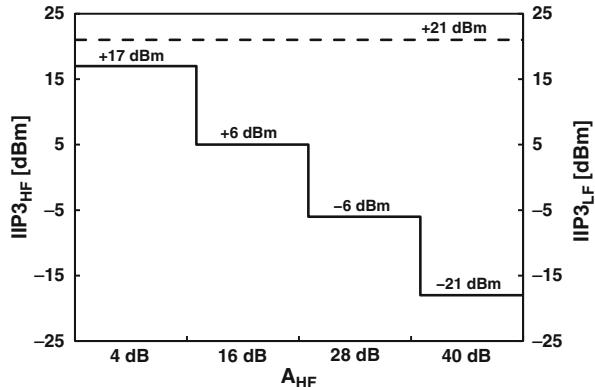

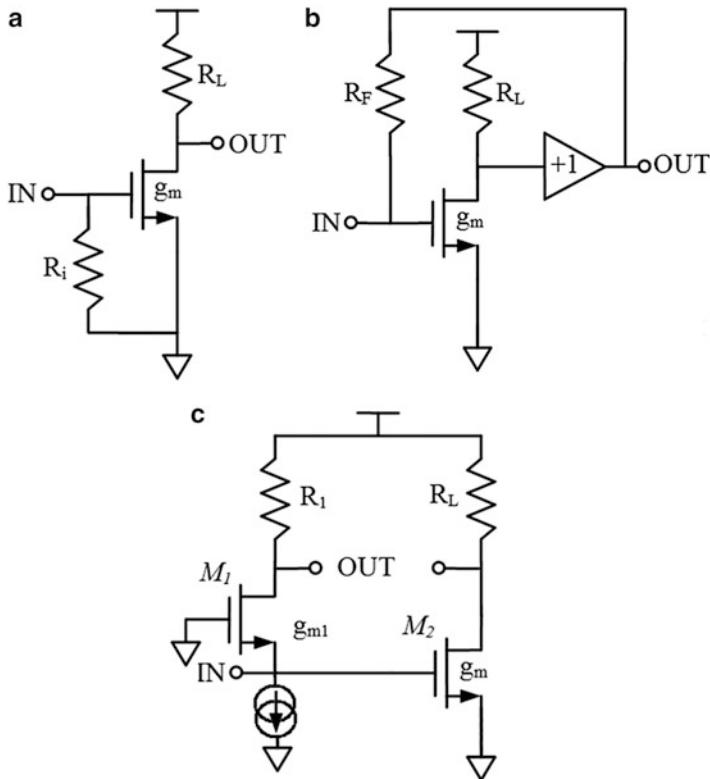

### 2.4.3 Reducing Self-Mixing