Dumitru Potop-Butucaru

Stephen A. Edwards

Gérard Berry

# Compiling ESTEREL

Springer

# Compiling Esterel

# Compiling Esterel

Dumitru Potop-Butucaru

Stephen A. Edwards

Gérard Berry

A C.I.P. Catalogue record for this book is available from the Library of Congress.

ISBN 978-0-387-70626-9 (HB)

ISBN 978-0-387-70628-3 (e-book)

---

Published by Springer,

P.O. Box 17, 3300 AA Dordrecht, The Netherlands.

*www.springer.com*

*Printed on acid-free paper*

All Rights Reserved

© 2007 Springer

No part of this work may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, microfilming, recording or otherwise, without written permission from the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work.

*To Maria, Eleonora, and Victoria*

# Preface

This book is about compiling the Esterel language. One of us (Berry) created Esterel in the early 1980s for programming embedded reactive systems. Over time, we and others have developed both academic and commercial compilers for it that generate software and hardware. The newest version of Esterel, called Esterel V7, is being standardized by the IEEE as of 2006.

This book had its genesis in 2002 as Potop-Butucaru's thesis. Written under Berry and Robert de Simone, it made two main contributions: the first semantics for Esterel that included data manipulation (long a part of the language, this was its first formalization), and a very sophisticated code generation technique that remains one of the best developed so far.

At Potop-Butucaru's thesis defense, held during the SYNCHRON workshop in La Londe les Maures, France in November 2002\*, Edwards, a jury member, remarked that the thesis would make a good book. Potop-Butucaru interpreted this as meaning only that the thesis would make a good starting point for the book. Thus, one of us (Edwards) expected to have a book within a few months, but instead it took years.

Little more than the general outline of the original thesis remains at this point; much has been added and clarified. We added chapters on the behavioral semantics of Esterel (Chapter 4), recently-developed compilation techniques used in the Columbia Esterel compiler (Chapter 10), and appendices on the extra constructs in the language that are not covered formally but must be handled by all compilers (Appendix A), the first formal language reference manual for the dialect of Esterel described in this book (Appendix B), the C language interface (Appendix C), and a description of the new Esterel V7 dialect of Esterel (Appendix D).

## *How to read this book*

We divided this book into three parts. In the first part (Chapters 1–2), we provide an intuitive description of the Esterel language—enough to familiarize the reader with Esterel's synchronous model of time and the implications it

---

\*A major side benefit of working on Esterel is that most of the meetings take place along the Côte d'Azur, which, not coincidentally, includes the Esterel region after which the language was named.

has for compilation. This should also be enough to get one started writing Esterel programs, but it does not presume to be a comprehensive tutorial on coding in Esterel.

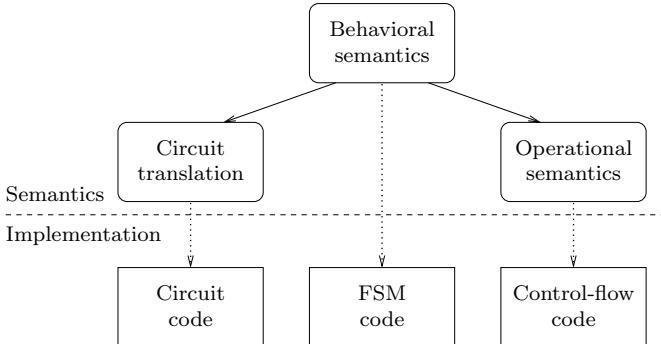

The second part (Chapters 3–6) describes the formal semantics of Esterel, extending the work of Berry [7]. Why do we need three very different presentations of Esterel semantics? Each takes a different approach to describing how an Esterel program is to be executed and is appropriate for addressing different issues in code generation. The behavioral semantics (Chapter 4) is the simplest we present and most clearly addresses some of the thornier aspects of Esterel’s rich control constructs and intra-cycle data dependencies. Unfortunately, it is a poor starting point for implementing the language as it represents control by rewriting the program. This makes for a convenient formalism but would make for an extremely inefficient implementation.

The practical shortcomings of the behavioral semantics lead us to the operational semantics (Chapter 5), which uses a more complicated formalism that represents program state by decorating the program text with all manner of diacritical marks. It is a much more complicated formalism as a result, but much closer to a practical implementation that represents program state as some sort of persistent marking of a program.

Unlike the behavioral and operational semantics, which use Plotkin’s structural operational style, the third style presented in the second part—the circuit translation—shows how to translate an Esterel program into a circuit netlist. While this may appear surprising for a compiler that produces software, it turns out to be quite effective as the semantics of the circuit model very closely match those of Esterel and are much simpler. In fact, all the efficient compilation techniques that we present in the third part of the book start from GRC—a circuit-netlist-like intermediate representation.

Finally, the third part of the book (Chapters 7–10) gets at our main point: how to translate Esterel programs into efficient software implementations. After an overview, we present the GRC intermediate format (Chapter 8)—a representation developed by Potop-Butucaru as part of his thesis work that has become the foundation for a number of compilers. GRC is a hybrid representation that resembles both a traditional control-flow graph and a circuit netlist; it embodies all that we have learned about the structure of Esterel semantics in the past twenty years. Generating efficient code from it is natural; we describe the basic translation in Chapter 9. Finally, in Chapter 10, we describe how a slight variant of the representation has been used as the basis of two back ends in the open-source Columbia Esterel compiler.

The four appendices contain information that had previously been scattered in various technical reports and tutorials. Appendix A discusses parts of the language that are not usually included in the formal presentation of the language semantics, including valued signals, the `pre` operator, concurrent `trap-exit` abortion handling, and task control. Most amount to syntactic sugar, but deserve the more formal treatment we give them here.

Appendix B is the first semi-formal language reference manual for the V5 dialect of Esterel we use in this book. Previously, this information has been presented in a less formal tutorial style that was not as suitable for writing a compiler. See the Esterel V5 primer [8].

Appendix C presents the C language interface used by all the compilers described in this book. This interface was first used in the INRIA compiler and has since become the de facto standard for code generated from Esterel. The appendix explains, among other things, how to interface with the C code generated by any Esterel compiler and actually make use of it, which in some sense is the whole point of this book.

Finally, Appendix D presents the new Esterel V7 dialect, which has been under development at Esterel Technologies since 2001 as a broad extension of Esterel V5. The compilation techniques presented in this book are being applied to this dialect, as its core semantics remain the same. The Esterel V7 language is open (not proprietary) and its language reference manual [29] has been submitted for IEEE standardization.

#### *Acknowledgements*

Potop-Butucaru would like to acknowledge the supervision and help of Robert de Simone in writing of the original Ph.D. thesis.

# Contents

|                                                         |            |

|---------------------------------------------------------|------------|

| <b>Preface</b>                                          | <b>vii</b> |

| <b>I The Esterel Language</b>                           | <b>1</b>   |

| <b>1 Introduction to Esterel</b>                        | <b>3</b>   |

| 1.1 Reactive Systems . . . . .                          | 3          |

| 1.2 The Synchronous Hypothesis . . . . .                | 4          |

| 1.3 Implementation Issues . . . . .                     | 5          |

| 1.4 Causality . . . . .                                 | 6          |

| 1.5 Related work . . . . .                              | 6          |

| 1.6 A First Esterel Example . . . . .                   | 7          |

| 1.7 Causality Cycles . . . . .                          | 8          |

| 1.8 Code Generation . . . . .                           | 9          |

| 1.8.1 Translation to Explicit State Machines . . . . .  | 9          |

| 1.8.2 Translation to Circuits . . . . .                 | 10         |

| 1.8.3 Direct Compilation to C Code . . . . .            | 12         |

| 1.9 Executing the Generated Code . . . . .              | 12         |

| 1.9.1 Existing Solutions . . . . .                      | 13         |

| <b>2 The Esterel Language</b>                           | <b>15</b>  |

| 2.1 Syntax and Naïve Semantic Principles . . . . .      | 15         |

| 2.2 The Kernel Esterel Language . . . . .               | 20         |

| 2.3 Esterel Through Examples . . . . .                  | 24         |

| 2.4 Host Language . . . . .                             | 31         |

| 2.5 Program Structure and Interface . . . . .           | 31         |

| 2.5.1 Data Handling . . . . .                           | 32         |

| 2.5.2 Signal and Signal Relation Declarations . . . . . | 34         |

| 2.5.3 The <code>run</code> Pseudo-Statement . . . . .   | 34         |

|                                                                                          |           |

|------------------------------------------------------------------------------------------|-----------|

| <b>II Formal Semantics</b>                                                               | <b>39</b> |

| <b>3 Introduction to Esterel Semantics</b>                                               | <b>41</b> |

| 3.1 Intuition and Mathematical Foundations . . . . .                                     | 41        |

| 3.1.1 The Constructive Approach . . . . .                                                | 43        |

| 3.2 Flavors of Constructive Semantics . . . . .                                          | 47        |

| 3.3 Conventions and Preliminary Definitions . . . . .                                    | 50        |

| 3.3.1 Global Correctness of an Esterel Program . . . . .                                 | 50        |

| 3.3.2 Restriction to Kernel Esterel . . . . .                                            | 51        |

| 3.3.3 Signal Events . . . . .                                                            | 51        |

| 3.3.4 Trap Handling and Completion Codes . . . . .                                       | 51        |

| <b>4 Constructive Behavioral Semantics</b>                                               | <b>55</b> |

| 4.1 Behavioral Transitions . . . . .                                                     | 55        |

| 4.1.1 Transition syntax . . . . .                                                        | 55        |

| 4.1.2 States as Decorated Terms . . . . .                                                | 56        |

| 4.1.3 State Syntax . . . . .                                                             | 57        |

| 4.2 Analysis of Potentials . . . . .                                                     | 58        |

| 4.2.1 The Definition of <i>Must</i> , <i>Can</i> , and <i>Can</i> <sup>+</sup> . . . . . | 60        |

| 4.2.2 Elementary Properties . . . . .                                                    | 68        |

| 4.3 Semantic Rules . . . . .                                                             | 68        |

| 4.4 Proof . . . . .                                                                      | 72        |

| 4.5 Determinism . . . . .                                                                | 72        |

| 4.6 Loop-Safe Programs. Completion Code Potentials . . . . .                             | 73        |

| 4.7 Program Behavior . . . . .                                                           | 75        |

| <b>5 Constructive Operational Semantics</b>                                              | <b>79</b> |

| 5.1 Microsteps . . . . .                                                                 | 80        |

| 5.2 COS Terms . . . . .                                                                  | 80        |

| 5.2.1 Control Flow Propagation . . . . .                                                 | 81        |

| 5.2.2 State-Dependent Behavior . . . . .                                                 | 81        |

| 5.2.3 Syntax of Semantic Terms . . . . .                                                 | 82        |

| 5.3 Data Representation . . . . .                                                        | 84        |

| 5.4 Semantic Rules . . . . .                                                             | 85        |

| 5.4.1 Rules for Pure Esterel Primitives . . . . .                                        | 85        |

| 5.4.2 Rules for Data-Handling Primitives . . . . .                                       | 92        |

| 5.5 Analysis of Potentials . . . . .                                                     | 95        |

| 5.5.1 Reduction to Non-Dotted Terms . . . . .                                            | 96        |

| 5.5.2 Non-Dotted Terms over Dataless Primitives . . . . .                                | 97        |

| 5.5.3 Non-Dotted Terms over Data-Handling Primitives . . . . .                           | 99        |

| 5.6 Behaviors as Sequences of Microsteps . . . . .                                       | 99        |

| 5.7 COS versus CBS . . . . .                                                             | 101       |

|                                                                       |            |

|-----------------------------------------------------------------------|------------|

| <b>6 Constructive Circuit Translation</b>                             | <b>103</b> |

| 6.1 Digital Circuits with Data . . . . .                              | 104        |

| 6.1.1 Circuit Semantics. Constructive Causality . . . . .             | 104        |

| 6.1.2 Extension to Circuits with Data . . . . .                       | 107        |

| 6.1.3 Formal Definitions . . . . .                                    | 110        |

| 6.2 Translation Principles . . . . .                                  | 112        |

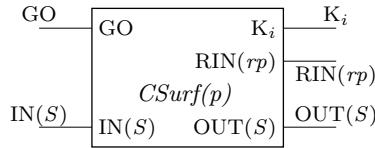

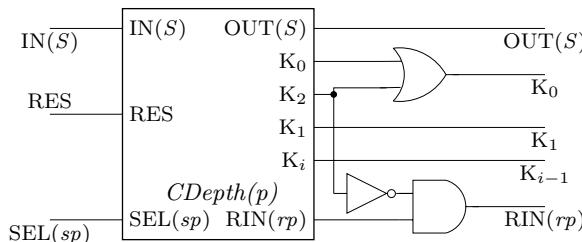

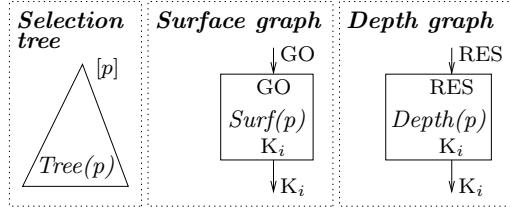

| 6.2.1 The Selection Circuit . . . . .                                 | 114        |

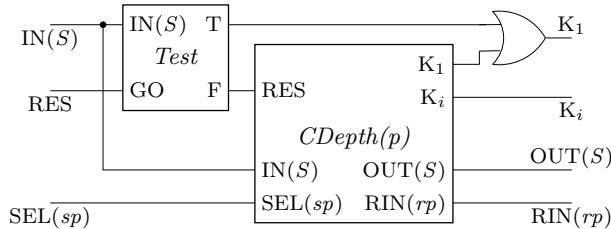

| 6.2.2 The Surface and Depth Circuits . . . . .                        | 115        |

| 6.2.3 The Global Context . . . . .                                    | 116        |

| 6.3 Translation Rules . . . . .                                       | 117        |

| 6.3.1 Dataless Primitives . . . . .                                   | 117        |

| 6.3.2 Data-Handling Primitives . . . . .                              | 126        |

| 6.4 Circuit Translation versus COS . . . . .                          | 128        |

| <b>III Compiling Esterel</b>                                          | <b>133</b> |

| <b>7 Overview</b>                                                     | <b>135</b> |

| 7.1 Compiler Classes . . . . .                                        | 135        |

| 7.2 A Brief History . . . . .                                         | 136        |

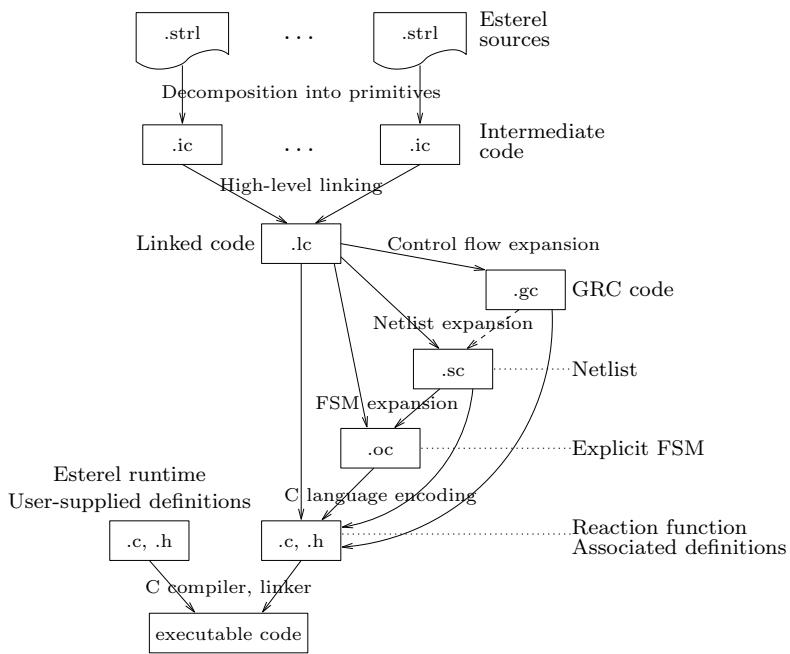

| 7.3 The INRIA Compiler . . . . .                                      | 137        |

| 7.4 The Synopsys Compiler . . . . .                                   | 139        |

| 7.5 The Saxo-RT Compiler . . . . .                                    | 140        |

| 7.6 The Columbia Esterel Compiler . . . . .                           | 144        |

| <b>8 The GRC Intermediate Format</b>                                  | <b>145</b> |

| 8.1 Definition and Intuitive Semantics . . . . .                      | 146        |

| 8.1.1 The Hierarchical State Representation . . . . .                 | 146        |

| 8.1.2 The Control/Data Flowgraph . . . . .                            | 149        |

| 8.1.3 Implementation Issues . . . . .                                 | 154        |

| 8.2 Esterel to GRC Translation . . . . .                              | 158        |

| 8.2.1 Translation Principles . . . . .                                | 158        |

| 8.2.2 Translation Rules . . . . .                                     | 159        |

| 8.2.3 The Global Context . . . . .                                    | 167        |

| 8.3 Formal Simulation Semantics and Translation Correctness . . . . . | 167        |

| 8.4 Format Optimizations . . . . .                                    | 168        |

| 8.4.1 State Representation Analysis . . . . .                         | 170        |

| 8.4.2 Flowgraph Optimizations . . . . .                               | 173        |

| <b>9 Code Generation from GRC</b>                                     | <b>179</b> |

| 9.1 Defining “Acyclic” . . . . .                                      | 180        |

| 9.2 Code Generation for Acyclic Specifications . . . . .              | 185        |

| 9.2.1 State Encoding . . . . .                                        | 185        |

| 9.2.2 Flowgraph Transformations . . . . .                             | 190        |

| 9.2.3 Scheduling . . . . .                                            | 192        |

|           |                                                     |            |

|-----------|-----------------------------------------------------|------------|

| 9.3       | Code Generation for Cyclic Specifications . . . . . | 193        |

| 9.4       | Benchmarks . . . . .                                | 200        |

| <b>10</b> | <b>The Columbia Compiler</b>                        | <b>203</b> |

| 10.1      | The Dynamic Technique . . . . .                     | 203        |

| 10.1.1    | An Example . . . . .                                | 204        |

| 10.1.2    | Sequential Code Generation . . . . .                | 211        |

| 10.1.3    | The Clustering Algorithm . . . . .                  | 214        |

| 10.2      | The Program Dependence Graph Approach . . . . .     | 215        |

| 10.2.1    | Program Dependence Graphs . . . . .                 | 216        |

| 10.2.2    | Scheduling . . . . .                                | 218        |

| 10.2.3    | Restructuring the PDG . . . . .                     | 221        |

| 10.2.4    | Generating Sequential Code . . . . .                | 228        |

| 10.3      | Benchmarks . . . . .                                | 229        |

| <b>A</b>  | <b>Language Extensions</b>                          | <b>235</b> |

| A.1       | Signal Expressions . . . . .                        | 235        |

| A.1.1     | Syntactic Aspects and Limitations . . . . .         | 236        |

| A.1.2     | Combinational Expressions . . . . .                 | 236        |

| A.1.3     | The <code>pre</code> Operator . . . . .             | 238        |

| A.1.4     | Delay Expressions. Preemption Triggers . . . . .    | 241        |

| A.2       | Traps and Trap Expressions . . . . .                | 242        |

| A.2.1     | Concurrent Traps and Trap Expressions . . . . .     | 243        |

| A.2.2     | Valued Traps . . . . .                              | 244        |

| A.3       | The <code>finalize</code> Statement . . . . .       | 245        |

| A.4       | Tasks . . . . .                                     | 247        |

| A.4.1     | Task Synchronization Semantics . . . . .            | 248        |

| A.4.2     | Multiple <code>exec</code> . . . . .                | 251        |

| <b>B</b>  | <b>An Esterel Reference Manual</b>                  | <b>253</b> |

| B.1       | Lexical Conventions . . . . .                       | 253        |

| B.1.1     | Tokens . . . . .                                    | 253        |

| B.1.2     | Comments . . . . .                                  | 253        |

| B.1.3     | Identifiers . . . . .                               | 253        |

| B.1.4     | Reserved Words . . . . .                            | 254        |

| B.1.5     | Literals . . . . .                                  | 254        |

| B.2       | Namespaces and Predefined Objects . . . . .         | 255        |

| B.2.1     | Signals and Sensors . . . . .                       | 256        |

| B.2.2     | Variables and Constants . . . . .                   | 256        |

| B.2.3     | Traps . . . . .                                     | 256        |

| B.2.4     | Types . . . . .                                     | 257        |

| B.2.5     | Functions and Procedures . . . . .                  | 257        |

| B.2.6     | Tasks . . . . .                                     | 257        |

| B.3       | Expressions . . . . .                               | 258        |

| B.3.1     | Data Expressions . . . . .                          | 258        |

|          |                                                                     |            |

|----------|---------------------------------------------------------------------|------------|

| B.3.2    | Constant Atoms . . . . .                                            | 258        |

| B.3.3    | Signal Expressions . . . . .                                        | 259        |

| B.3.4    | Delay Expressions . . . . .                                         | 259        |

| B.3.5    | Trap Expressions . . . . .                                          | 259        |

| B.4      | Statements . . . . .                                                | 260        |

| B.4.1    | Control Flow Operators . . . . .                                    | 260        |

| B.4.2    | <code>abort</code> : Strong Preemption . . . . .                    | 261        |

| B.4.3    | <code>await</code> : Strong Preemption . . . . .                    | 262        |

| B.4.4    | <code>call</code> : Procedure Call . . . . .                        | 264        |

| B.4.5    | <code>do-upto</code> : Conditional Iteration (deprecated) . . . . . | 264        |

| B.4.6    | <code>do-watching</code> : Strong Preemption (deprecated) . . . . . | 264        |

| B.4.7    | <code>emit</code> : Signal Emission . . . . .                       | 264        |

| B.4.8    | <code>every-do</code> : Conditional Iteration . . . . .             | 265        |

| B.4.9    | <code>exec</code> : Task Execution . . . . .                        | 265        |

| B.4.10   | <code>exit</code> : Trap Exit . . . . .                             | 266        |

| B.4.11   | <code>halt</code> : Wait Forever . . . . .                          | 266        |

| B.4.12   | <code>if</code> : Conditional for Data . . . . .                    | 266        |

| B.4.13   | <code>loop</code> : Infinite Loop . . . . .                         | 267        |

| B.4.14   | <code>loop-each</code> : Conditional Iteration . . . . .            | 267        |

| B.4.15   | <code>nothing</code> : No Operation . . . . .                       | 268        |

| B.4.16   | <code>pause</code> : Unit Delay . . . . .                           | 268        |

| B.4.17   | <code>present</code> : Conditional for Signals . . . . .            | 268        |

| B.4.18   | <code>repeat</code> : Iterate a Fixed Number of Times . . . . .     | 269        |

| B.4.19   | <code>run</code> : Module Instantiation . . . . .                   | 270        |

| B.4.20   | <code>signal</code> : Local Signal Declaration . . . . .            | 271        |

| B.4.21   | <code>suspend</code> : Preemption with State Freeze . . . . .       | 272        |

| B.4.22   | <code>sustain</code> : Emit a Signal Indefinitely . . . . .         | 273        |

| B.4.23   | <code>trap</code> : Trap Declaration and Handling . . . . .         | 273        |

| B.4.24   | <code>var</code> : Local Variable Declaration . . . . .             | 273        |

| B.4.25   | <code>weak abort</code> : Weak Preemption . . . . .                 | 274        |

| B.5      | Modules . . . . .                                                   | 275        |

| B.5.1    | Interface Declarations . . . . .                                    | 276        |

| <b>C</b> | <b>The C Language Interface</b>                                     | <b>281</b> |

| C.1      | Overview . . . . .                                                  | 281        |

| C.2      | C Code for Data Handling . . . . .                                  | 283        |

| C.2.1    | Defining Data-handling Objects . . . . .                            | 283        |

| C.2.2    | Predefined Types . . . . .                                          | 283        |

| C.2.3    | User-defined Types . . . . .                                        | 283        |

| C.2.4    | Constants . . . . .                                                 | 286        |

| C.2.5    | Functions . . . . .                                                 | 286        |

| C.2.6    | Procedures . . . . .                                                | 287        |

| C.3      | The Reaction Interface . . . . .                                    | 288        |

| C.3.1    | Input Signals . . . . .                                             | 288        |

| C.3.2    | Return Signals . . . . .                                            | 289        |

|                     |                                                                      |            |

|---------------------|----------------------------------------------------------------------|------------|

| C.3.3               | Output Signals . . . . .                                             | 289        |

| C.3.4               | Inputoutput Signals . . . . .                                        | 289        |

| C.3.5               | Sensors . . . . .                                                    | 290        |

| C.3.6               | Reaction and Reset . . . . .                                         | 290        |

| C.3.7               | Notes . . . . .                                                      | 291        |

| C.4                 | Task Handling . . . . .                                              | 292        |

| C.4.1               | The Low-level Layer: ExecStatus . . . . .                            | 292        |

| C.4.2               | The Functional Interface to Tasks . . . . .                          | 295        |

| <b>D</b>            | <b>Esterel V7</b>                                                    | <b>297</b> |

| D.1                 | Data Support . . . . .                                               | 298        |

| D.1.1               | Basic Data Types . . . . .                                           | 298        |

| D.1.2               | Arrays . . . . .                                                     | 298        |

| D.1.3               | Generic Types . . . . .                                              | 299        |

| D.1.4               | Bitvectors . . . . .                                                 | 299        |

| D.1.5               | From Numbers to Bitvectors and Back . . . . .                        | 300        |

| D.1.6               | Data Units . . . . .                                                 | 300        |

| D.2                 | Signals . . . . .                                                    | 301        |

| D.2.1               | Value-only Signals . . . . .                                         | 301        |

| D.2.2               | Temporary Signals . . . . .                                          | 301        |

| D.2.3               | Registered Signals . . . . .                                         | 301        |

| D.2.4               | Signal Initialization . . . . .                                      | 302        |

| D.2.5               | Oracles . . . . .                                                    | 302        |

| D.3                 | Interfaces . . . . .                                                 | 303        |

| D.3.1               | Interface Declaration . . . . .                                      | 303        |

| D.3.2               | Interfaces and Modules . . . . .                                     | 303        |

| D.3.3               | Mirroring an Interface . . . . .                                     | 304        |

| D.3.4               | Interface Refinement in Modules . . . . .                            | 304        |

| D.4                 | Statements . . . . .                                                 | 304        |

| D.4.1               | Expressions and Tests . . . . .                                      | 304        |

| D.4.2               | Static Replication . . . . .                                         | 304        |

| D.4.3               | Enhanced Emit and Sustain Statements . . . . .                       | 305        |

| D.4.4               | Explicit and Implicit Assertions . . . . .                           | 306        |

| D.4.5               | Weak Suspension . . . . .                                            | 307        |

| D.4.6               | Signal Connection by Module Instantiation . . . . .                  | 309        |

| D.5                 | Multiclock Design . . . . .                                          | 310        |

| D.5.1               | Clocks and Multiple Units . . . . .                                  | 311        |

| D.5.2               | Simulation of Multiclock Designs by Single-clocked Designs . . . . . | 312        |

| <b>Bibliography</b> |                                                                      | <b>315</b> |

| <b>Index</b>        |                                                                      | <b>323</b> |

# Figures

|      |                                                                                       |     |

|------|---------------------------------------------------------------------------------------|-----|

| 1.1  | Execution cycle . . . . .                                                             | 5   |

| 1.2  | A possible execution trace for ABRO . . . . .                                         | 8   |

| 1.3  | The automaton and explicit FSM code for the ABRO example . . . . .                    | 10  |

| 1.4  | Synchronous circuit model . . . . .                                                   | 11  |

| 1.5  | Circuit code for ABRO (the reaction function) . . . . .                               | 11  |

| 1.6  | Control-flow (pseudo-)code for ABRO . . . . .                                         | 12  |

| 1.7  | A possible asynchronous run of ABRO . . . . .                                         | 13  |

| 2.1  | An execution trace of <code>MainExample</code> . . . . .                              | 25  |

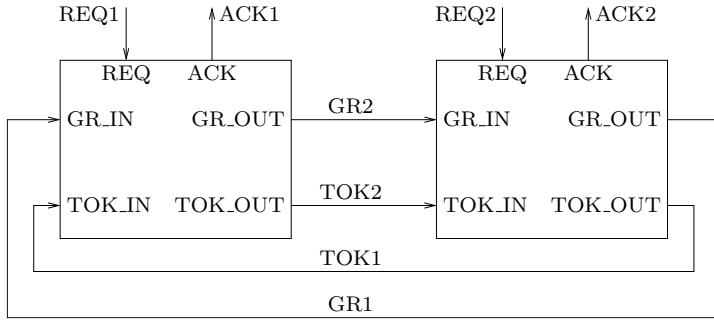

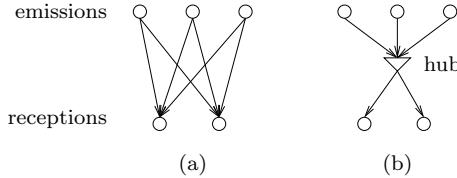

| 2.2  | Interconnections between <code>Cell</code> modules in <code>Arbiter2</code> . . . . . | 28  |

| 2.3  | A 3-cell FIFO in Esterel. . . . .                                                     | 35  |

| 3.1  | A correct, but complex Esterel example . . . . .                                      | 43  |

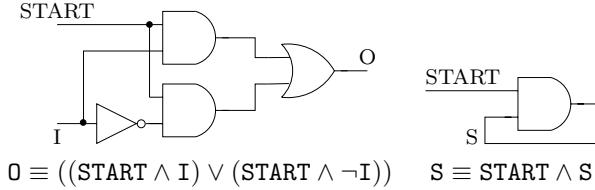

| 3.2  | Boolean circuits for two intuitionistic formulas . . . . .                            | 46  |

| 3.3  | Truth table for ternary logic ( $\mathcal{B}_\perp$ ) operators . . . . .             | 46  |

| 3.4  | Completion codes in the start instant of a simple statement . . . . .                 | 53  |

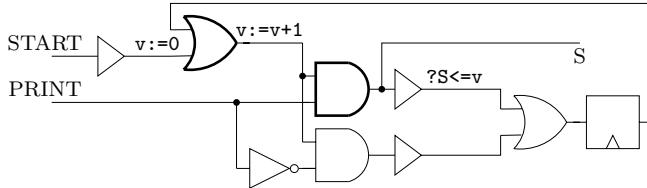

| 6.1  | A possible circuit translation for ABRO . . . . .                                     | 105 |

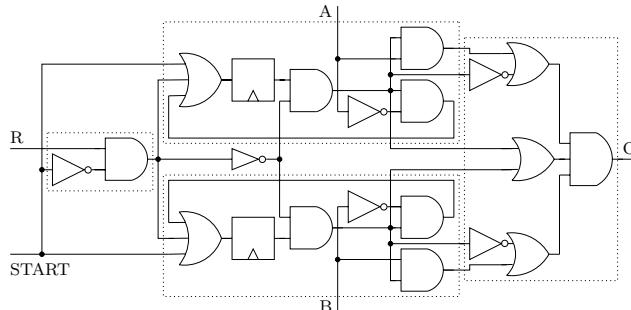

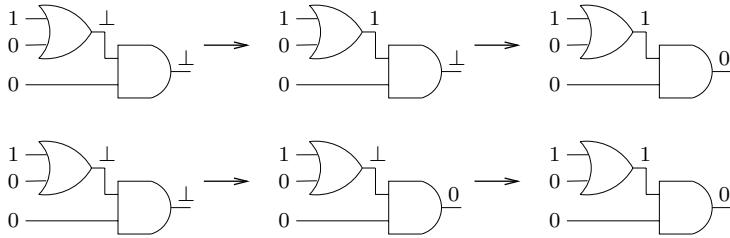

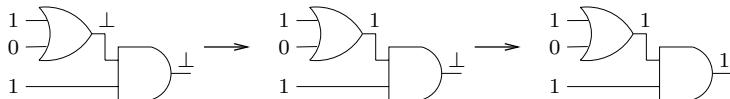

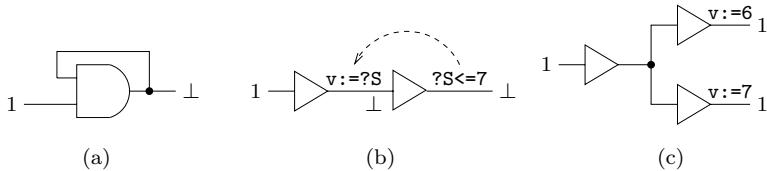

| 6.2  | The two possible evaluation sequences for a small circuit . . . . .                   | 106 |

| 6.3  | Causality in circuit evaluation . . . . .                                             | 106 |

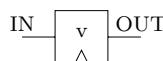

| 6.4  | A simple sequential circuit . . . . .                                                 | 107 |

| 6.5  | Circuit with data, first example . . . . .                                            | 108 |

| 6.6  | Circuit with data, second example . . . . .                                           | 109 |

| 6.7  | Circuit with data, third example . . . . .                                            | 109 |

| 6.8  | Incorrect circuits . . . . .                                                          | 112 |

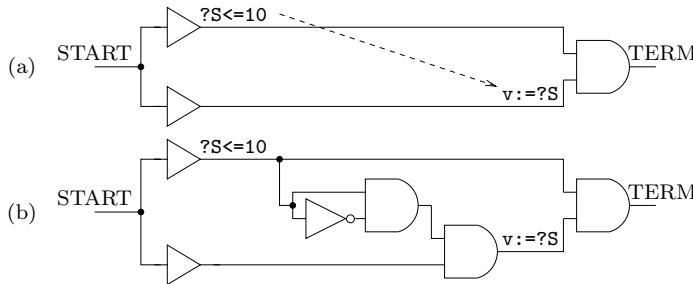

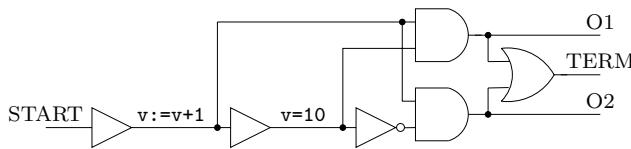

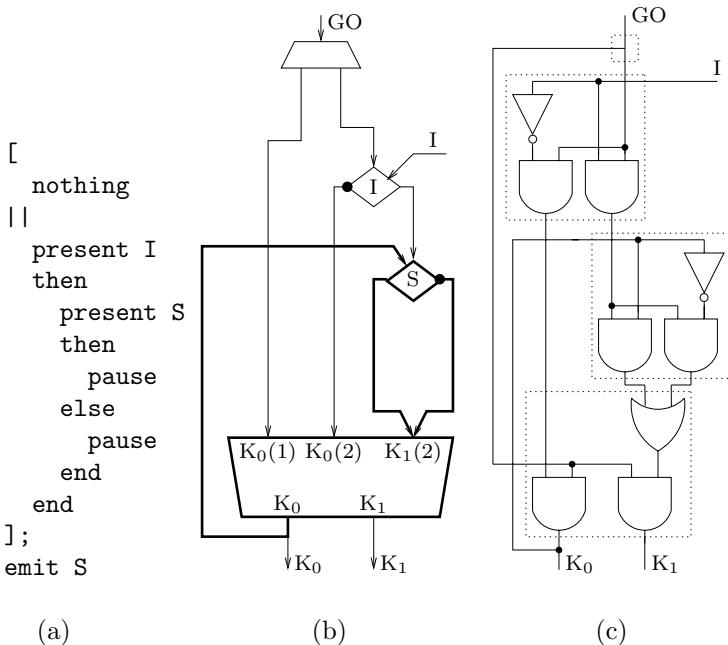

| 6.9  | The selection circuit of a simple example . . . . .                                   | 115 |

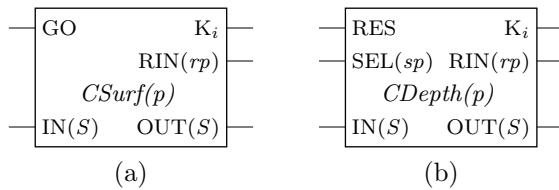

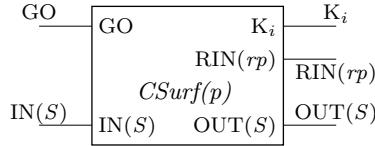

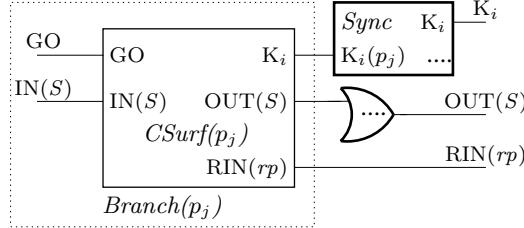

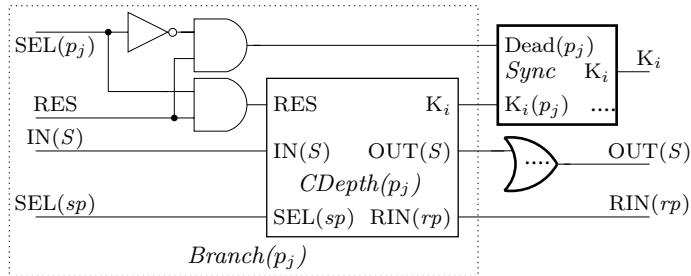

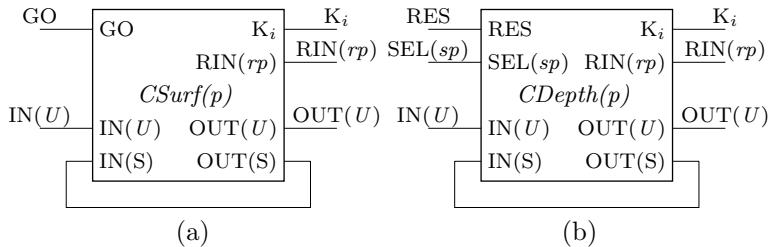

| 6.10 | The interface of the generated circuits . . . . .                                     | 115 |

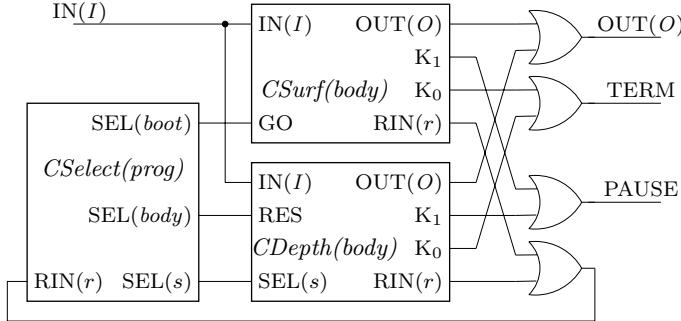

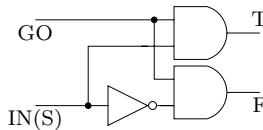

| 6.11 | The global translation context . . . . .                                              | 116 |

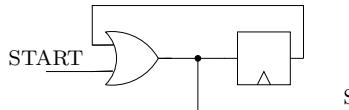

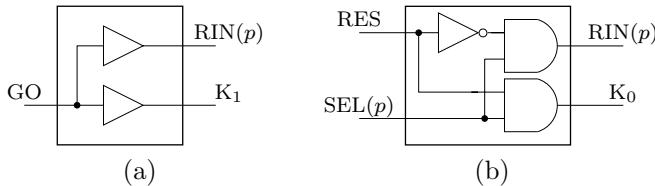

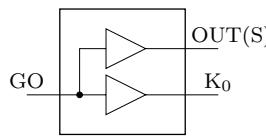

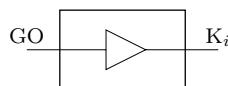

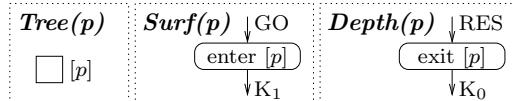

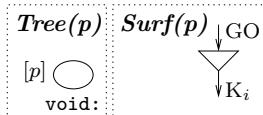

| 6.12 | Surface and depth circuits for <code>pause</code> . . . . .                           | 117 |

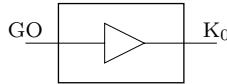

| 6.13 | Surface circuit for <code>nothing</code> . . . . .                                    | 117 |

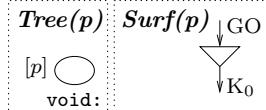

| 6.14 | Surface circuit for “loop $p$ end” . . . . .                                          | 118 |

| 6.15 | Depth circuit for “loop $p$ end” . . . . .                                            | 118 |

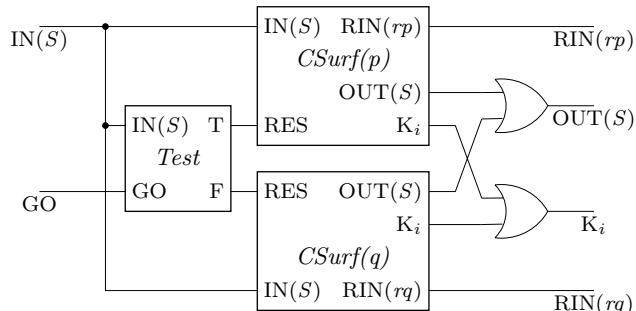

|      |                                                                                                |     |

|------|------------------------------------------------------------------------------------------------|-----|

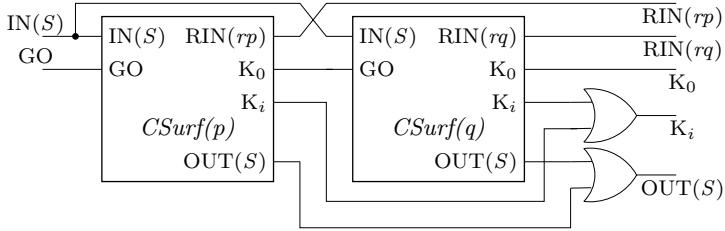

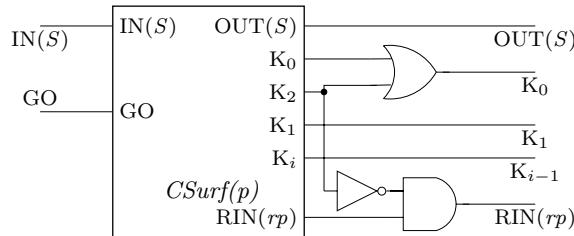

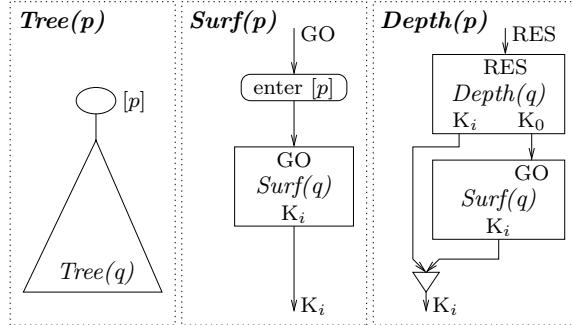

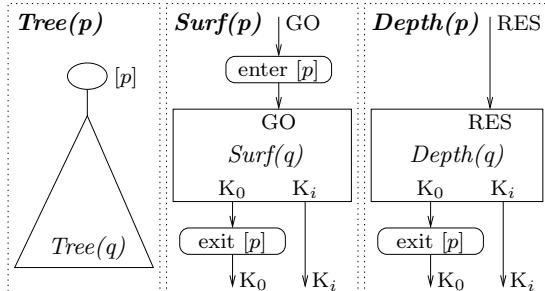

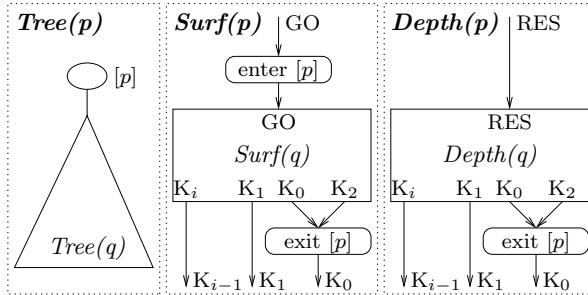

| 6.16 | Surface circuit for the two-way sequence “ <i>p</i> ; <i>q</i> ” . . . . .                     | 119 |

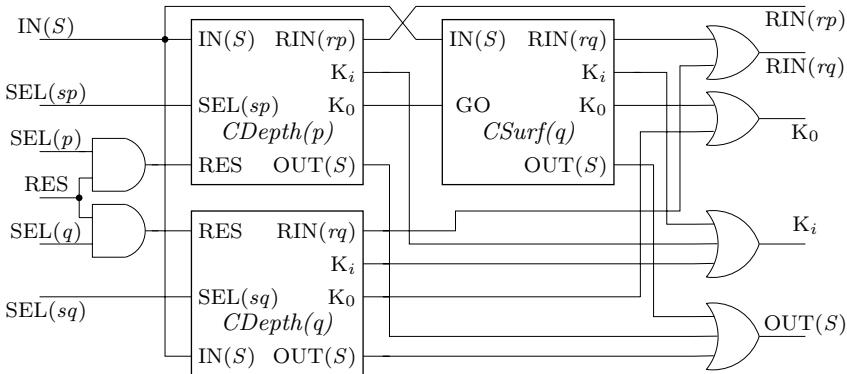

| 6.17 | Depth circuit for the binary sequence “ <i>p</i> ; <i>q</i> ” . . . . .                        | 119 |

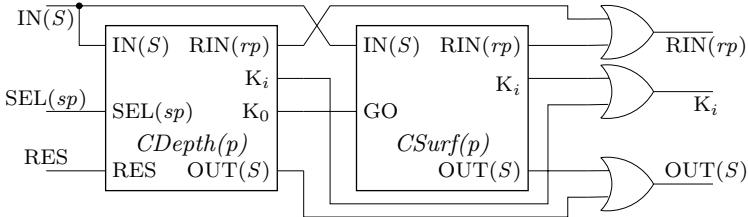

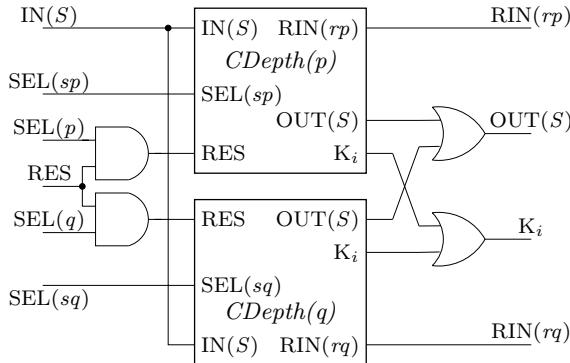

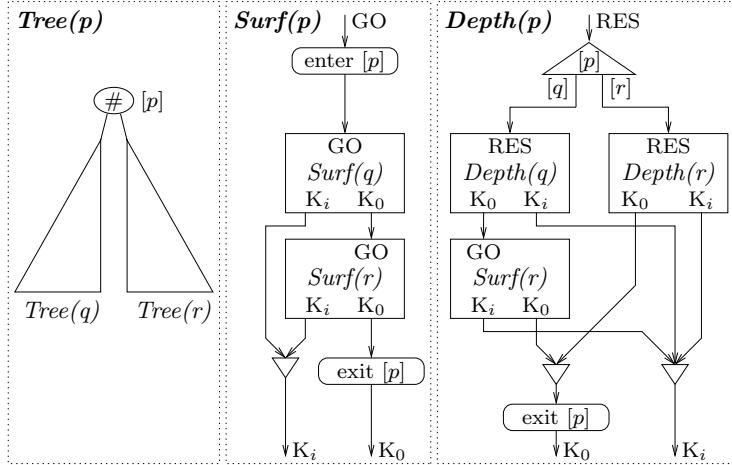

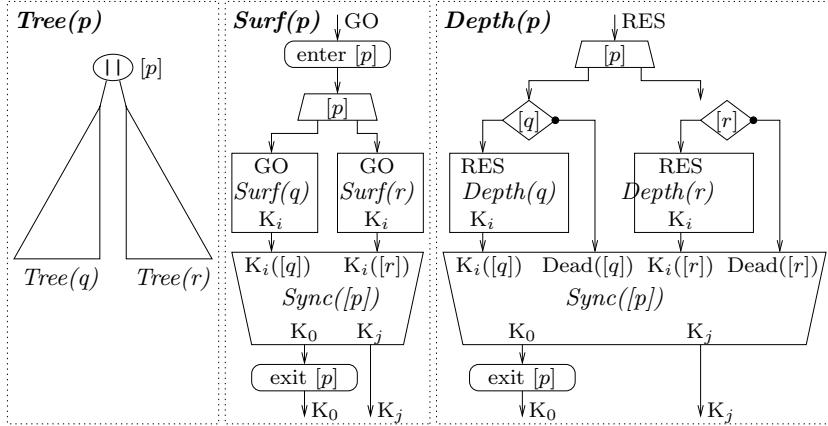

| 6.18 | Surface circuit for “ <i>p</i> <sub>1</sub>    ...    <i>p</i> <sub><i>n</i></sub> ” . . . . . | 120 |

| 6.19 | Depth circuit for “ <i>p</i> <sub>1</sub>    ...    <i>p</i> <sub><i>n</i></sub> ” . . . . .   | 120 |

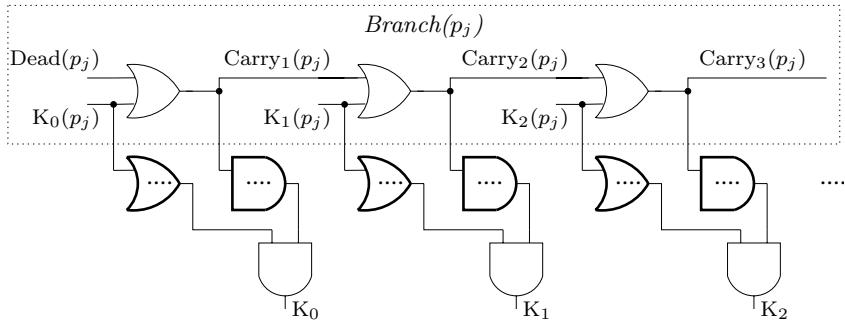

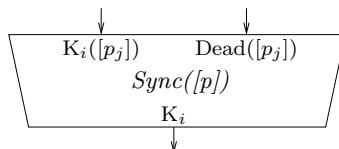

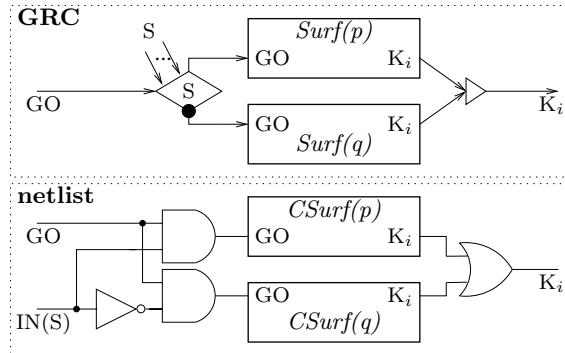

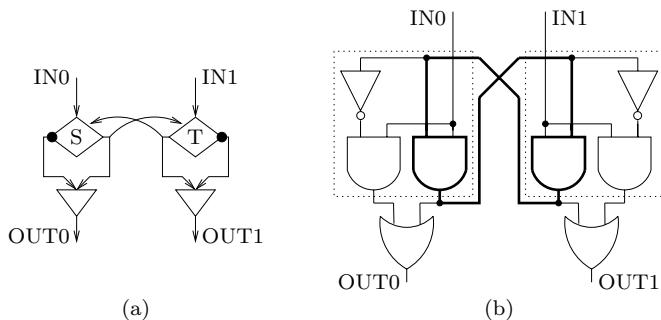

| 6.20 | The circuit-level parallel synchronizer . . . . .                                              | 121 |

| 6.21 | Surface circuit for “ <b>emit S</b> ” . . . . .                                                | 121 |

| 6.22 | Surface and depth circuits for “ <b>signal S in <i>p</i> end</b> ” . . . . .                   | 122 |

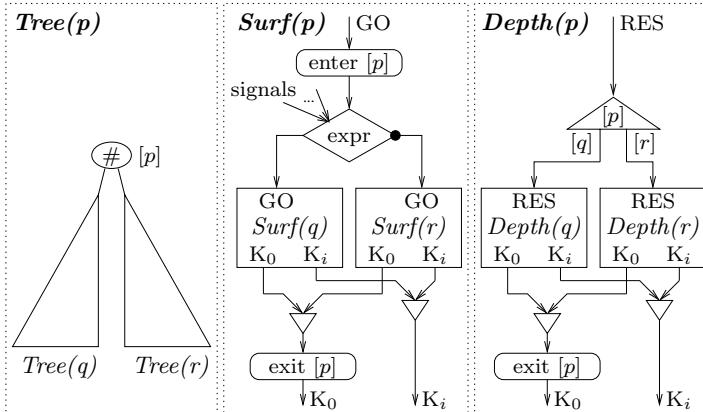

| 6.23 | Surface circuit for the signal and data tests . . . . .                                        | 122 |

| 6.24 | Depth circuit for the test statements . . . . .                                                | 123 |

| 6.25 | Signal test circuit (present statement) . . . . .                                              | 123 |

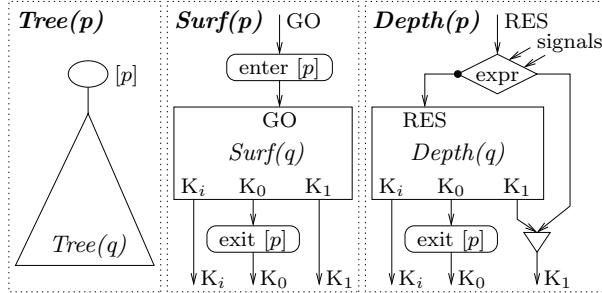

| 6.26 | Surface circuit for “ <b>suspend <i>p</i> when <i>expr</i></b> ” . . . . .                     | 124 |

| 6.27 | Depth circuit for “ <b>suspend <i>p</i> when <i>expr</i></b> ” . . . . .                       | 124 |

| 6.28 | Surface circuit for “ <b>exit <i>T</i>(<i>i</i>)</b> ” . . . . .                               | 124 |

| 6.29 | Surface circuit for “ <b>trap <i>T</i> in <i>p</i> end</b> ” . . . . .                         | 125 |

| 6.30 | Depth circuit for “ <b>trap <i>T</i> in <i>p</i> end</b> ” . . . . .                           | 125 |

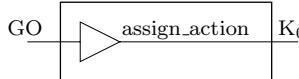

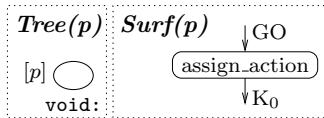

| 6.31 | Surface circuit for the variable assignments . . . . .                                         | 126 |

| 6.32 | Surface circuit for variable declarations . . . . .                                            | 127 |

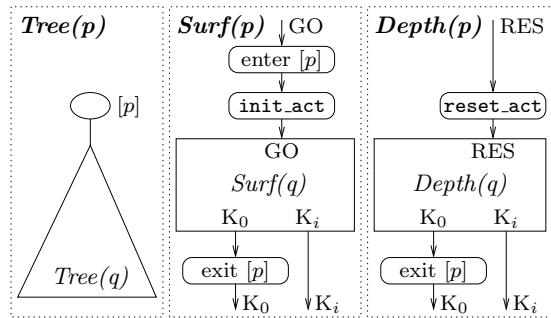

| 6.33 | Depth circuit for variable declarations . . . . .                                              | 128 |

| 6.34 | Variable test circuit ( <b>if</b> statement) . . . . .                                         | 128 |

| 7.1  | Esterel implementation flavors . . . . .                                                       | 136 |

| 7.2  | The flow of the INRIA compiler . . . . .                                                       | 138 |

| 7.3  | Esterel fragment and its Synopsys translation into C . . . . .                                 | 140 |

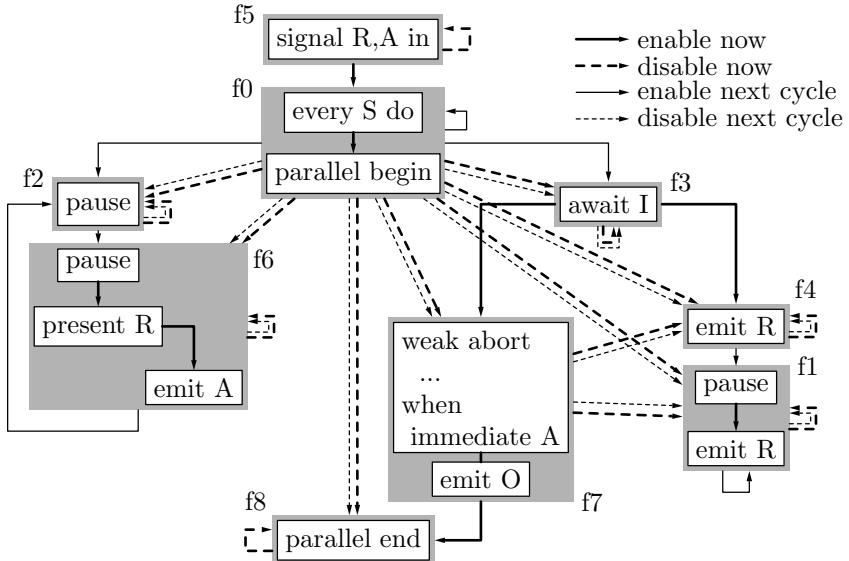

| 7.4  | Concurrent control-flow graph, Synopsys style . . . . .                                        | 141 |

| 7.5  | A simple Esterel program modeling a shared resource . . . . .                                  | 142 |

| 7.6  | Event graph and C code generated by the<br>Saxo-RT compiler . . . . .                          | 143 |

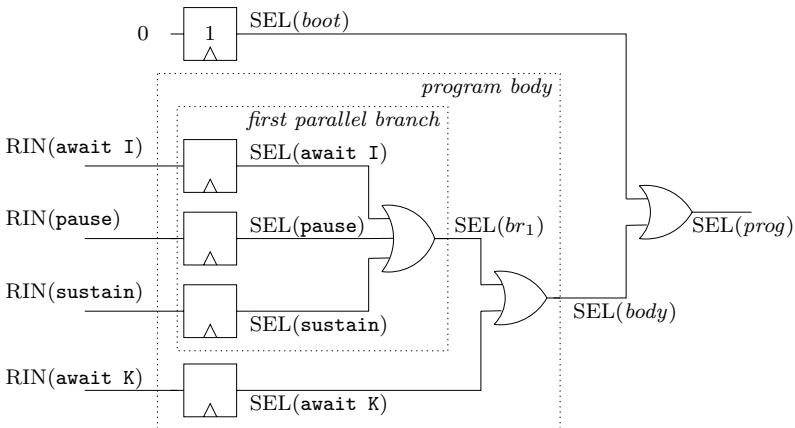

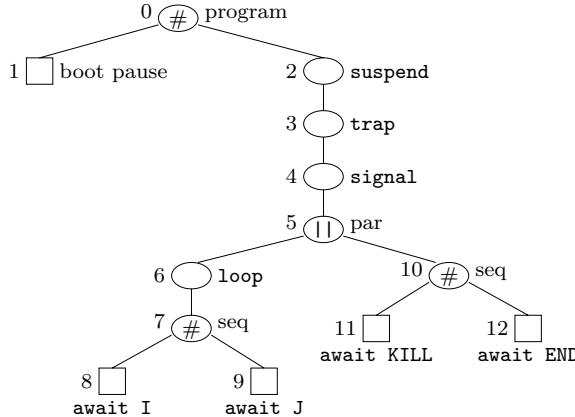

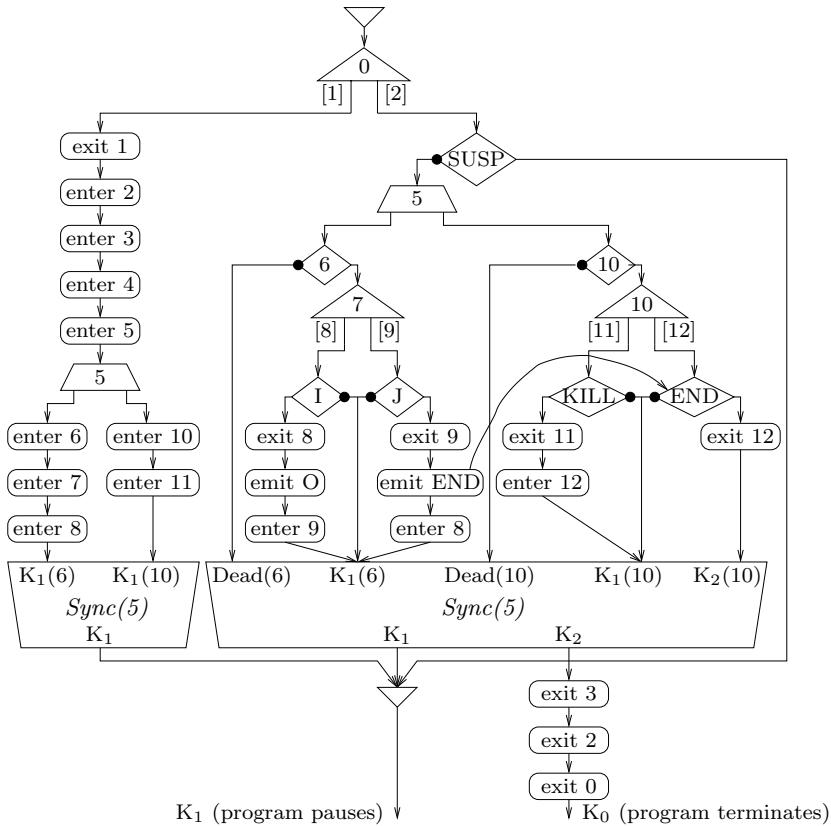

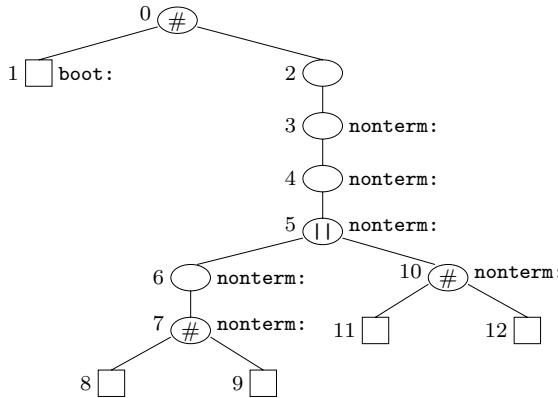

| 8.1  | The <b>MainExample</b> Esterel program . . . . .                                               | 147 |

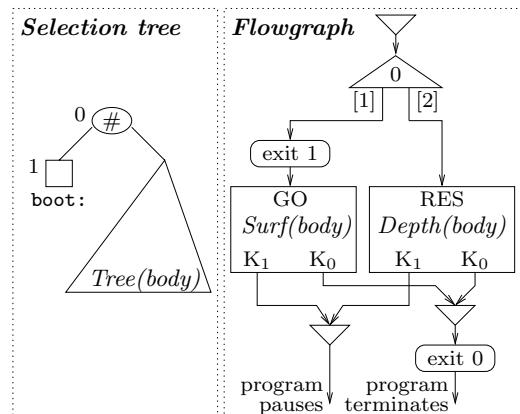

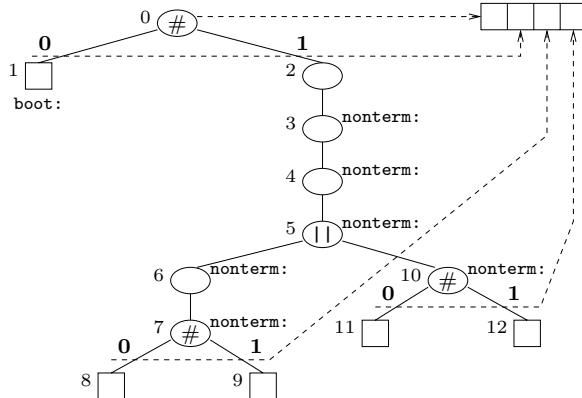

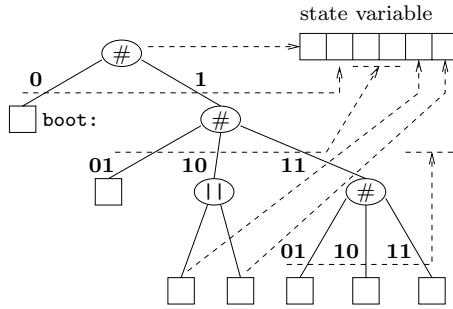

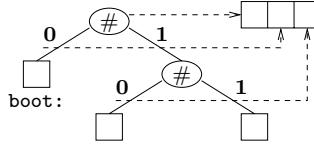

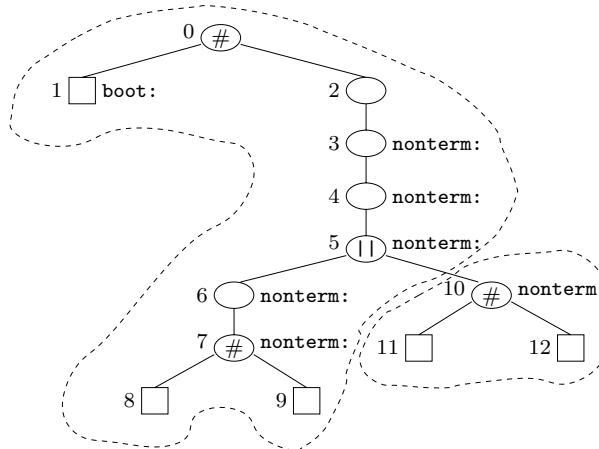

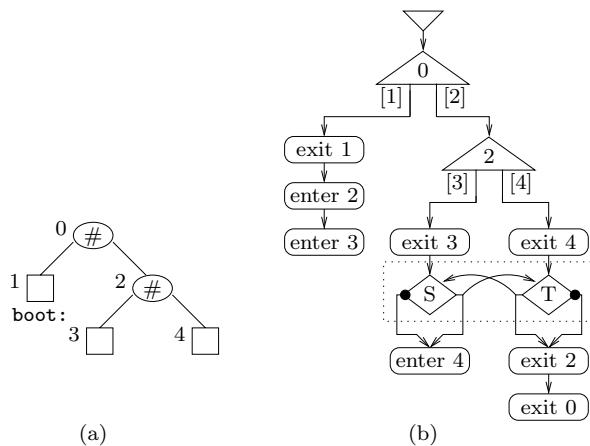

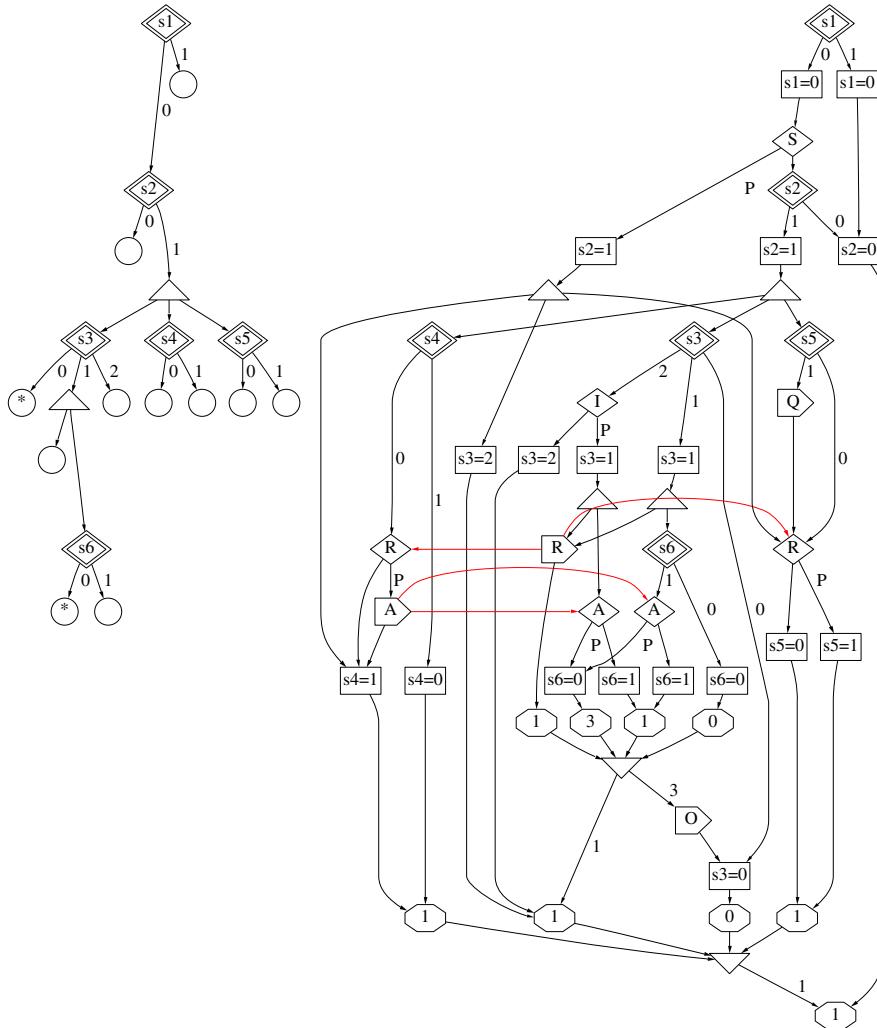

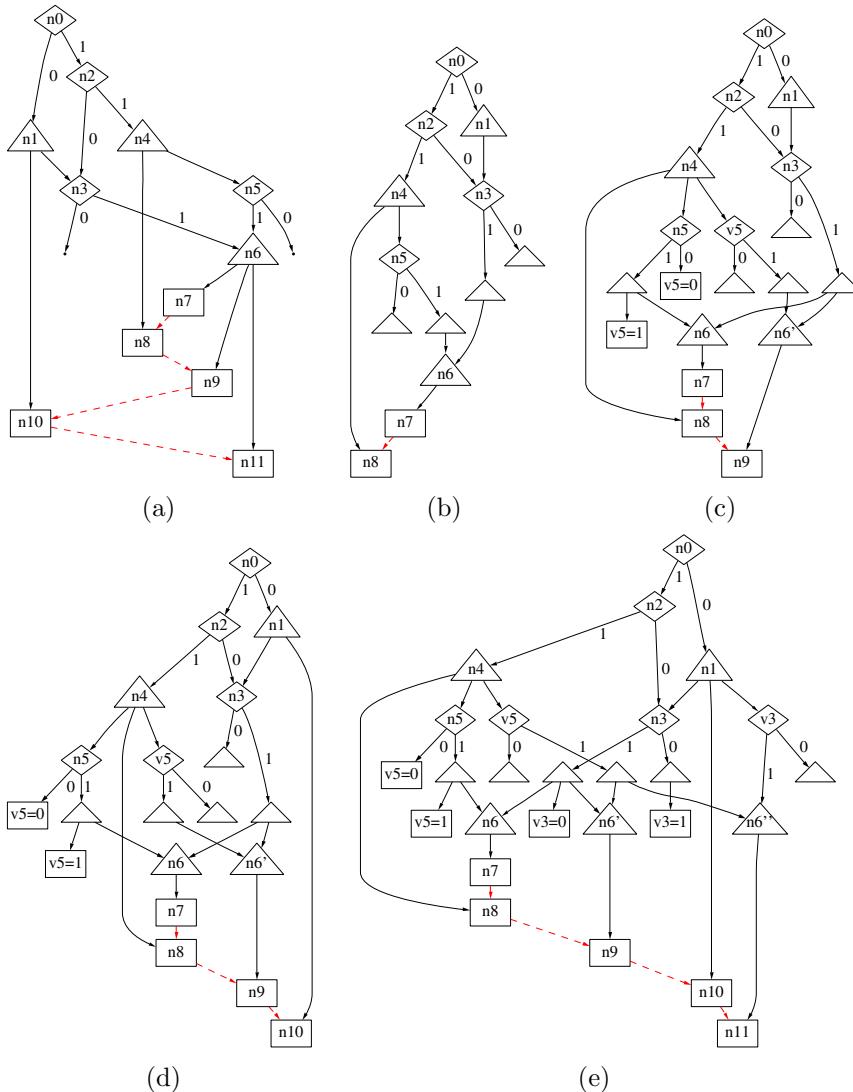

| 8.2  | The selection tree of <b>MainExample</b> . . . . .                                             | 148 |

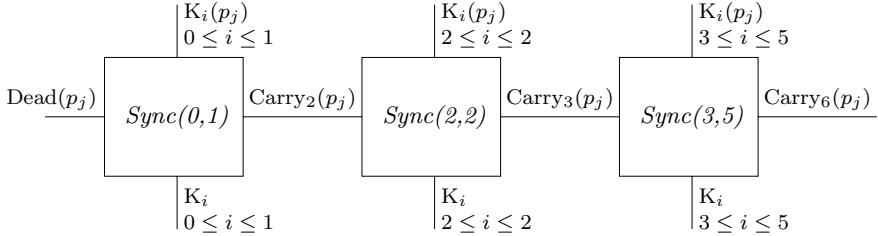

| 8.3  | Selection tree and selection flags for a small example . . . . .                               | 148 |

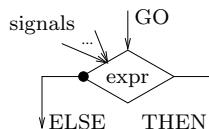

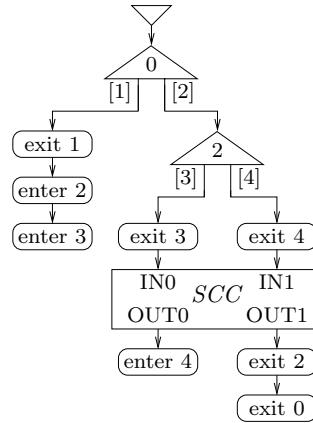

| 8.4  | Simple GRC flowgraph . . . . .                                                                 | 149 |

| 8.5  | Signal dependency representations . . . . .                                                    | 150 |

| 8.6  | The flowgraph of <b>MainExample</b> . . . . .                                                  | 153 |

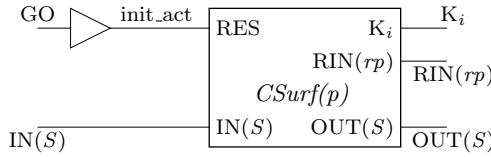

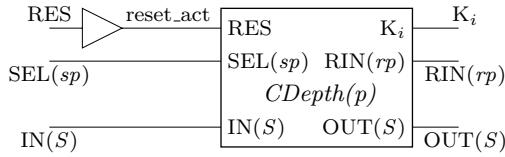

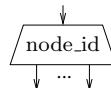

| 8.7  | The Esterel to GRC translation interface . . . . .                                             | 158 |

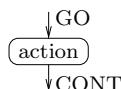

| 8.8  | The translation of <b>pause</b> . . . . .                                                      | 159 |

| 8.9  | The translation of <b>nothing</b> and <b>emit S</b> . . . . .                                  | 160 |

| 8.10 | The translation of <b>loop <i>q</i> end</b> . . . . .                                          | 160 |

| 8.11 | The translation of <b><i>q</i> ; <i>r</i></b> . . . . .                                        | 161 |

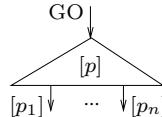

| 8.12 | The translation of <b><i>q</i>    <i>r</i></b> . . . . .                                       | 162 |

| 8.13 | The translation of <b>signal S in <i>q</i> end</b> . . . . .                                   | 162 |

| 8.14 | The translation of the test primitives . . . . .                                               | 163 |

| 8.15 | The translation of <b>suspend <i>q</i> when <i>expr</i></b> . . . . .                          | 164 |

| 8.16 | The translation of <b>exit <i>T</i>(<i>i</i>)</b> . . . . .                                    | 164 |

| 8.17 | The translation of <b>trap <i>T</i> in <i>q</i> end</b> . . . . .                              | 165 |

|       |                                                                          |     |

|-------|--------------------------------------------------------------------------|-----|

| 8.18  | The translation of variable assignment . . . . .                         | 165 |

| 8.19  | The translation of variable declarations . . . . .                       | 166 |

| 8.20  | The global translation context . . . . .                                 | 166 |

| 8.21  | Circuit counterpart for the <b>Test</b> node . . . . .                   | 167 |

| 8.22  | Circuit counterpart for the <b>Switch</b> node . . . . .                 | 168 |

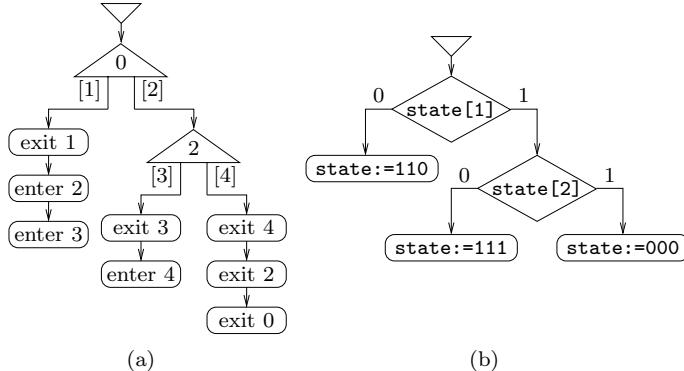

| 8.23  | Tagged tree for <b>MainExample</b> . . . . .                             | 173 |

| 8.24  | Simplified graph for <b>MainExample</b> . . . . .                        | 177 |

| 9.1   | A GRC-level cycle resolved at the circuit level . . . . .                | 181 |

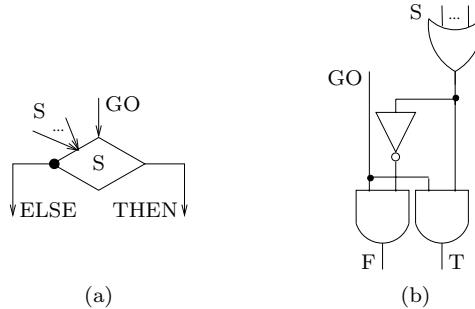

| 9.2   | Simplified translation patterns for <b>present</b> . . . . .             | 182 |

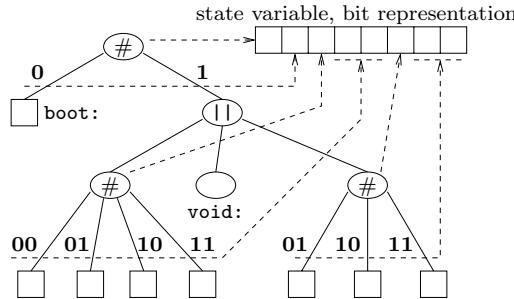

| 9.3   | Example of synchronizer refinement . . . . .                             | 184 |

| 9.4   | Bit allocation for our first small example . . . . .                     | 186 |

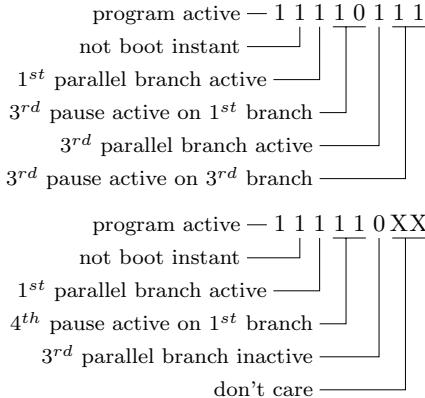

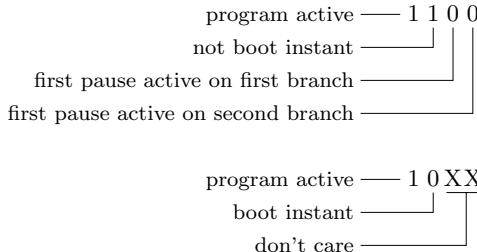

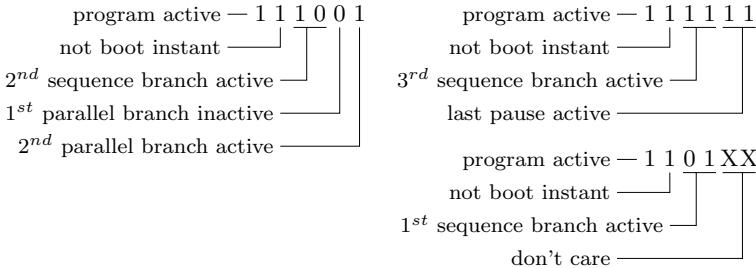

| 9.5   | State encoding examples for our first small example . . . . .            | 187 |

| 9.6   | Bit allocation for <b>MainExample</b> . . . . .                          | 188 |

| 9.7   | State encoding examples for <b>MainExample</b> . . . . .                 | 188 |

| 9.8   | Bit allocation for the third small example . . . . .                     | 189 |

| 9.9   | State encoding examples for the third small example . . . . .            | 189 |

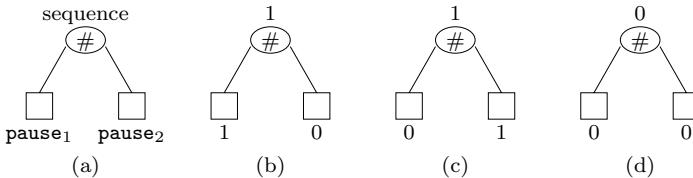

| 9.10  | Bit allocation for <b>pause ; pause</b> . . . . .                        | 191 |

| 9.11  | Possible states for <b>pause ; pause</b> and their encoding . . . . .    | 191 |

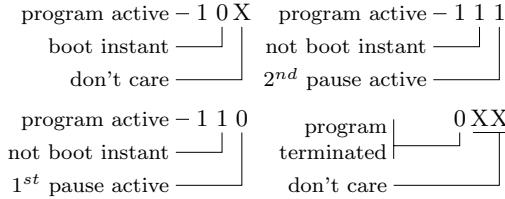

| 9.12  | Flowgraph transformation due to state encoding . . . . .                 | 192 |

| 9.13  | A partition of the selection tree of <b>MainExample</b> . . . . .        | 193 |

| 9.14  | Code generated from the flowgraph of Figure 8.24 . . . . .               | 194 |

| 9.15  | The GRC of the cyclic example . . . . .                                  | 196 |

| 9.16  | The SCC at GRC and circuit level . . . . .                               | 196 |

| 9.17  | Globally acyclic graph for our cyclic example . . . . .                  | 197 |

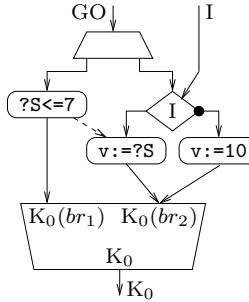

| 10.1  | An Esterel model of a shared resource . . . . .                          | 205 |

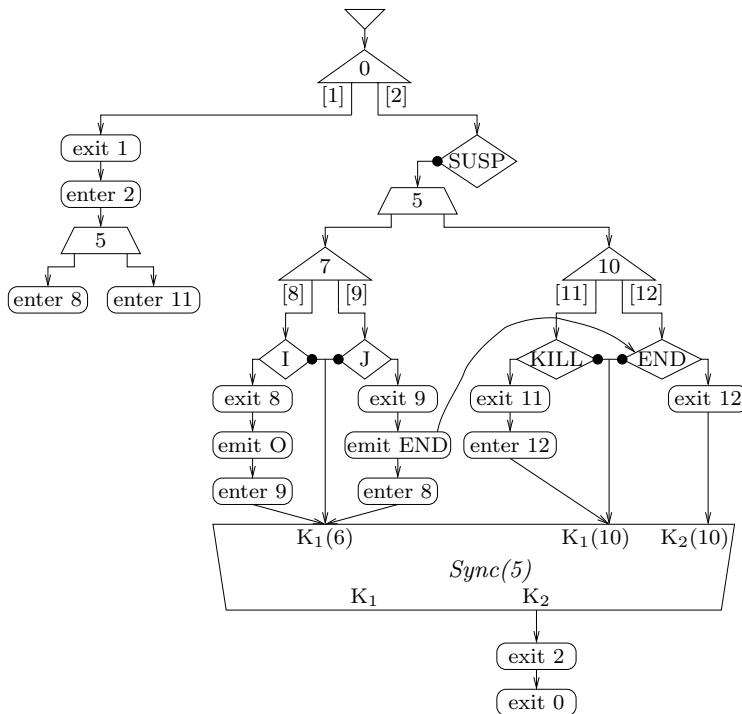

| 10.2  | The GRC <sub>CEC</sub> for the program in Figure 10.1 . . . . .          | 206 |

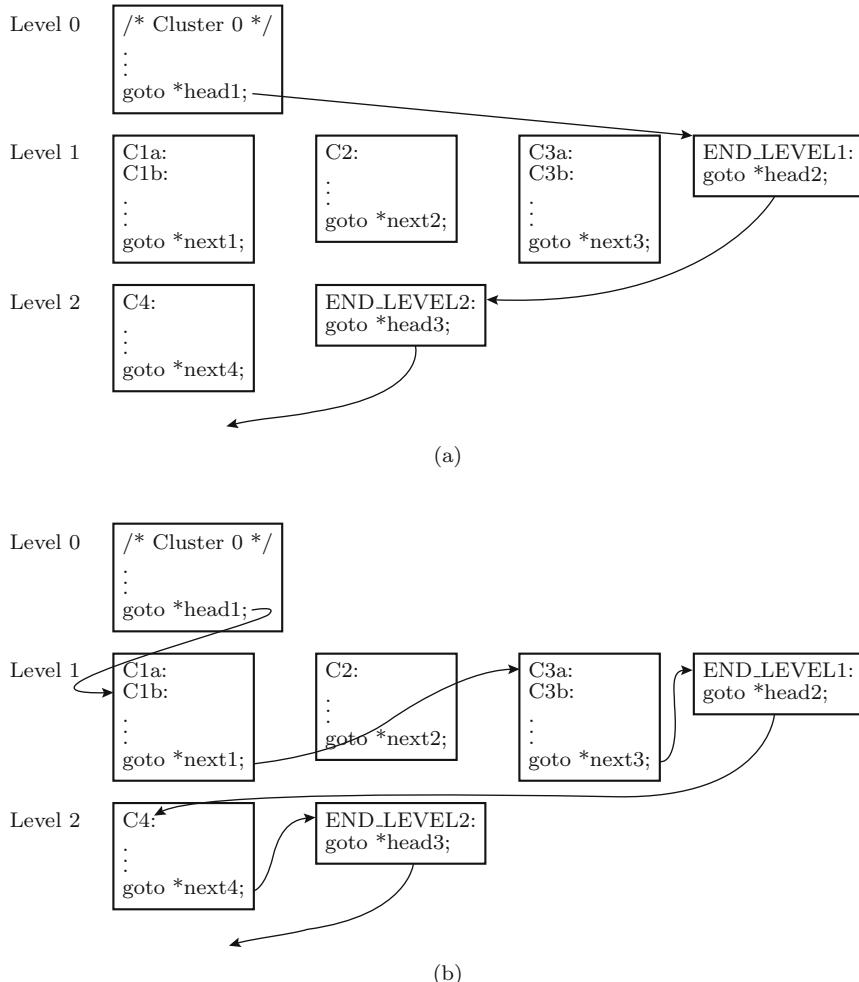

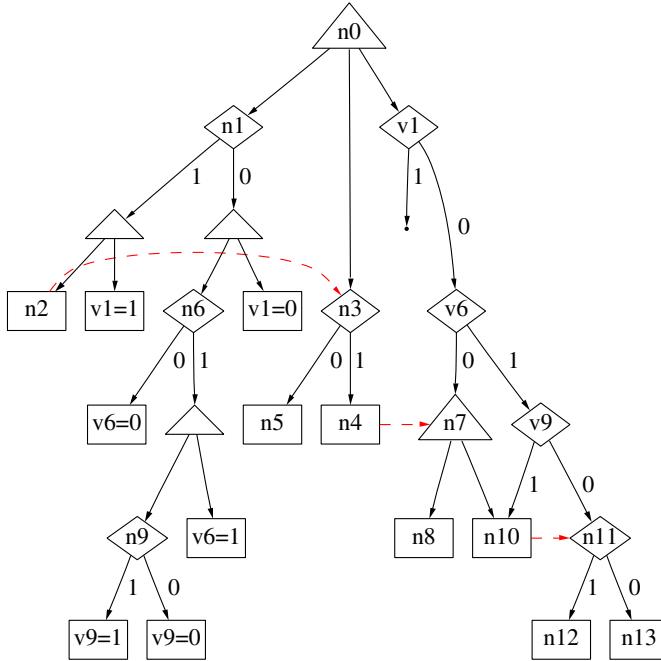

| 10.3  | The control-flow graph from Figure 10.2<br>divided into blocks . . . . . | 209 |

| 10.4  | The code CEC generates for part of the graph<br>in Figure 10.3 . . . . . | 210 |

| 10.5  | Cluster code and the linked list pointers . . . . .                      | 213 |

| 10.6  | The clustering algorithm . . . . .                                       | 214 |

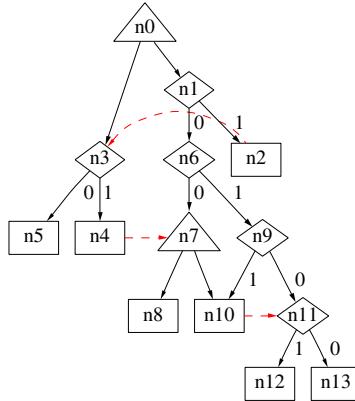

| 10.7  | A program dependence graph requiring interleaving . . . . .              | 217 |

| 10.8  | The Main procedure . . . . .                                             | 219 |

| 10.9  | Successor Priority Assignment . . . . .                                  | 220 |

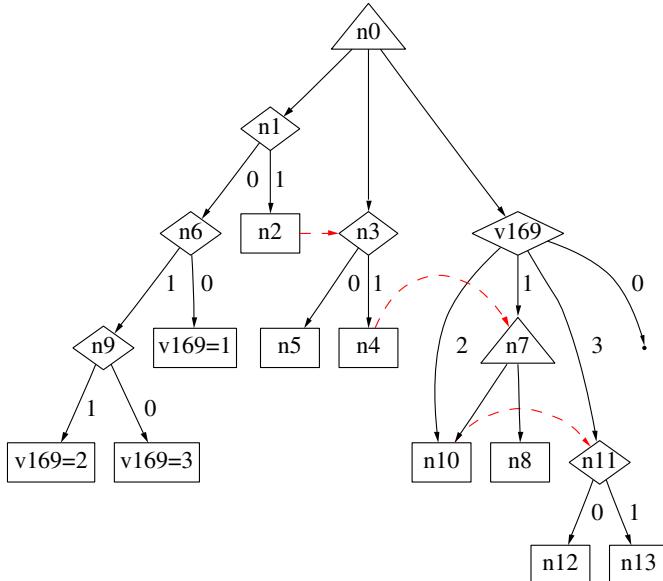

| 10.10 | The Scheduling Procedure . . . . .                                       | 221 |

| 10.11 | The Restructure procedure . . . . .                                      | 221 |

| 10.12 | The DuplicationSet function . . . . .                                    | 222 |

| 10.13 | The DuplicateNode procedure . . . . .                                    | 223 |

| 10.14 | The ConnectPredecessors procedure . . . . .                              | 223 |

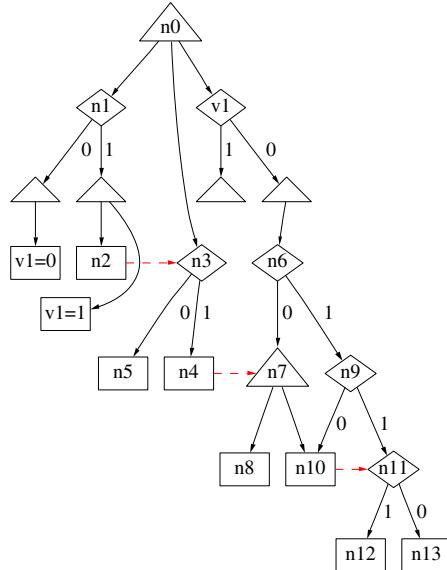

| 10.15 | The restructured PDG from Figure 10.7 . . . . .                          | 226 |

| 10.16 | A complex example . . . . .                                              | 227 |

| 10.17 | The reconstructed PDG from Figure 10.7 . . . . .                         | 229 |

|       |                                                                         |     |

|-------|-------------------------------------------------------------------------|-----|

| 10.18 | The PDG of Figure 10.17 after guard variable fusion . . . . .           | 231 |

| 10.19 | The successor ordering procedure . . . . .                              | 232 |

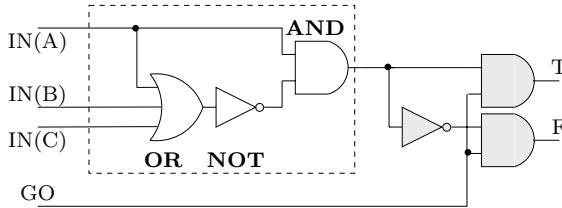

| A.1   | Test sub-circuit for the expression “C and not (A or B or C)” . . . . . | 237 |

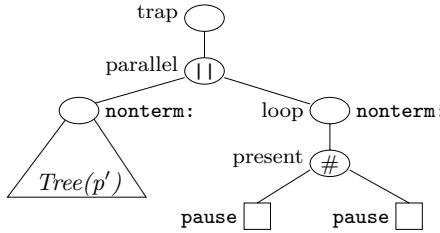

| A.2   | Tagged selection tree for the expansion of <code>pre</code> . . . . .   | 239 |

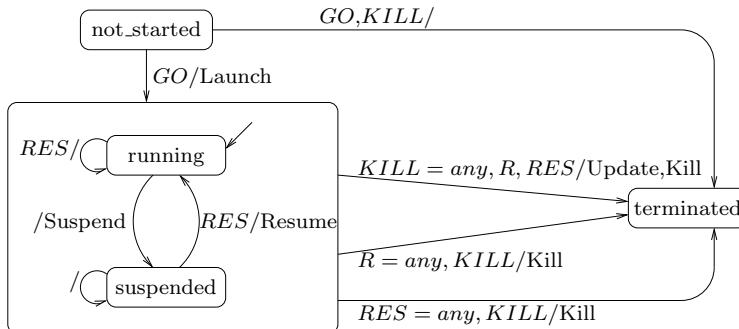

| A.3   | The life cycle of a task . . . . .                                      | 249 |

# Tables

|      |                                                           |     |

|------|-----------------------------------------------------------|-----|

| 2.1  | The primitives of Pure Esterel . . . . .                  | 22  |

| 8.1  | Parallel branch status redundancy statistics . . . . .    | 172 |

| 9.1  | State encoding results on some typical examples . . . . . | 190 |

| 9.2  | Code speed . . . . .                                      | 202 |

| 9.3  | Code size . . . . .                                       | 202 |

| 10.1 | Experimental results for the dynamic approach . . . . .   | 230 |

| 10.2 | Statistics for the examples . . . . .                     | 230 |

| 10.3 | Experimental Results for the PDG-based approach . . . . . | 233 |

## Part I

# The Esterel Language

# Introduction to Esterel

Esterel is a synchronous programming language tailored for the development of control-dominated embedded reactive applications in both hardware and software. In this chapter, we explain what this means. We explain what a reactive system is, introduce the key concepts of synchronous reactive system programming, and give a short overview of the Esterel language and framework.

## 1.1 Reactive Systems

*Reactive systems*, defined in the 1980s [41, 40, 39], are computer systems that continuously react to input events from their environment by producing appropriate output events in a timely manner. They differ from *transformational systems*, which emphasize data computation instead of system-environment interaction; and from *interactive systems*, which react to environment requests at their own rate instead of at the rate required by the environment. For instance, an airplane autopilot is reactive while a web browser is interactive. Classical programming and verification techniques were originally geared to transformational systems and later extended to interactive systems. Unfortunately, they turn out to be inadequate for reactive systems. It is just too much of a stretch.

To address this problem, several groups in the 1980s developed specific techniques geared to the design and verification of reactive systems. One technique, the synchronous approach, is based on mathematical semantics and has generated a variety of languages and compilers that are now widely used in applications ranging from safety-critical embedded systems in avionics, automotive, and railways to electronic circuit design.

Reactive systems have two essential traits: concurrency and determinism. They are invariably composed of concurrent components that react concurrently to their environment. While interactive systems may also have this structure, there is a fundamental philosophical difference between the two:

The concurrent pieces in a reactive system are mostly concerned with cooperating and communicating in a deterministic way. The concurrency in an interactive system usually involves much more competition over shared resources, which is resolved in a nondeterministic way. Such nondeterminism renders classical concurrent programming techniques such as the shared memory and locks model inadequate for reactive systems.

The synchronous approach to reactive systems, embodied in the Esterel, Lustre, and Signal languages [39, 3, 4, 58] is among the solutions that have been proposed for the development of reactive systems. This concurrent model provides determinism and convenient mechanisms for cooperation. Furthermore, its crisp formal semantics simplifies verification. The Esterel synchronous language is the focus of this book.

Reactive systems are often embedded in objects that interact with the physical world, e.g., airplanes or automotive controllers, and their correct function is very often safety-critical. A system crash in an airplane is a much more literal problem than one on a desktop computer. Thus, validation and certification of reactive systems is an absolute must. Experience has shown that the synchronous approach can greatly improve the verification process, in particular by being well-suited to formal verification.

Reactive systems are also made of heterogeneous hardware and software components. A further advantage of the the synchronous approach, and of Esterel in particular, is that it applies equally to hardware and software. The Esterel V7 production compiler generates C/C++/SystemC code as well as VHDL/Verilog code with exactly the same behavior. The same verification algorithms apply to both. This does not solve the issue of hardware/software partitioning, but is an enabler for it: when writing a module, one does not need to decide upfront whether it will be implemented in hardware or software. One can use a unique programming style instead of two widely different ones (e.g., C and register-transfer-level Verilog).

## 1.2 The Synchronous Hypothesis

The synchronous hypothesis, the fundamental principle on which Esterel is based, states that a system reacts to environmental events in no time. Furthermore, communication among system components is also done instantaneously. The synchronous hypothesis thus separates the notion of physical time, which arises from the physics of the environment, from the execution time of the system, which is largely a side-effect of how it is implemented. An Esterel specification only refers to physical time, and assumes implementation time is exactly zero. This is a brutal but effective way to separate concerns, simplify the semantics, and to reconcile concurrency and determinism. It is the interference between physical and implementation time that makes classical asynchronous concurrent programs nondeterministic, hard to analyze, and difficult to write. For more on this philosophy, see Berry [9]. When

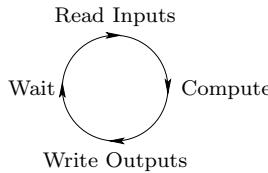

Figure 1.1: The execution cycle of the synchronous model

programming in a synchronous way, one concentrates on the functionality, postponing implementation details. Of course, one must check that the synchronous hypothesis is “correctly approximated” by the final implementation. We later show how this can be done.

Esterel relies on another fundamental principle: the discretization of time. The synchronous hypothesis as stated above applies equally well to continuous- and discrete-time systems. However, computer applications are most often based on discrete time. The discretization of time is ubiquitous in control and signal theory. It also applies to newer systems such as man-machine interfaces (e.g., cockpit displays), where the environment sends discrete events. Therefore, Esterel adopts a discrete model of time, where programs only react at discrete instants. At each reaction instant, a program reads its inputs, computes the outputs, and sends them to the environment, conceptually in no time.

### 1.3 Implementation Issues

Esterel is not just a specification language; it is meant to be implemented and used in actual systems. The object of this book is to present practical techniques for implementing theoretical zero-delay behavior, which is not obvious since any real computation takes time. The central idea is to approximate zero-delay reactions using the cycle-based model of computation pictured in Figure 1.1.

At any instant where the program should react, we perform a computation cycle: we sample the input, compute the output, and deliver it to the environment. Each of these operations takes some time. If the cycle computation is over before the next cycle should start, we have avoided input/computation interference exactly as required by the zero-delay model, and we can consider the computation as correct in practice.

Think of people talking to each other in a room. They can (and do) neglect the speed of sound, because the room is small enough to make communication practically instantaneous. By analogy, an Esterel implementation has two goals.

**Speed.** Efficiently fit the “people” inside the “room.” That is, schedule the

various computing elements of the system so that they perform their computations and communications fast.

**Timing predictability.** Make sure that the resulting system behaves like a “small room” where the communication speed can be neglected, so that reactions are predictable, and meet their timing constraints.

This book concentrates on speed issues; we do not address the important issue of predictability, which involves many non-trivial techniques such as worst-case execution time analysis (WCET), which can be performed using abstract interpretation and precise processor models. See for instance [42] for WCET analysis applicable to synchronous programs.

To respect the semantics, the execution of a cycle should be atomic. In an implementation, the environment should not be allowed to change during the cycle, and cycles should not overlap. Therefore, computations are performed on a frozen input snapshot taken during the input phase.

## 1.4 Causality

Causality among events is the key link between the zero delay model and a practical implementation. Roughly, an abstract event A causes an event B if the occurrence or non-occurrence of A determines the occurrence or non-occurrence of B. In the zero-delay model, events are determined by causal chain reactions among concurrent system components. In implementations, events are determined by sequences of computations that implement such causal reaction chains. Thus, compiling Esterel amounts to finding a way to implement causality chains with instruction sequences. This can be done in many ways, leading to the variety of implementation techniques studied here.

Unfortunately, not all synchronous programs are automatically causal. For instance, the logical contradiction “emit A if and only if A is not emitted” can be expressed as a synchronous program that is syntactically correct but has no synchronous semantics (note the similarity with the classical liar paradox). The theory of causal and non-causal programs is not a simple one; it is the subject of a separate book [7]. In practice, non-causal programs should be rejected by compilers with appropriate error messages. Most compilers take a conservative approach, sometimes rejecting projects that could be viewed as causal, but the conservative approach appears adequate in practice. In this book, we formally describe causality requirements and discuss which rejection algorithms are suitable for practical applications.

## 1.5 Related work

Esterel is only one of the synchronous languages; Argos [49], Lustre/Scade [38, 22], Signal [46], SyncCharts [1], and Quartz [62] also take the synchronous approach and benefit from the simplicity of the synchronous hypothesis. A

key difference among these languages is the class of applications they target. Among these others, SCADE (“Safety-Critical Application Development Environment”), is perhaps the most successful. It is a graphical version of Lustre dedicated to safety-critical embedded software systems, and especially to certified avionics systems: flight control, cockpit display, engine control, brake control, etc. The SCADE compiler itself has been certified by avionics authorities, which greatly simplifies the laborious process of certifying the avionics software [24]. The simplicity and rigor of synchronous semantics and compiling techniques is the key to such a compiler certification.

Similar abstractions have lead to the development of quasi-synchronous formalisms such as Statecharts [40] or the synthesizable subset of the hardware description languages Verilog [44] and VHDL [51].

In compiler technology, the static single-assignment (SSA) intermediate representation [23, 45] requires that each variable has a single, non-recursive definition, so that it has a unique value throughout the execution. This is similar to synchronous causality, and facilitates various analysis and code generation techniques.

Synchrony is also commonly used for hardware design. In the Register Transfer Level (RTL) model, one describes circuits using gates that conceptually compute in zero time. After mapping the gates to hardware components, placing these components in space and routing the interconnect wires, one can statically analyze the timing of the circuit, i.e., compute the maximal time it takes for signals to stabilize. Then, the circuit behaves as in the zero-delay model if the period of the circuit clock is larger than the maximal stabilization time.\* Unfortunately, although it is implicit in the definition of the synthesizable subset of VHDL [51], the zero-delay hardware model and its precise relation with timed models have not yet been formalized; the semantics of hardware description languages such as Verilog or VHDL remain informal.

## 1.6 A First Esterel Example

**ABRO** is perhaps the simplest interesting Esterel program. This program has three inputs, **A**, **B**, and **R**, and one output, **O**. It waits for the last of **A** and **B** to occur and then immediately emits **O**. The entire process restarts when **R** occurs. If **R** occurs at the same time as **A** or **B**, the reset takes priority. The Esterel code is as follows.

```

module ABRO:

input A, B, R ;

output O ;

loop

```

---

\*If we refer to our “small room” analogy, such static timing analysis determines the room size that allows us to neglect communication time.

| Instant | Inputs | Outputs | Comment                |

|---------|--------|---------|------------------------|

| 0       |        |         |                        |

| 1       | A,B    | O       |                        |

| 2       | A      |         | Signal A ignored       |

| 3       | R      |         | Reset                  |

| 4       | A      |         | Still waiting for B    |

| 5       | B      | O       |                        |

| 6       | A,B,R  |         | Reset, A and B ignored |

Figure 1.2: A possible execution trace for ABRO

```

[ await A || await B ];

emit 0

each R

end module

```

This simple example features the four main ingredients of Esterel: signalling, concurrency, and preemption. It is actually a pattern commonly found in reactive designs: think of **ABRO** as a memory write controller, with **A** the address, **B** the value, **0** the write command, an **R** a synchronous reset.

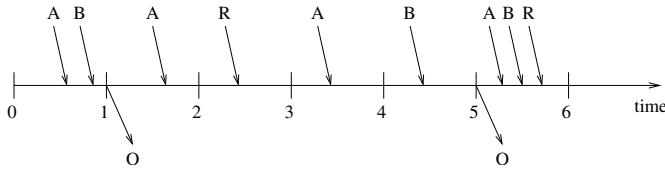

Figure 1.2 presents a possible execution of **ABRO**. This trace is an indexed sequence of execution instants. At each instant, the input event tells which input signals have arrived, and the reaction determines whether to emit the output signal **0**. Note that input signals can arrive simultaneously.

At instant 0, no input arrives and no output is produced. The control enters the program, forks at the parallel statement, and is blocked at the concurrent **await** statements. At instant 1, the arrival of **A** and **B** makes both **await** statements terminate. Then, their parallel composition immediately terminates and passes control to the next statement in sequence: the statement **emit 0**. This is immediately executed and outputs **0**. Then, control blocks, awaiting **R**. At instant 2, the input **A** is simply ignored because nothing is observing it. At instant 3, signal **R** arrives, the loop body is restarted, and **ABRO** waits again for **A** and **B**. When **A** arrives at instant 4, “**await A**” terminates. The parallel statement does not yet terminate; it is waiting for its right branch to terminate. This occurs at instant 5 because **B** arrives. **0** is immediately emitted. At instant 6, **A**, **B**, and **R** arrive at the same time. Then the “**loop...each R**” statement preempts its body and performs the reset, ignoring **A** and **B**.

## 1.7 Causality Cycles

Unfortunately, it appears the simplicity of synchrony comes at the price of the thorny problem of *causality cycles*. Reactions are computed by chains of

instantaneous elementary actions, such as signal reception, statement termination, parallel synchronization, and signal emission. Control transmission makes these actions belong to causal chains. The problem is that the syntax of Esterel makes it possible to write cyclic causal chains that have no obvious meaning. For instance, it is easy to introduce a causality cycle to to ABRO example:

```

module Cycle :

input I;

output O;

signal A in

run ABRO

||

await O; emit A

end signal

end module

```

In `Cycle`, we remove `A` from inputs and declare it as a scoped local signal. The `run` statements instantiates `ABRO`, automatically connecting its inputs and outputs by name. The second parallel branch waits for `O` from `ABRO` to instantaneously feed `A` back to `ABRO`. The causality cycle is as follows: within `ABRO`, emission of `O` depends on reception of `A`; within the second parallel branch, emission of `A` depends on reception of `O`; both dependencies are instantaneous. The program makes no sense and should be rejected. The classical solution to avoiding causality cycles is to cut any instantaneous cycle by inserting a delay. This condition is indeed sufficient and useful in practice, but we will also study much finer conditions that have also proven useful. Formal semantics are essential to understanding the causality problem and for developing algorithms to reject non-causal programs with error messages that point to the root cause of the problem.

## 1.8 Code Generation

Three main techniques have been developed to translate Esterel programs into hardware or software: expansion to explicit state machines, translation into circuits, and direct software generation. In this book we shall focus on the generation of software. We shall not cover distributed software generation, studied for instance by Girault et al. [19], and we will address issues related to hardware generation only when they are relevant to generating software.

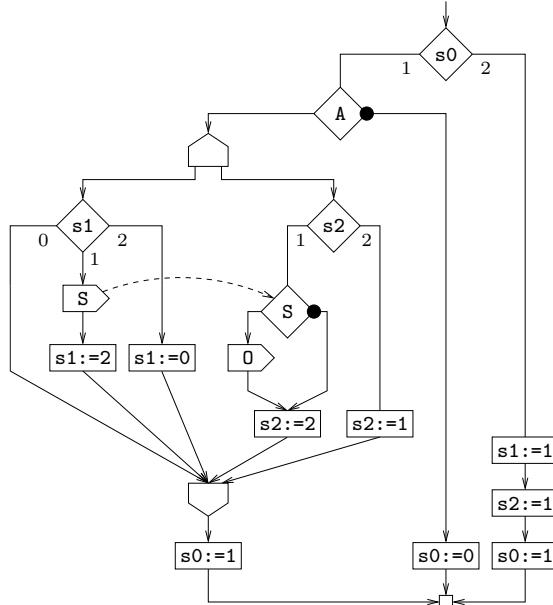

### 1.8.1 Translation to Explicit State Machines

The first INRIA compilers Esterel V2 (1985) and Esterel V3 (1988) translated Esterel programs into explicit finite automata, specifically Mealy state machines. These compilers explicitly enumerate all the reachable states and

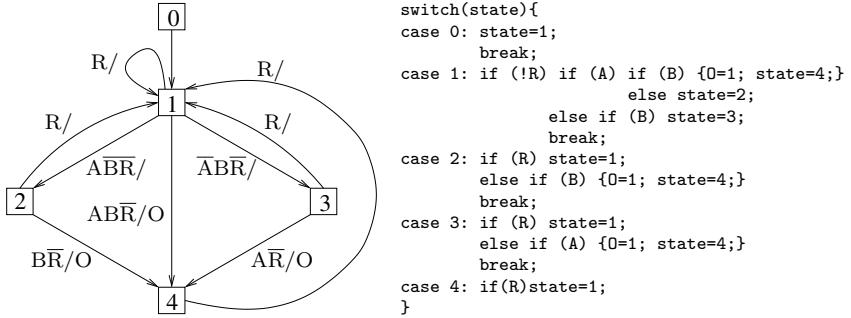

Figure 1.3: The automaton and explicit FSM code for the ABRO example

transitions of a program. This state machine is then encoded into C. We call this form of code (*explicit*) *FSM code*.

Figure 1.3 shows the state graph of ABRO along with its implementation in C. Notice the number of times A, B, R, and O appear in the state graph. With its constructs for concurrency and preemption, Esterel can be much more succinct than explicit finite automata for the same behavior. This is an essential advantage for clean and maintainable specifications.

The FSM code is very fast, since only the active code is evaluated in each instant. However, FSM translation is subject to exponential state space explosion.\* The method can only be applied to small- and medium-sized programs.

Esterel V2 is based on Brzozowski’s residual technique [17] to translate regular expressions into automata. Transitions are computed using a direct interpretation of the Esterel semantic rules, given in Plotkin’s Structural Operational Semantics (SOS) style [5], and states were represented by textual Esterel programs. Causality analysis was simplistic and limited. Esterel V3 uses a more elaborate operational semantics due to Gonthier and Berry [10, 35], a much finer causality analysis that accepts many more programs, and an efficient bit-vector representation of states. Compilation is orders of magnitude more efficient in time and space than with Esterel V2, but the generated code is about the same and still subject to state explosion.

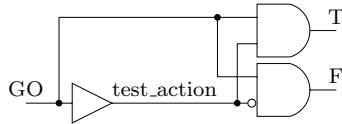

### 1.8.2 Translation to Circuits

The INRIA Esterel V4–V6 compilers (1992–1999) and the Esterel Studio commercial compiler use a very different technique: direct translation of an Esterel program into a digital circuit, developed by Berry [6, 7].

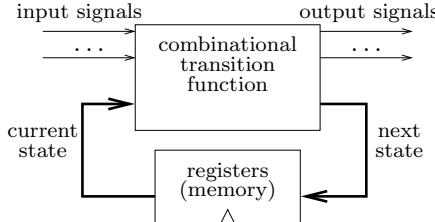

Figure 1.4 shows the standard form of a synchronous circuit. It is divided

\*The FSM for ABRO has 5 states. Adding “`await C`” in the parallel construct produces 9 states. Further adding “`await D`” produces 17 states. In general, waiting for  $n$  signals in an ABRO-like program leads to an FSM with  $2^n + 1$  states.

Figure 1.4: The standard representation of sequential circuits

```

RESET = R & !BOOT

A.TEST_TRIGGER = A.REG_OUT & !RESET

A.TEST_THEN = A.TEST_TRIGGER & A

A.TEST_ELSE = A.TEST_TRIGGER & !A

A.TERMINATED = A.TEST_THEN | ! A.TEST_TRIGGER

A.REG_IN = BOOT | RESET | A.TEST_ELSE

B.TEST_TRIGGER = B.REG_OUT & !RESET

B.TEST_THEN = B.TEST_TRIGGER & B

B.TEST_ELSE = B.TEST_TRIGGER & !B

B.TERMINATED = B.TEST_THEN | ! B.TEST_TRIGGER

B.REG_IN = BOOT | RESET | B.TEST_ELSE

ACTIVE = A.TEST_TRIGGER | B.TEST_TRIGGER

O = A.TERMINATED & B.TERMINATED & ACTIVE

```

Figure 1.5: Circuit code for ABRO (the reaction function)

into combinational logic, which computes the outputs and new states from the inputs and current state, and sequential logic (registers), which stores the state. A global clock ticks off the instants by triggering state updates. The circuit for ABRO is pictured in Figure 6.1, page 105.

The circuit translation technique scales to large programs since state is held in registers and encoded compactly, hence eliminating the exponential code-size explosion.

The circuit can be translated into VHDL or Verilog for implementation in hardware. After applying sequential optimization techniques developed by Toma et al. [69, 63] to improve the size and speed of the circuit, one gets very efficient circuits that are often better than manually designed ones. Sequential optimization does not scale to big programs, but can be applied on a per-module basis and produce reasonable results.

Software code is generated by topologically sorting the circuit gates and translating their function into C (or C-based languages such as C++ and SystemC), as pictured in Figure 1.5. We call this form of generated code *circuit code*. Compared to automaton code, circuit code is slower because in every instant it executes every equation, even those corresponding to inactive states.

The causality of the generated circuit is now well-studied. That the

```

ABRO_start() { //called in the initial simulation instant

await_A.active=true ; await_B.active=true ;

}

ABRO_resume() { //called when ABRO is resumed

if (R) { ABRO_start() ; }

else {

if (await_A.active || await_B.active) {

if (await_A.active && A) { await_A.active=false ; }

if (await_B.active && B) { await_B.active=false ; }

if ((!await_A.active)&&(!await_B.active)) { emit 0 ; }

}

}

}

```

Figure 1.6: Control-flow (pseudo-)code for ABRO

combinational logic be acyclic is the simplest criterion, but such cyclic circuits may also be causal if every cycle is effectively broken at each instant by input or current state values. Cyclic circuits have been studied by Malik [48] and Berry and Shiple [65]. The latter showed that *constructive logic* can be used to model circuits with cycles. Such constructive analysis of circuits was later extended to the *constructive semantics* of the Esterel language itself [7] and implemented in the Esterel V5 compiler. The constructive semantics of Esterel is the subject of the second part of this book.

### 1.8.3 Direct Compilation to C Code

To improve upon circuit code, Edwards [26, 27], Closse and Weil [21, 72], and Potop-Butucaru [57, 56] developed new compilers based on control flow graph construction and optimization. These techniques will be explained in detail in this book. The commercial Esterel V7 commercial compiler embodies a C code generator based on Potop-Butucaru’s technique.

The main idea in these compilers is to generate C code that compute only the active part of the Esterel program in each reaction, as does FSM code, while representing the state in a compact bit vector form, as done in circuit code. We call this form of generated code *control-flow code*. Figure 1.6 shows control-flow code similar to what Edwards’s and Potop-Butucaru’s compilers produce.

## 1.9 Executing the Generated Code

The code generated from an Esterel synchronous program is generally executed in a standard sequential framework where events come asynchronously. Since its execution does take time, running the code in a way that respects the synchronous requires some care. It basically requires the definition and implementation of an external *execution shell* that gather inputs from the

Figure 1.7: A possible run of ABRO in an asynchronous environment

environment, builds logical input events for the reaction functions, and performs the actual output actions. To date, all Esterel code generators have relied on a simple execution shell structure that has remained practically unchanged since its initial definition for Esterel V2.

The generated code is organized around a *reaction function* that effectively computes the transition function of the underlying FSM. The reaction function is called at each logical instant. Conceptually, it takes environmental inputs and the current state as parameters and produces outputs and the next state. The actual implementation is a bit more detailed; see Appendix C.

The execution shell is responsible for repeatedly triggering the reaction function. There are a variety of choices for how to do this. The reaction function may be called periodically, typical in automatic control; when any input signal arrives, an event-driven style; when a particular signal arrives, in which case that signal acts as a clock; or immediately after the previous reaction has been computed. The only restriction imposed by the synchrony hypothesis is that the computations of successive reactions do not overlap and that the state of the inputs does not appear to change during a reaction. Checking that reactions do not overlap in the periodic case can be done through worst-case execution time (WCET) analysis.

One way to keep the inputs constant is for the execution shell to buffer inputs, effectively synchronizing them. One simple strategy is to freeze the input buffers when the reaction function is called and start recording input events again when it returns. If the implementation respects the synchrony hypothesis, these may be simple single-place buffers that simply record whether an event has been observed since the last instant. Figure 1.7 shows a possible run of a software implementation of ABRO that corresponds to the synchronous trace of Figure 1.2. The reaction function is called at the numbered times. Of course, other execution schemes are possible.

### 1.9.1 Existing Solutions

The execution shell assumed by Esterel compilers has remained practically unchanged from the first compilers. Its API, called the *host language interface* is a *de facto* standard shared by the different existing compilers. We present it in Appendix C.

The main research effort in Esterel compilation has focused on the synthesis of reaction functions. The goal is a practical compilation process that generates correct, fast, and compact reaction functions for all Esterel programs. In practice, different compilation schemes have different advantages and disadvantages.

More recent techniques attempt to combine the advantages of previous ones. They generate code that simulate the reactive features of the language at run-time. We shall call such a target code *control-flow code* of the Esterel description. The control-flow code is small—comparable in size to the circuit—and evaluates only active statements in an instant—as the FSM code does. The difficulty comes in scheduling program fragments that respect the language semantics, more specifically the causality relations. Code to ensure the correct activation of such fragments is a significant part of the generated code.

As the example of Figure 1.6 shows, efficient sequential code is obtained by *statically scheduling* the reaction operations. The results are excellent: the code is smaller than that from the circuit technique and approaches the speed of explicit FSM code. The drawback is that this technique cannot handle all correct Esterel programs. Specifically, to statically schedule an Esterel program, the control- and data-flow structure of the program must be statically acyclic, a stronger restriction than necessary. In particular, the order may depend on the program state and inputs, meaning completely static scheduling is impossible. More importantly, each translation technique defines “acyclicity” of the control- and data-flow structure in a slightly different way and optimizations may add or remove cycles. Thus, the class of accepted programs depends on the chosen compiler and optimization level. We shall give a detailed overview of existing control-flow code generators in Chapter 7.

# 2

## The Esterel Language

Esterel is an imperative synchronous language for the programming of reactive applications. Developed by a team lead by Gérard Berry, its first version was defined more than twenty years ago [12]. This book describes version 5 (V5) of the language [7, 13]. The current commercial version of Esterel is 7 [29]—a broad syntactic extension of V5 with little change to its semantics.

This chapter is devoted to an intuitive presentation of the language that omits details and certain constructs. We cover these later in the reference manual in Appendix B. Furthermore, we defer a detailed discussion of the Esterel semantics to the second part of the book. Instead, we concentrate on the description of the mechanisms that allow the definition of high-level reactive behaviors.

The presentation is roughly divided in two: The first part focuses on the expressive power of the language; the second covers practical issues such as modular development and interfacing with the real world. The first part starts with an overview of the language constructs, followed by the definition of the *primitive* statements of Esterel. Next, we show examples to familiarize the reader with the notions of *cyclicity*, *schizophrenia*, and *reincarnation*, which present key challenges in the code generation process.

The second part of the chapter defines the notions of *host language* and *module* and defines the general structure of an Esterel specification.

### 2.1 Syntax and Naïve Semantic Principles

An Esterel program consists of a declaration header followed by a reactive body statement. The header defines the *interface* of the program: input and output signals, data types, variables, and external data manipulation routines. Esterel offers a wide variety of statements that may appear in the imperative body. Among them are the primitive language constructs, also called *kernel statements*, on which the language semantics is defined. The

rest of the statements are syntactic sugar derived from the kernel statements, which prove convenient for the development of practical applications.

We now take a short tour of the language features. We have divided our presentation into several steps, each introducing a certain class of language constructs. The complex issues are clarified at each step through small examples.

### *Control flow*

Esterel provides classical control-flow constructs. It has a no-operation statement (**nothing**), parallel ( $p \parallel q$ ) and sequential ( $p ; q$ ) composition, and iterative sequential loop (**loop**  $p$  **end**). Once executed, a parallel statement terminates when all of its branches have terminated. A loop runs forever unless terminated by an explicit exit or preempted by its environment. The body of a loop is not allowed to terminate instantly when first executed to prevent unbounded computation and guarantee the completion of synchronous reactions. Compilers reject programs that contain such loops.

The trap statement “**trap**  $T$  in  $p$  **end**” defines an instantaneous exit point for its body. The termination of the trap statement is triggered by “**exit**  $T$ ” statements, where  $T$  is a trap label. If “**exit**  $T$ ” executes inside  $p$ , the entire trap statement terminates immediately. Notice that we use the specific “trap” word instead of the better known “exception” word used in some languages. We think that “exception” is much less precise, since it also covers arithmetic exceptions such as zero-divide that are not covered by trap.

Classical sequential variables can be defined in Esterel as follows.

```

var v := expr : type in p end

```

Such variables can be assigned

```

v := expr

```

and tested

```

if cond then p else q end

```

Here,  $v$  is a variable name,  $expr$  is an expression, and  $cond$  is a Boolean expression involving variables, such as “ $v < 10$ .” The variable declaration statement defines the sequential variable  $v$  of type  $type$ . The scope of  $v$  is the statement  $p$ . When the declaration statement is executed, the initializing expression is computed and the result is assigned to the variable as initial value before control is passed to the body  $p$ .

Variable initialization is required to ensure the macrostep determinism of the language, but it can be skipped to simplify the code when no initialization is needed (i.e., when an assignment is always executed before the variable is read).

Concurrent access to sequential variables is restricted syntactically. When one branch of a parallel statement assigns a sequential variable, none of the

other branches is allowed to read or assign the same variable. Esterel thus prohibits both write-write and read-write conflicts. For example, Esterel compilers reject the following compound statements.

```

w := 10 || w := 11

v := 10 || w := v

if u = 0 then v := 10 end || if u <> 0 then w := v end

```

The first example contains a write-write conflict. A read-write race is present in the second. The third example emphasizes the syntactic nature of the restriction enforced by compilers. While the guards prevent the read and write actions from occurring simultaneously, the fragment is still rejected.

#### *Division of behavior in reactions*