# Verification Methodology Manual for SystemVerilog

**Janick Bergeron**

**Eduard Cerny**

**Alan Hunter**

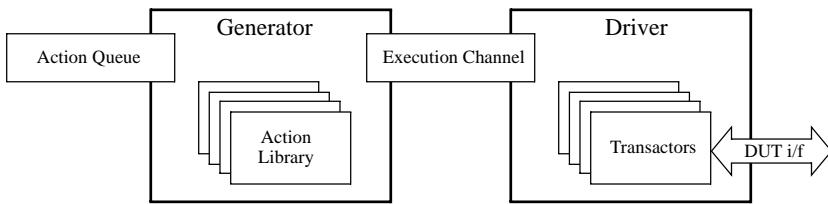

**Andrew Nightingale**

---

---

# **Verification Methodology Manual for SystemVerilog**

---

---

# **Verification Methodology Manual for SystemVerilog**

by

Janick Bergeron

Eduard Cerny

Alan Hunter

Andrew Nightingale

Springer

Janick Bergeron, *Synopsys, Inc.*

Andrew Nightingale, *ARM, Ltd.*

Eduard Cerny, *Synopsys, Inc.*

Alan Hunter, *ARM, Ltd.*

Verification methodology manual for SystemVerilog / by Janick Bergeron ... [et al.].

p. cm.

Includes bibliographical references and index.

ISBN-13: 978-0-387-25538-5 (alk. paper)

ISBN-10: 0-387-25538-9 (alk. paper)

ISBN-10: 0-387-25556-7 (e-book)

1. Verilog (Computer hardware description language) 2. Integrated circuits--Verification.

I. Bergeron, Janick.

TK7885.7 V44 2005

621.39'2--dc22

2005051724

Cover: Die photograph of the ARM926EJ-S™ PrimeXsys™ Platform Development Chip © 2005 ARM Ltd.

ARM is a registered trademark and ARM926EJ-S and PrimeXsys are trademarks of ARM Limited. “ARM” is used to represent ARM Holdings plc; its operating company ARM Limited; and the regional subsidiaries ARM INC.; ARM KK; ARM Korea Ltd.; ARM Taiwan; ARM France SAS; ARM Consulting (Shanghai) Co. Ltd.; ARM Belgium N.V.; AXYS Design Automation Inc.; AXYS GmbH; ARM Embedded Technologies Pvt. Ltd.; and ARM Physical IP, Inc. Synopsys is a registered trademark of Synopsys, Inc.

© 2006 Synopsys, Inc. and ARM Limited

All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, Inc., 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden.

The use in this publication of trade names, trademarks, service marks and similar terms, even if the are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

Printed in the United States of America.

9 8 7 6 5 4 3 2 1

SPIN 11055174

[springeronline.com](http://springeronline.com)

---

---

# FOREWORD

---

When I co-authored the original edition of the *Reuse Methodology Manual for System-on-Chip Designs* (RMM) nearly a decade ago, designers were facing a crisis. Shrinking silicon geometry had increased system-on-chip (SoC) capacity well into the millions of gates, but development teams simply didn't have the time or resources to design so much logic while meeting product schedules. At that time, design reuse was emerging as the best way to resolve this dilemma. The RMM was written to provide an extensive set of rules, guidelines, and best practices for developing reusable IP that could be quickly and easily integrated into SoC designs.

IP-reuse-based SoC design methodology is now a fully accepted industry practice, and I am proud that the three editions of the RMM have helped to guide this evolution. It is now time for a book providing similar guidance for verification methodology and verification reuse. As many studies have shown, verification has emerged as the biggest portion of SoC development, consuming the most time and resources on most projects. The practices that sufficed for small designs-hand-written directed tests with minimal coverage metrics-are woefully insufficient in the SoC world.

I am pleased to introduce the *Verification Methodology Manual for SystemVerilog*, a book that will revolutionize the practices of verification engineers much as the RMM led designers to a better methodology with more predictable results. It encompasses all the latest techniques, including constrained-random stimulus generation, coverage-driven verification, assertion-based verification, formal analysis, and system-level verification in an open, well-defined methodology. It introduces and illustrates these techniques with examples from SystemVerilog, the industry standard linking RTL design, testbenches, assertions, and coverage together in a coherent and comprehensive language.

---

## Foreword

---

This book is not a theoretical exercise; it is based upon many years of verification experience from the authors, their colleagues, and their customers. It is practical and usable for SoC teams looking to greatly reduce the pain of verification while significantly increasing their chances of first-silicon success. It is my hope that the *Verification Methodology Manual for SystemVerilog* will be an essential reference guide for a whole new generation of SoC projects.

Pierre Bricaud

Co-Author of *Reuse Methodology Manual for System-on-Chip Designs*

Synopsys, Inc.

---

# CONTENTS

---

|                 |          |

|-----------------|----------|

| <i>Foreword</i> | <i>v</i> |

|-----------------|----------|

|                |             |

|----------------|-------------|

| <i>Preface</i> | <i>xiii</i> |

|----------------|-------------|

|                                   |      |

|-----------------------------------|------|

| How this Book is Structured ..... | xiii |

| How to Read this Book .....       | xv   |

| For More Information .....        | xvi  |

| Acknowledgements .....            | xvi  |

---

|                  |                     |          |

|------------------|---------------------|----------|

| <b>CHAPTER 1</b> | <i>Introduction</i> | <b>1</b> |

|------------------|---------------------|----------|

|                                        |    |

|----------------------------------------|----|

| Verification Productivity .....        | 2  |

| <i>Increasing Productivity</i> .....   | 3  |

| Verification Components .....          | 4  |

| <i>Interface-Based Design</i> .....    | 4  |

| Design for Verification .....          | 6  |

| <i>The Benefit of Assertions</i> ..... | 7  |

| Methodology Implementation .....       | 8  |

| <i>Methodology Adoption</i> .....      | 8  |

| <i>Guidelines</i> .....                | 11 |

| <i>Basic Coding Guidelines</i> .....   | 12 |

| <i>Definition of Terms</i> .....       | 13 |

---

**CHAPTER 2** *Verification Planning* **17**

|                                                    |           |

|----------------------------------------------------|-----------|

| Planning Process .....                             | <b>18</b> |

| <i>Functional Verification Requirements</i> .....  | <b>18</b> |

| <i>Verification Environment Requirements</i> ..... | <b>22</b> |

| <i>Verification Implementation Plan</i> .....      | <b>29</b> |

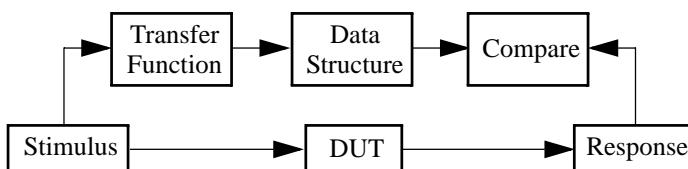

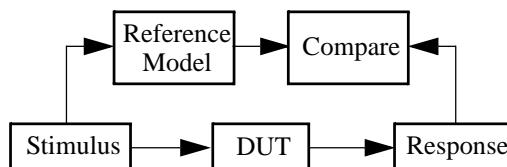

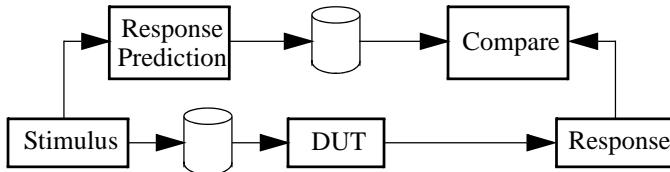

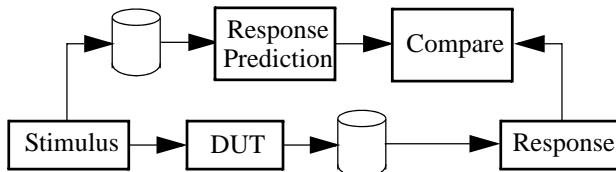

| Response Checking .....                            | <b>31</b> |

| <i>Embedded Monitors</i> .....                     | <b>32</b> |

| <i>Assertions</i> .....                            | <b>33</b> |

| <i>Accuracy</i> .....                              | <b>36</b> |

| <i>Scoreboarding</i> .....                         | <b>38</b> |

| <i>Reference Model</i> .....                       | <b>39</b> |

| <i>Offline Checking</i> .....                      | <b>40</b> |

| Summary .....                                      | <b>41</b> |

**CHAPTER 3** *Assertions* **43**

|                                                 |            |

|-------------------------------------------------|------------|

| Specifying Assertions .....                     | <b>44</b>  |

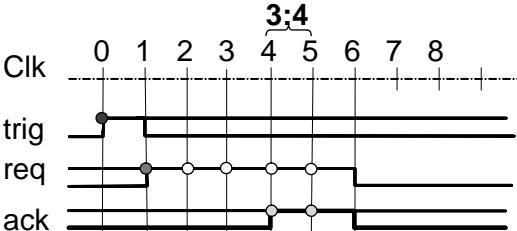

| <i>Assertion Language Primer</i> .....          | <b>46</b>  |

| Assertions on Internal DUT Signals .....        | <b>50</b>  |

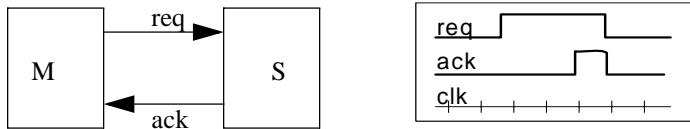

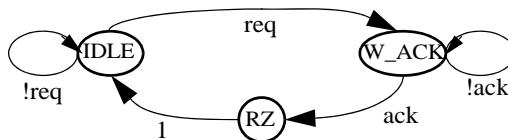

| Assertions on External Interfaces .....         | <b>59</b>  |

| Assertion Coding Guidelines .....               | <b>63</b>  |

| <i>Coverage Properties</i> .....                | <b>72</b>  |

| Reusable Assertion-Based Checkers .....         | <b>77</b>  |

| <i>Simple Checkers</i> .....                    | <b>78</b>  |

| <i>Assertion-Based Verification IP</i> .....    | <b>86</b>  |

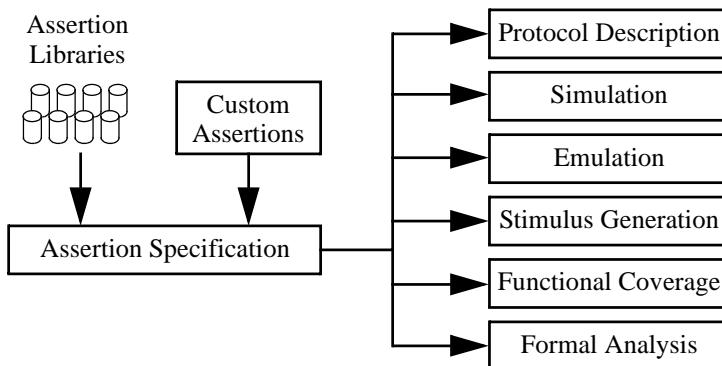

| <i>Architecture of Assertion-Based IP</i> ..... | <b>90</b>  |

| <i>Documentation and Release Items</i> .....    | <b>99</b>  |

| Qualification of Assertions .....               | <b>100</b> |

| Summary .....                                   | <b>102</b> |

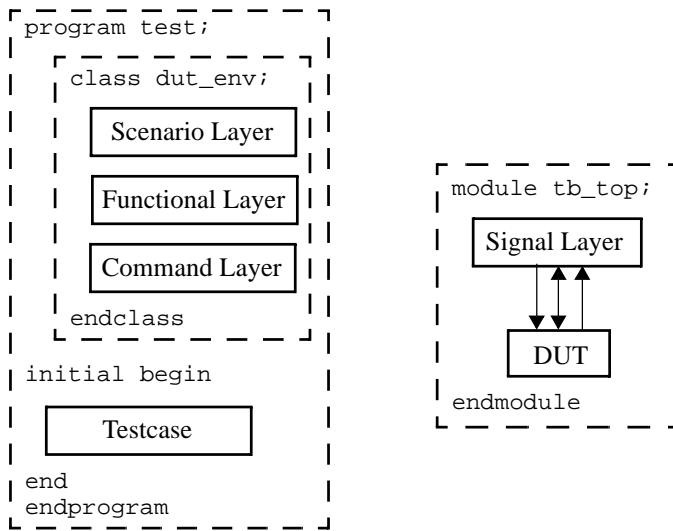

**CHAPTER 4** *Testbench Infrastructure* **103**

|                               |            |

|-------------------------------|------------|

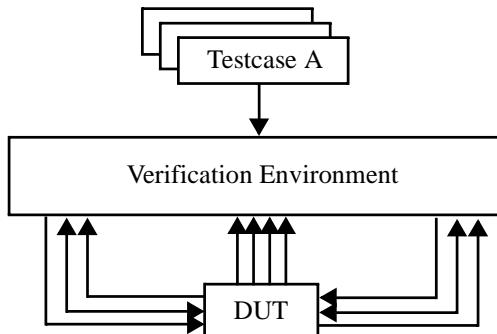

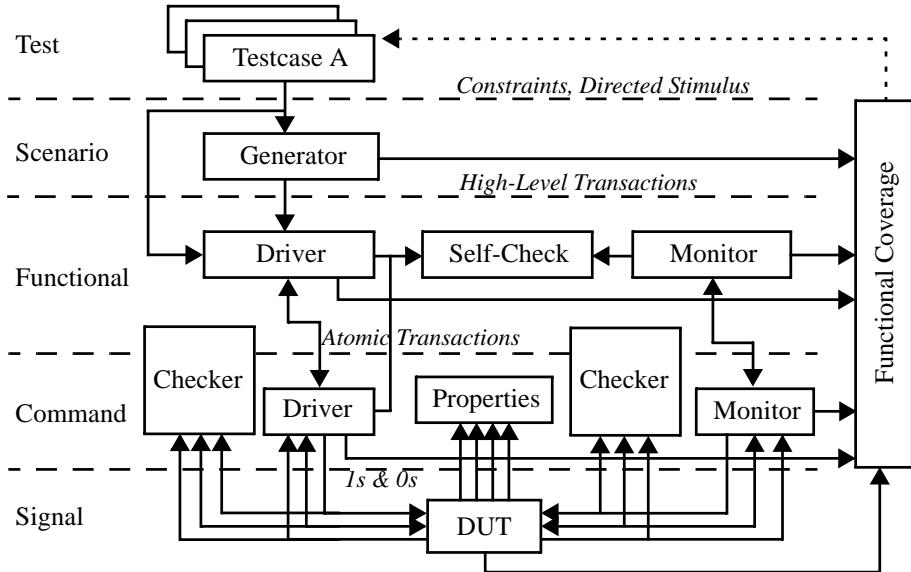

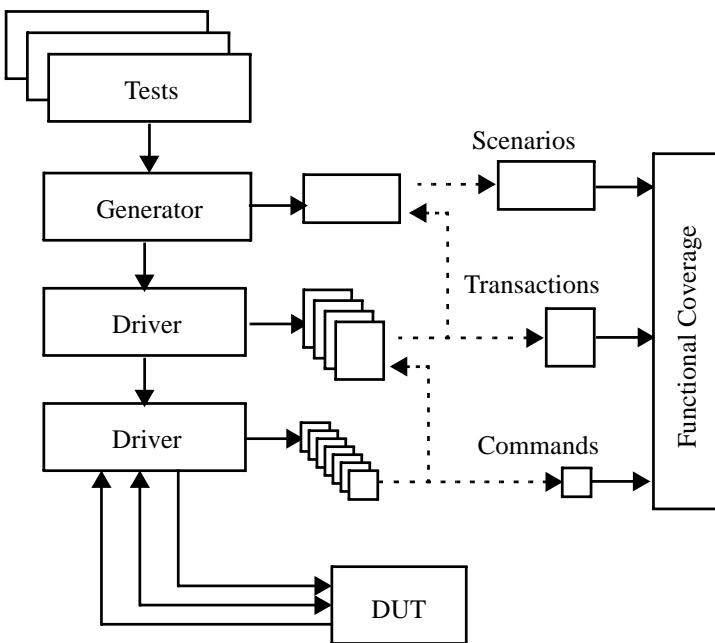

| Testbench Architecture .....  | <b>104</b> |

| <i>Signal Layer</i> .....     | <b>107</b> |

| <i>Command Layer</i> .....    | <b>116</b> |

| <i>Functional Layer</i> ..... | <b>118</b> |

| <i>Scenario Layer</i> .....   | <b>122</b> |

| <i>Test Layer</i> .....       | <b>123</b> |

| Simulation Control .....      | <b>124</b> |

---

---

|                                            |            |

|--------------------------------------------|------------|

| <i>OOP Primer: Virtual Methods</i>         | 126        |

| <i>Message Service</i>                     | 134        |

| <b>Data and Transactions</b>               | <b>140</b> |

| <i>Class Properties/Data Members</i>       | 143        |

| <i>Methods</i>                             | 154        |

| <i>Constraints</i>                         | 157        |

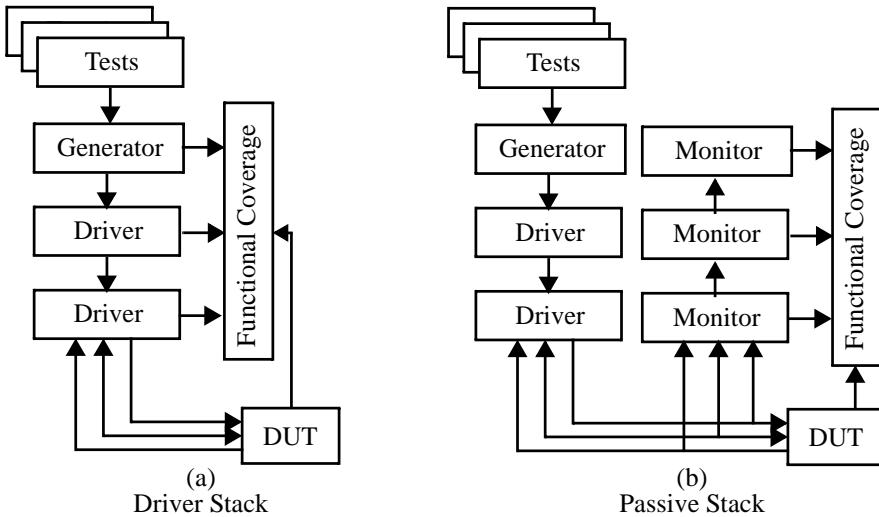

| <b>Transactors</b>                         | <b>161</b> |

| <i>Physical-Level Interfaces</i>           | 169        |

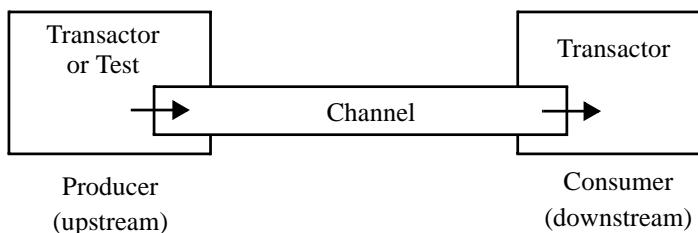

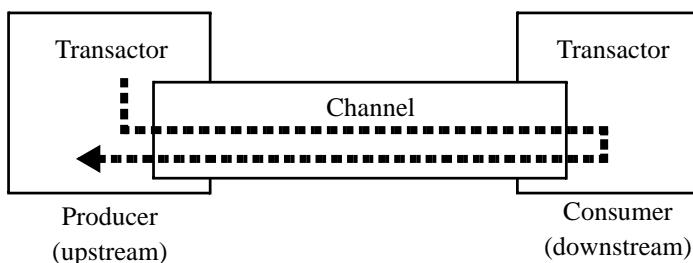

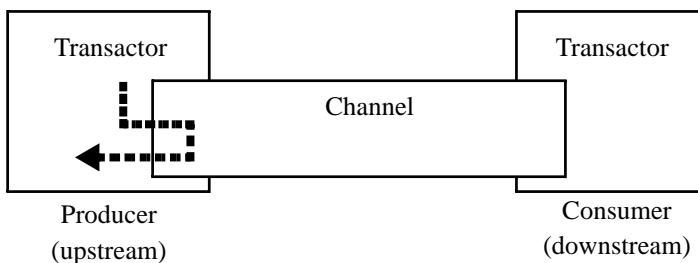

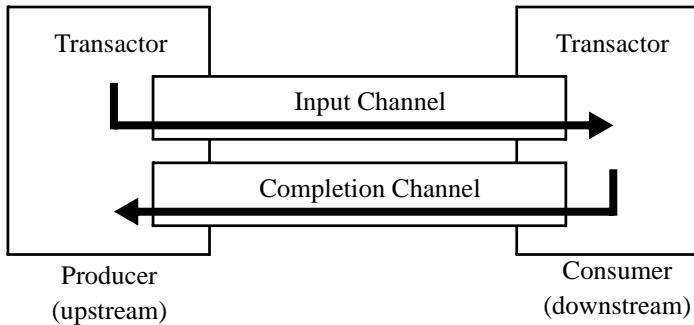

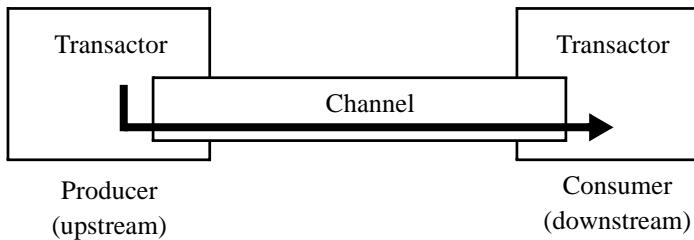

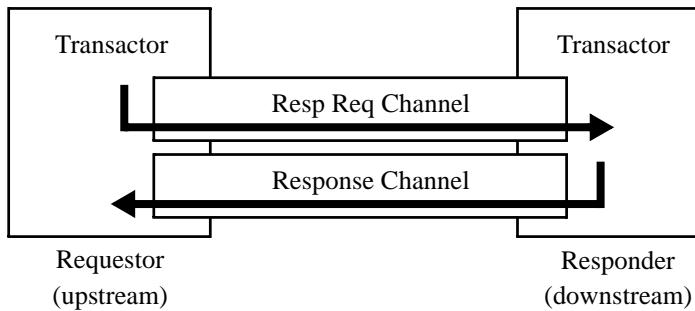

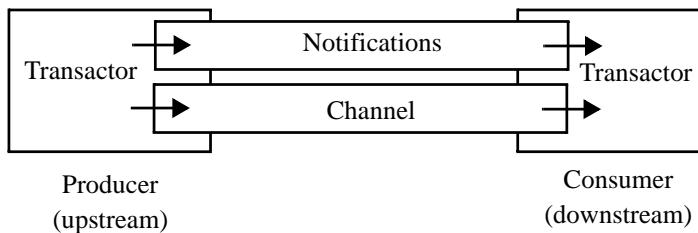

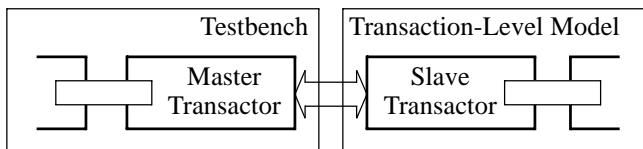

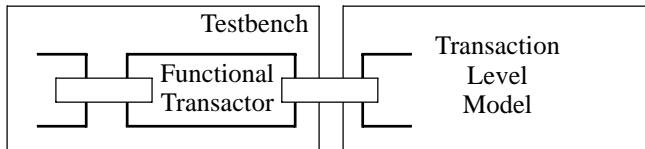

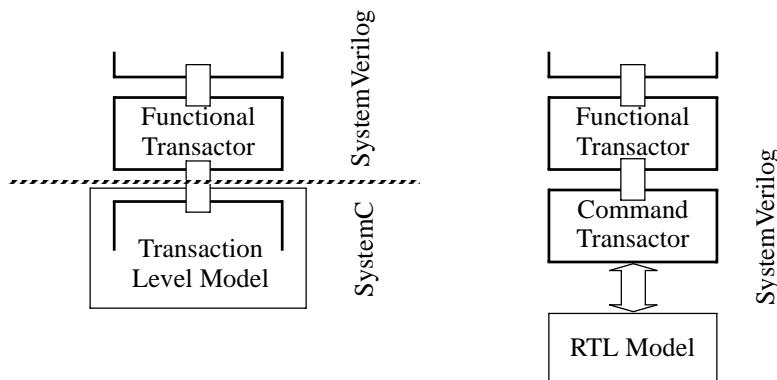

| <b>Transaction-Level Interfaces</b>        | <b>171</b> |

| <i>Completion and Response Models</i>      | 176        |

| <i>In-Order Atomic Execution Model</i>     | 177        |

| <i>Out-of-Order Atomic Execution Model</i> | 182        |

| <i>Non-Atomic Transaction Execution</i>    | 185        |

| <i>Passive Response</i>                    | 189        |

| <i>Reactive Response</i>                   | 192        |

| <b>Timing Interface</b>                    | <b>195</b> |

| <b>Callback Methods</b>                    | <b>198</b> |

| <b>Ad-Hoc Testbenches</b>                  | <b>201</b> |

| <b>Legacy Bus-Functional Models</b>        | <b>206</b> |

| <i>VMM-Compliance Upgrade</i>              | 206        |

| <i>VMM-Compliant Interface</i>             | 207        |

| <b>Summary</b>                             | <b>210</b> |

## CHAPTER 5 *Stimulus And Response* 211

|                                         |            |

|-----------------------------------------|------------|

| <b>Generating Stimulus</b>              | <b>211</b> |

| <i>Random Stimulus</i>                  | 213        |

| <i>OOP Primer: Factory Pattern</i>      | 217        |

| <i>Directed Stimulus</i>                | 219        |

| <i>Generating Exceptions</i>            | 221        |

| <i>Embedded Stimulus</i>                | 226        |

| <b>Controlling Random Generation</b>    | <b>227</b> |

| <i>Atomic Generation</i>                | 231        |

| <i>Scenario Generation</i>              | 232        |

| <i>Multi-Stream Generation</i>          | 236        |

| <i>State-Dependent Generation</i>       | 238        |

| <i>Which Type of Generator to Use?</i>  | 244        |

| <b>Self-Checking Structures</b>         | <b>246</b> |

| <i>Scoreboarding</i>                    | 249        |

| <i>Integration with the Transactors</i> | 253        |

---

---

|                                                             |                                     |            |

|-------------------------------------------------------------|-------------------------------------|------------|

| <i>Dealing with Exceptions</i> .....                        | 255                                 |            |

| Summary .....                                               | 257                                 |            |

| <b>CHAPTER 6</b>                                            | <i>Coverage-Driven Verification</i> | <b>259</b> |

| Coverage Metrics .....                                      | 260                                 |            |

| Coverage Models .....                                       | 261                                 |            |

| <i>Structural Coverage Modeling</i> .....                   | 262                                 |            |

| <i>Functional Coverage Modeling</i> .....                   | 263                                 |            |

| <i>Functional Coverage Analysis</i> .....                   | 265                                 |            |

| <i>Coverage Grading</i> .....                               | 266                                 |            |

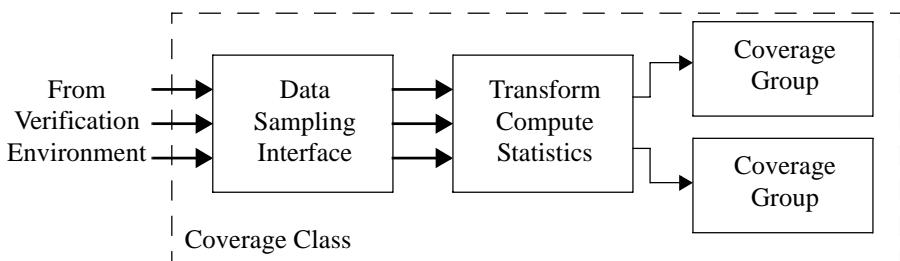

| Functional Coverage Implementation .....                    | 266                                 |            |

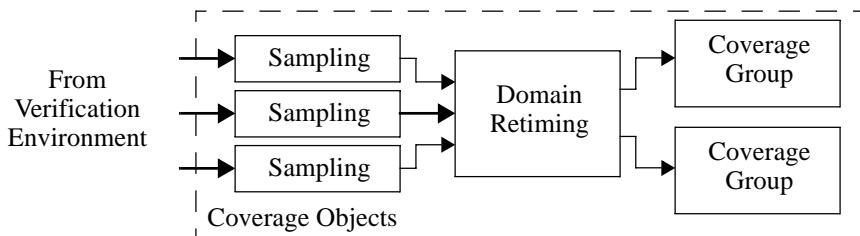

| <i>Coverage Groups</i> .....                                | 268                                 |            |

| <i>Coverage Properties</i> .....                            | 276                                 |            |

| Feedback Mechanisms .....                                   | 277                                 |            |

| Summary .....                                               | 280                                 |            |

| <b>CHAPTER 7</b>                                            | <i>Assertions for Formal Tools</i>  | <b>281</b> |

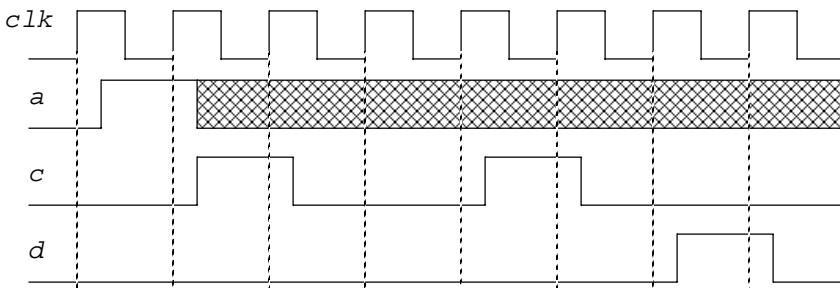

| Model Checking and Assertions .....                         | 282                                 |            |

| Assertions on Data .....                                    | 292                                 |            |

| <i>Without Local Variables</i> .....                        | 293                                 |            |

| <i>With Local Variables</i> .....                           | 297                                 |            |

| <i>Compatibility with Formal Tools</i> .....                | 302                                 |            |

| Summary .....                                               | 303                                 |            |

| <b>CHAPTER 8</b>                                            | <i>System-Level Verification</i>    | <b>305</b> |

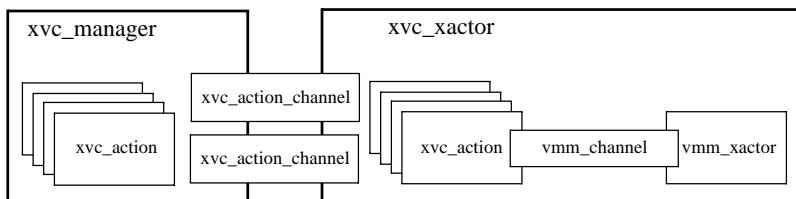

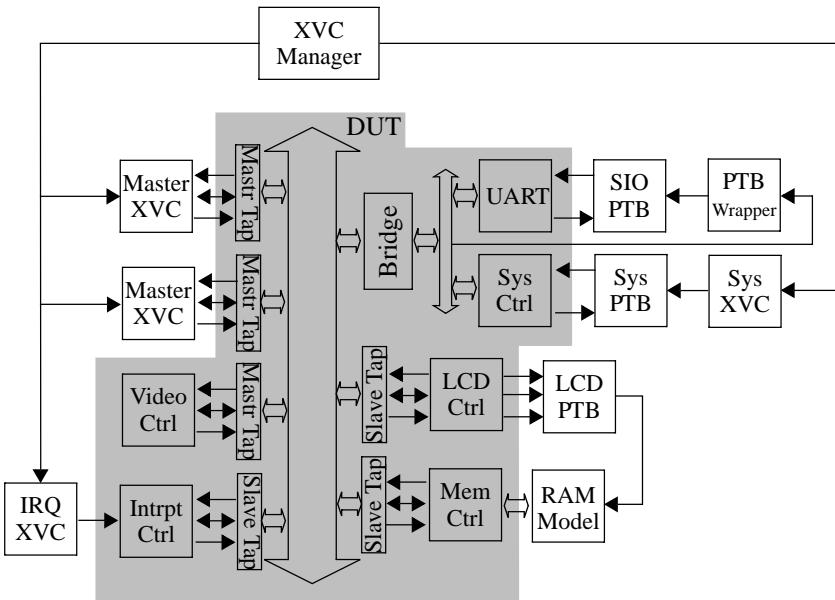

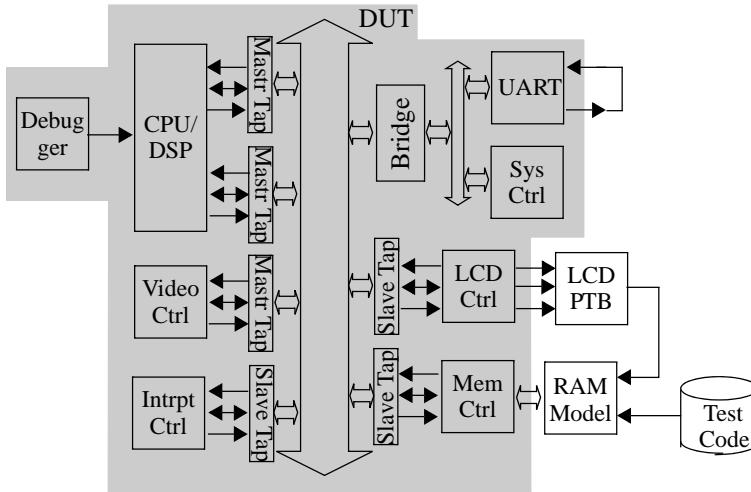

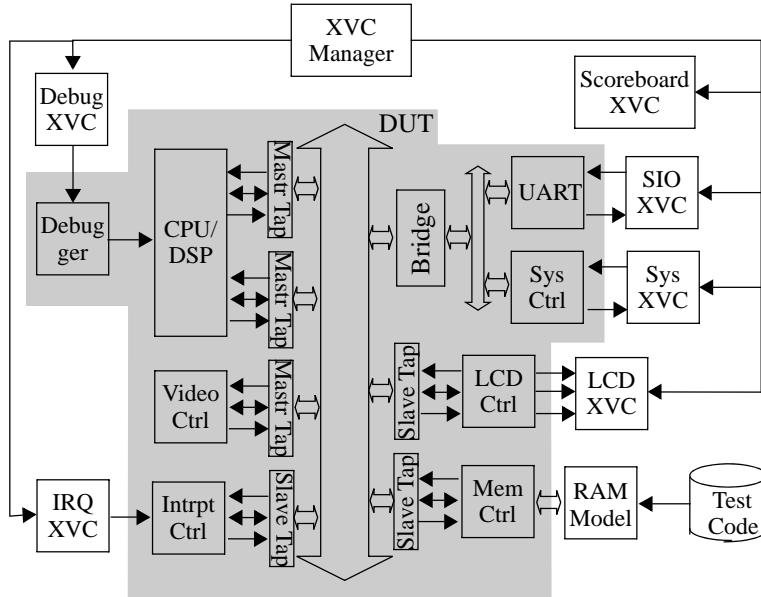

| Extensible Verification Components .....                    | 306                                 |            |

| <i>XVC Architecture</i> .....                               | 306                                 |            |

| <i>Implementing XVCs</i> .....                              | 309                                 |            |

| <i>Implementing Actions</i> .....                           | 311                                 |            |

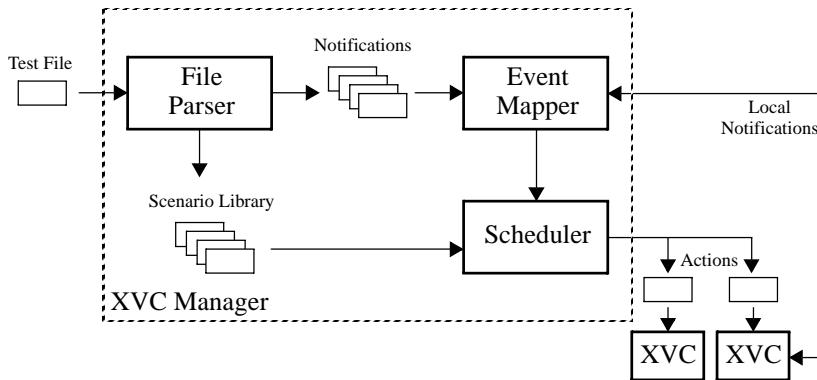

| XVC Manager .....                                           | 316                                 |            |

| <i>Predefined XVC Manager</i> .....                         | 317                                 |            |

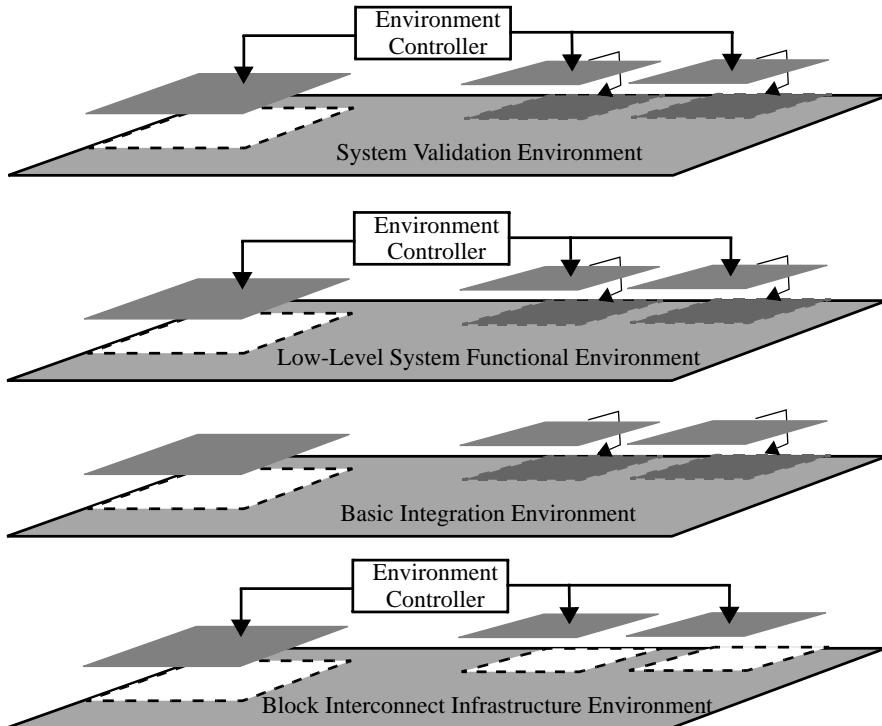

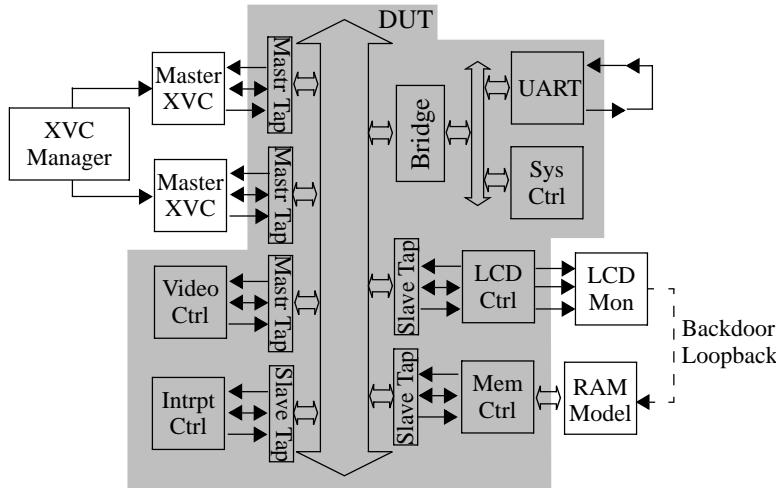

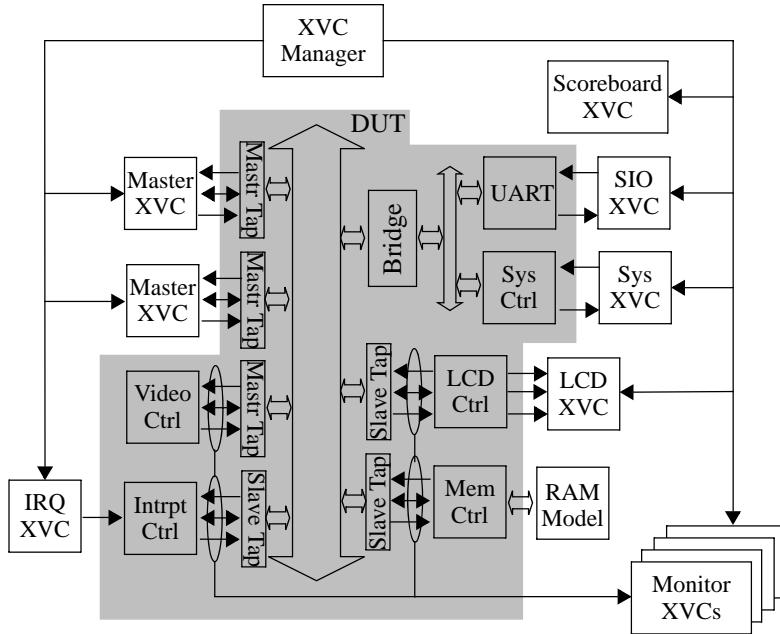

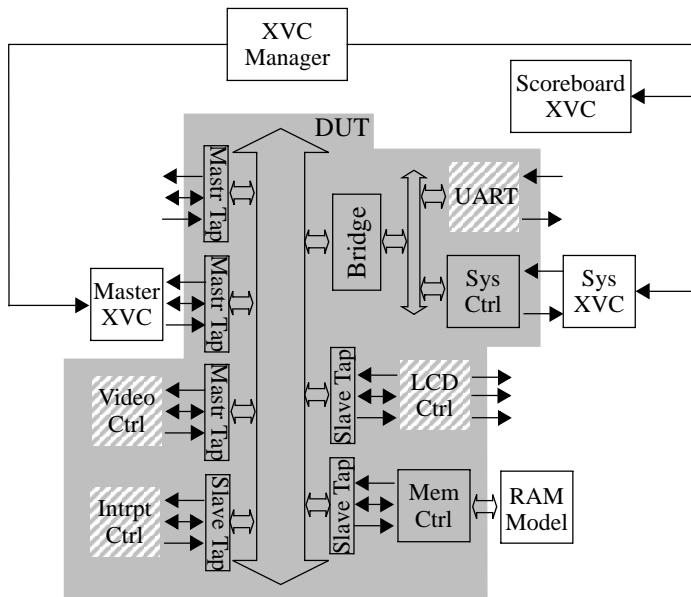

| System-Level Verification Environments .....                | 319                                 |            |

| <i>Block Interconnect Infrastructure Verification</i> ..... | 323                                 |            |

| <i>Basic Integration Verification</i> .....                 | 326                                 |            |

| <i>Low-Level System Functional Verification</i> .....       | 328                                 |            |

| <i>System Validation Verification</i> .....                 | 329                                 |            |

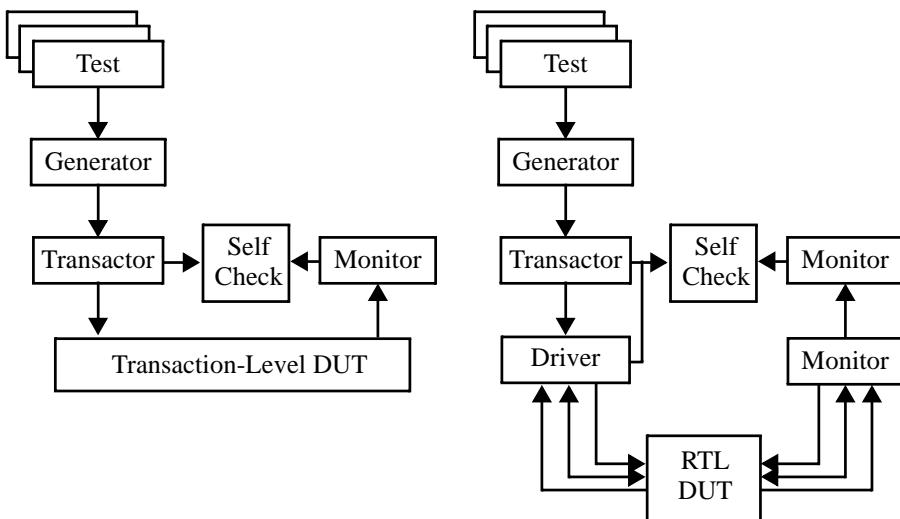

| Verifying Transaction-Level Models .....                    | 332                                 |            |

---

---

|                                                      |            |

|------------------------------------------------------|------------|

| <i>Transaction-Level Interface</i> .....             | 334        |

| Hardware-Assisted Verification .....                 | 336        |

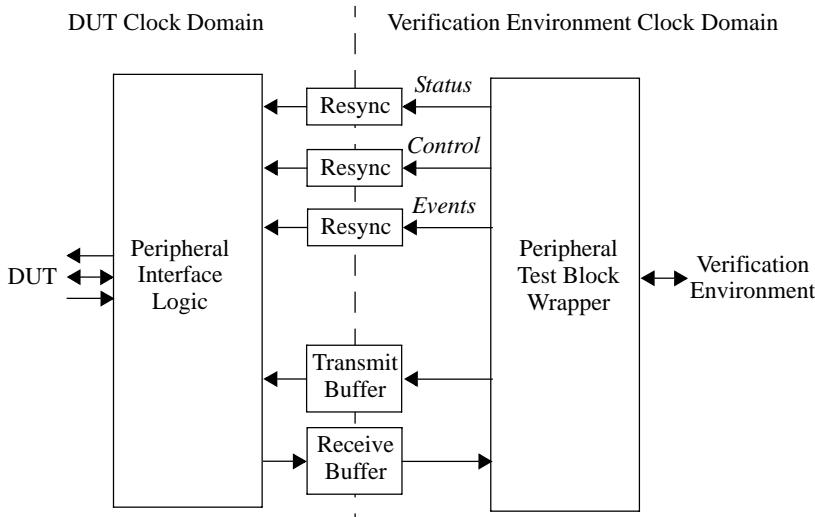

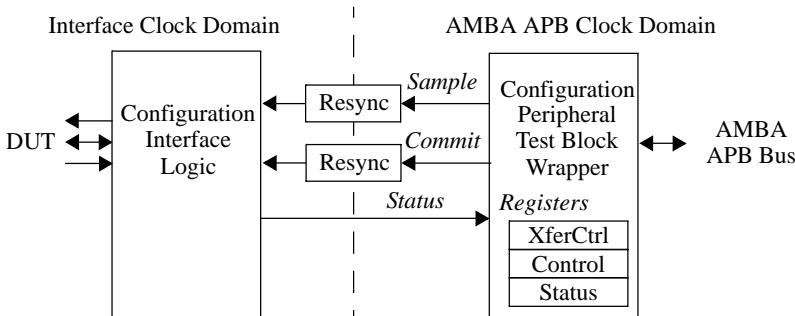

| <i>Peripheral Test Block Structure</i> .....         | 339        |

| Summary .....                                        | 342        |

| <b>CHAPTER 9 Processor Integration Verification</b>  | <b>343</b> |

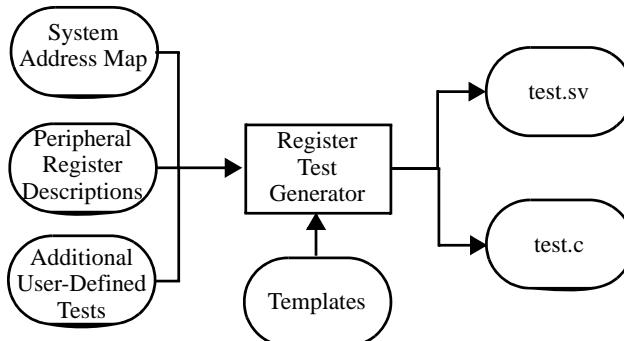

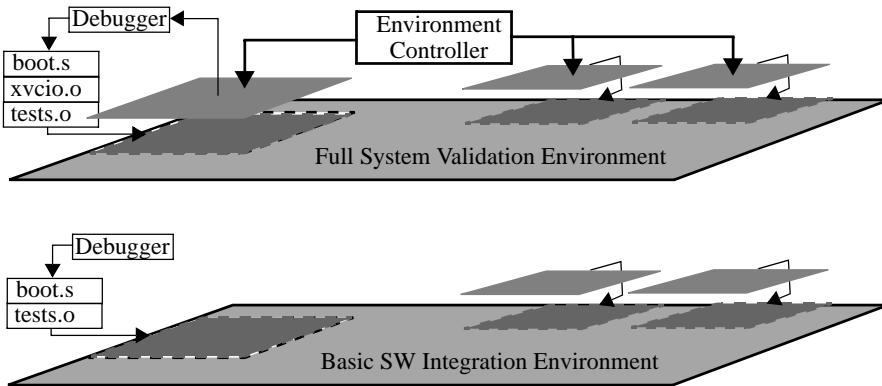

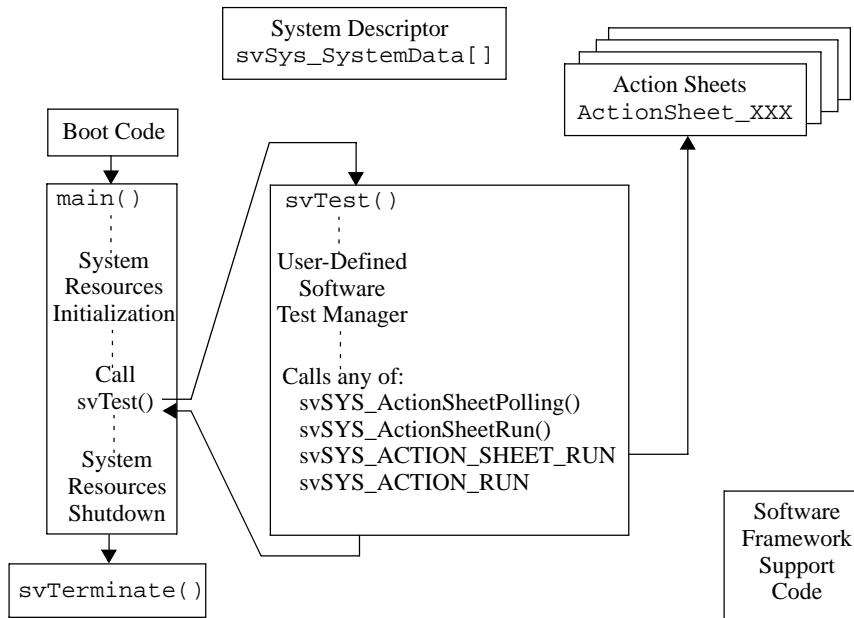

| Software Test Environments .....                     | 343        |

| <i>Basic Software Integration Verification</i> ..... | 345        |

| <i>Full System Verification Environment</i> .....    | 346        |

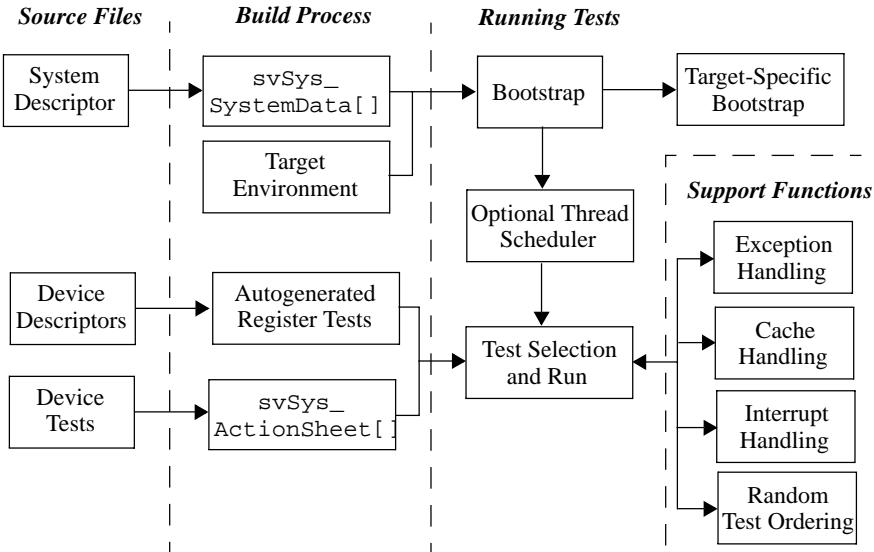

| Structure of Software Tests .....                    | 349        |

| Test Actions .....                                   | 354        |

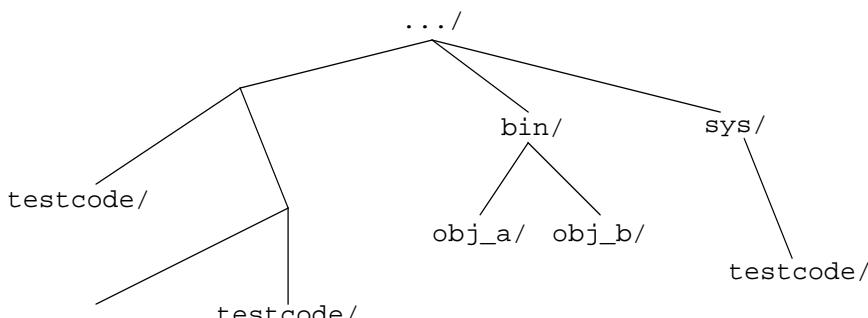

| <i>Compilation Process</i> .....                     | 359        |

| <i>Running Tests</i> .....                           | 361        |

| <i>Bootstrap</i> .....                               | 363        |

| Summary .....                                        | 364        |

| <b>APPENDIX A VMM Standard Library Specification</b> | <b>365</b> |

| vmm_env .....                                        | 365        |

| vmm_log .....                                        | 368        |

| <i>vmm_log_msg</i> .....                             | 378        |

| <i>vmm_log_format</i> .....                          | 379        |

| <i>vmm_log_callbacks</i> .....                       | 381        |

| vmm_data .....                                       | 383        |

| vmm_channel .....                                    | 387        |

| vmm_broadcast .....                                  | 397        |

| vmm_scheduler .....                                  | 401        |

| <i>vmm_scheduler_election</i> .....                  | 404        |

| vmm_notify .....                                     | 405        |

| <i>vmm_notification</i> .....                        | 409        |

| vmm_xactor .....                                     | 411        |

| <i>vmm_xactor_callbacks</i> .....                    | 415        |

| vmm_atomic_gen .....                                 | 415        |

| <i>&lt;class_name&gt;_atomic_gen_callbacks</i> ..... | 418        |

| vmm_scenario_gen .....                               | 418        |

| <i>&lt;class_name&gt;_scenario</i> .....             | 421        |

| <i>&lt;class_name&gt;_atomic_scenario</i> .....      | 424        |

| <i>&lt;class_name&gt;_scenario_election</i> .....    | 425        |

---

---

|                                                      |            |

|------------------------------------------------------|------------|

| <i>&lt;class_name&gt;_scenario_gen_callbacks</i>     | 426        |

| <b>APPENDIX B VMM Checker Library</b>                | <b>429</b> |

| OVL-Equivalent Checkers (SVL)                        | 429        |

| Advanced Checkers                                    | 434        |

| <b>APPENDIX C XVC Standard Library Specification</b> | <b>439</b> |

| xvc_manager                                          | 439        |

| xvc_xactor                                           | 440        |

| xvc_action                                           | 442        |

| vmm_xvc_manager                                      | 444        |

| Notifications                                        | 444        |

| File Structure                                       | 445        |

| Commands                                             | 447        |

| <b>APPENDIX D Software Test Framework</b>            | <b>459</b> |

| Basic Types                                          | 459        |

| System Descriptor                                    | 460        |

| Peripheral Descriptor                                | 460        |

| Interrupt Descriptor                                 | 463        |

| DMA Channel Descriptor                               | 464        |

| Test Actions                                         | 465        |

| Low-Level Services                                   | 470        |

| Cache Lockdown                                       | 474        |

| Interrupt Controller                                 | 475        |

| Software-XVC Connectivity                            | 478        |

| <i>Index</i>                                         | 481        |

| <i>About the Authors</i>                             | 503        |

---

---

## PREFACE

---

When VHDL first came out as an IEEE standard, it was thought to be sufficient to model hardware designs. Reality proved to be a little different. Because it did not have a predefined four-state logic type, each simulator and model vendor had to create its own—and incompatible—logic type. This situation prompted the quick creation of a group to create a standard multi-valued logic package for VHDL that culminated with the 1164 standard. With such a package, models became interoperable and simulators could be optimized to perform well-defined operations.

The authors of this book hope to create a similar standard for verification components within the SystemVerilog language. The infrastructure elements specified in the appendices can form the basis of a standard verification interface. If model vendors use it to build their verification components, they will be immediately interoperable. If simulator vendors optimize their implementation of the standard functions, the runtime performances can be improved.

---

## HOW THIS BOOK IS STRUCTURED

The book is composed of chapters and appendices. The chapters describe guidelines that must or should be followed when implementing the verification methodology. The appendices specify application-generic support elements to help in the implementation process.

Chapter 3 provides guidelines for writing assertions. Its companion Appendix B specifies a set of predefined checkers that can be used in lieu of writing new assertions.

Chapter 4 describes the components of a verification environment and how to implement them. Its companion Appendix A specifies a set of base and utility classes that are used to implement the generic functionality required by all environments and components.

Chapter 5 describes how to provide stimulus to the design under verification and how it can be constrained to create interesting conditions. The generator classes specified in Appendix A help to rapidly create VMM-compliant generator components.

Chapter 6 describes how to use qualitative metrics to drive the verification process and using a constrainable random verification environment built using the guidelines presented in the previous chapters to efficiently implement it.

Chapter 7 describes how assertions can be used with formal technology. Only a subset of the checkers described in Appendix B can be used within this context.

Chapter 8 describes how the principles presented in the previous chapters can be leveraged for system-level verification. Its companion Appendix C specifies a command language and extensible component infrastructure to implement block and system-level verification environments.

Chapter 9 describes how the integration of a general-purpose programmable processor in a system can be verified using a set of predefined C functions described in Appendix D.

The support infrastructure is specified in appendices A through D by describing the interface and functionality of each element. No implementation is provided. It is up to each vendor to provide a suitable implementation. This gives the opportunity to EDA or IP vendors to optimize the implementation of the infrastructure for their particular platform. It also eliminates the risk that unintended side effects of a particular "reference" implementation might be interpreted as expected behavior. The code for the interface specifications is available at the companion Web site:

<http://vmm-sv.org>

Note that the methodology can be followed without using the support elements specified in the appendices. Any functionally equivalent set of elements, providing similar functionality, would work. However, using a different set of support elements will likely diminish the interoperability of verification components and environments written using different support infrastructures.

## HOW TO READ THIS BOOK

---

This book is not designed as a textbook that can be read and applied linearly. Although the authors have made their best effort to present the material in a logical order, it will be often difficult to appreciate the importance or wisdom of some elements of the methodology without a grasp of the overall picture. Unfortunately, it is not possible to draw an overall picture without first building the various elements used to construct it.

The chicken-and-egg paradox is inherent to describing methodologies. A methodology is about taking steps today to make life easier in some future. A successful methodology will help reduce the overall cost of a project through investments at earlier stages that will provide greater returns later on. In a practical description of a methodology, it is difficult to justify some of the initial costs as their future benefit is not immediately apparent. Similarly, describing the future benefits is not possible without describing the elements that, when put together, will create these benefits.

A reader unfamiliar with an equivalent methodology would typically require two readings of the entire book. A first reading will help form the overall picture of the methodology, how the various elements fit together and the benefits that can be realized. A second reading will help appreciate its detailed implementation process and supporting library.

Although everyone will benefit from reading the entire book, there are sections that are more relevant to specific verification tasks. Designers must read Chapter 3. They should also read Chapter 7 if they intend to use formal technology to verify their design. Verification leaders and project managers should read Chapters 2 and 6. Verification engineers responsible for the implementation and maintenance of the verification environment must read Chapters 4 and 5 and should read Chapter 8. Verification IP developers should read Chapters 4 and 8. Verification engineers responsible for implementing testcases should read the first half of Chapter 5. If they are also responsible for implementing functional coverage points, they should read the second half of Chapter 6. Embedded software verification engineers should read Chapter 9.

## FOR MORE INFORMATION

---

At the time of writing, SystemVerilog was in the process of being ratified as an IEEE standard. In addition to several books already—or to be—published, more information about SystemVerilog can be obtained from:

<http://www.eda.org/sv>

<http://www.eda.org/sv-ieee1800>

This book assumes the reader has experience with the entire SystemVerilog language. It is not designed as an introductory or training text to the verification or assertion constructs. The following books, listed in alphabetical order, can be used to gain the necessary experience and knowledge of the language constructs:

Janick Bergeron, "*Writing Testbenches Using SystemVerilog*", Springer

Ben Cohen, Srinivasan Venkataraman and Ajeetha Kumari, "*SystemVerilog Assertions Handbook*", VhdlCohen Publishing

Chris Spear and Arturo Salz, "*SystemVerilog for Verification*", Springer

In this book, code examples are provided as extracts that focus on the various points they are designed to illustrate. It does not contain a full example of the methodology application within its page. Such an example would consume several tens of pages filled with SystemVerilog code. It would be difficult to navigate, would become obsolete as improvements to the methodology are made and impossible to actually simulate. Pointers to several complete examples and the complete code that includes the various examples can be found at the companion Web site:

<http://vmm-sv.org>

The companion Web site will also contain an errata for the latest edition of the book. It may also publish additional guidelines as the methodology evolves and is expanded. These additional guidelines will be included in future editions. Discussions on the use or interpretation of the methodology and suggestions for improvement are carried in the forums at:

<http://verificationguild.com>

## ACKNOWLEDGEMENTS

---

The authors would like to thank Holger Keding for his contribution to Chapter 8. They are also grateful for the thoughtful reviews and challenging comments from Pierre Aulagnier, Oliver Bell, Michael Benjamin, Jonathan Bradford, Craig Deaton,

---

## Acknowledgements

---

Jeff DeChiaro, Geoff Hall, Wolfgang Ecker, Rémi Francard, Christian Glaßner, Olivier Haller, Takashi Kambe, Masamichi Kawarabayashi, Michael Keating, Dave Matt, Aditya Mukherjee, Seiichi Nishio, Zenji Oka, Michael Röder, Kostas Siomalias, Stefan Sojka, Jason Sprott, STARC IP Verification SWG (Masahiro Furuya, Hiroyuki Fukuyama, Kohkichi Hashimoto, Masanori Imai, Masaharu Kimura, Hiroshi Koguchi, Hirohisa Kotegawa, Youichiro Kumazaki, Yoshikazu Mori, Tadahiko Nakamura, Sanae Saitou, Masayuki Shono, Tsuneo Toba, Hideaki Washimi, Takeru Yonaga), Rob Swan, Yoshio Takamine, Gary Vrckovnik and Frazer Worley. The book also benefited from the loving attention of Kyle Smith, the technical editor.

Many others have contributed to making this book and its content a reality. Alphabetically, they are: Jay Alphey, Tom Anderson, Tom Borgstrom, Dan Brook, Dan Coley, Tom Fitzpatrick, Mike Glasscock, John Goodenough, Badri Gopalan, David Gwilt, Tim Holden, Ghassan Khoory, FrameMaker, Mehdi Mohtashemi, Phil Moorby, Dave Rich, Spencer Saunders, David Smith, Michael Smith, Manoj Kumar Thottasseri and the VCS and Magellan implementation team.

---

# CHAPTER 1 INTRODUCTION

---

In the process of design and verification, experience shows that it is the latter task that dominates time scales. This book defines a methodology that helps minimize the time necessary to meet the verification requirements. It also takes the opportunity offered by the definition of a methodology to also define standards that will enable the creation of interoperable verification environments and components.

Using interoperable environments and components is essential in reducing the effort required to verify a complete product. A consistent usage model is present in all verification environments. System-level environments are able to leverage the components, self-checking structure and coverage from block-level environments. Formal tools are able to share the same properties used by simulation. Verification IP is able to meet the requirement of verifying the interface block as well as the system-level functionality that resides behind it.

The methodology described in this book defines standards for specifying reusable properties that are efficient to simulate and that can be formally verified. It defines standards for creating transaction and data descriptors to facilitate their constrainable random generation while maintaining a flexible directed capability. This methodology standardizes how bus-functional models, monitors and transactors are designed to provide stimulus and checking functions that are relevant from block to system. Furthermore, this methodology sets standards for the integration of the various components into a verification environment so they can be easily combined, controlled and later extricated to leverage in different environments. The book also defines standards for implementing coverage models and software verification environments. These standards, when put together in a coherent methodology, help reduce the effort required to verify a design.

---

## Introduction

---

The methodology described in this book could be implemented using a different language or a different set of standards. But interoperability is maximized when the same language and the same set of standards are used. The classes and associated guidelines specified in this book can be freely used by anyone, users and EDA vendors alike. The objective is to create a vibrant SystemVerilog verification ecosystem that speaks a common language, uses a common approach and creates highly interoperable verification environments and components.

---

## VERIFICATION PRODUCTIVITY

---

The progress of a verification project is measured by the number of functional features that are confirmed as functionally correct. Therefore, verification productivity is a measure of how many such features are confirmed as functionally correct over a period of time, including the time necessary to debug and fix any functional errors in the same features. The greater the productivity, the faster a high-quality product can be manufactured. This measure of productivity is not necessarily correlated to the amount of code written in the same time period, nor is it correlated to the runtime performance of the simulations used to confirm functional correctness. It is possible to achieve a higher verification productivity while writing less code and running more concurrent simulations.

Historically, verification methodologies have evolved alongside the design abstraction and kept pace with the complexities of the designs being implemented. When design was done at the mask level, verification was accomplished by simulating transistor models. When design transitioned to standard cells, verification transitioned to gate-level digital simulations. When design took advantage of the simulation language to introduce logic synthesis, verification evolved to transaction-level testbenches using bus-functional models. Throughout these evolutionary steps, the approach to verification has not fundamentally changed: Individual design features are verified using individual testcases crafted to exercise the targeted feature.

However, the traditional individual testcase approach does not scale to handle today's largest multi-million gate designs. A project with one thousand separate features to verify would require over one calendar year to complete with the help of a team of 10 verification engineers able—on average—to write, debug and maintain one testcase every three days for the entire duration of the project. That effort requires an unusually large team of unusually productive engineers. Such large projects require a different approach.

## Increasing Productivity

The methodology presented in this book improves the productivity of a verification project through four different mechanisms: assertions, abstraction, automation and reuse.

When using assertions to identify defects on interfaces or in runtime assumptions, errors are reported close in space and time to their ultimate cause. Otherwise, the consequence of the error *may* have been detected after several clock cycles *if and when* it reached a monitored output and checked against expectations. Some classes of errors produce symptoms that are easy to detect at the boundary of the design—a missing packet for example. However, some classes of errors have symptoms that are not so obvious—for example, an arbitration error that can be recovered from, only producing a small reduction in throughput for a certain class of service. Assertions create monitors at critical points in the design without having to create separate testbenches where these points would be externally visible.

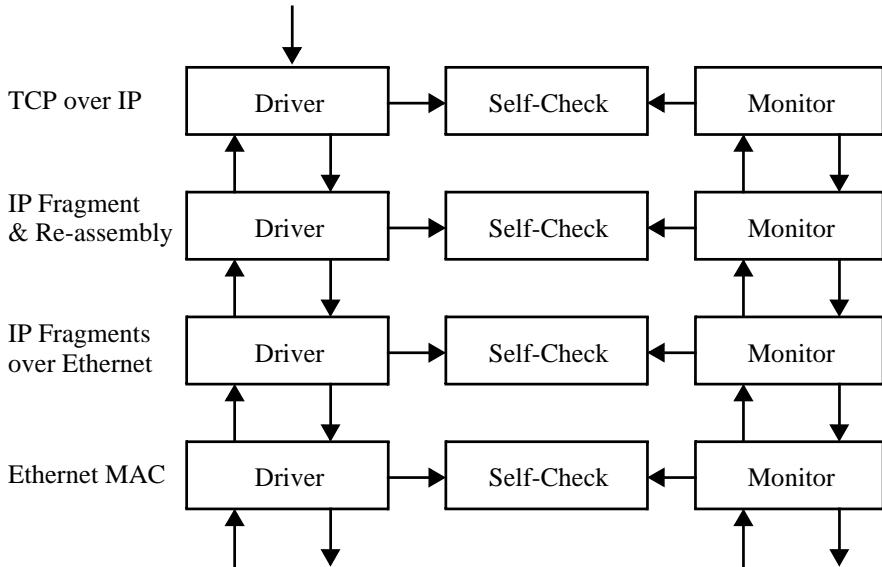

Verifying at an increasing the level of abstraction is simply continuing the past historical trend. But unlike historical increases in abstraction, this one need not be accompanied by an equivalent increase in the design abstraction. It is still necessary to verify low-level implementation and physical details. Once low-levels of functionality are verified, verification can proceed at higher levels using a layered testbench architecture. The layering of transactors to form successive layers of abstraction is also used to break away from the monolithic bus-functional model that makes it difficult to introduce additional or combinations of protocol layers.

The design-specific nature of the tests and the response-checking mechanism makes general purpose automation of the verification process impossible. True automation would produce the exact same testcases that would be written manually. But random stimulus can emulate automation: Left to its own devices, a properly-designed random source will eventually generate the desired stimulus. Random stimulus will also create conditions that may not have been foreseen as significant. When random stimulus fails to produce the required stimulus, or when the required stimulus is unlikely to be produced by an unbiased random stimulus source, constraints can be added to the random stimulus to increase the probability (sometimes to 100%) of generating the required stimulus. Due to the random nature of the stimulus, it is necessary to use a coverage mechanism to identify which testcases have been pseudo-automatically produced so far. This coverage metrics measure the progress and productivity of the verification process. Verification requirements that were automatically met are quickly identified, allowing the effort to be concentrated on those that remain to be met.

---

## Introduction

---

Reusing code avoids having to duplicate its functionality. Reuse is not limited to reusing code across projects. First-order reuse occurs when the same verification environment is reused across multiple testcases on the same project. By reusing code as much as possible, a feature can be verified using just a few lines of additional code. Ultimately, testcases should become simple reconfigurations of highly reusable verification components forming a design-specific verification environment or platform. Note that this book is not about a reuse methodology. Reuse is only a means, not an end.

# VERIFICATION COMPONENTS

---

As stated previously, first-order reuse occurs when a design-specific verification environment is reused across testcases for that design. Second-order reuse occurs when some components of the design-specific verification environment are reused in a system-level environment. Third-order reuse occurs when those same components are reused across different verification environments for different designs. For all of these reuse opportunities to be realized, verification components have to be properly designed.

For verification components to be reusable, they must be functionally correct and they must be configurable to meet the needs of the environments and testcases built on top of them. The term *configurable* in this context refers to the ability of the verification component to exhibit the required functionality to adequately exercise the design or system under verification. A configurable verification component can be used to drive an interface in a block-level environment. Later, the same component can be used, without modification, in a system-level verification environment. A verification component must thus meet the different stimulus and monitoring requirements of a block-level environment and a system-level environment. This book describes methodologies to build, then leverage, verification components to reduce the verification effort and increase reusability.

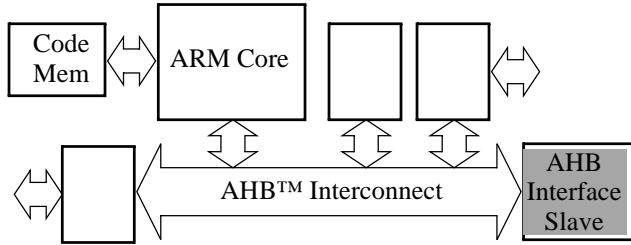

## Interface-Based Design

Nowadays, designs have external interfaces and on-chip buses which, in all likelihood, implement industry-standard protocols such as the AMBA™ Protocol Family, USB or Utopia. The benefits of standardized external interfaces and on-chip buses are well understood and include availability of design IP, reusability of existing validation components during design development and ease of understanding by engineers during development.

---

## Verification Components

---

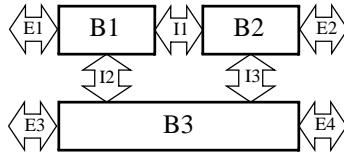

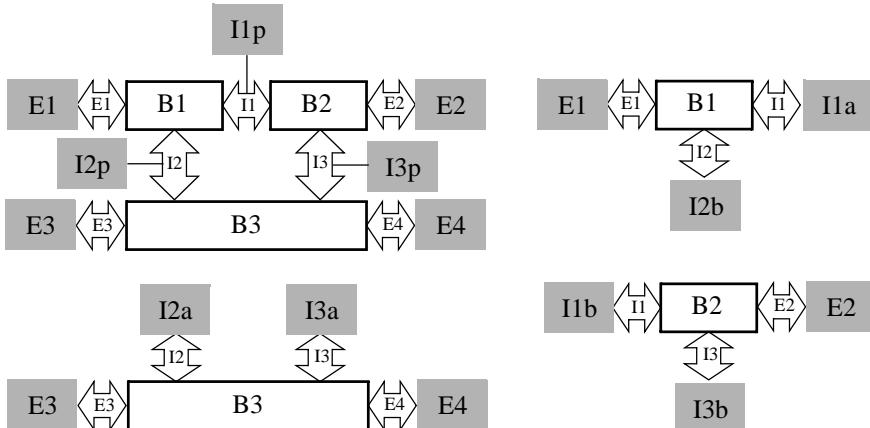

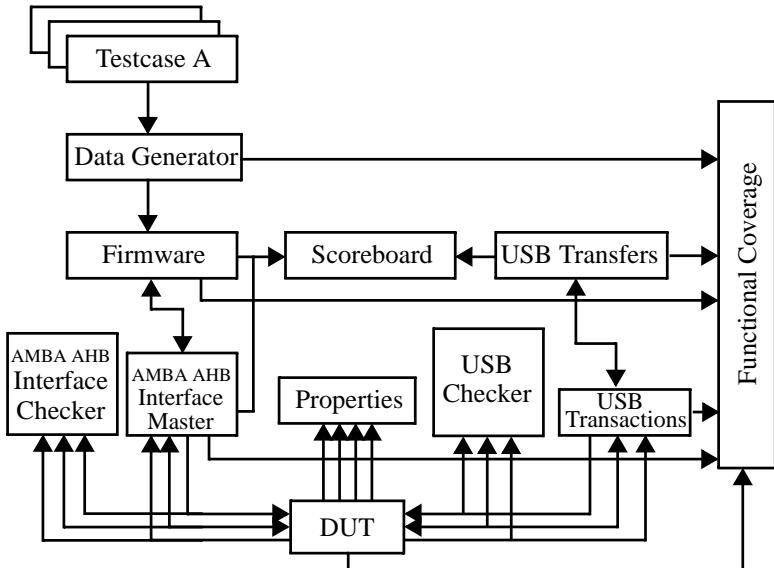

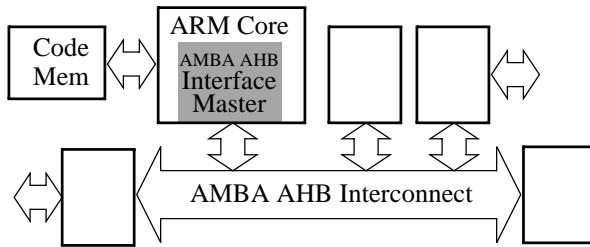

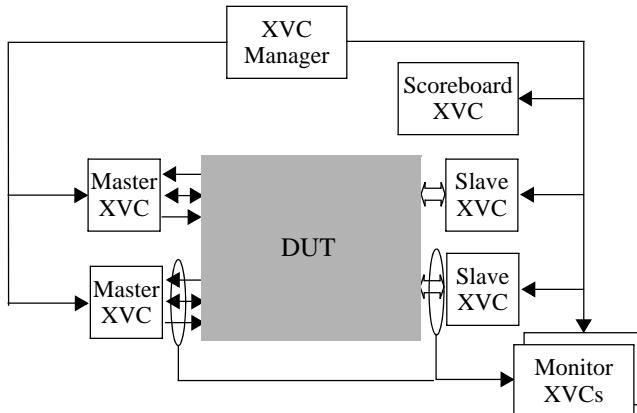

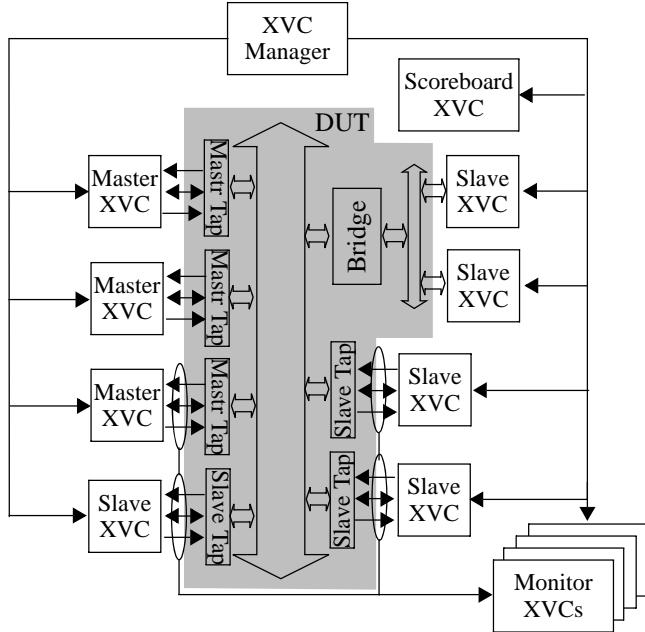

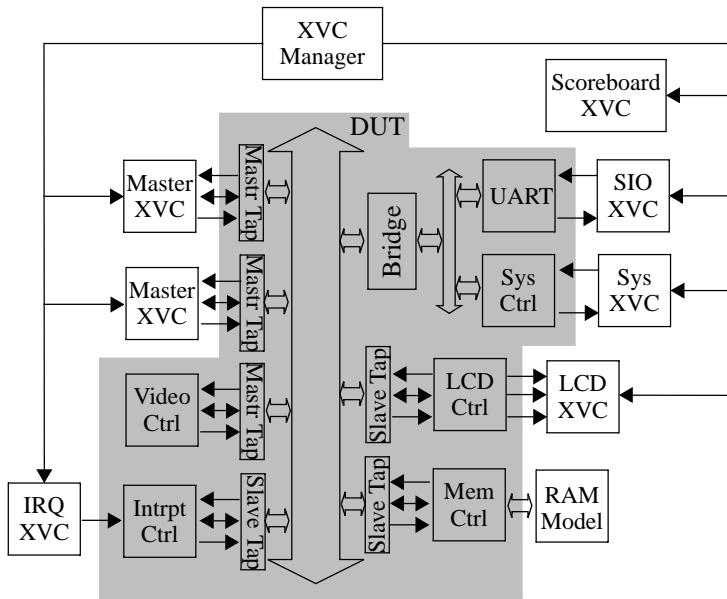

Early in the design process, functional partitioning takes place to make the detailed design phase both manageable and suitable for execution by an engineering team. As shown in Figure 1-1, this procedure introduces many new internal interfaces into the design.

**Figure 1-1.** Interface-Based Design

Being internal, design engineers are free to implement these interfaces. There can often be as many different implementations of interfaces as interfaces themselves. To validate a partitioned design, verification components are required to stimulate each internal interface from the perspective of each agent on that interface. The number of verification components required for a partitioned design is therefore potentially proportional to the number of interfaces, which in itself grows exponentially with the number of partitions. For example, verifying the partitioned design shown in Figure 1-1—with three internal interfaces and four external interfaces—requires 13 different verification components, as illustrated in Figure 1-2.

**Figure 1-2.** Verification Environments for Partitioned Design

An interface-based design methodology should have internal interfaces well specified early in the design process, aim to minimize the number of unique interfaces and leverage a library of common verification components. This approach will enable designers to concentrate on the value-add of the design while meeting the performance goals of the various interfaces.

## DESIGN FOR VERIFICATION

---

*Design for verification* is a response to the problems encountered when verifying the current (and future) complex microelectronics devices. Like *design for synthesis* and *design for test*, it requires a change in how designs are specified, captured and implemented.

Design for synthesis methodologies introduced, along with RTL-based specifications, specific hardware design language (HDL) coding styles and required synchronous designs. These restrictions allowed the use of a set of tools supporting the methodology—logic synthesis, cycle-based simulation, static timing analysis and equivalence checking—which contributed to increasing the overall design productivity.

Design for test separated testing for structural defects from verifying the functional aspects of the devices. These methodologies imposed further restrictions on the designs—synchronous interfaces, no clock gating, no latches and exclusive bus drivers—but also came with additional tool support. These methodological restrictions, coupled with the tools that supported them, helped improve the controllability and observability of internal structural failures to yield enormous gains in device reliability at a much lower cost.

Design for verification involves the designer in the verification process as early as possible, even before—and especially during—the design process itself. Small upfront investments by designers can reap a substantial reduction in the effort and time required to verify a design. Design for verification includes providing a way for the designer to express his or her intent concisely and naturally as part of the design process so that it can be objectively verified. To that end, SystemVerilog provides assertions to check the behavior and assumptions of the design and interface signals. It also provides specific language constructs—such as the `always_comb` block—to remove ambiguity and further specify the intent of the implementation code.

Design for verification also encourages designers to make architectural and design decisions that minimize the verification costs of the system. For example, a write-only and a read-only register can share the same address, but making every writable register readable helps in verifying that they can be written to correctly. Similarly, minimizing the number of unique internal interfaces and using industry standard external interfaces and on-chip buses, as mentioned in “Interface-Based Design” on page 4, helps minimize the number of verification components that must be created. The ability to preset large counters, bypass computation paths or force exception status bits can also greatly ease the verification process. These decisions may require the addition of nonfunctional features in the design.

Design for verification elements and features would not be exercised during the normal operations of the design. Some, such assertions, are usually removed from the final design by the synthesis process. However, these elements and features can help in on-chip diagnostics and debugging. For example, assertions may be synthesized into an emulated version of the design and their failure indication routed to a status register where they can generate an interrupt should they fail.

### The Benefit of Assertions

The three main sources of functional flaws in taped-out designs are design errors, specification errors and errors in reused modules and IP (either internal errors or incorrect usage). Most of these errors are due to ambiguous or changing specifications or unwritten or unverified assumptions on the behavior of surrounding blocks.

When creating the RTL implementation of a design, the designer often makes assumptions on the behavior of the surrounding designs and on internal synchronization. These assumptions are usually extraneous to the specification, unwritten and not verified during simulation. Any change in the behavior of the surrounding designs or functional errors in internal synchronization may violate these assumptions, which leads to failures. The symptoms of these failures may not be apparent until much later in the simulation—if at all—when the data affected by the failure reaches an observed output. These undocumented assumptions make the detection and the identification of the cause of a failure difficult and time consuming.

Designers should state such assumptions using assertions and insert them into the RTL code where these assumptions are used. A violation of these assumptions would cause an assertion failure near the point in space and time of the ultimate cause of the failure. This approach makes debugging the design that much easier.

A similar situation exists when reusing an existing module or IP block. If the assumptions on the usage of the module are not precisely stated and verified, errors may be difficult to identify due to the black-box nature of reused designs. Assertions can play an important role in specifying the usage rules of the module.

Temporal constructs, like those available in SystemVerilog, provide an efficient means for system architects to complement design specifications with non-ambiguous and executable statements in the form of properties that, when asserted, precisely express the intent or requirement of the specification. Such assertions reduce ambiguity and thus the chance of misinterpretation. Since properties are a different, more abstract description of the required behavior than the RTL specification of the design’s implementation, they increase the likelihood of detecting a design error

---

## Introduction

---

during simulation. Moreover, formal and hybrid (a combination of formal engines and simulation) tools can prove that the design does not violate some properties under any legal input stimulus.

Finally, properties can be used to describe interesting stimulus and states that should be covered during verification. These properties are not used to detect failures, but to detect the occurrence of some important condition. They specify corner cases created by the chosen implementation architecture that may not have been obvious based on the functional specification alone. A designer can thus contribute to the verification plan of a design by including coverage properties in the RTL design. Similarly, several compliance statements of standard protocols can be implemented using coverage properties.

# METHODOLOGY IMPLEMENTATION

---

The methodology presented in this book is quite extensive. It contains several different—but interrelated—facets and elements. The increase in productivity that can be obtained by this methodology comes from its breath and depth. It is not a methodology designed to be tidily presented in a 30-minute conference paper or three-page journal article on a toy example. It is designed to be scalable and applicable to real-life designs and systems.

The goal of the methodology is to obtain the maximum level of confidence in the quality of a design in a given amount of time and engineering resources. To accomplish this goal, it uses assertions, functional abstraction, automation through randomization and reuse techniques *all at the same time*. The guidelines presented in the subsequent chapters are designed to implement a verification process that combines all of these techniques to maximum effect.

It may be difficult to appreciate the usefulness of a particular set of guidelines without knowing the overall methodology implementation. But it is equally difficult to effectively implement a methodology without detailed guidelines to construct its basic elements. It may thus be beneficial to read this book twice: the first time to learn the overall methodology; the second time to learn its implementation details.

## Methodology Adoption

It is not necessary to adopt all the elements of the methodology presented in the following chapters. Obviously, maximum productivity is achieved when all of the synergies between the elements of the methodology are realized. But real projects, with real people and schedules, may not be able to afford the ramp-up time necessary

---

## Methodology Implementation

---

for a wholesale adoption. Individual elements of the methodology can still be adopted and provide incremental benefits to a project.

Many design teams already use assertions to detect errors in the design or interface signals. Many other books have already been written on their benefit. Adopting the methodology elements presented in Chapter 3 will accelerate their correct application, development and deployment. The same chapter also describes how to construct reusable assertion-based checkers that can be used without knowing the underlying assertion language, thus minimizing the cost of introducing assertions into an existing design methodology.

The message service, embodied in the `vmm_log` class described in “Message Service” on page 134, is the easiest one to adopt. It can immediately replace the message routines or packages that most teams develop for themselves. Its adoption requires no change in methodology and provides additional functionality at no cost. But unlike traditional message packages, it allows messages from verification components reused from different sources to be consistently displayed and controlled, without modifying the reused component itself.

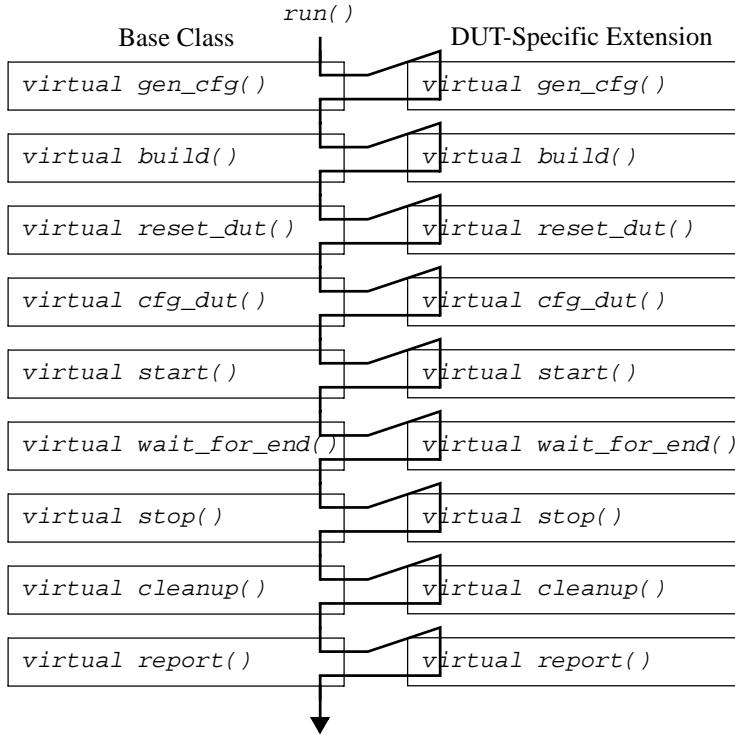

Formalizing the simulation steps described in “Simulation Control” on page 124, as embodied in the `vmm_env` base class, is the next natural adoption step. All simulations have to perform the same overall sequence of steps to successful completion. Instead of creating an arbitrary synchronization and sequencing scheme with each new verification environment, the `vmm_env` base class helps to formalize the execution steps in a consistent and maintainable fashion. Different block-level environments will be easier to combine to create system-level environments if they use a similar control mechanism. Formalizing the simulation steps allows different tests to intervene at the appropriate time, without ever violating the simulation sequence.

Modeling transactions using transaction descriptors and building all data models upon the `vmm_data` base class, as described in “Data and Transactions” on page 140, creates a uniform stimulus creation mechanism described in “Controlling Random Generation” on page 227. Whether transactions or data, all stimulus is created the same way. Both can be easily randomized and constrained using identical mechanisms. Different tests can apply different constraints without having to rewrite the random generator. Fully directed or partially directed transactions can also be easily created.

Once transactions and data are modeled as objects, interfacing transactors using `vmm_channels` as described in “Transaction-Level Interfaces” on page 171 and decoupling transactor functionality according to protocol and abstraction layers

---

## Introduction

---

comes next. Using these channels allows the creation of finer-grain plug-and-play transactors that can be reused across verification environments within the same project. Having a well-defined transaction-level interface mechanism enables the creation of transactors operating at higher level of abstraction without having to be associated with a physical level interface like traditional bus-functional models. It also enables the construction of verification environments along layers that can be built top-down—first on a transaction-level model of the DUT then adapted to a RTL model—or bottom-up—first verifying low-level operations then on to more complex and abstract functions.

A major step must be taken to adopt factory-patterned generators described in “Random Stimulus” on page 213 and callback methods in transactors as described in “Transactors” on page 161. But they offer the ability to create tests with fewer lines of codes in a single file, without modifying—and potentially breaking—code that is known to work. Tests can be written without affecting any of the already-written tests. And because tests can be written with so few lines to target a specific function of the device under test, it becomes cost effective to implement a true coverage-driven verification methodology. As a secondary benefit, generators and transactors that can meet the unpredictable needs of different tests, will be able to meet the needs of different verification environments or projects, making them truly reusable.

If the nature of the corner cases of the system depends on the synchronization of concurrent stimulus on multiple interfaces, adopting the extensible verification component (XVC) approach described in Chapter 8 becomes a good idea. Once the interesting stimulus parameters for an interface are known and implemented, it provides a natural command-based interface for writing system-level tests unlikely to occur spontaneously in a purely random environment. And should more stimulus parameters or patterns be required, they can be easily added to the environment without requiring modifications to the existing, working environment. It also creates an easy-to-learn test specification mechanism that can be used without being familiar with the details of the entire methodology or its implementation.

Formal tools are very effective in finding hard-to-identify or hard-to-reach corner-case bugs on complex control-dominated design blocks, such as arbiters, bus protocol controllers, instruction schedulers, pipeline controls, and so on. The RTL implementation of these structures is compared against a description of their expected behavior using assertions. When writing assertions that can be formally proven as well as simulated, the guidelines described in Chapter 7 become pertinent in addition to those in Chapter 3.

If there is any software component to the project, verifying the hardware/software interaction will require the adoption of the techniques described in Chapter 9.

## Guidelines

The purpose of this book is not to extol the virtues of SystemVerilog and the verification methodology it can support. Rather, like its predecessor the *Reuse Methodology Manual*, this book is focused on providing clear guidelines to help the reader make the most effective use of SystemVerilog and implement a productive verification methodology. The book does not claim that its methodology is the only way to use SystemVerilog for verification. It presents what the authors believe to be the best way.

Not all guidelines are created equal, and the guidelines in this book are classified according to their importance. More important guidelines should be adopted first, then eventually supported by a greater set of less important guidelines. However, it is important to recognize the synergies that exist among the guidelines presented in this book. Even if they are of lesser importance, adopting more of the guidelines will generally result in greater overall efficiency in the verification process.

**Rules** — A rule is a guideline that must be followed to implement the methodology. Not following a rule will jeopardize the productivity gains that are offered by other aspects of the methodology. *SystemVerilog Verification Methodology Manual*-compatibility (VMM-compatibility) requires adherence to all rules. VMM-compliance requires that all rules be followed.

**Recommendations** — A recommendation is a guideline that should be followed. In many cases, the detail of the guideline is not important—such as a naming convention—and can be customized. Adherence to all recommendations within a verification team or business unit is strongly recommended to ensure a consistent and portable implementation of the methodology.

**Suggestions** — Suggestions are recommendations that will make the life of a verification team easier. Like recommendations, the detailed implementation of a suggestion may not be important and may be customizable.

**Alternatives** — Alternatives provide different mechanisms for achieving similar results. Different alternatives may not be equally efficient or relevant and depend on the available verification components and the verification environment being constructed.

The guidelines in this book focus on the methodology, not the tools that support SystemVerilog or other aspects of this methodology. Additional guidelines may be required to optimize the methodology with a particular toolset.

## Basic Coding Guidelines

There is no value in reiterating generic coding guidelines—such as rules for indentation and commenting—that can be found in a variety of sources. All previous coding guidelines applicable to Verilog will remain applicable to SystemVerilog. However, the presence of high-level and verification-centric constructs in SystemVerilog require that some additional basic coding guidelines be specified.

**Recommendation 1-1** — *Unique prefixes or suffixes should be used to identify the construct that implements user-defined types.*

SystemVerilog has a rich set of user-definable types: *interface*, *struct*, *union*, *class*, *enums*. It may be difficult to know what construct is used to implement all user-defined types, and thus what are the allowed operations on objects of that type. Using a construct-specific prefix or suffix helps identify the underlying implementation.

**Example 1-1.** Using Unique Construct-Specific Suffixes

```

typedef enum ... states_e;

typedef struct ... header_s;

typedef union ... format_u;

class packet_c;

...

endclass: packet_c

interface mii_if;

...

endinterface: mii_if

```

**Recommendation 1-2** — *End tags should be used.*

SystemVerilog supports end tags on all of the named constructs that create a scope. Because there can be several dozens or hundreds of lines within that scope, indentation alone is often insufficient to clearly identify the matching opening and closing markers. By using end tags, associating a closing marker with its corresponding marker is much easier.

**Example 1-2.** Using End Tags

```

function compute_fcs(...);

...

if (...) begin: is_special

...

end: is_special

...

endfunction: compute_fcs

```

## Definition of Terms

Verification is about communication. A design must be unambiguously specified to be correctly implemented and verified against that specification. Verification often identifies miscommunication of intent among the various teams in a project. A book about verification must also be as unambiguous as possible. The following section defines the terminology used in this book. Other works may use the same terms to mean other things.

**Assertion** — A *property* that must hold true at all times. *if* statements and the entire verification environment can be considered assertions. But in this book, the term refers only to the behavior described using the *property* specification constructs.

**Assertion-based verification** — The systematic use of assertions to help identify design faults and specify assumptions on input signals.

**Assertion coverage** — A measure of how thoroughly an asserted *property* has been exercised. Does not imply any measure of functional intent. Part of *code coverage*.

**Bus-functional model** — A *transactor* with a physical-level interface.

**Code coverage** — A measure of the structural code constructs exercised during specific simulations. Includes several metrics, such as line coverage, path coverage, toggle coverage, expression coverage and *assertion coverage*.

**Checker** — A *verification component* that verifies the correctness of a protocol. Low-level checkers are usually implemented using *assertions*. Checkers may be combined with *monitors*.

**Class property** — A data member in a *class* type declaration.

**Constrained-random** — A modification of a verification environment, through additional constraints, to increase the likelihood that specific *stimulus* will be generated.

**Coverage** — A measure of progress of the verification process. Includes several coverage metrics, such as *code coverage*, *functional coverage* and *FSM coverage*.

**Coverage property** — A *property* that, when true, indicates that an interesting condition has occurred. The occurrence is recorded in a database for later analysis. Coverage properties can be used to implement *functional coverage points*.

**Cross coverage** — The combination of two or more coverage metrics to measure their relative occurrences. Cannot be used to combine heterogeneous coverage measurements, such as *code coverage* and *functional coverage*.

**Data protection class property** — A class data member implementing a protocol mechanism used to detect, and sometimes repair, errors in data or a transaction. FCS, CRC and HEC fields are examples of data protection class properties.

**Design for test** — Nonfunctional design requirements and activities to make structural testing of the manufactured design easier.

**Design for verification** — Nonfunctional design requirements and activities to make functional verification easier. Includes *assertion-based verification*.

**Directed random** — A synonym for *constrained-random*.

**Directed testbench** — *Testbench* specified using hand-crafted stimulus. Usually contains a hand-crafted description of the expected response as well. May include some random data for the irrelevant portions of the stimulus that do not affect the outcome of the feature targeted by the *testcase*. May be implemented on top of a *random verification environment*.

**Discriminant class property** — A class data member, usually randomized, whose value determines the presence or absence of additional data representing different data or transaction formats.

**FSM coverage** — A measure of the visited states and transitions observed on a finite-state machine during specific simulations. Can be automatically extracted from the FSM implementation or independently specified.

**Formal verification** — A mathematical comparison of an implementation against a specification or requirement to determine if the implementation can violate its specification or requirement.

**Functional coverage** — A measure of the *testcases* and interesting conditions that were observed as having been exercised on the design (e.g., corner cases, applied input scenarios, and so on.)

**Functional coverage point** — A specific testcase or interesting condition that must be observed as having been exercised on the design.

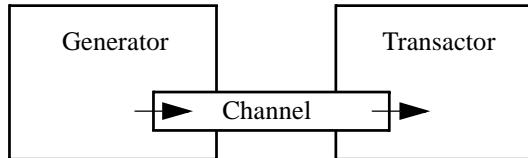

**Generator** — A *proactive transactor* that autonomously generates *stimulus*.

---

**Monitor** — A *reactive* or *passive transactor* that autonomously reports observed data or transactions. May include a *checker* or equivalent checking functionality for the observed protocol, but not the data or transactions transported by the protocol.

**Passive transactor** — A *transactor* that strictly observes the design under verification or lower-level transactors. It has no control of the timing and initiation of transactions. May include *functional coverage points*. See *reactive transactor* and *proactive transactor*.

**Proactive transactor** — A *transactor* that provides stimulus to the design under verification or a lower-level transactor and is under full control of the timing and initiation of transactions. See *reactive transactor*.

**Property** — A specification of functional behavior using a sequence of Boolean expressions. Properties can be used to specify events, conditions that must always hold true or functional coverage points.

**Random environment** — Synonym of *verification environment*.

**Reactive transactor** — A *transactor* that provides stimulus to the design under verification or a lower-level transactor but has no control over the initiation of transactions. It may have limited control over the timing of certain elements of transaction initiated by the DUT or lower-level transactor, such as the insertion of wait states. See *proactive transactor* and *passive transactor*.

**Scenario** — A sequence of random or directed stimulus that is particularly interesting to the device under test. A scenario is unlikely to be spontaneously generated with individually constrained-random stimulus. Multiple scenarios are applied to the device under test during a single simulation.

**Simulation** — A run, with a specific seed and set of source files, of a model and associated testbench, resulting in a specific set of output messages and coverage metrics.

**Stimulus** — Input to the design under verification. Includes, but is not limited to, configuration information, transactions, instructions, exceptions and injected protocol errors.

**Structural coverage** — A synonym for *code coverage*.

**System** — A design composed of independently verified sub-designs. A system may go on to become an independently verified design in a super-system.

**Test** — A synonym for *testcase*.

**Testcase** — A requirement of the functional verification process. Usually corresponds to an interesting feature or corner condition of the design that must be verified.

**Testbench** — A complete verification environment applying *stimulus* and checking the response of a design to implement one or more *testcases*. A *testcase* can be verified using a *directed testbench* or *constrained-random* testbench with *functional coverage*.

**Testing** — The process to determine that a physical device was correctly manufactured without defects, according to a specific implementation.

**Transaction** — An operation on an interface. A transaction can be abstract and high-level—such as the reliable transmission of a TCP packet—or physical—such as a write cycle on a APB™ interconnect.

**Transactor** — A *verification component* of a *verification environment*. A transactor is a static object that autonomously generates, processes or monitors *transactions*. Bus-functional models are transactors—but transactors are not limited to bus-functional models. See *proactive transactor*, *reactive transactor* and *passive transactor*.

**Validation** — The process to determine that a specification meets its functional and market requirements.

**Verification** — The process to determine that an implementation meets its specification.

**Verification component** — A potentially reusable component of a *verification environment*. See *transactor*.

**Verification environment** — Verification automation, abstraction and response checking environment used to verify a specific design. Can be used to implement *constrained-random* simulations. Can be used to implement *directed testbenches*.

---

## CHAPTER 2      VERIFICATION PLANNING

---

As stated in the previous chapter—and in several other published works—more effort is required to verify a design than to write the RTL code for it. As early as 1974, Brian Kernighan, creator of the C language, stated that “*Everyone knows debugging is twice as hard as writing a program in the first place.*” A lot of effort goes into specifying the requirements of the design. Given that verification is a larger task, even more effort should go into specifying how to make sure the design is correct.

Every design team signs up for first-time success. No one plans for failures and multiple design iterations. But how is *first-time success* defined? How can resources be appropriately allocated to ensure critical functions of the design are not jeopardized without a definition of what functionality is critical? The *verification plan* is that specification. And that plan must be based on the intent of the design, not its implementation. Of course, corner cases created by the implementation, which are not apparent from the initial intent, have to be verified but that should be done once the initial intent-based verification plan has been completed.

This chapter will be of interest to verification lead engineers and project managers. It will help them define the project requirements, allocate resources, create a work schedule and track progress of the project of time. Examples in this chapter are based on OpenCore *Ethernet IP Core Specification*, Revision 1.19, November 27, 2002. This document can be found in the Examples section of the companion Web site:

<http://vmm-sv.org>

## PLANNING PROCESS

---

The traditional approach of writing verification plans should be revised to take advantage of new verification technologies and methodologies. The new verification constructs in SystemVerilog offer new promises of productivity but only if the verification process is designed to take advantage of them. Individual computers, like individual language features, can improve the productivity of the person sitting in front of it. But taking advantage of the network, like the synergies that exist among those language features, can be achieved only by redesigning the way an entire business processes information; and it can dramatically improve overall efficiency.

The traditional verification planning process—when there is one— involves identifying testcases targeting a specific function of the design and describing a specific set of stimulus to apply to the design. Sometimes, the testcase may be self-checking and looks for specific symptoms of failures in the output stream observed from the design. Each testcase is then allocated to individual engineers for implementation. Other than low-level bus-functional models directly tied to the design's interface, little is reused between testcases. This approach to verification is similar to specifying a complete design block by block and hoping that, once put together, it will meet all requirements.

A design is specified in stages: first requirements, then architecture and finally detailed implementation. The verification planning process should follow similar steps. Each step may be implemented as separate cross-referenced documents, or by successive refinement of a single document.

### Functional Verification Requirements

The purpose of defining functional verification requirements is to identify the verification requirements necessary for the design to fulfill the intended function. These requirements will form the basis from which the rest of the verification planning process will proceed. These requirements should be identified as early as possible in the project life cycle, ideally while the architectural design is being carried out. It should be part of a project's technical assessment reviews.

It is recommended that the requirements be identified and reviewed by a variety of stakeholders from both inside and outside the project team. The contributors should include experienced design, verification and software engineers so that the requirements are defined from a hardware and a software perspective. The reviews are designed to ensure that the identified functional verification requirements are complete.

**Rule 2-1** — *A definition of what the design does shall be specified.*

Defining what the design does—what type of input patterns it can handle, what errors it can sustain—is part of the verification requirements. These requirements ensure that the design implements the intended functionality. These requirements are based on a functional specification document of the design agreed upon by the design and verification teams.

These requirements are outlined, separate from the functional specification document.

**Example 2-1.** Ethernet IP Core Verification Requirements

R3.1/14/0 Packets are limited to MAXFL bytes

R3.1/13/0 Does not append a CRC

R3.1/13/1 Appends a valid CRC

R4.2.3/1 Frames are transmitted

**Rule 2-2** — *A definition of what the design must not do shall be specified.*

Defining what makes the behavior of the design incorrect is also part of the verification requirements. These requirements ensure that functional errors in the design will not go unnoticed. The section titled "Response Checking" on page 31 specifies guidelines on how to look for errors.

A functional specification document is concerned with specifying the intended behavior. That is captured by Rule 2-1. Verification is concerned with detecting errors. But it can only detect errors that it is looking for. The verification requirements must outline which errors to look for. There is an infinite number of ways something can go wrong. The verification requirements enumerate only those errors that are relevant and probable, given the functionality and architecture of the design.

**Rule 2-3** — *Any functionality not covered by the verification process shall be defined.*

It is not possible to verify the behavior of the design under conditions it is not expected to experience in real life. The conditions considered to be outside the usage space of the design must be outlined to clearly delineate what the design is and is not expected to handle.

For example, a datacom design may be expected to automatically recover from a parity error, a complete failure of the input protocol or a loss of power. But a

---

## Verification Planning

---

processor may not be expected to recover from executing invalid instruction codes or a loss of program memory.

**Example 2-2.** Ethernet IP Core Verification Requirements

- R3.1/9/0    Frames are lost only if attempt limit is reached

- R4.2.3/2    Frames are transmitted in BD order

**Rule 2-4 —** *Requirements shall be uniquely identified.*

Each verification requirement must have a unique identifier. That identifier can then be used in cross-referencing the functional specification document, testcase implementation and functional coverage points.

**Rule 2-5 —** *Requirement identifiers shall never be reused within the same project.*

As the project progresses and the design and verification specifications are modified, design requirements will be added, modified or removed. Corresponding verification requirements will have to be added, modified or removed. When adding new requirements, never reuse the identifier of previously removed verification requirements to avoid confusion between the obsolete and new requirements.

**Rule 2-6 —** *Requirements shall refer to the design requirement or specification documents.*

The completeness of the functional verification requirements is a critical aspect of the verification process. Any verification requirement that is missing may cause a functional failure in the design to go unnoticed. Cross-referencing the functional verification requirements with the design specification will help ensure that all functional aspects of the design are included in the verification plan.

Furthermore, verification is complex enough without verifying something that is not ultimately relevant to the final design. If something is not specified, don't verify it. Do not confuse this idea with an incomplete specification. The former is a "don't care." The latter is a problem that must be fixed.

**Recommendation 2-7 —** *Requirements should be ranked.*

Not all requirements are created equal. Some are critical to the correct operation of the design, others may be worked around if they fail to operate. Yet others are optional and included for speculative functionality of the end product.

Ranking the requirements lets them be prioritized. Resources should be allocated to the most important requirements first. The decision to tape-out the design should similarly be taken when the most important functional verification requirements have been met.

**Example 2-3.** Ethernet IP Core Verification Requirements Ranking

|           |                                    |               |

|-----------|------------------------------------|---------------|

| R3.1/14/0 | Packets are limited to MAXFL bytes | <b>SHOULD</b> |

| R3.1/14/1 | Packets can be up to 64kB          | <b>SHOULD</b> |

| R3.1/14/2 | Packets can be up to 1500 bytes    | <b>MUST</b>   |

**Recommendation 2-8** — *Requirements should be ordered.*

Many requirements depend on the correct operation of other requirements. The latter requirements must be verified first. Dependencies between requirements should be documented.

For example, verifying that all configuration registers can be correctly written to must be completed before verifying the different configurations.

**Example 2-4.** Ethernet IP Core Verification Requirements Order

|           |                                 |