R. Castro-López

F.V. Fernández

O. Guerra-Vinuesa

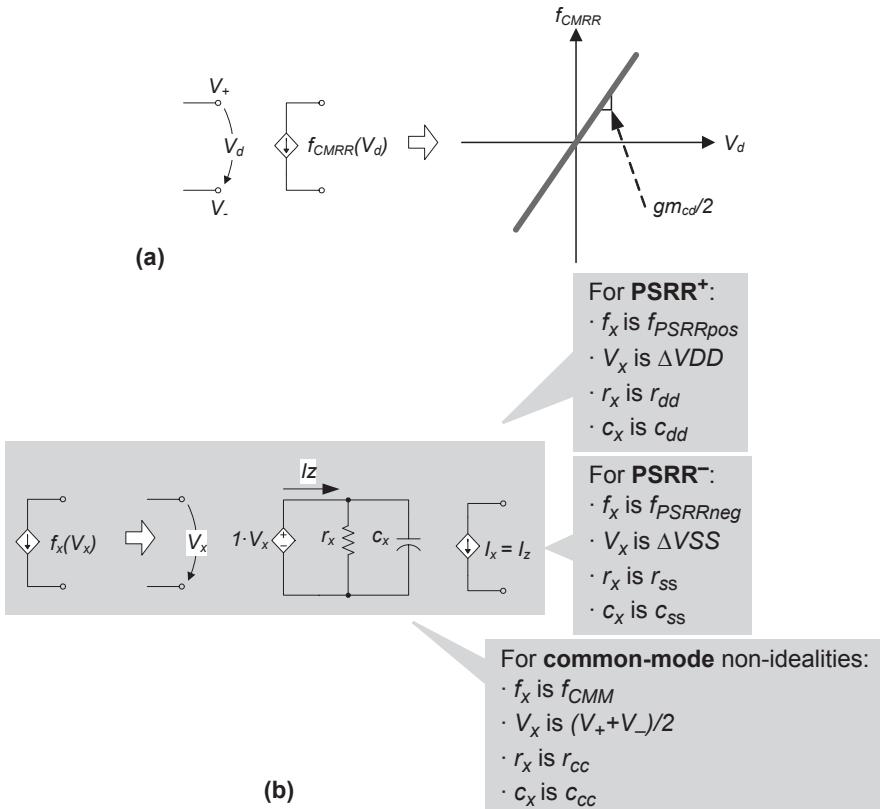

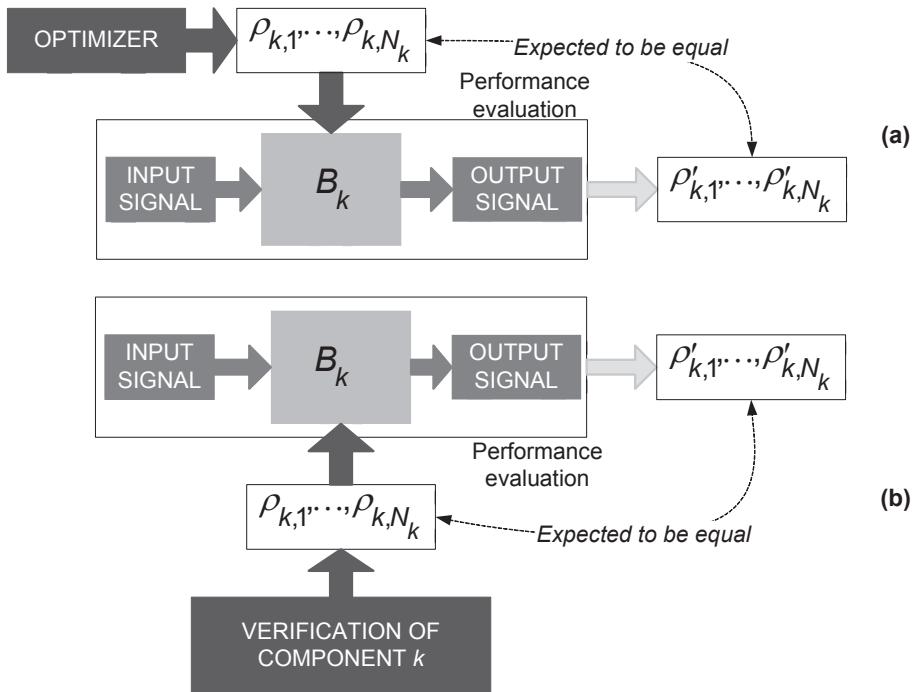

Á. Rodríguez-Vázquez

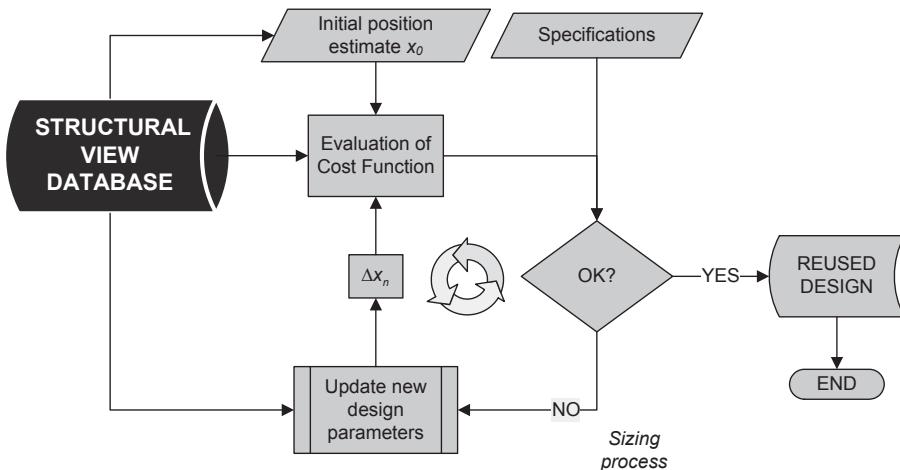

# Reuse-Based Methodologies and Tools in the Design of Analog and Mixed-Signal Integrated Circuits

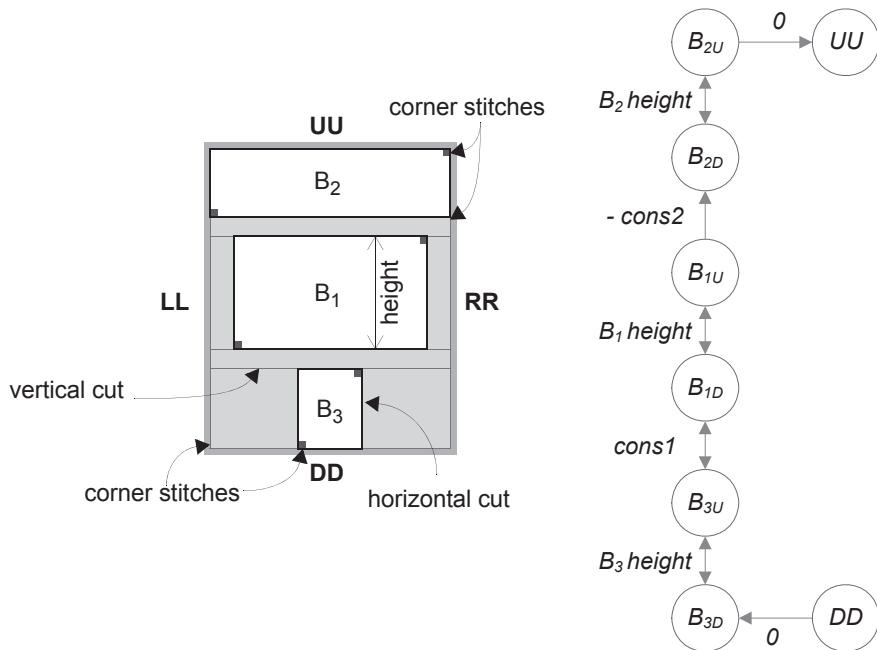

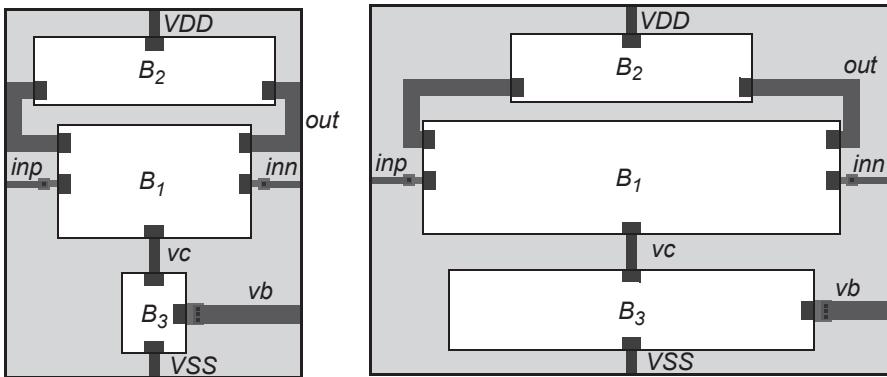

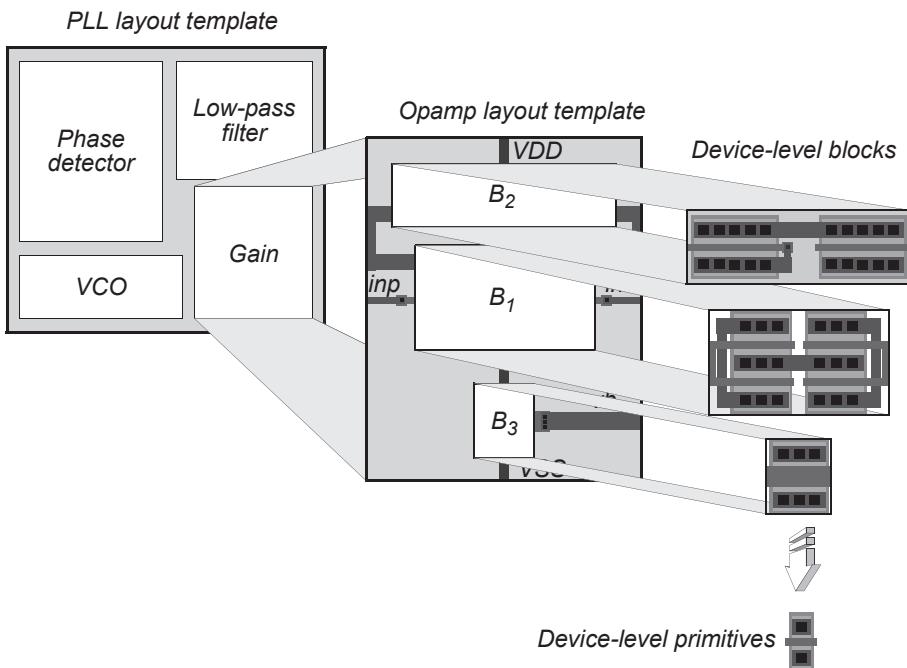

REUSE-BASED METHODOLOGIES AND TOOLS IN THE DESIGN

OF ANALOG AND MIXED-SIGNAL INTEGRATED CIRCUITS

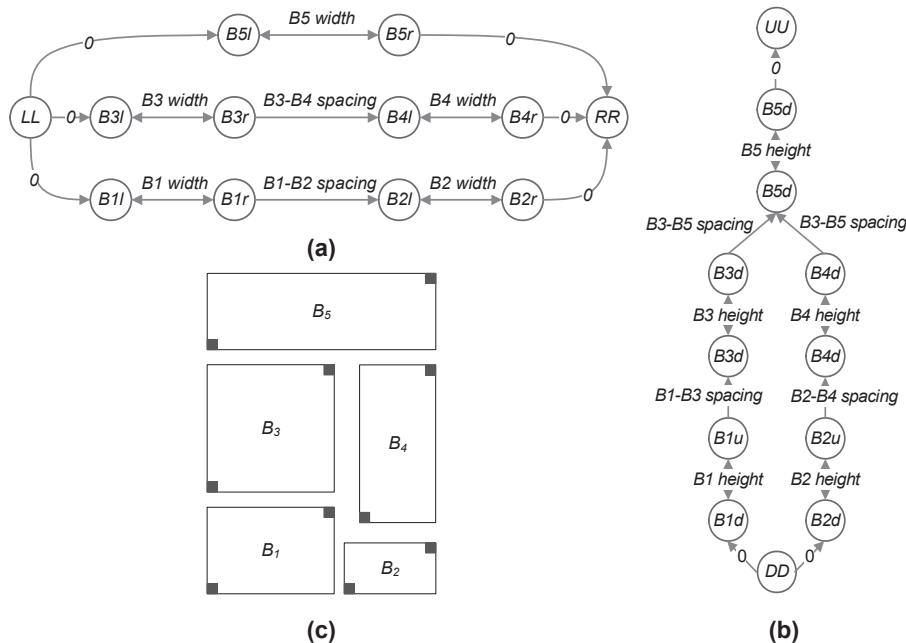

# Reuse-Based Methodologies and Tools in the Design of Analog and Mixed-Signal Integrated Circuits

by

R. CASTRO-LÓPEZ

*IMSE-CNM-CSIC,*

*Spain*

F.V. FERNÁNDEZ

*University of Seville, IMSE-CNM-CSIC,*

*Spain*

O. GUERRA-VINUESA

*University of Seville,*

*Spain*

and

Á. RODRÍGUEZ-VÁZQUEZ

*University of Seville,*

*Spain*

Springer

A C.I.P. Catalogue record for this book is available from the Library of Congress.

ISBN-10 1-4020-5126-3 (HB)

ISBN-13 978-1-4020-5126-5 (HB)

ISBN-10 1-4020-5139-5 (e-book)

ISBN-13 978-1-4020-5139-5 (e-book)

---

Published by Springer,

P.O. Box 17, 3300 AA Dordrecht, The Netherlands.

*www.springer.com*

*Printed on acid-free paper*

All Rights Reserved

© 2006 Springer

No part of this work may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, microfilming, recording or otherwise, without written permission from the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work.

Printed in the Netherlands.

***Rafael Castro López***

*To my family and friends*

***Francisco V. Fernández***

*To Eli, Judit, and Nuria*

***Óscar Guerra Vinuesa***

*To my wife and daughters*

***Ángel Rodríguez Vázquez***

*To my former doctoral students and current friends*

# Contents

|                                                        |           |

|--------------------------------------------------------|-----------|

| Preface                                                | xi        |

| <b>1 INTRODUCTION</b>                                  | <b>1</b>  |

| 1    Problem overview: The design gap                  | 1         |

| 1.1    Evolution of the semiconductor industry         | 1         |

| 1.2    The design gap                                  | 5         |

| 1.2.1    Time-to-market                                | 7         |

| 1.2.2    Design complexity                             | 8         |

| 1.3    Analog design automation                        | 10        |

| 2    Problem definition                                | 14        |

| 2.1    Hierarchy, abstraction, and views               | 14        |

| 2.2    The AMS design flow                             | 16        |

| 3    Summary                                           | 25        |

| <b>2 A REUSE-BASED DESIGN FRAMEWORK FOR ANALOG ICs</b> | <b>27</b> |

| 1    Design automation                                 | 27        |

| 1.1    Preliminary definitions                         | 28        |

| 1.2    The two sides of automation                     | 29        |

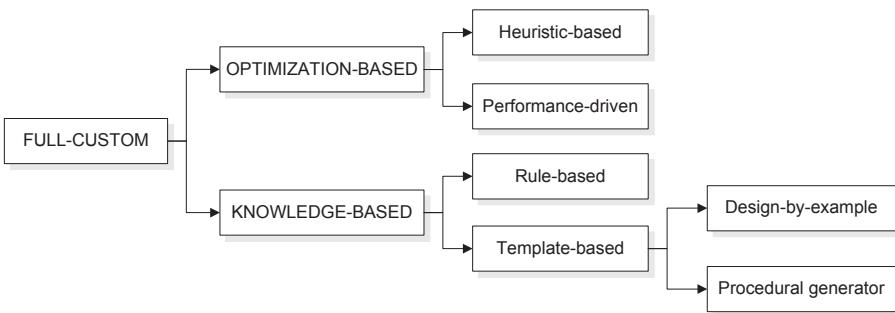

| 1.2.1    Knowledge-based synthesis                     | 30        |

| 1.2.2    Optimization-based synthesis                  | 31        |

| 1.2.3    Quality metrics for analog synthesis          | 34        |

| 1.3    Knowledge versus optimization-based synthesis   | 35        |

| 2    Circuit reuse                                     | 38        |

| 2.1    Preliminary definitions                         | 38        |

| 2.2    Digital design reuse                            | 41        |

| 2.3    Analog design reuse                             | 42        |

| 2.4    Other approaches to analog reuse                | 45        |

|          |                                                                   |           |

|----------|-------------------------------------------------------------------|-----------|

| 3        | The reuse-based design framework                                  | 49        |

| 3.1      | The analog reusable block                                         | 51        |

| 3.2      | The design reuse flow                                             | 54        |

| 3.2.1    | Adopted synthesis approaches                                      | 54        |

| 3.2.2    | The top-down path                                                 | 56        |

| 3.2.3    | The bottom-up path                                                | 58        |

| 3.2.4    | The role of the analog reusable block                             | 59        |

| 3.3      | The design for reusability methodology                            | 60        |

| 4        | Summary                                                           | 62        |

| <b>3</b> | <b>THE ANALOG REUSABLE BLOCK: BEHAVIORAL FACET</b>                | <b>63</b> |

| 1        | Introduction: Why behavioral descriptions?                        | 63        |

| 1.1      | Analog behavioral modeling taxonomy                               | 66        |

| 2        | Facing design reuse                                               | 68        |

| 2.1      | The design reuse flow: top-down electrical synthesis              | 68        |

| 2.2      | The design reuse flow: bottom-up verification                     | 72        |

| 2.3      | Characteristics of the behavioral facet of the AMS reusable block | 73        |

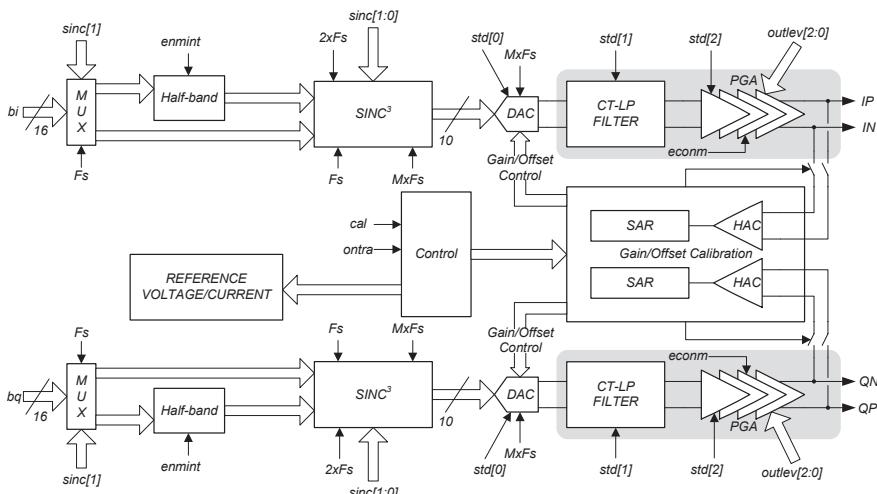

| 3        | Case study: a quadrature DA transmit interface                    | 76        |

| 3.1      | System description                                                | 76        |

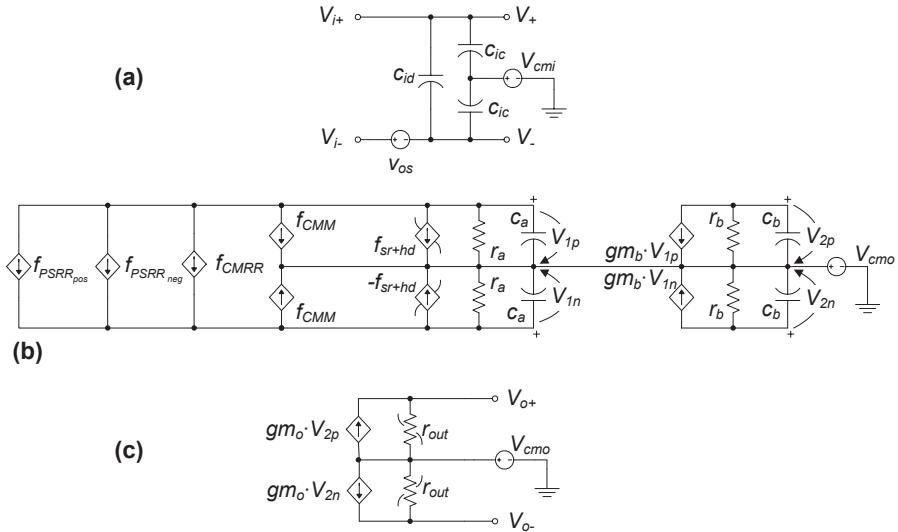

| 3.2      | Reusable macromodels                                              | 79        |

| 4        | Summary                                                           | 88        |

| <b>4</b> | <b>THE ANALOG REUSABLE BLOCK: STRUCTURAL FACET</b>                | <b>89</b> |

| 1        | Introduction                                                      | 89        |

| 1.1      | Adopted sizing approach                                           | 92        |

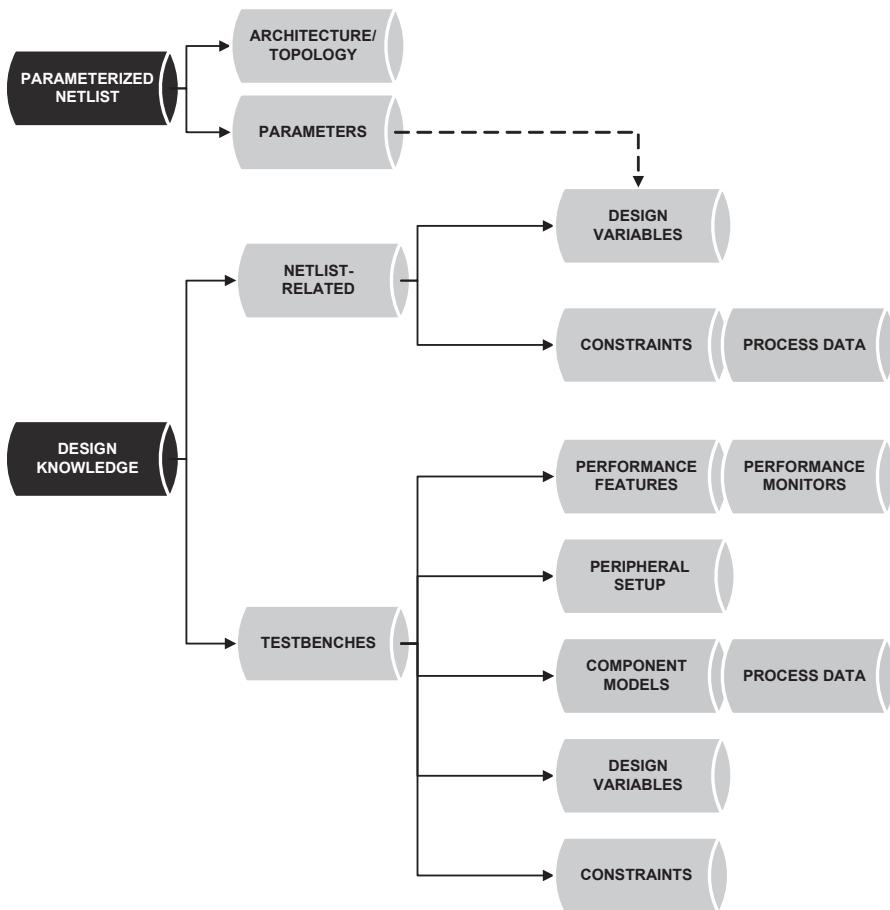

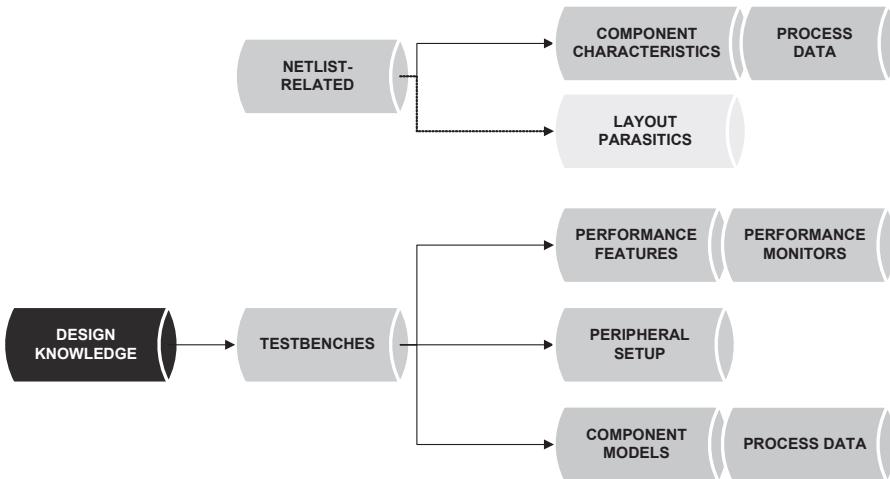

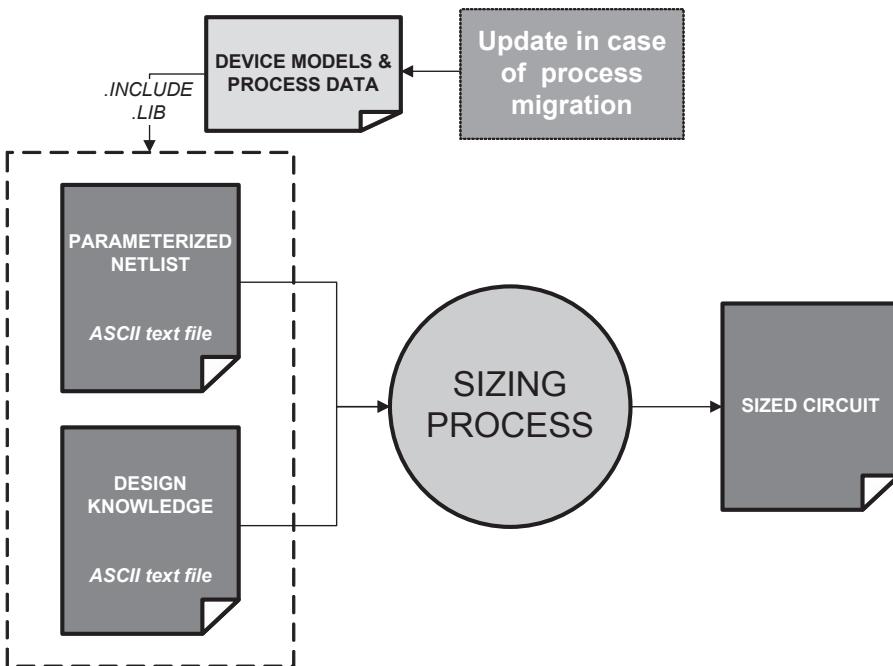

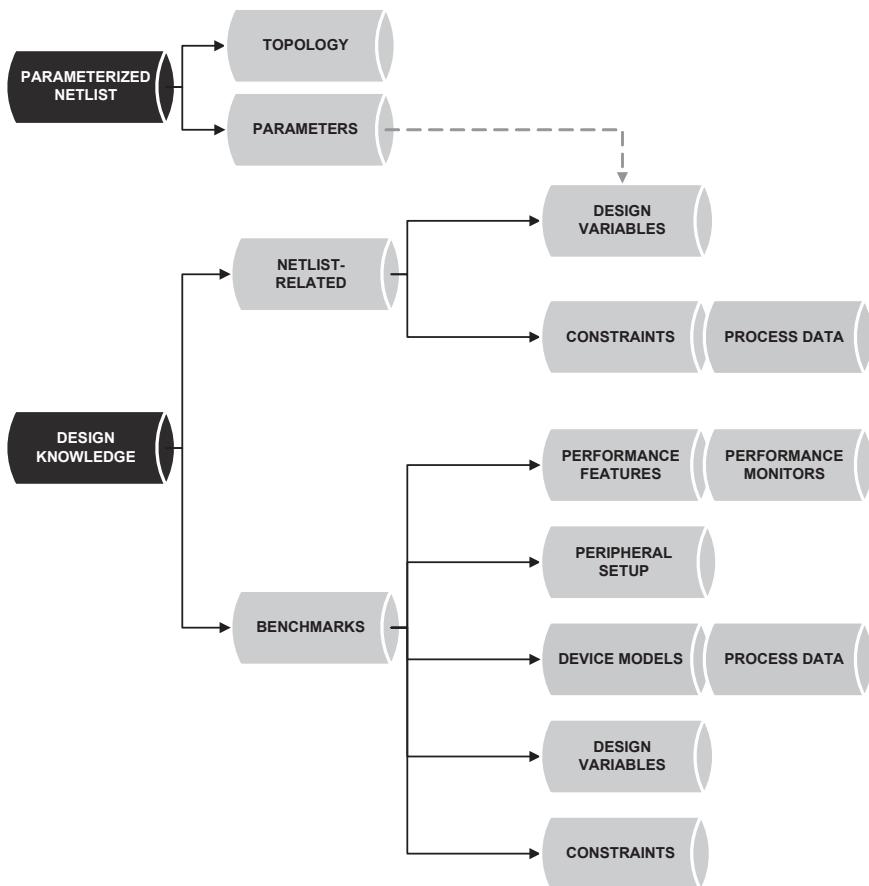

| 2        | Design knowledge encapsulation                                    | 93        |

| 2.1      | Netlist-related elements                                          | 96        |

| 2.1.1    | Design variables                                                  | 97        |

| 2.1.2    | Constraints                                                       | 100       |

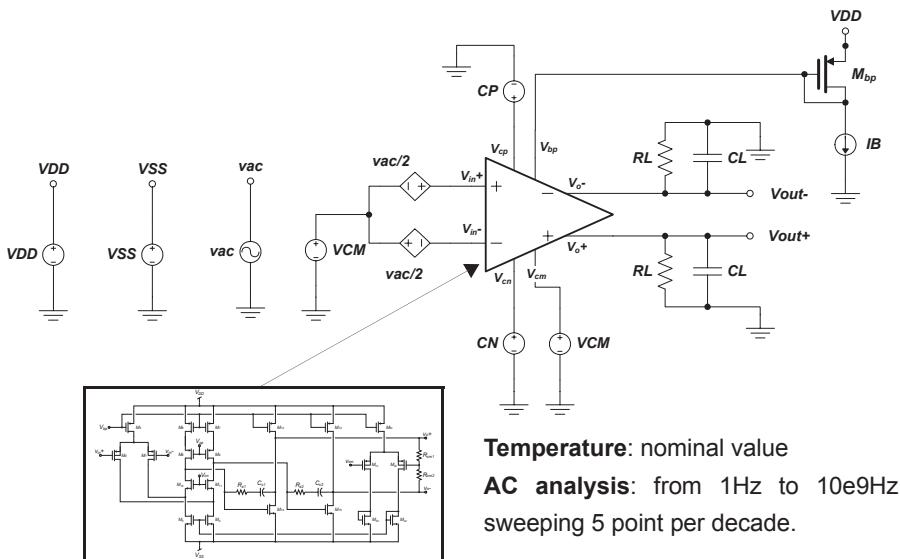

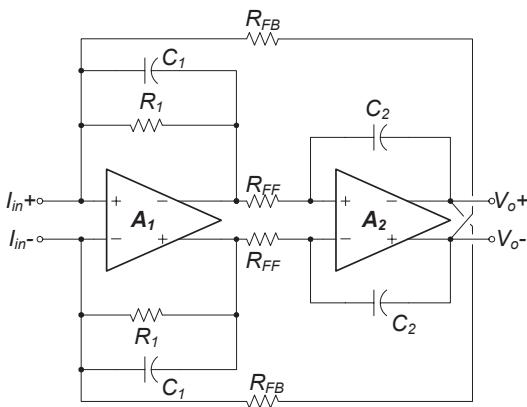

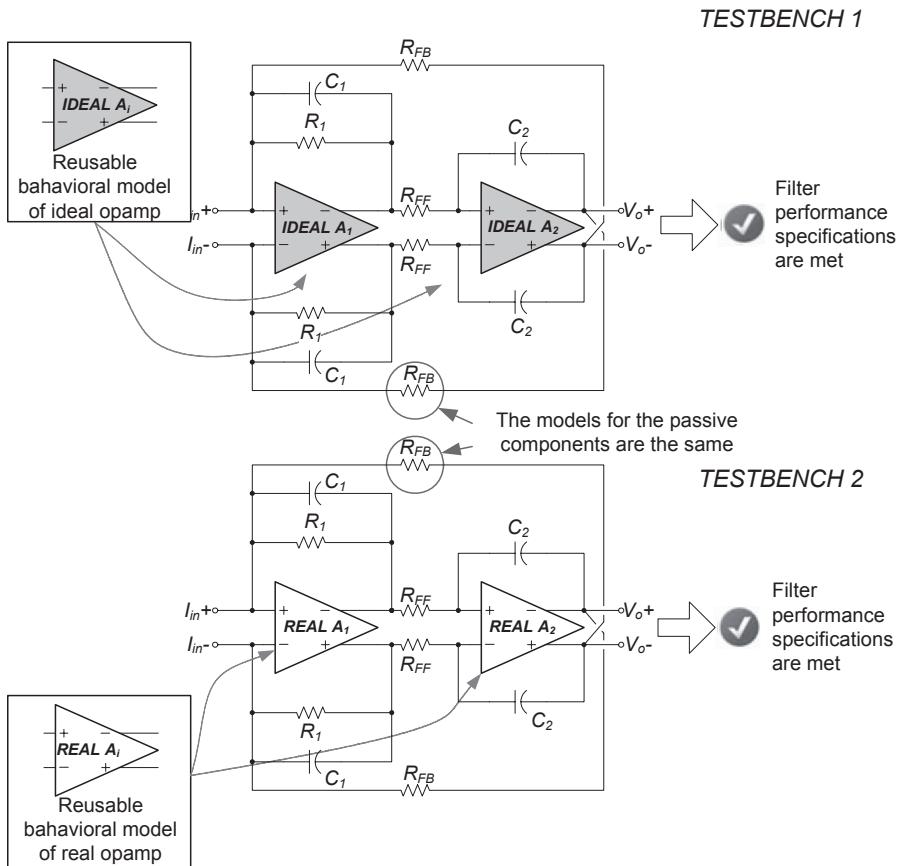

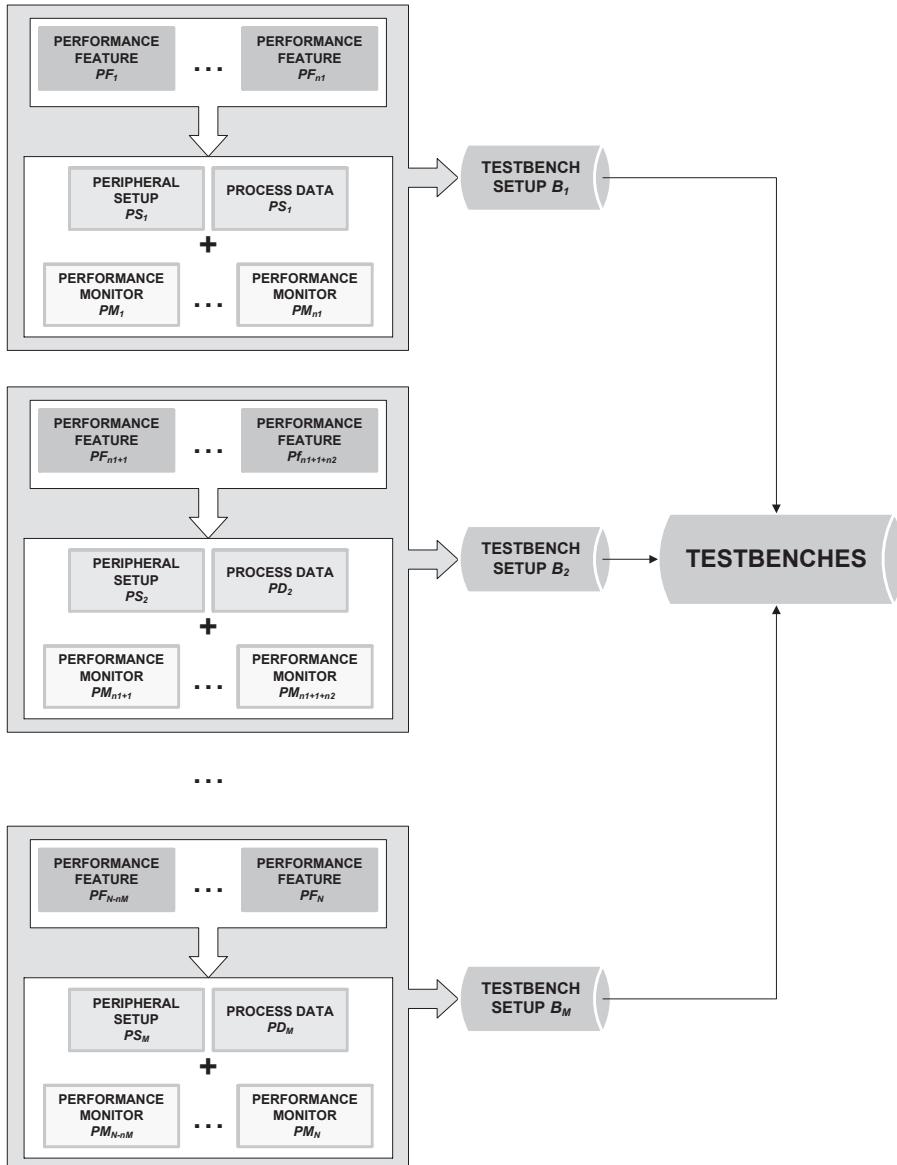

| 2.2      | Testbench setups                                                  | 105       |

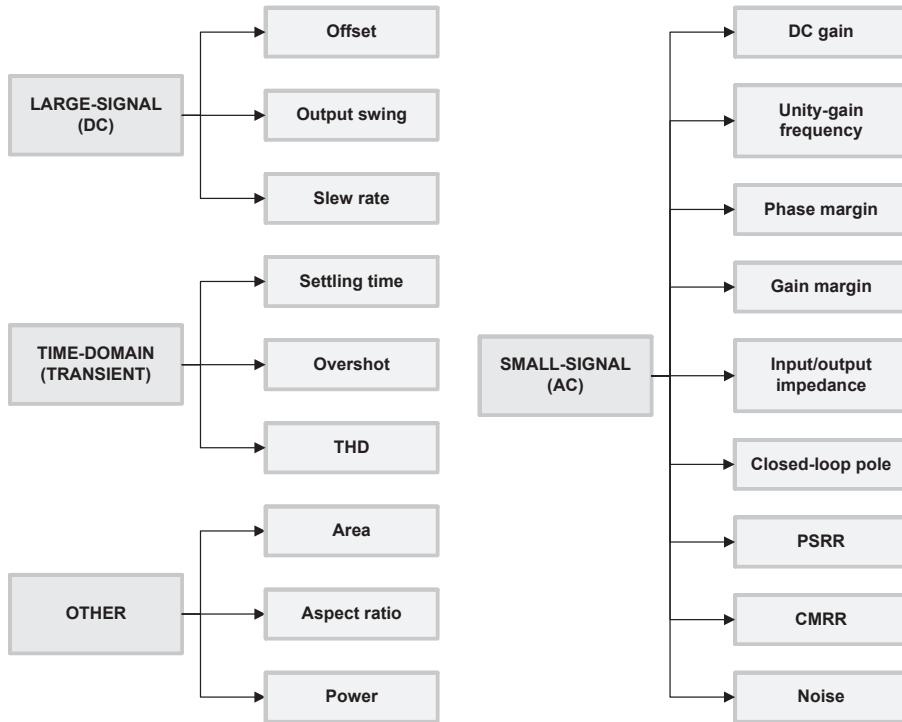

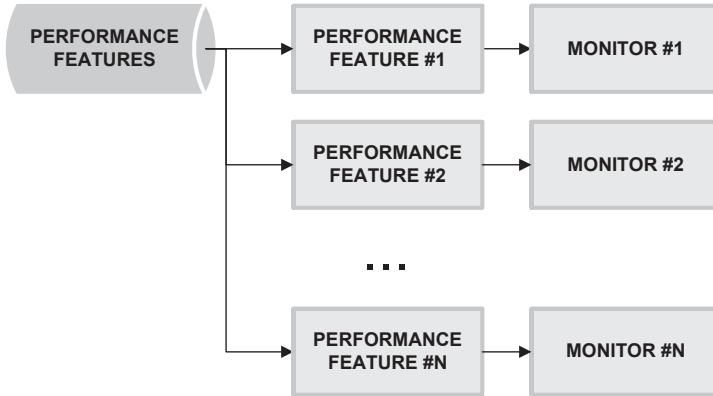

| 2.2.1    | Performance feature elements                                      | 106       |

| 2.2.2    | Peripheral setup elements                                         | 109       |

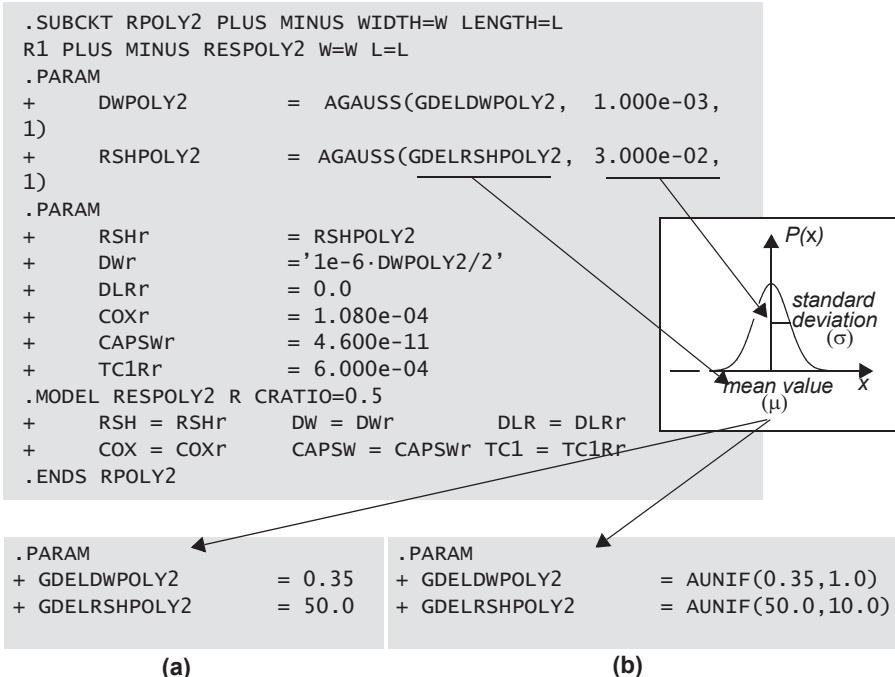

| 2.2.3    | Component model and process data elements                         | 111       |

| 2.2.4    | Design variables, dependent variables, and constraints            | 113       |

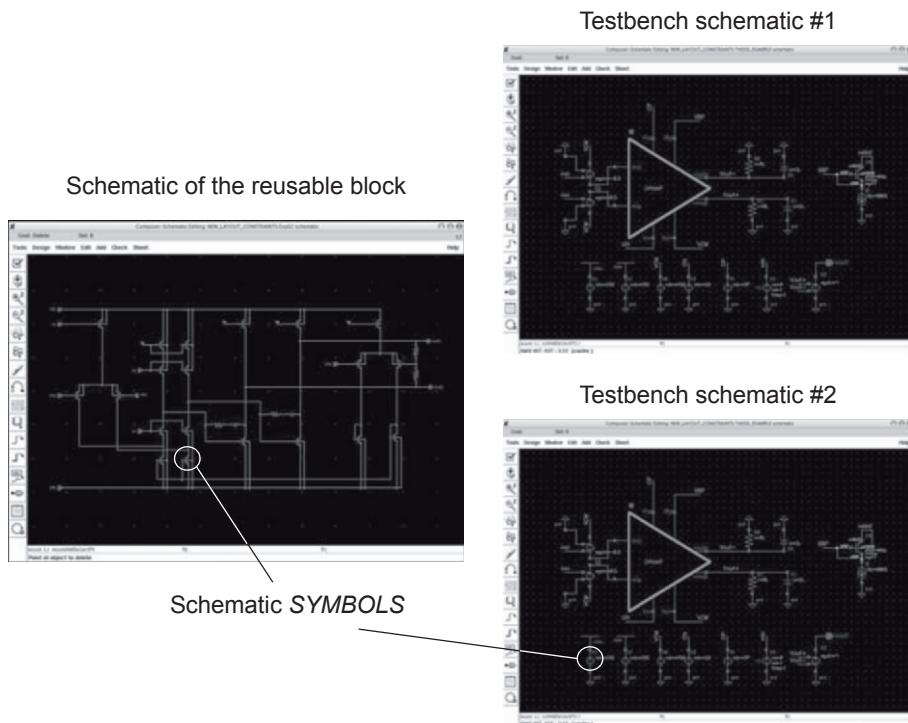

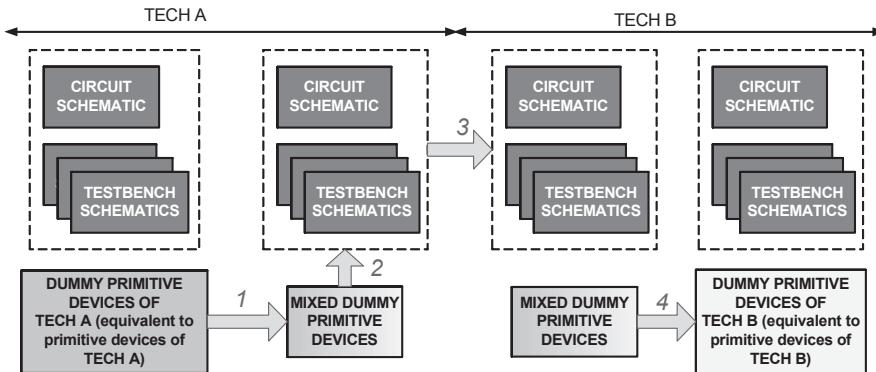

| 3        | Practical aspects of structural view reuse                        | 117       |

| 4        | Summary                                                           | 122       |

|                                                                        |            |

|------------------------------------------------------------------------|------------|

| <b>5 THE ANALOG REUSABLE BLOCK: LAYOUT FACET</b>                       | <b>123</b> |

| 1    Introduction                                                      | 123        |

| 2    Layout retargeting                                                | 125        |

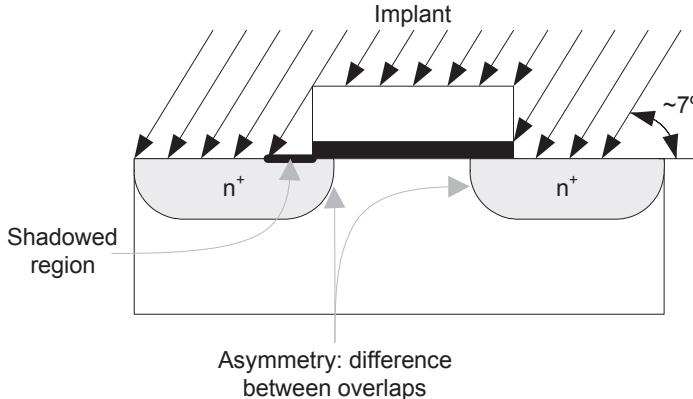

| 2.1    Device mismatch                                                 | 125        |

| 2.2    Loading effects                                                 | 128        |

| 2.3    Coupling effects                                                | 129        |

| 2.4    Reliability                                                     | 130        |

| 2.5    Area occupation                                                 | 131        |

| 3    Layout migration                                                  | 132        |

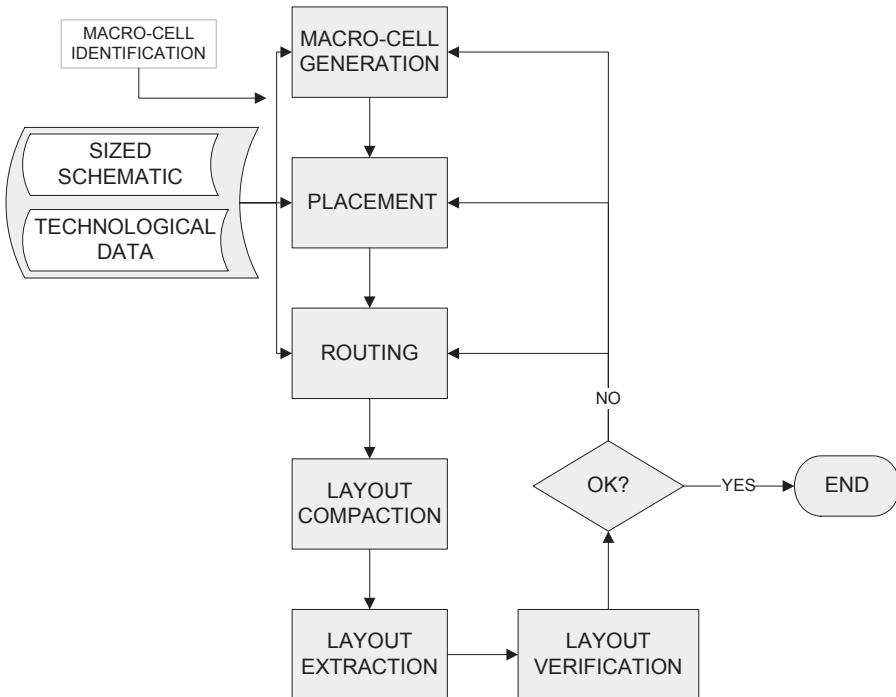

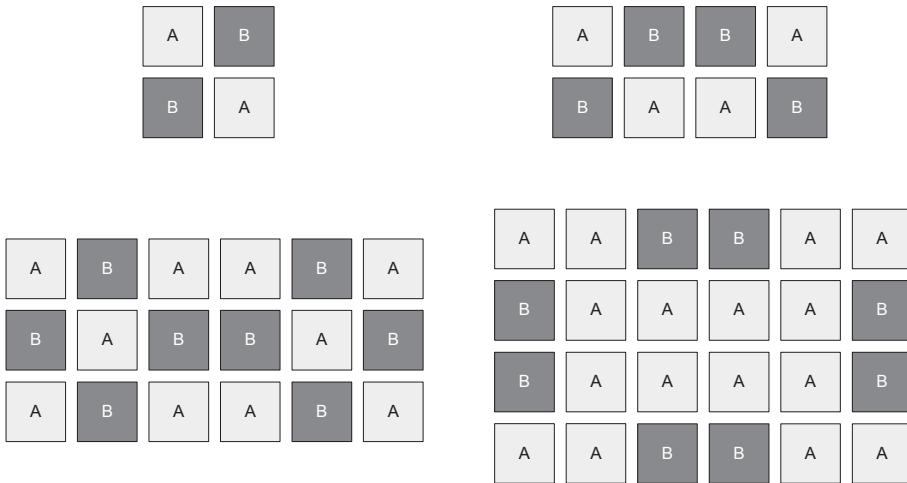

| 4    Analog layout strategies                                          | 135        |

| 4.1    Optimization-driven approaches                                  | 138        |

| 4.2    Knowledge-driven approaches                                     | 140        |

| 5    Automated layout generation for design reuse                      | 142        |

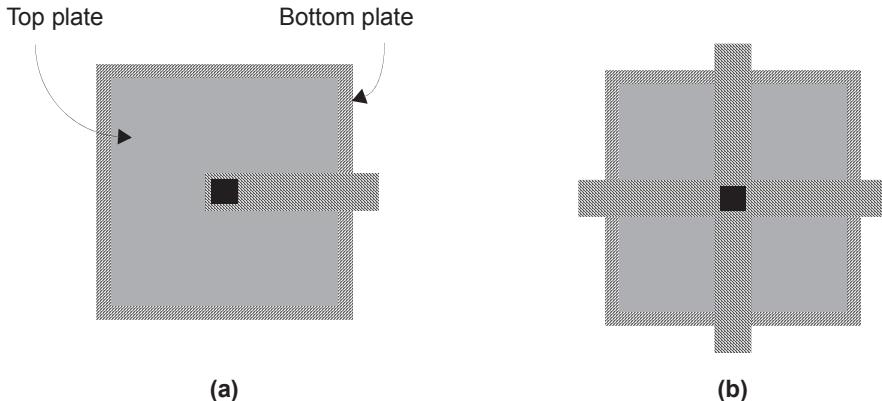

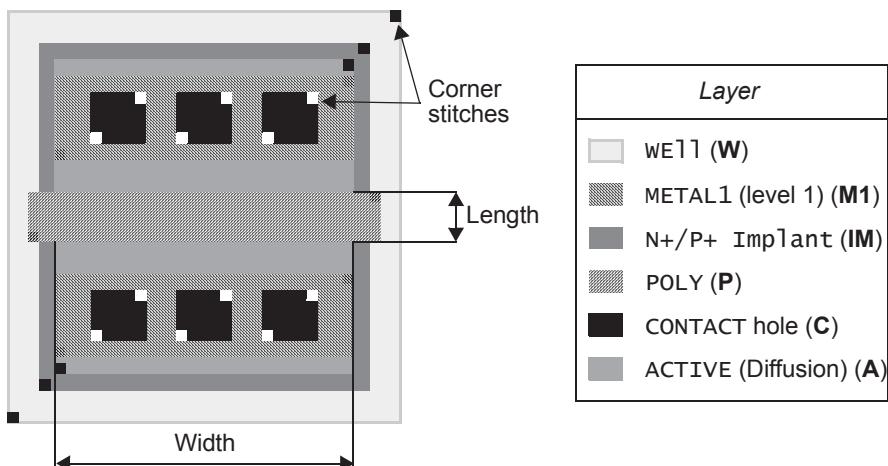

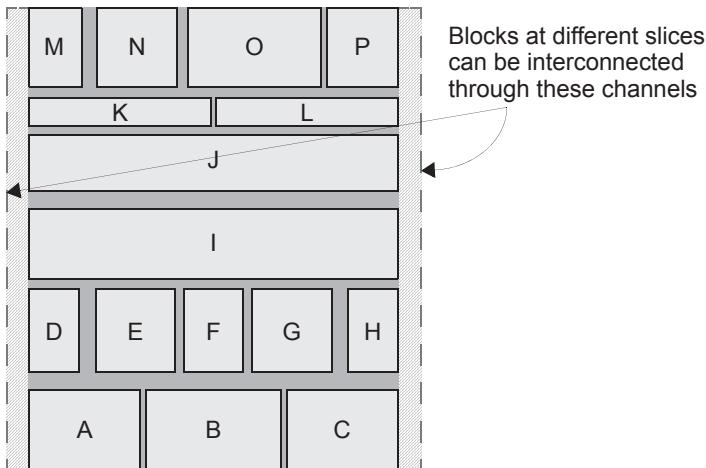

| 6    Layout template: definition and properties                        | 144        |

| 7    Creating the layout template                                      | 150        |

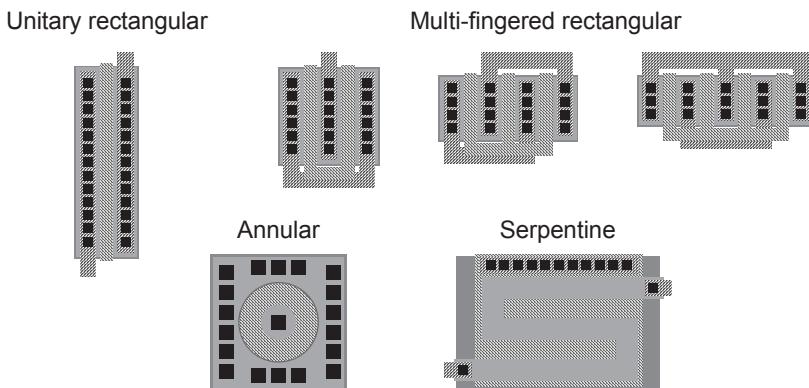

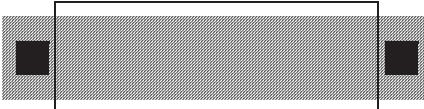

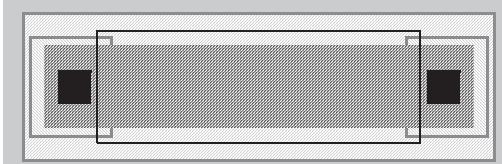

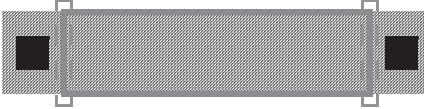

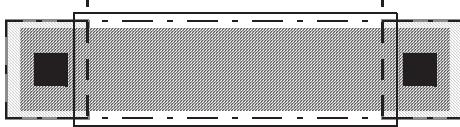

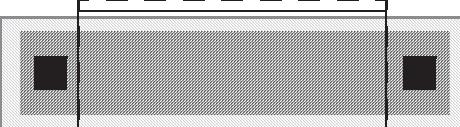

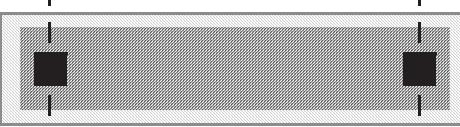

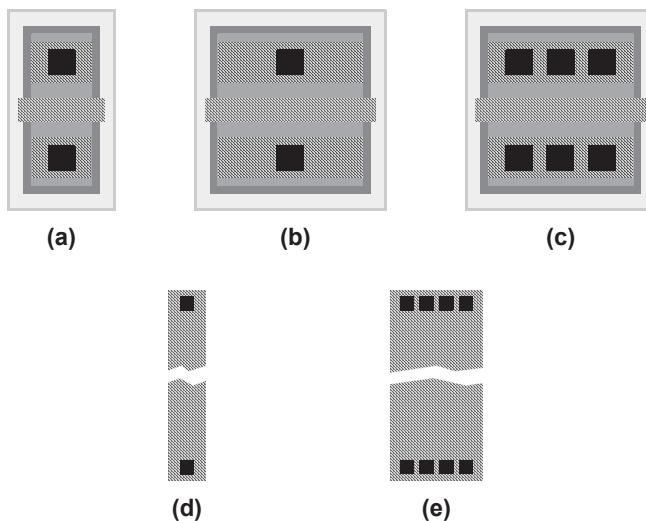

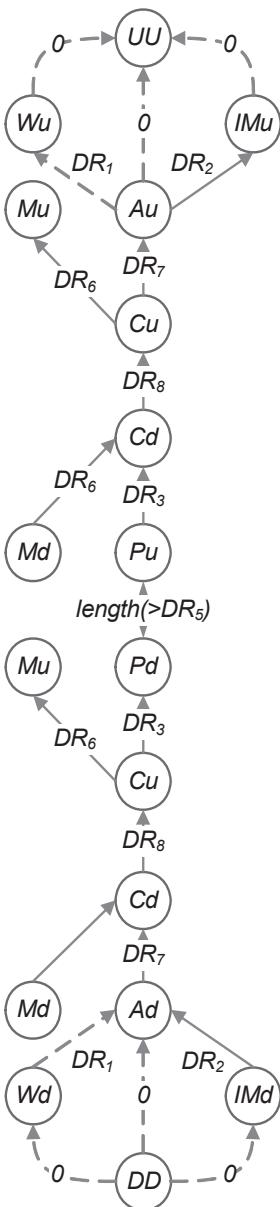

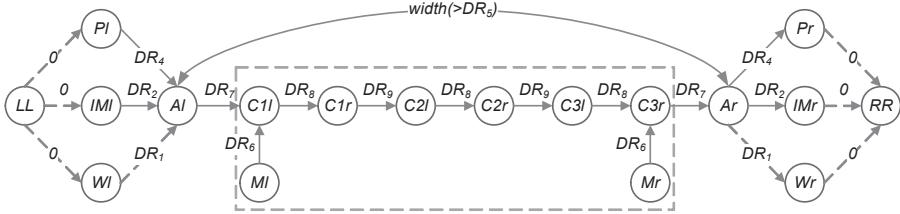

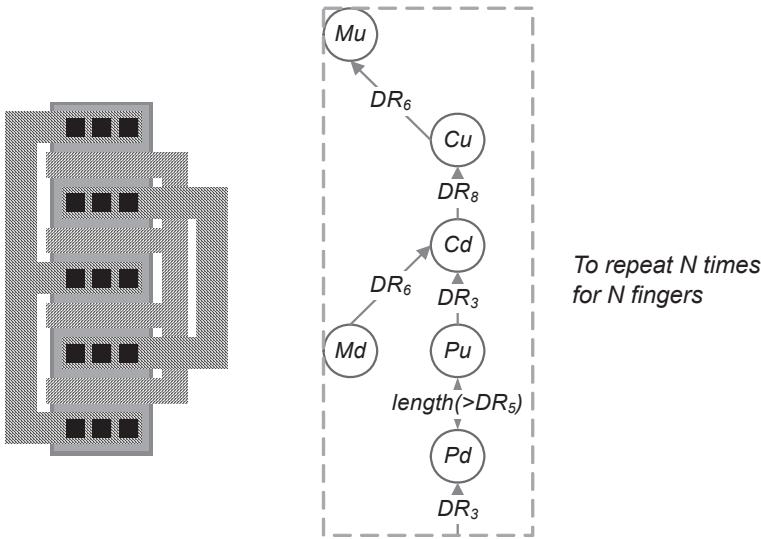

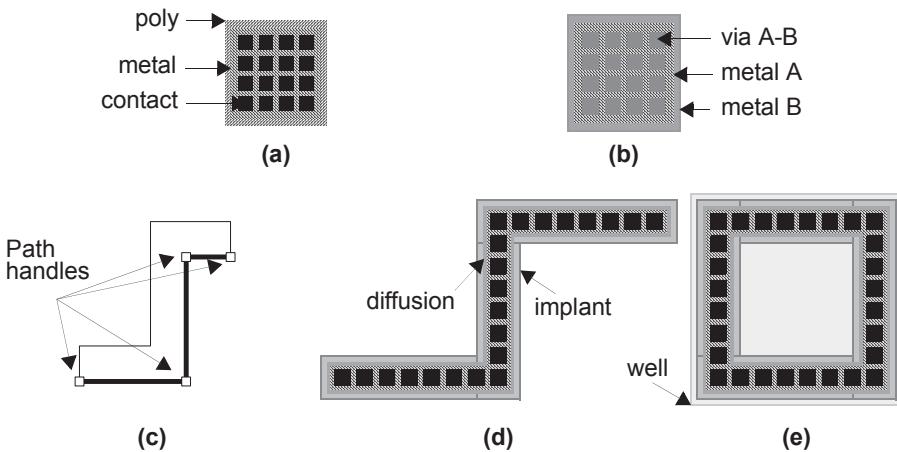

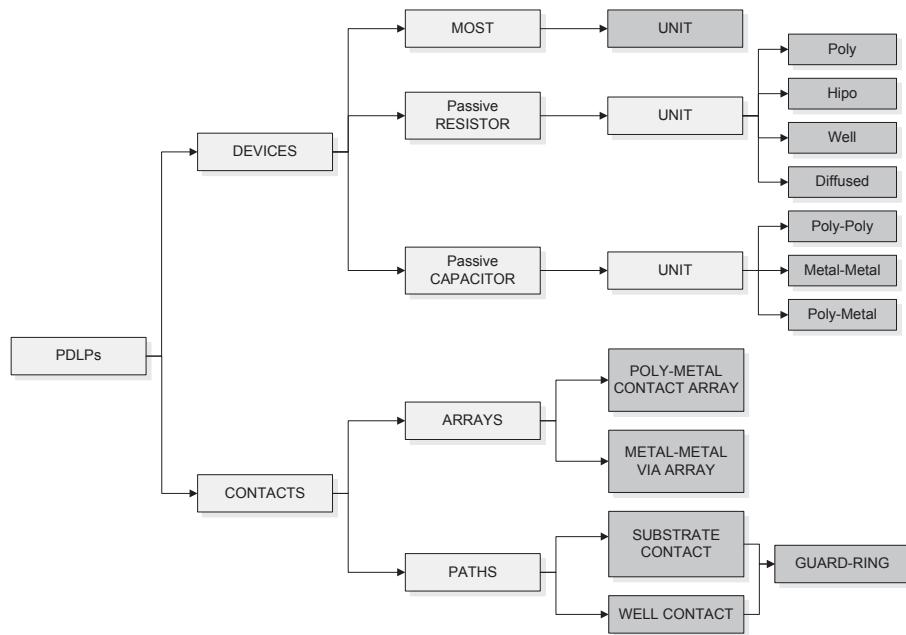

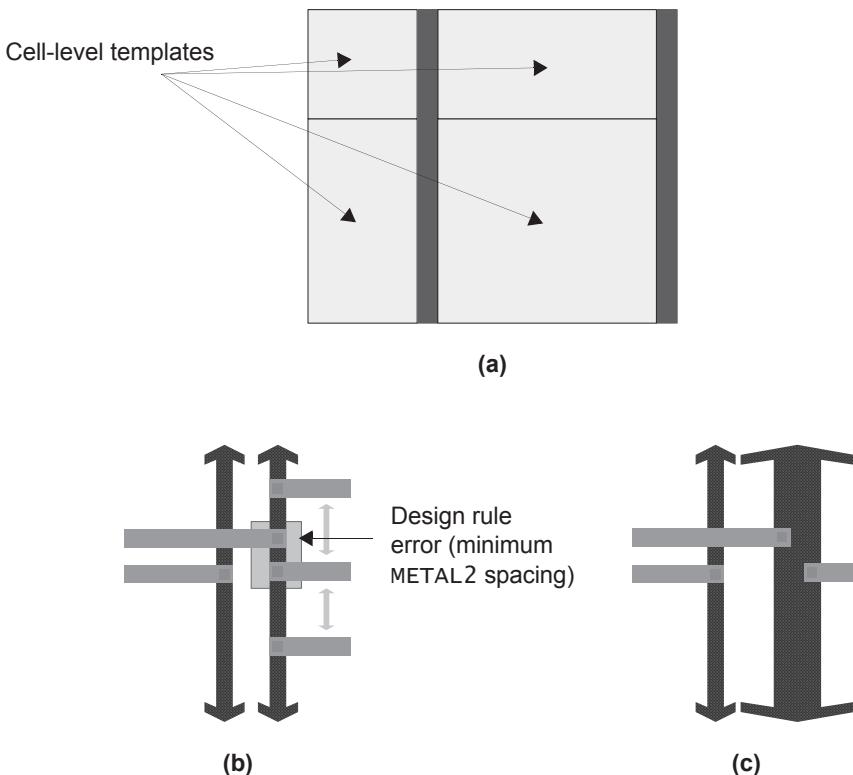

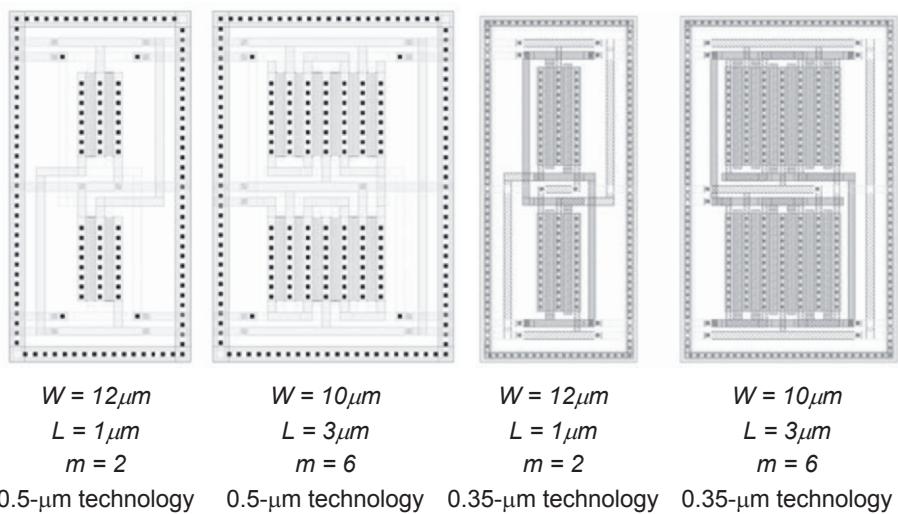

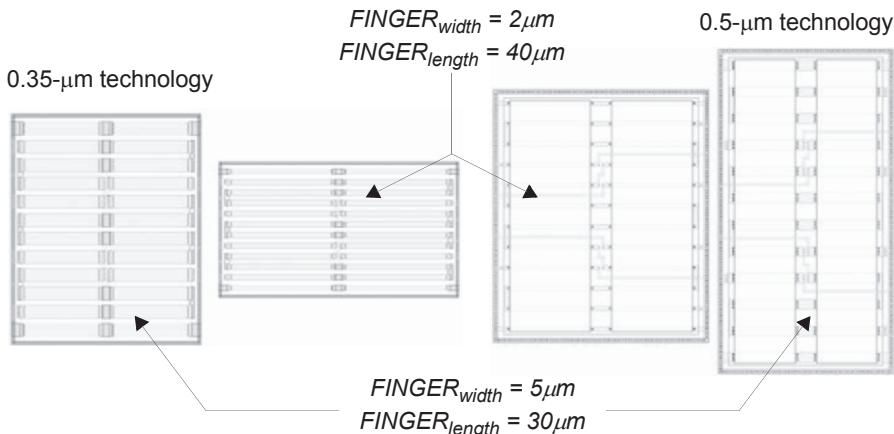

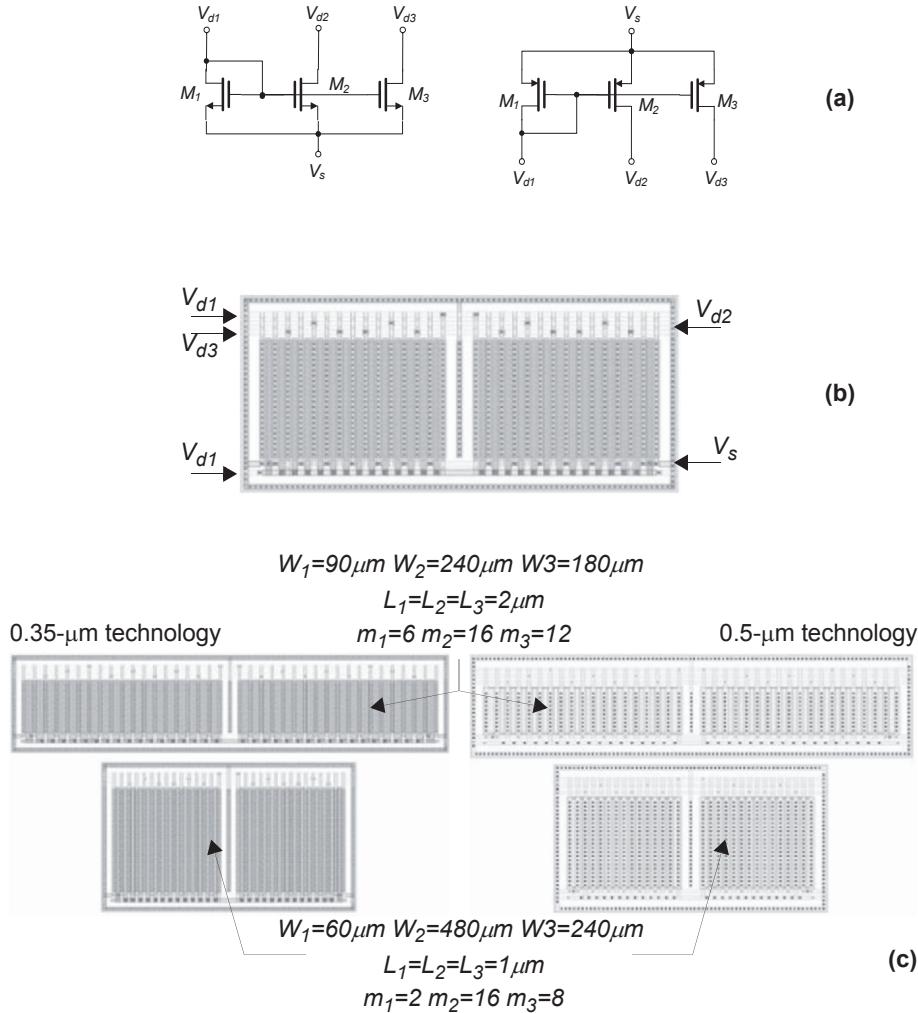

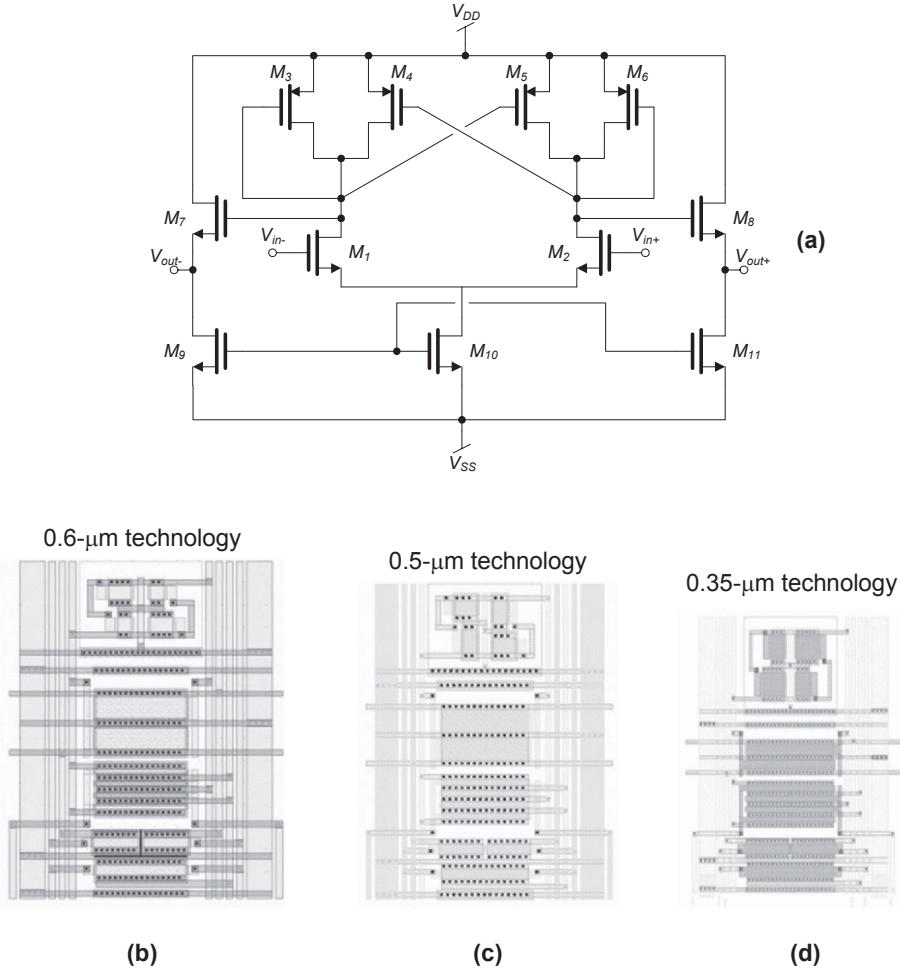

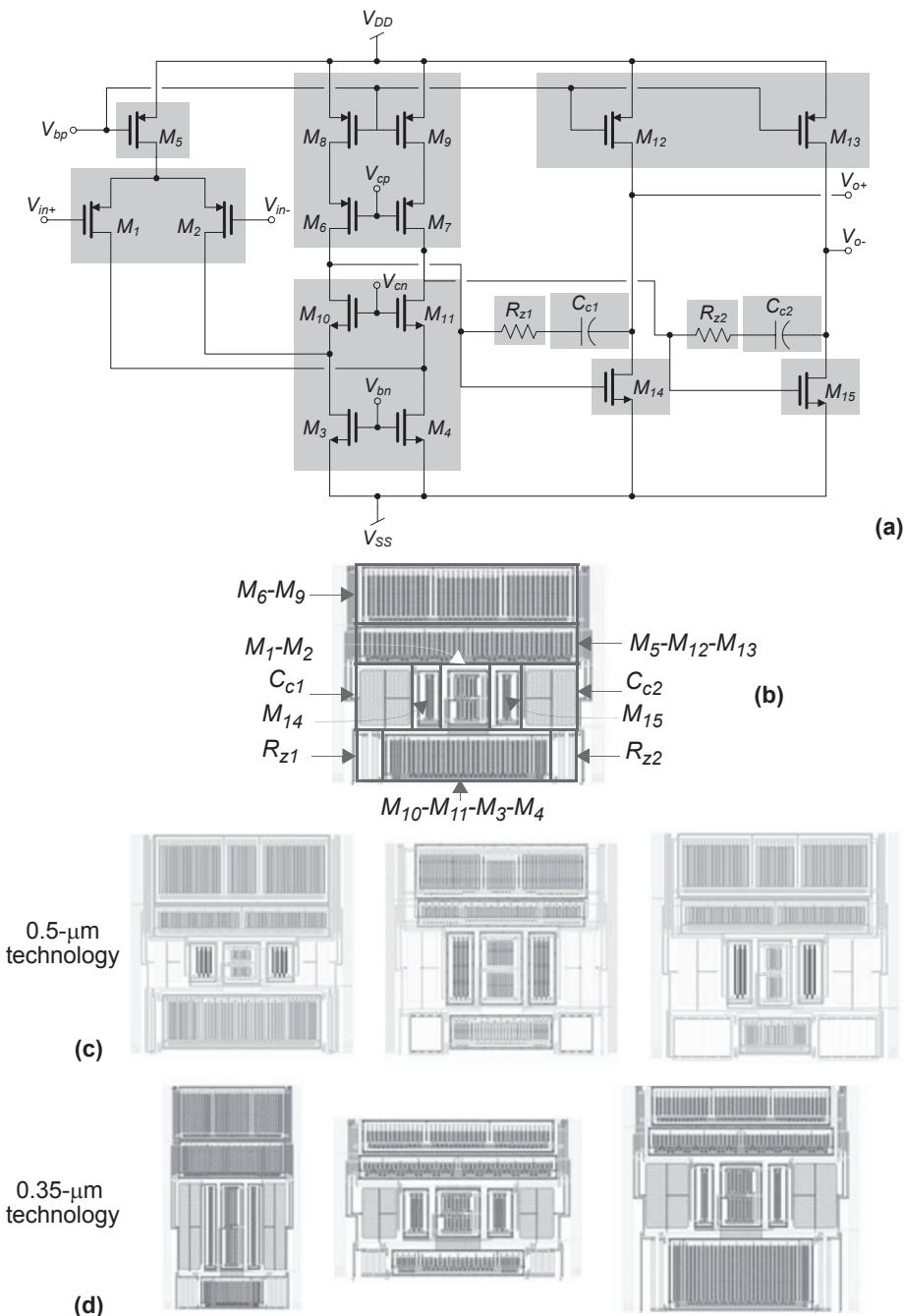

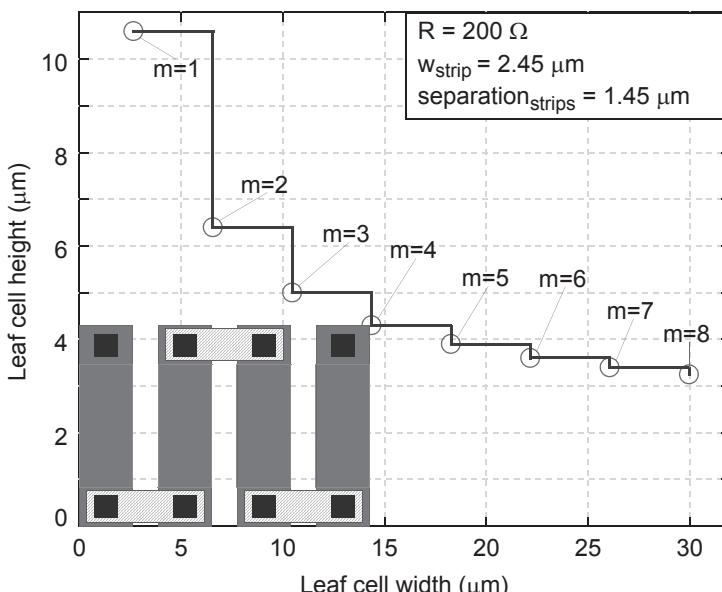

| 7.1    Device-level layout generation: primitives                      | 158        |

| 7.1.1    Reuse: migration issues                                       | 159        |

| 7.1.2    Reuse: retargeting issues                                     | 160        |

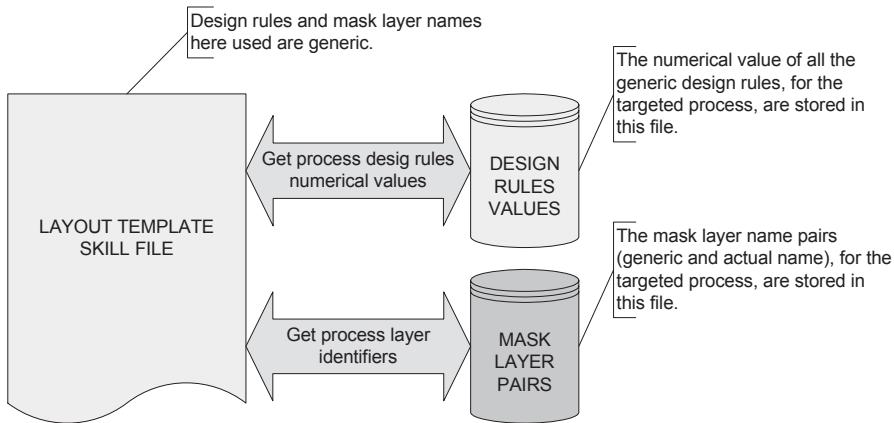

| 7.1.3    PDLP coding                                                   | 162        |

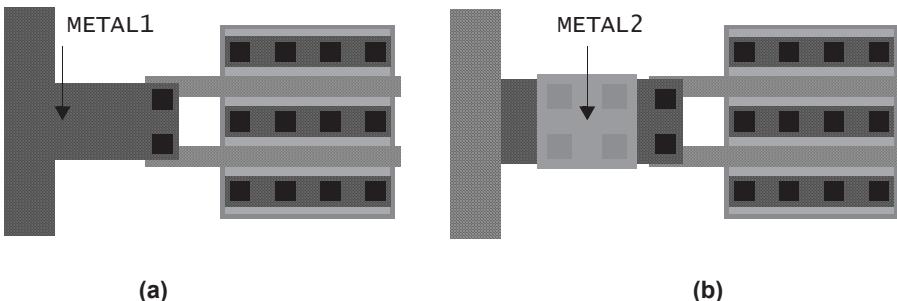

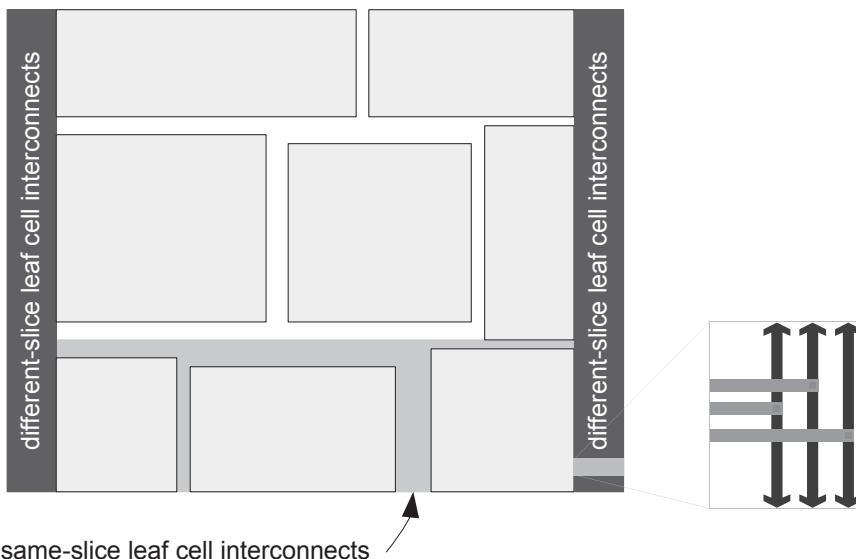

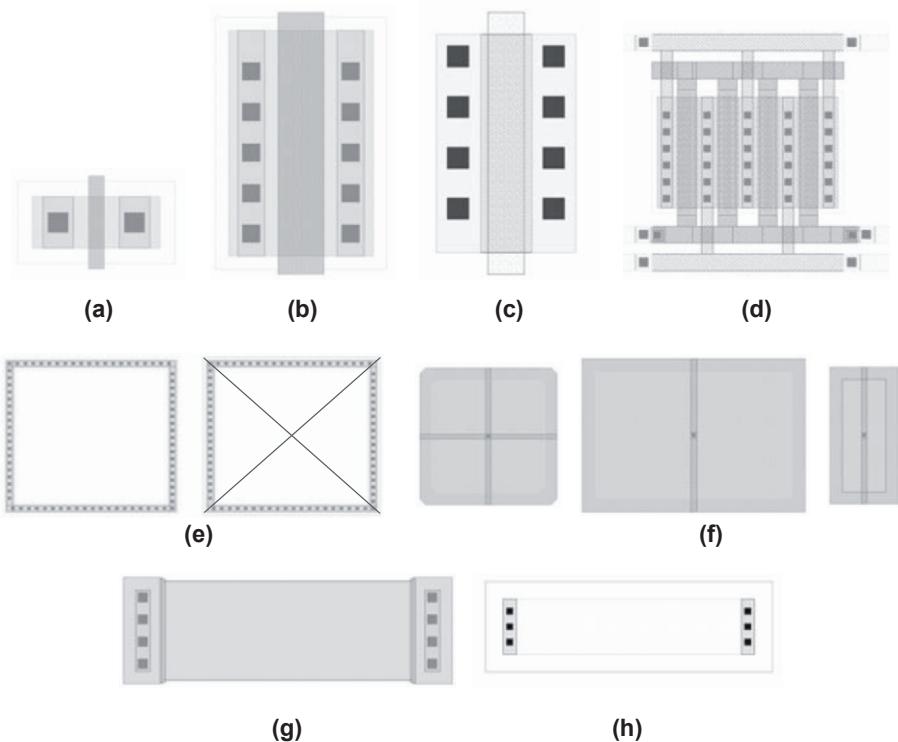

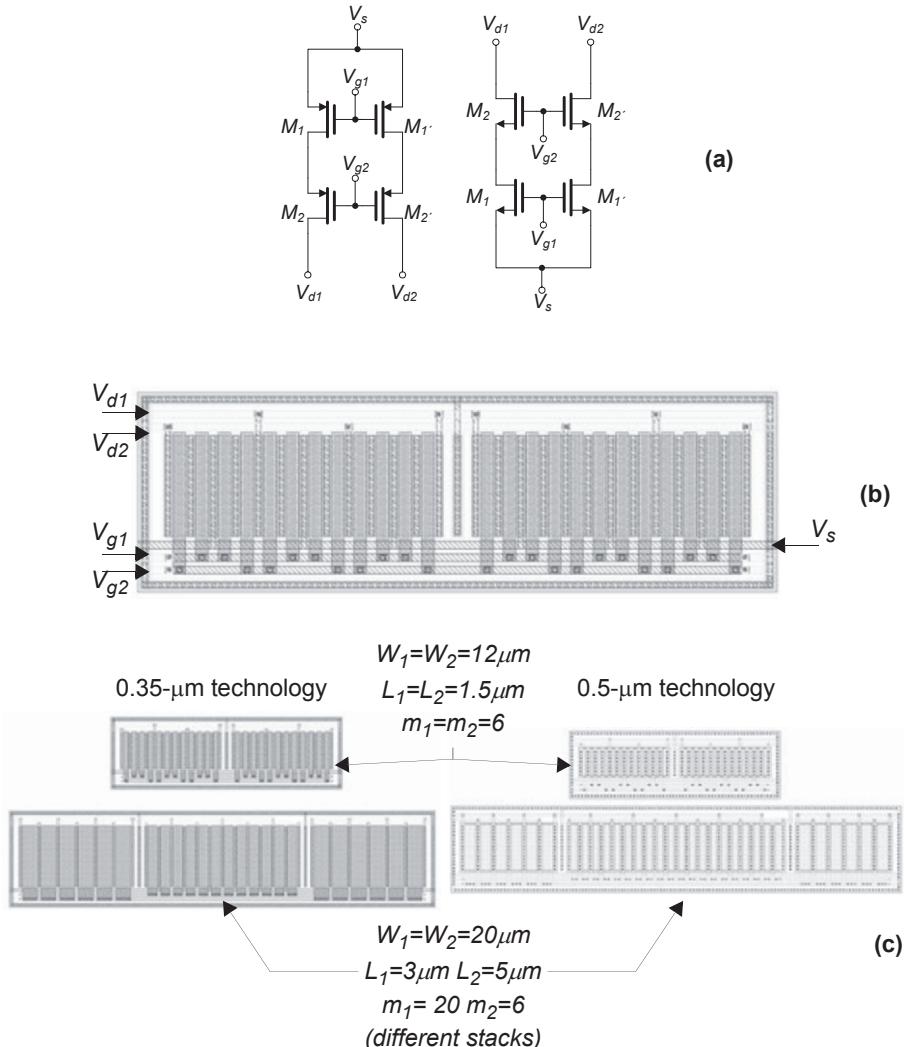

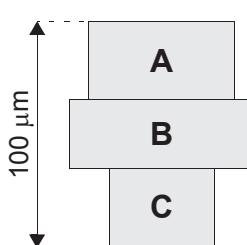

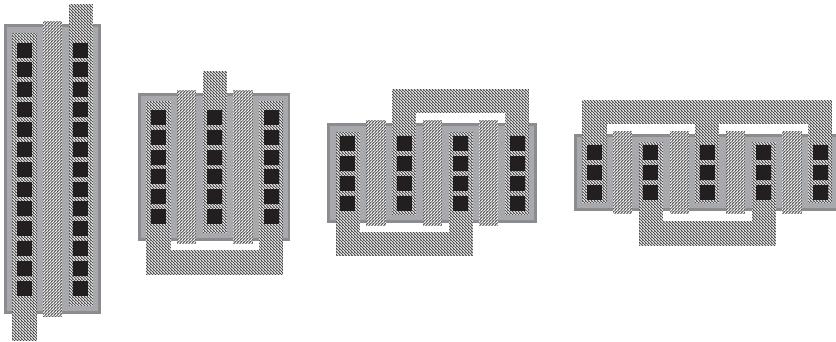

| 7.2    Device-level layout generation: blocks                          | 170        |

| 7.2.1    Reuse: migration issues                                       | 172        |

| 7.2.2    Reuse: retargeting issues                                     | 172        |

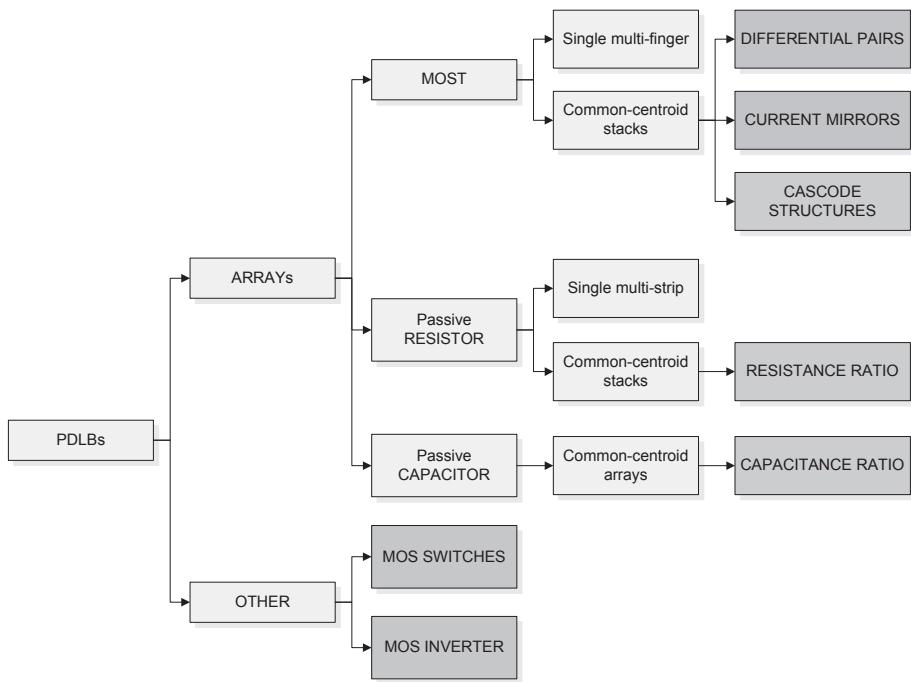

| 7.2.3    PDLB coding                                                   | 173        |

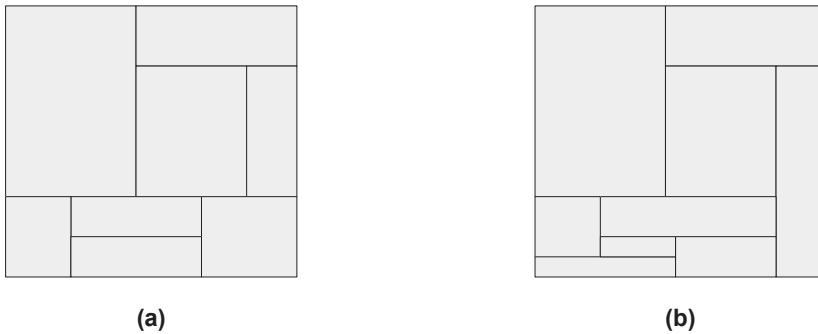

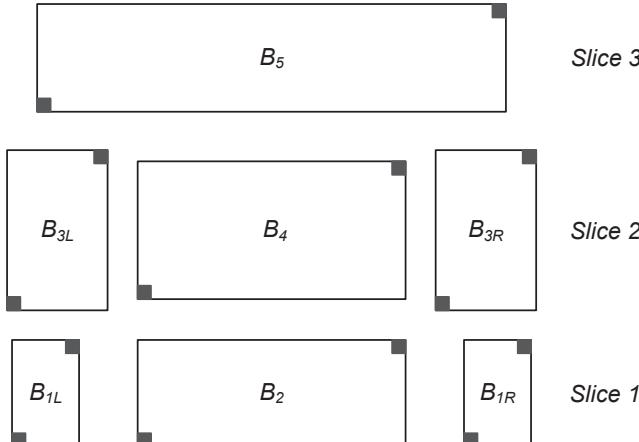

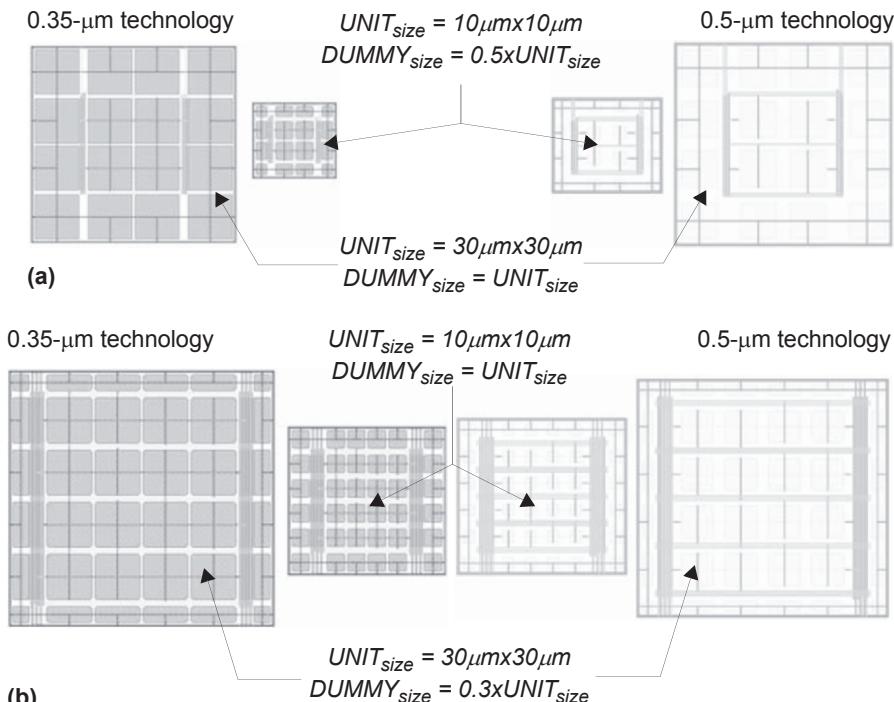

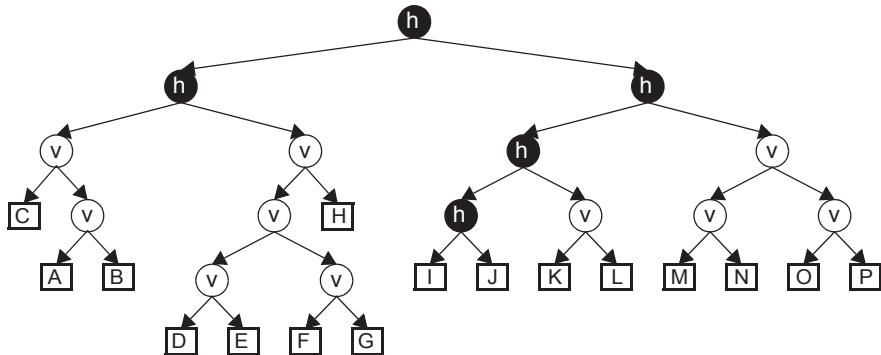

| 7.3    Layout template generation                                      | 182        |

| 7.3.1    Reuse: migration issues                                       | 183        |

| 7.3.2    Reuse: retargeting issues                                     | 185        |

| 7.3.3    Layout template coding                                        | 187        |

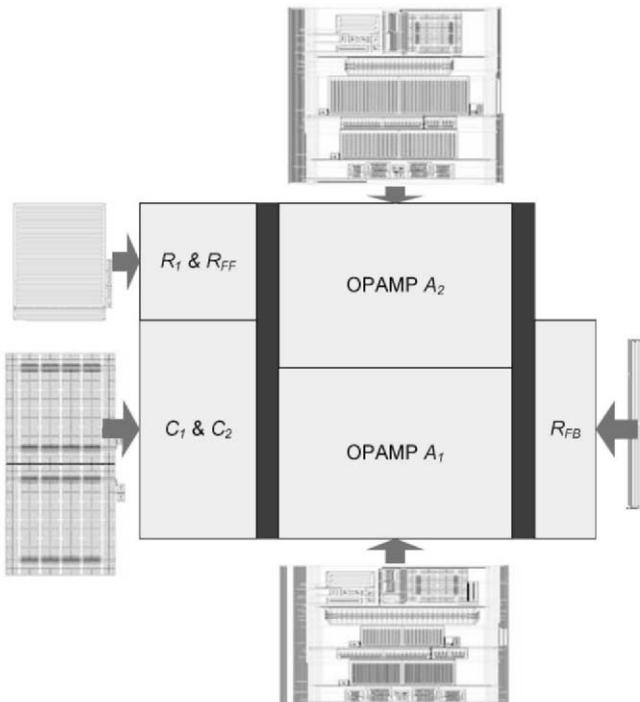

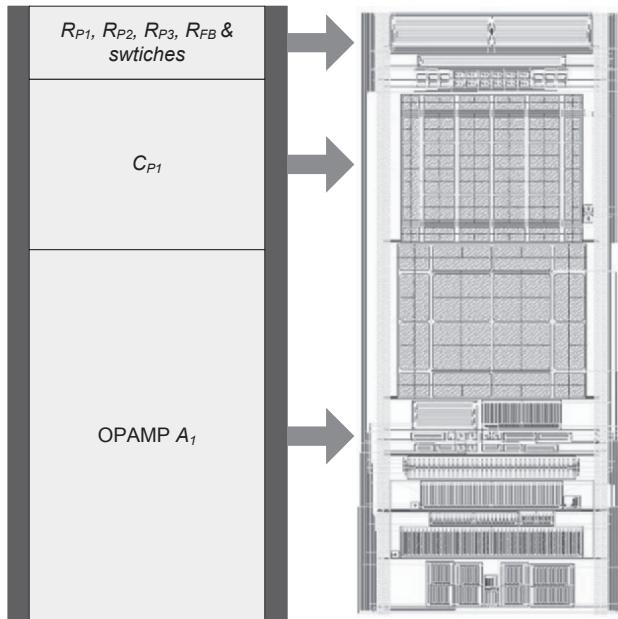

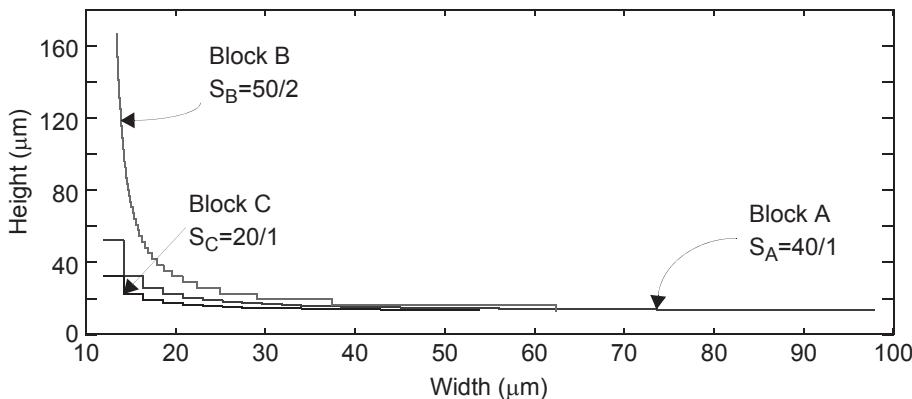

| 8    Practical implementation of layout-reusable analog blocks         | 194        |

| 8.1    Layout languages                                                | 194        |

| 8.2    Implementation examples                                         | 196        |

| 9    Summary                                                           | 205        |

| <b>6 DESIGN EXAMPLES AND SILICON PROTOTYPE</b>                         | <b>207</b> |

| 1    Introduction                                                      | 207        |

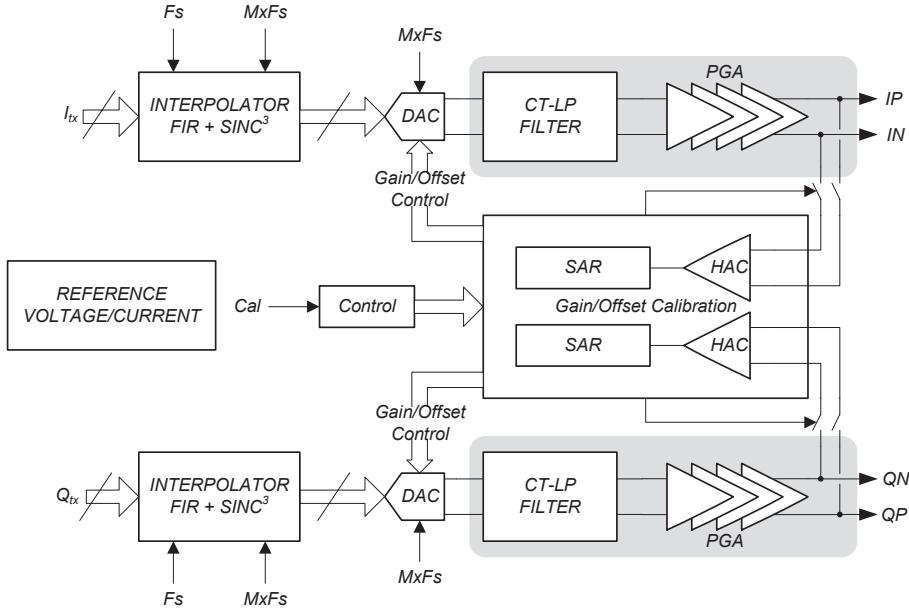

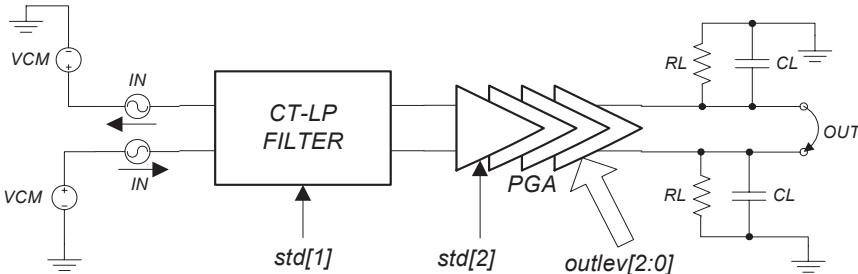

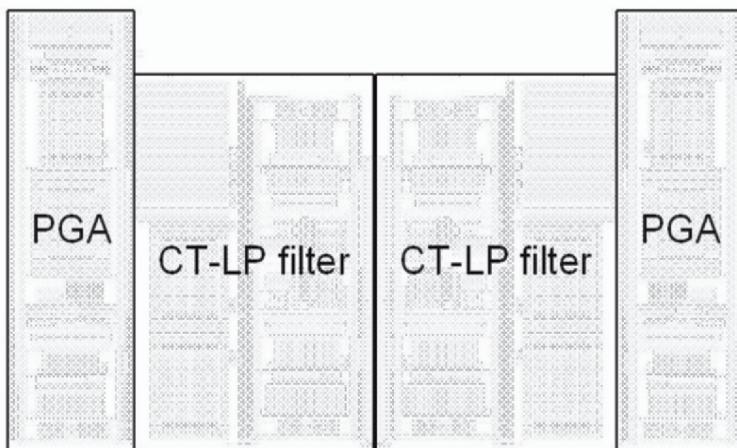

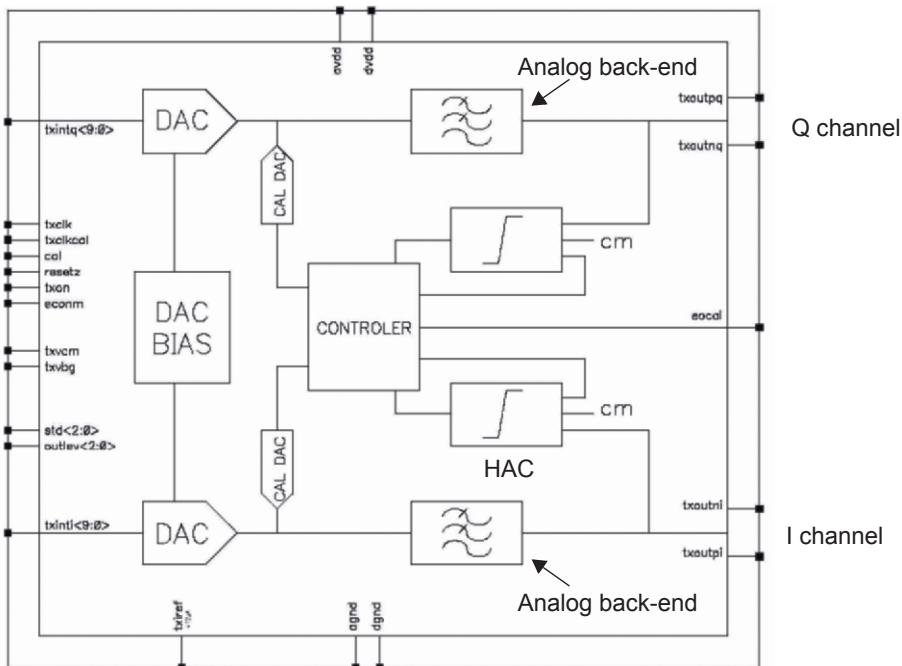

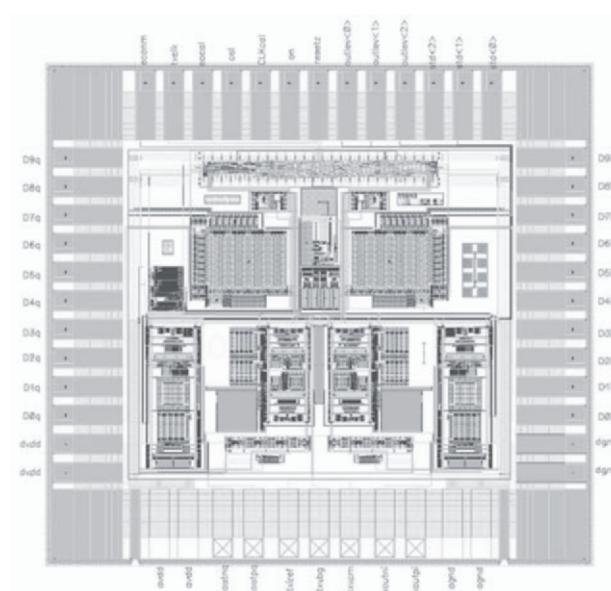

| 2    The demonstration vehicle                                         | 209        |

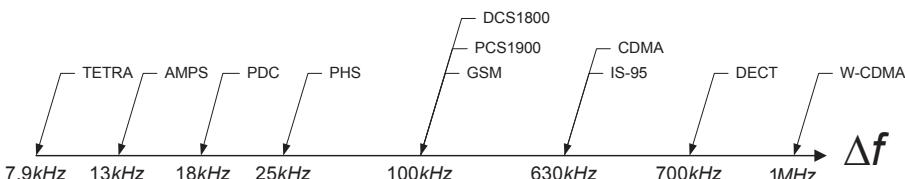

| 2.1    Application area and rationale for architecture selection       | 210        |

| 2.2    System specifications and specifications of the analog back-end | 214        |

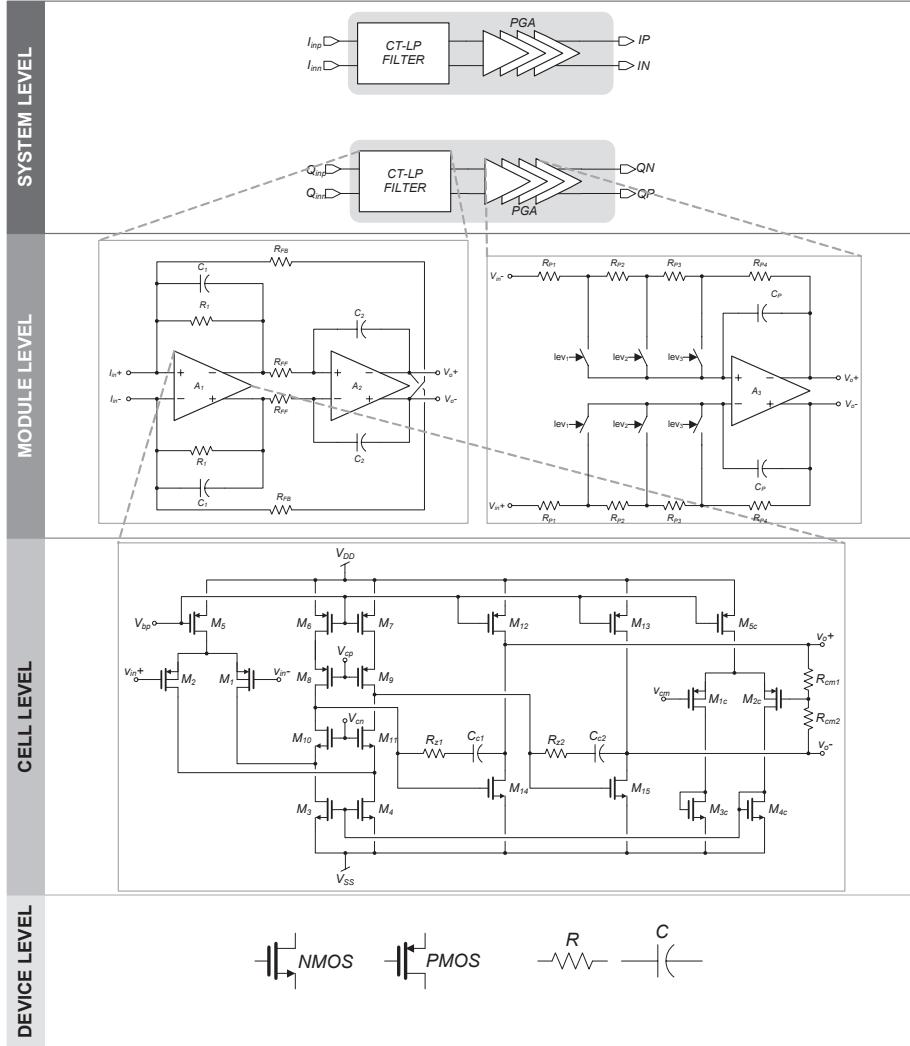

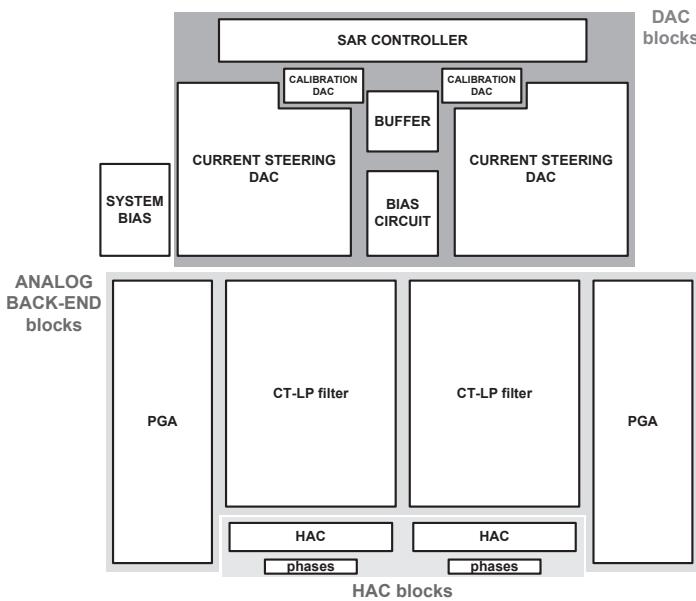

| 2.3    Hierarchy of the analog back-end                                | 214        |

|                                                         |                                                                         |            |

|---------------------------------------------------------|-------------------------------------------------------------------------|------------|

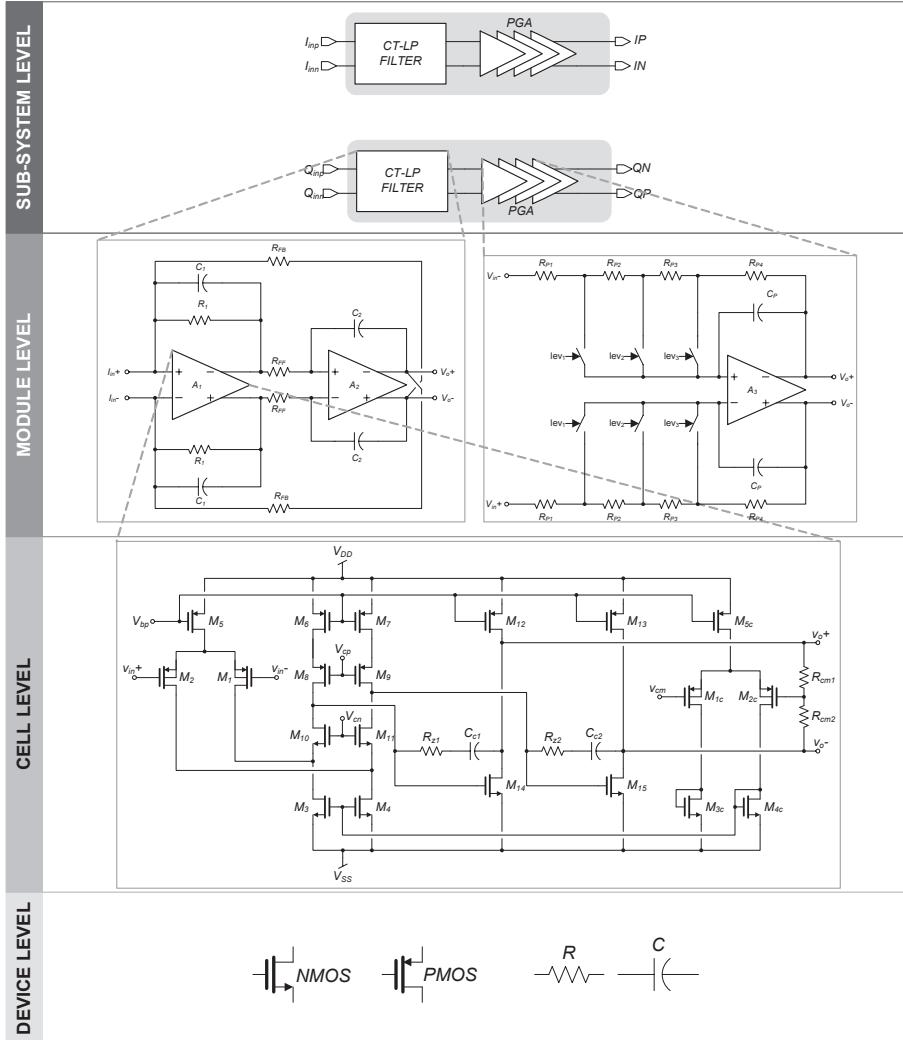

| 2.4                                                     | Analysis of the analog back-end                                         | 216        |

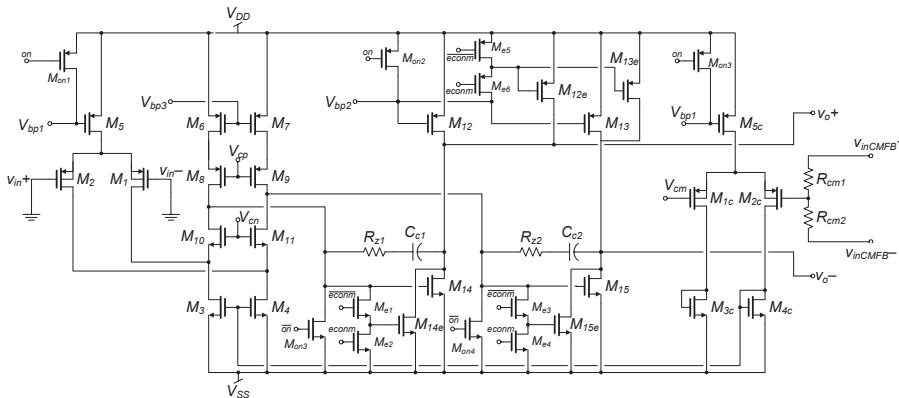

| 2.4.1                                                   | The CT-LP filter                                                        | 217        |

| 2.4.2                                                   | The PGA                                                                 | 224        |

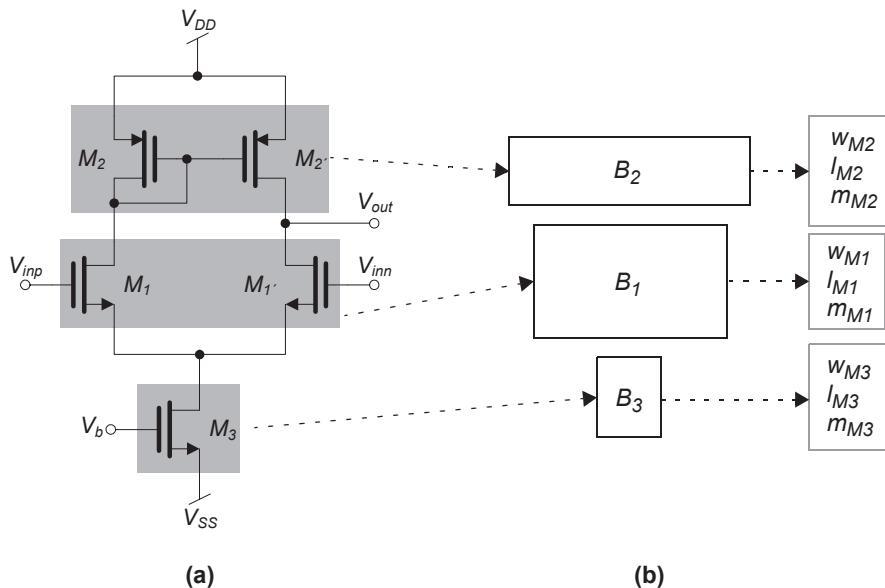

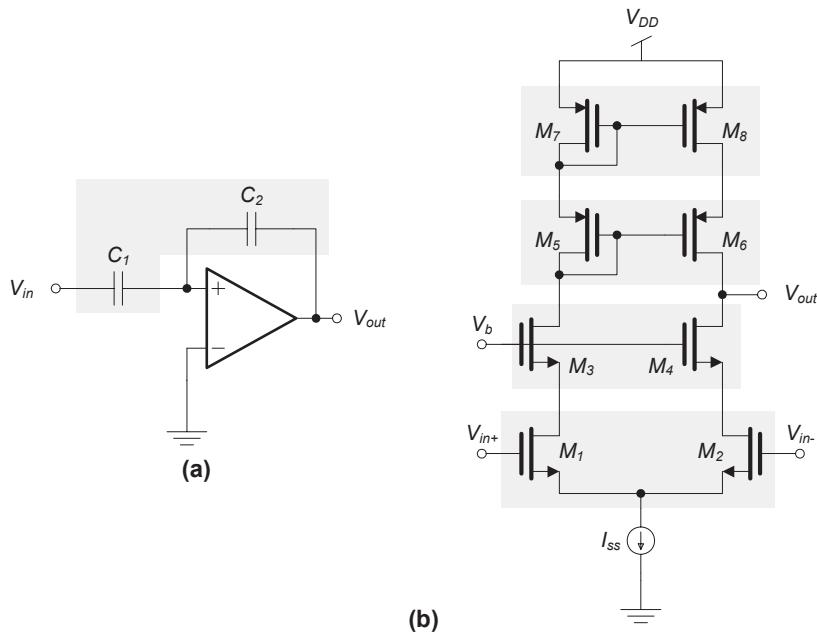

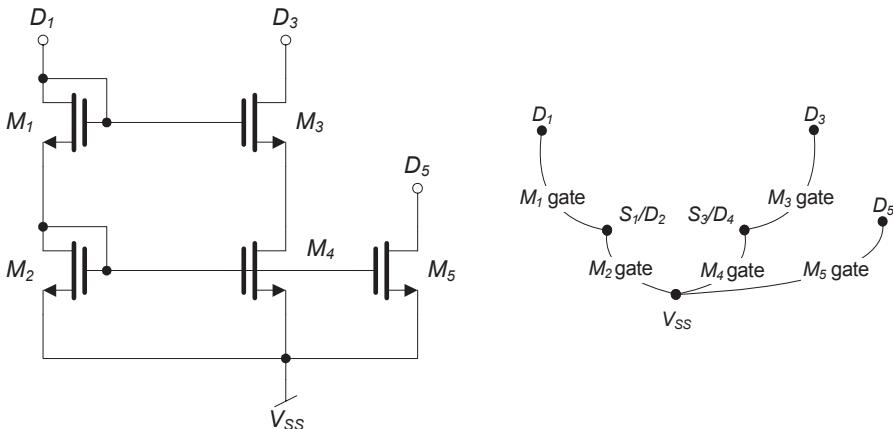

| 3                                                       | Reusable blocks                                                         | 228        |

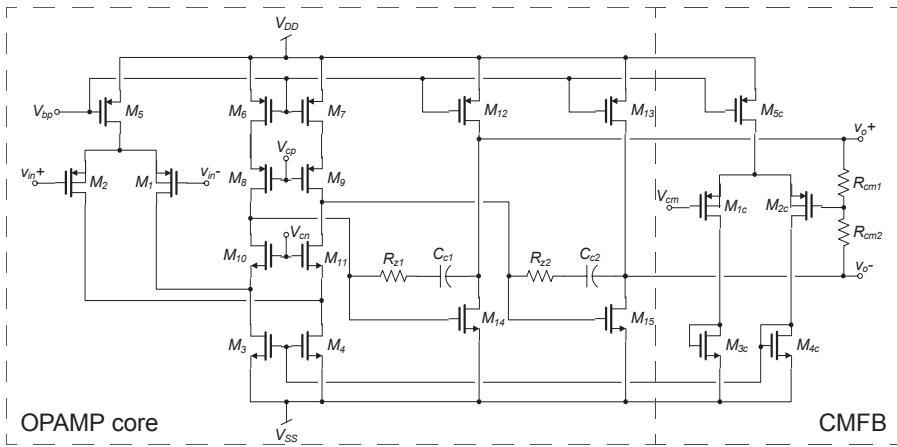

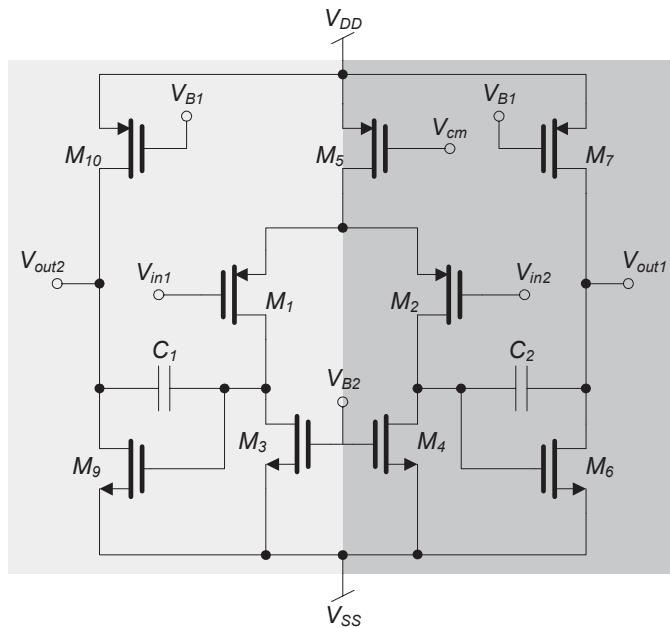

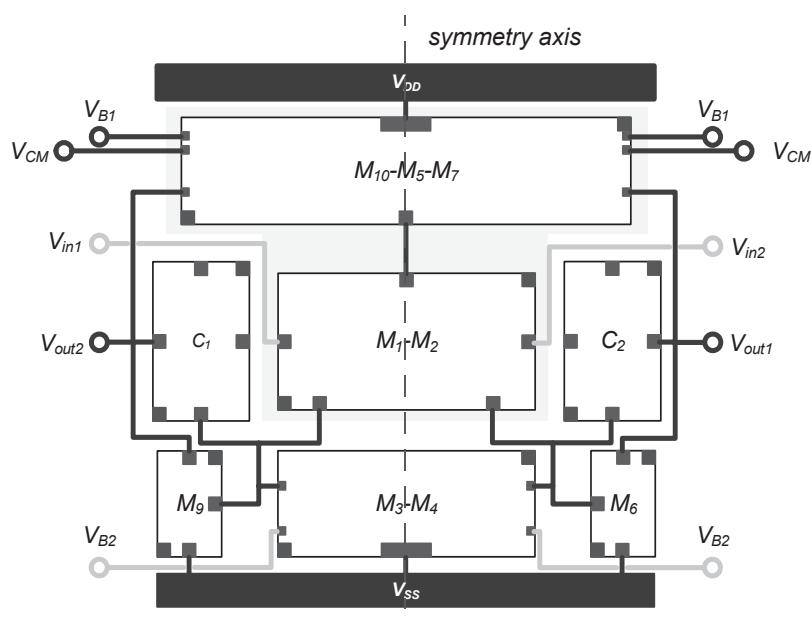

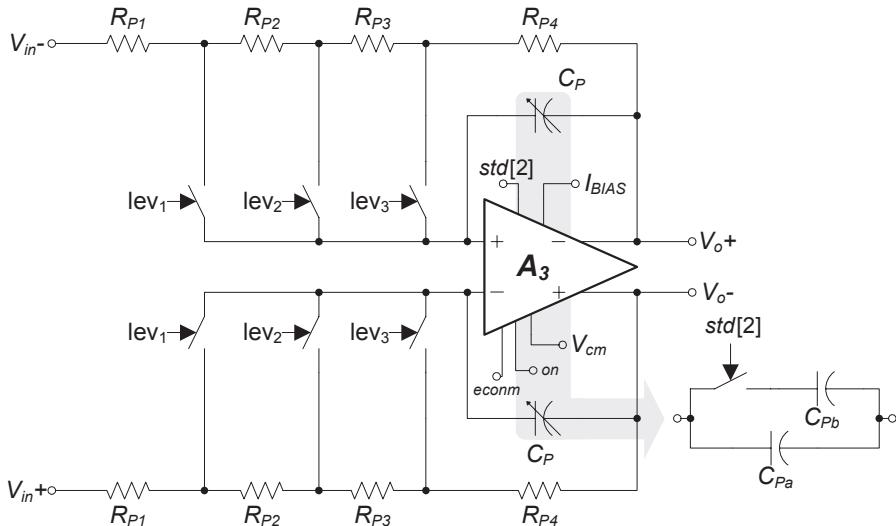

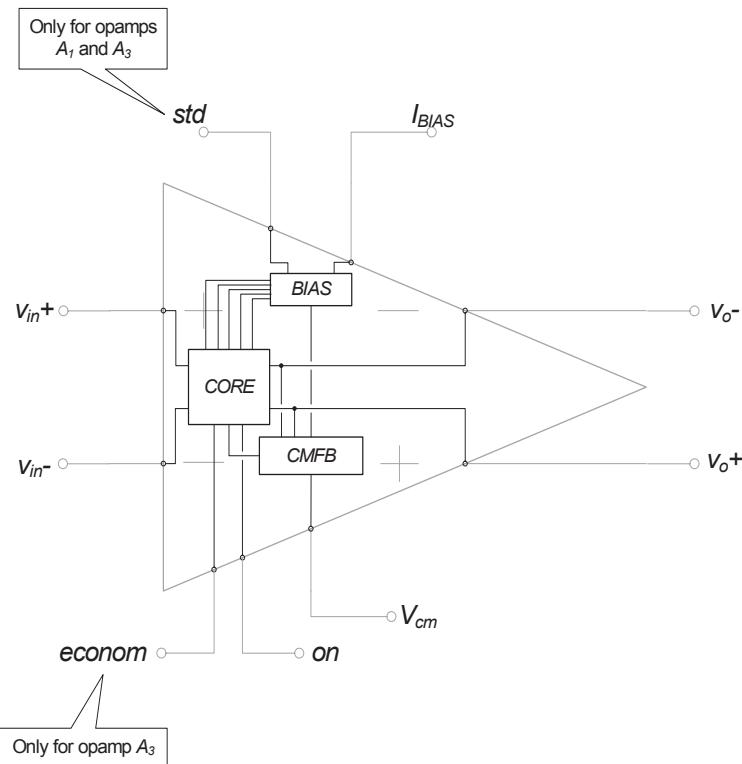

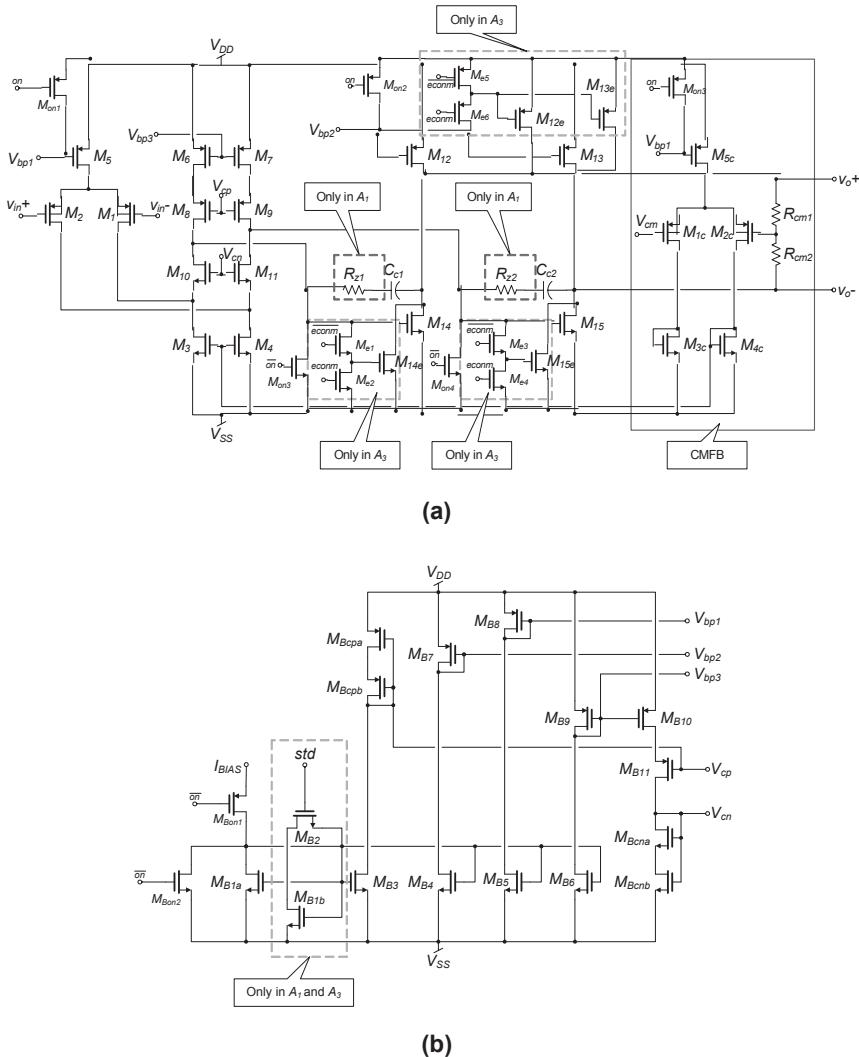

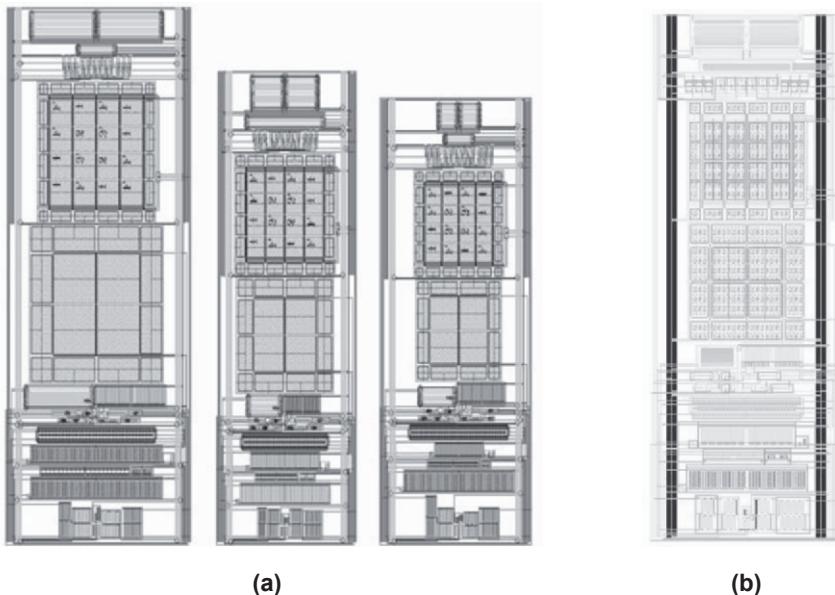

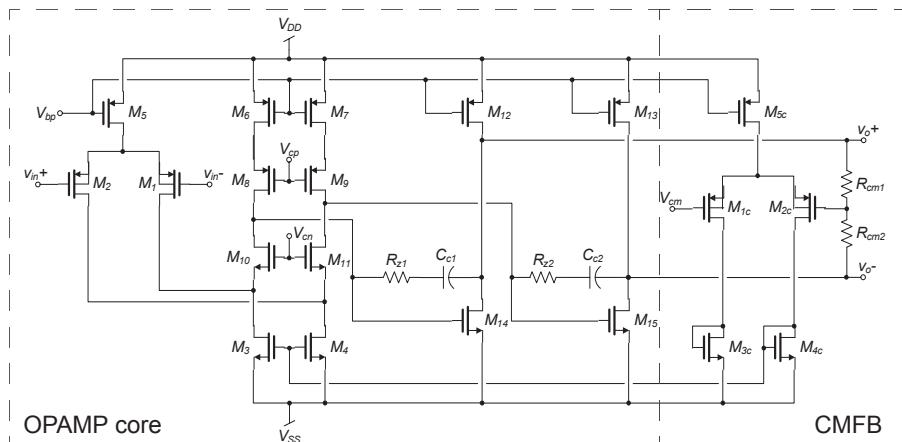

| 3.1                                                     | Reusable blocks: opamps                                                 | 230        |

| 3.2                                                     | Reusable blocks: analog back-end                                        | 237        |

| 4                                                       | Design examples                                                         | 244        |

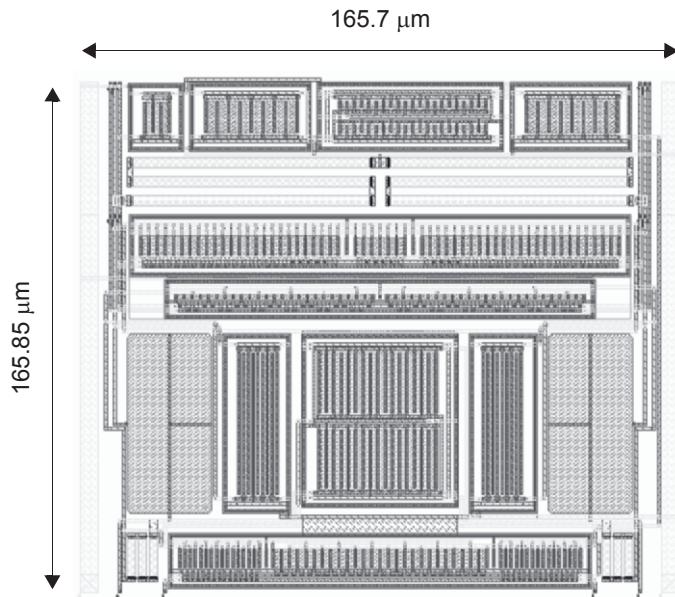

| 4.1                                                     | Design example (I): design retargeting and migration of the opamp       | 247        |

| 4.1.1                                                   | Opamp retargeting in process A ( $0.35\mu\text{m}$ )                    | 248        |

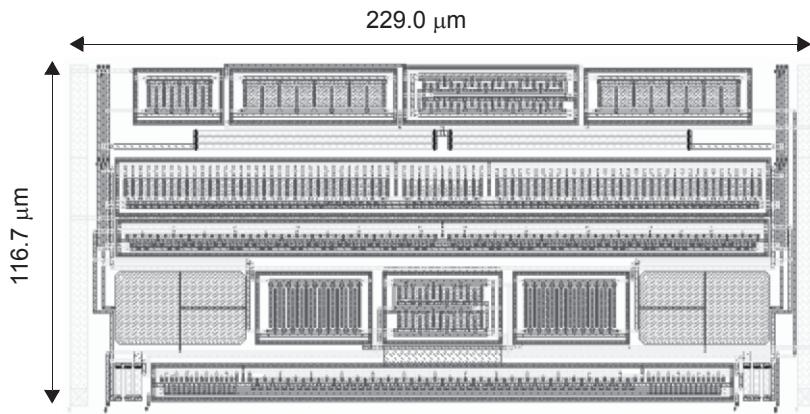

| 4.1.2                                                   | Opamp migration to process B ( $0.5\mu\text{m}$ )                       | 254        |

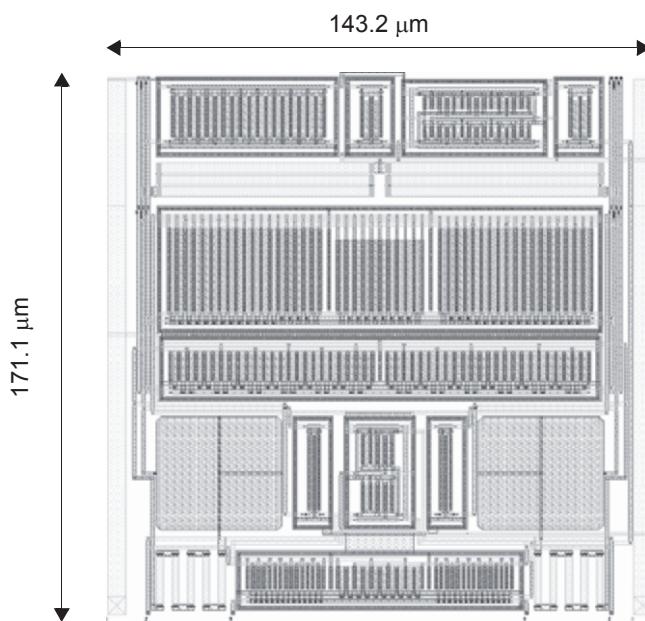

| 4.2                                                     | Design example (II): GSM retargeting of the analog back-end             | 259        |

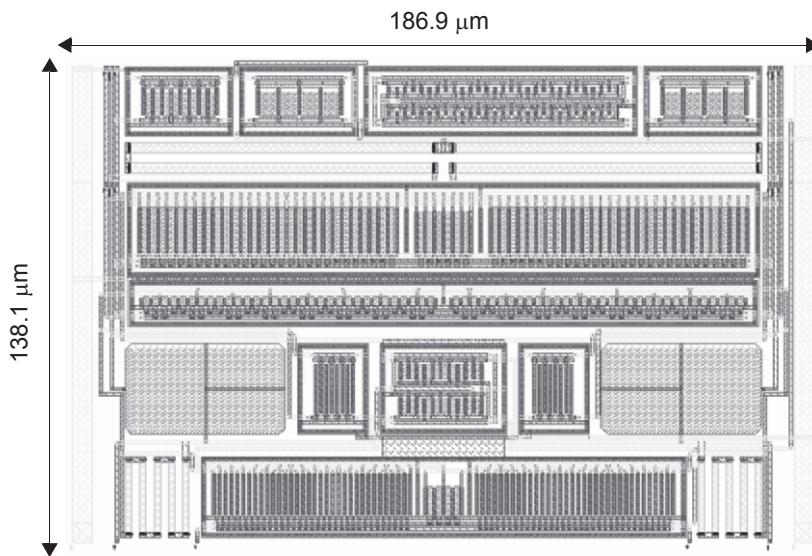

| 4.3                                                     | Design example (III): multi-standard retargeting of the analog back-end | 267        |

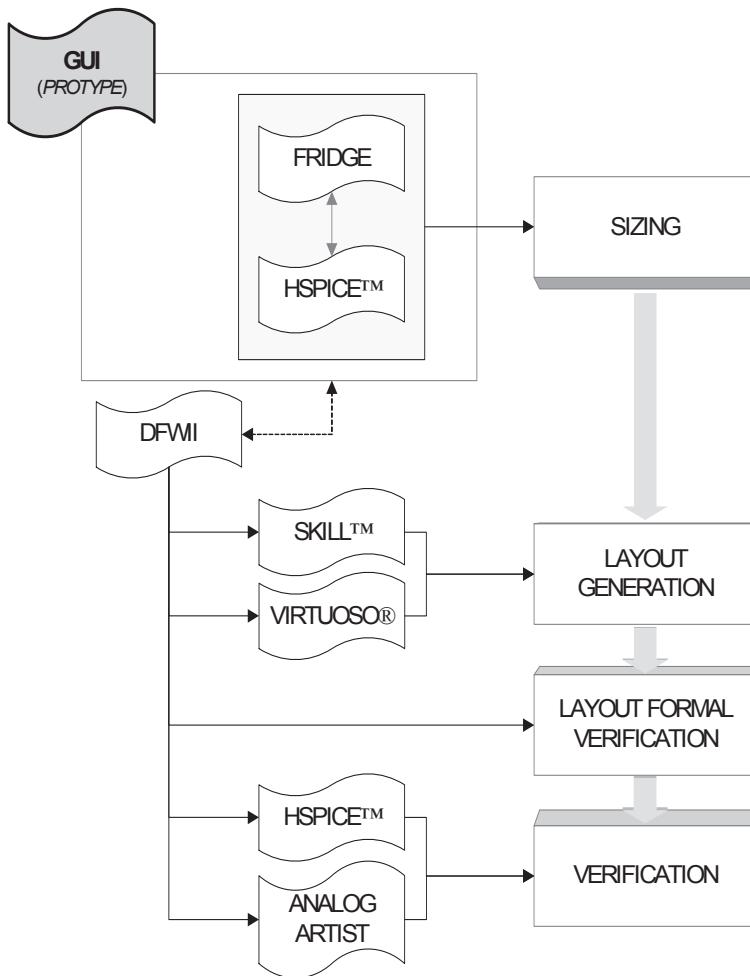

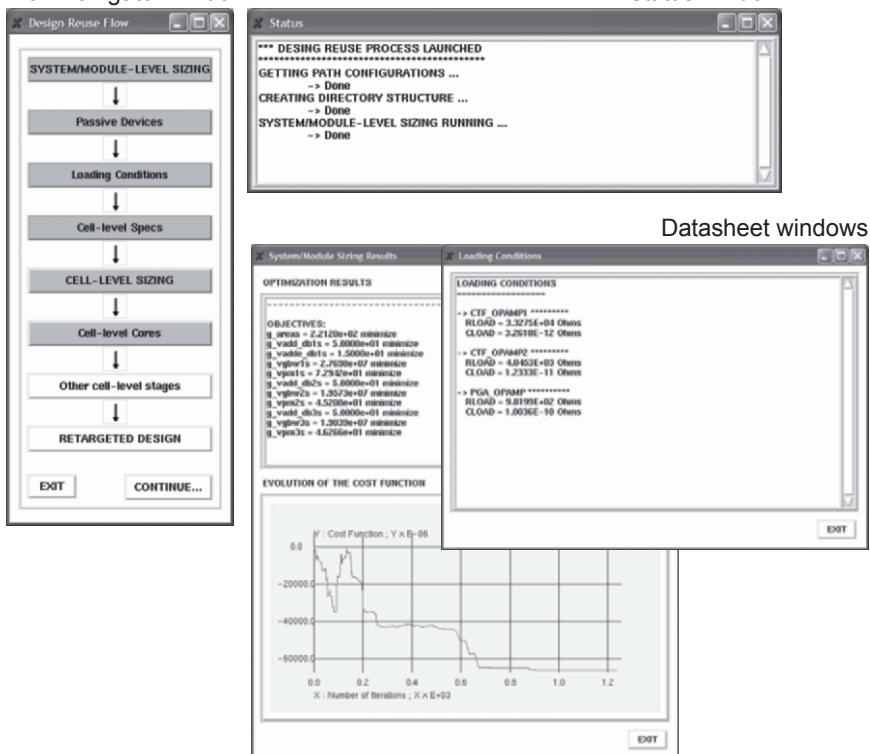

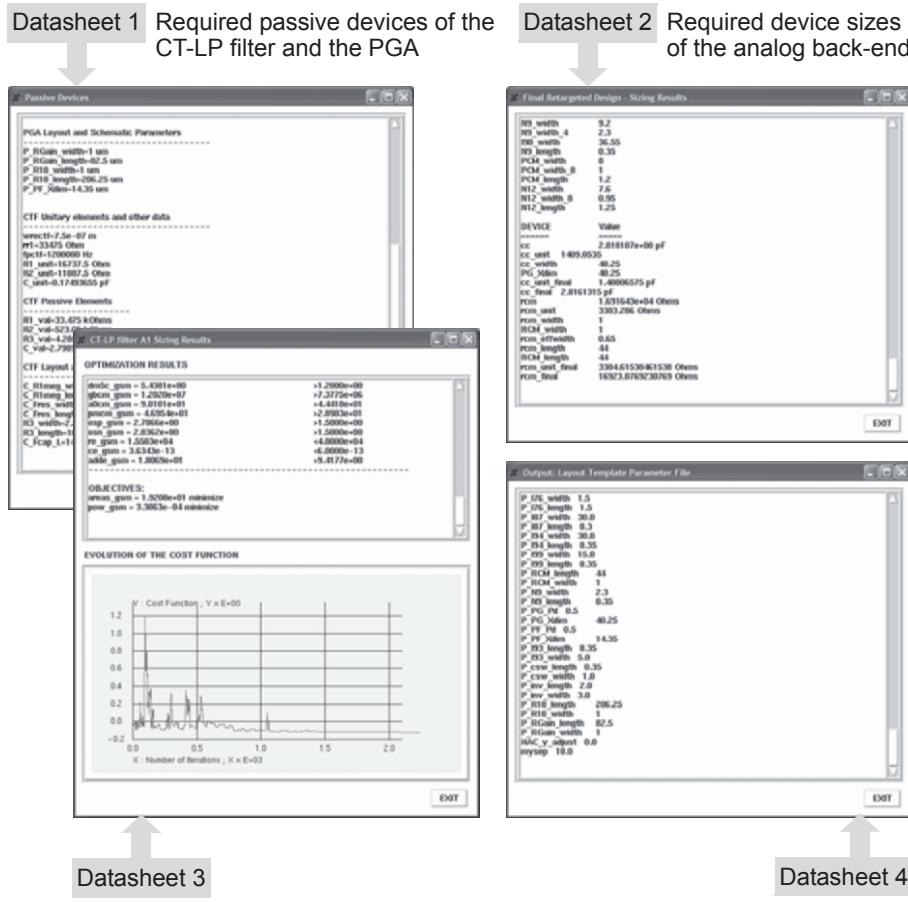

| 4.4                                                     | Automation prototype                                                    | 277        |

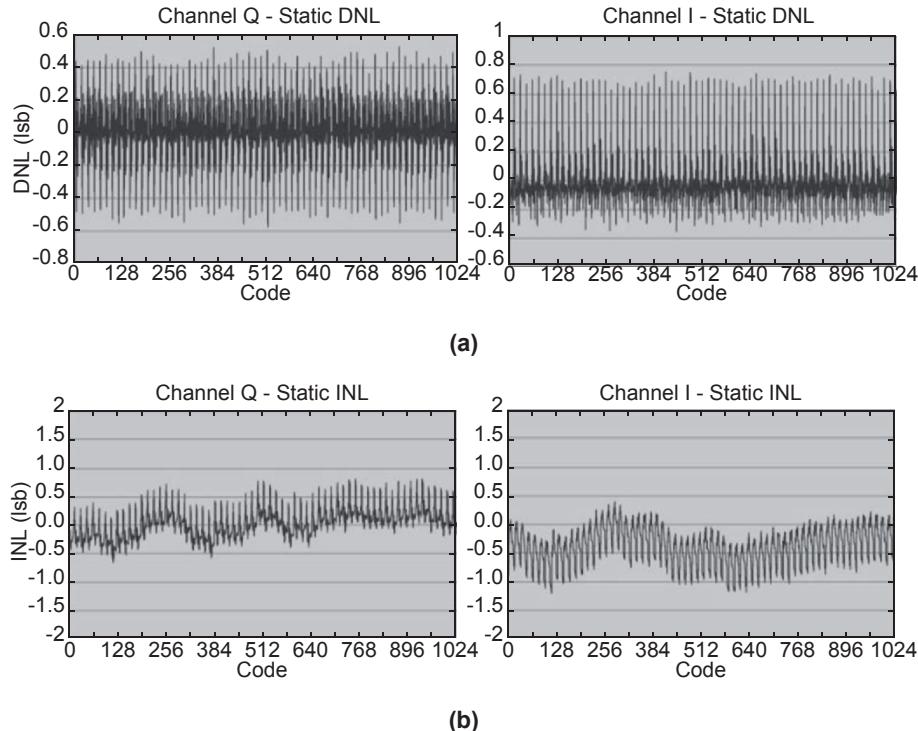

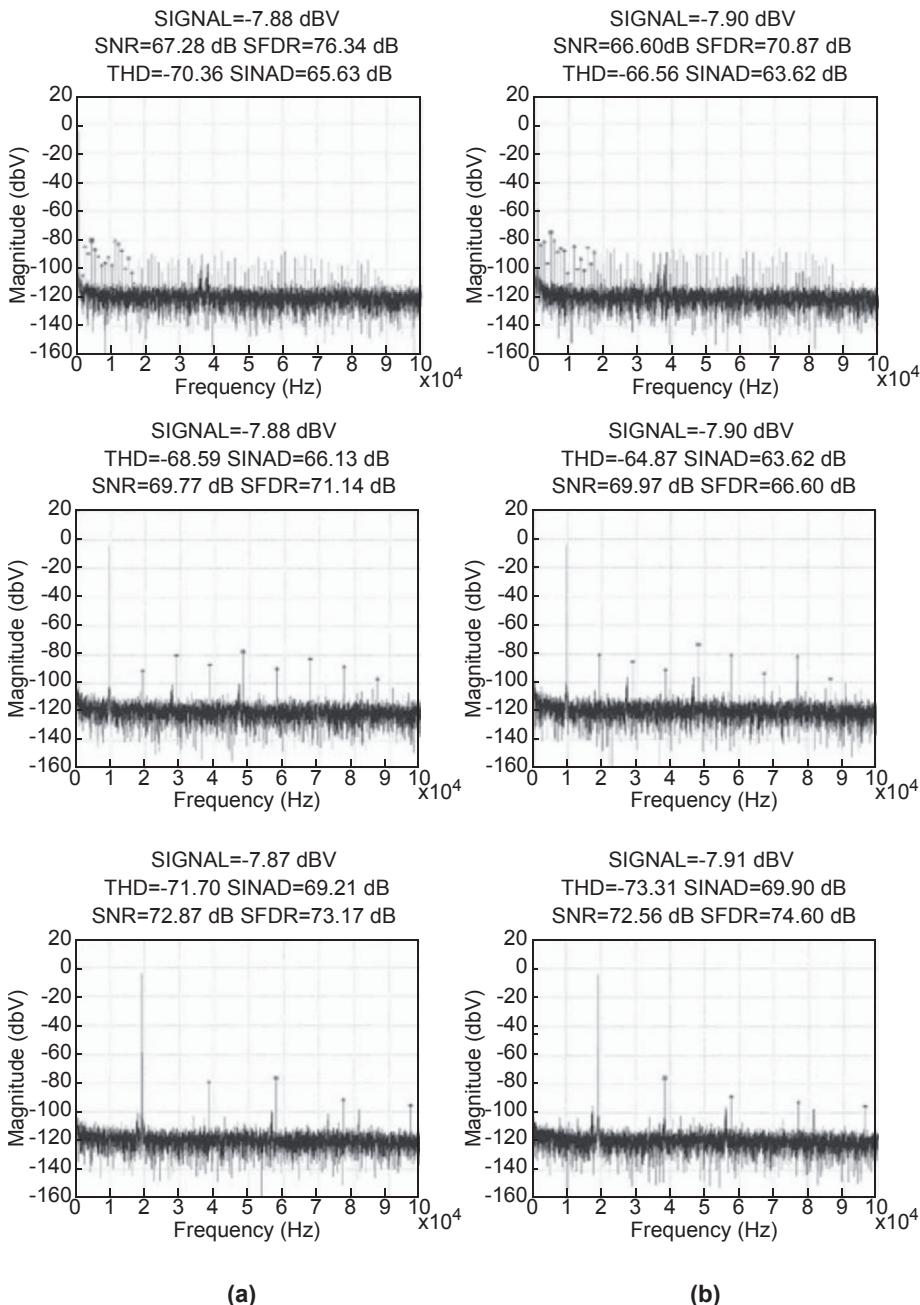

| 5                                                       | Silicon prototype                                                       | 279        |

| 6                                                       | Costs and benefits                                                      | 287        |

| 7                                                       | Summary                                                                 | 288        |

| <b>7 LAYOUT-AWARE CIRCUIT SIZING</b>                    |                                                                         | <b>289</b> |

| 1                                                       | Introduction                                                            | 289        |

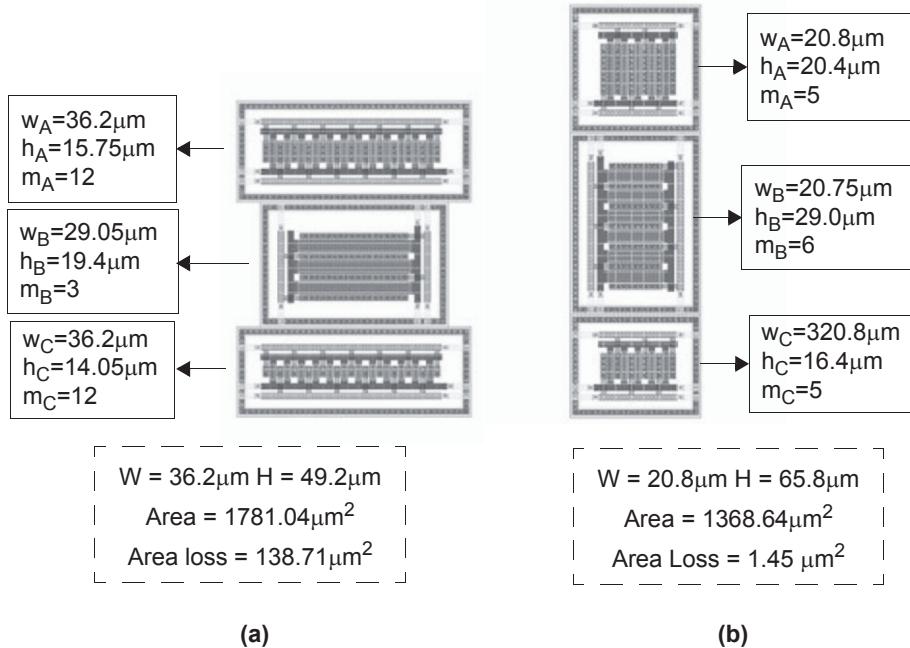

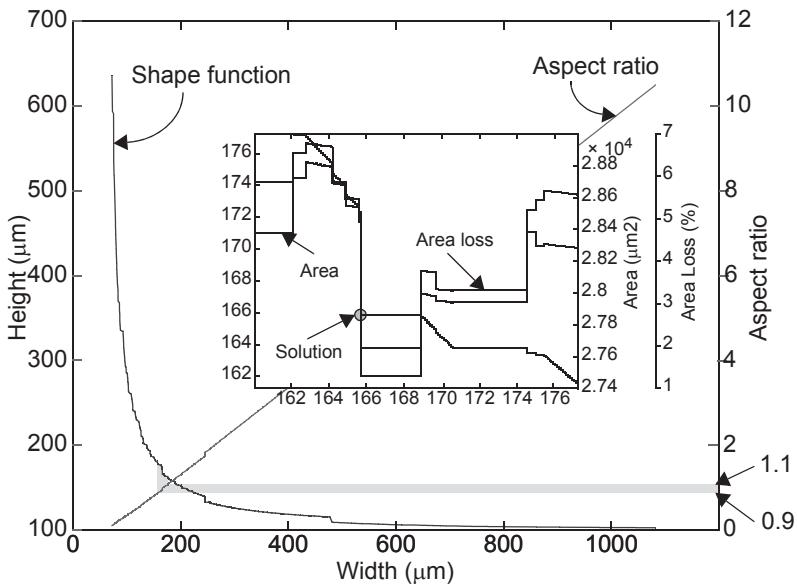

| 2                                                       | Geometrically constrained sizing                                        | 290        |

| 2.1                                                     | Formulation of the problem                                              | 292        |

| 2.2                                                     | Review of previous approaches                                           | 294        |

| 2.3                                                     | An integrated approach                                                  | 300        |

| 2.4                                                     | Experimental results                                                    | 312        |

| 3                                                       | Parasitic-aware sizing                                                  | 324        |

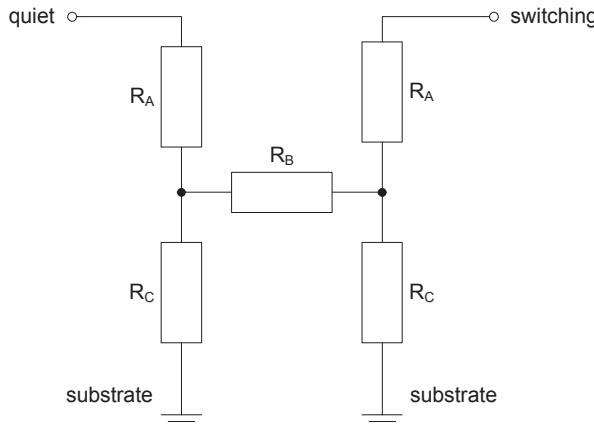

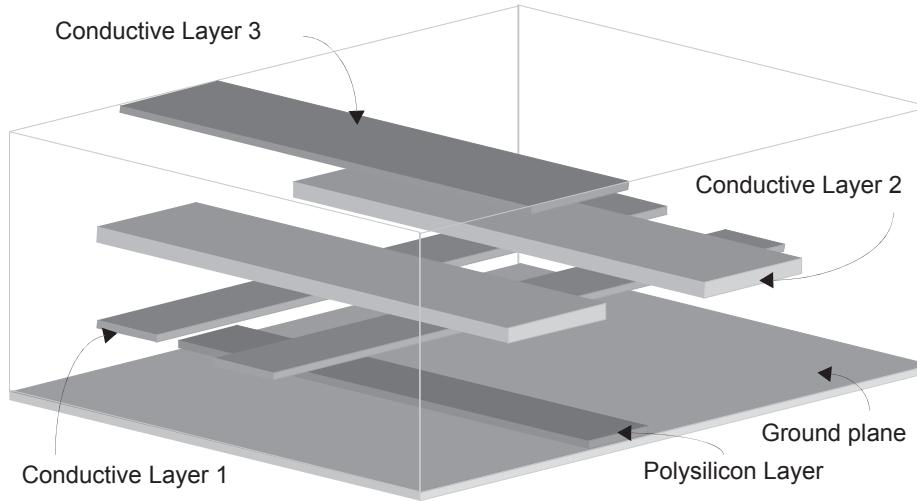

| 3.1                                                     | Layout parasitics                                                       | 324        |

| 3.2                                                     | Extraction methods                                                      | 329        |

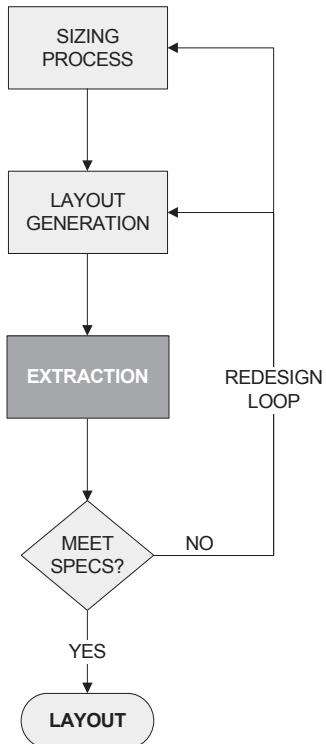

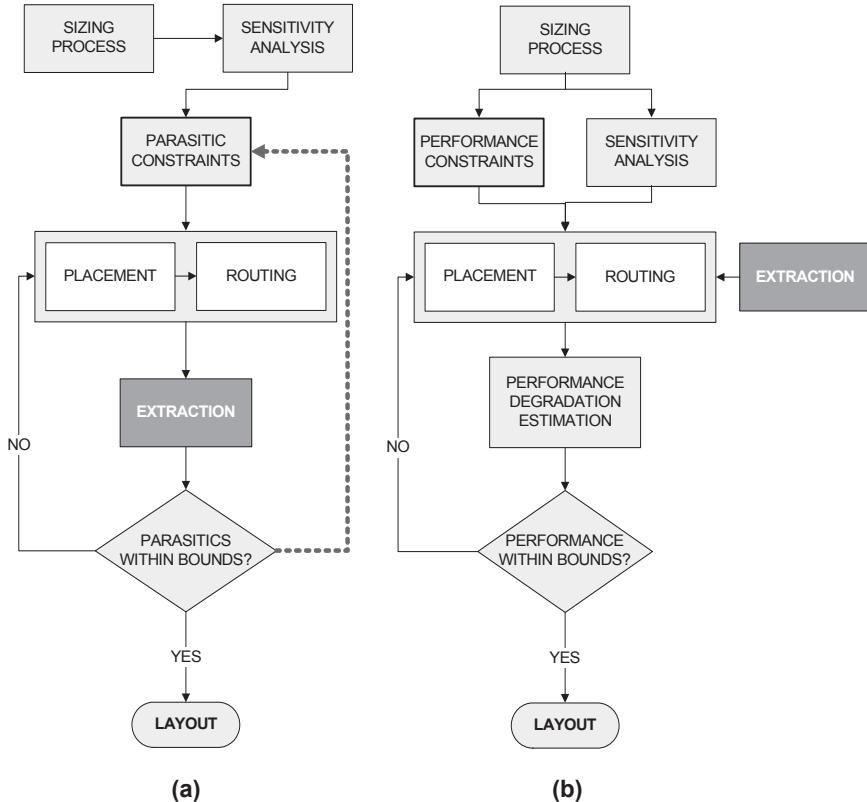

| 3.3                                                     | Extraction of parasitics in the design process                          | 332        |

| 3.4                                                     | Demonstration of the parasitic-aware design flow                        | 337        |

| 4                                                       | Summary                                                                 | 345        |

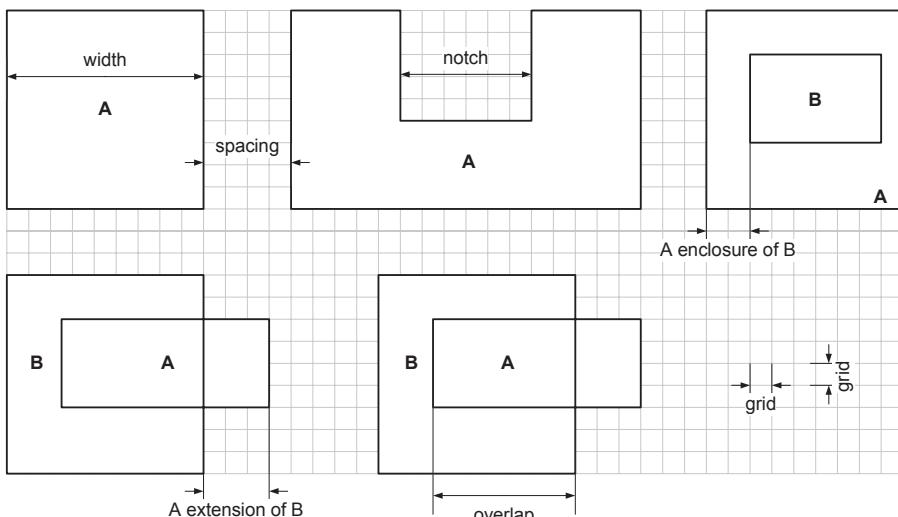

| <b>APPENDIX A: Analog and Mixed-Signal Layout Rules</b> |                                                                         | <b>347</b> |

| <b>REFERENCES</b>                                       |                                                                         | <b>371</b> |

## Preface

Whether the widely cited Moore's Law –forecasting that the number of transistors that can be fit into a chip roughly doubles every two years– has actually represented a roadmap the semiconductor industry has struggled to comply with or a long-term prediction proven true, the fact is that this industry has accomplished spectacular breakthroughs in past decades, pervasively impacting most aspects of everyday life.

Despite these breakthroughs, the spiraling cost of integrated circuit (IC) design is slowly but surely wrapping a noose around the neck of the semiconductor industry. The economics of building today's even-more-complex ICs under even-more-stringent time-to-market requirements (perhaps the most impelling forces in modern semiconductor industry) are already so daunting that the 2003 ITRS report singled out the cost of chip design as "the greatest threat to the continuation of the semiconductor roadmap". The resulting design productivity gap –the gulf between what is possible to manufacture and what is possible to design– will certainly widen, slowing down this industry's phenomenal growth.

In the past, the industry has extracted itself from design cost traps by finding a way to automate portions of the IC design process, allowing designers to become more productive and driving costs back down. Today, the problem cannot be tackled by still relying on 20-year-old design automation technology or by simply hiring more qualified engineers. The design community believes that powerful computer-aided design (CAD) tools and capable CAD-based methodologies do not suffice in order to successfully and utterly bridge the design gap, but that some kind of design paradigm shift must be urgently put on stage.

In this sense, reuse-based design practices are regarded as a promising solution, and concepts such as IP Block, Virtual Component, and Design

Reuse have become commonplace thanks to the significant advances in the digital arena. Although far from being completely settled, an important market has flourished around digital reuse that furnishes design companies with solutions to noticeably improve their productivity rate.

When it comes to analog and mixed-signal (AMS) design, the scenario is, unfortunately, not that optimistic. The current level of AMS CAD, lagging several generations behind digital design automation partly because of the very nature of AMS design –more subtle, hierarchically loose, and handicraft-demanding–, partly because of the comparatively smaller amount of R&D dedicated to AMS CAD, and the huge heterogeneity of AMS circuits, has so far hindered a similar level of consensus and development on AMS reuse-based design, frequently influencing the idea that inheriting digital reuse concepts is impractical or simply unrealizable. It is necessary to remark, however, the importance of improving AMS design productivity: despite the relatively smaller silicon area dedicated to AMS circuitry, the time needed to design this circuitry dominates, in most cases, the total design time. Therefore, any research ultimately targeted at the improvement of the design productivity of ICs should consider AMS design productivity as a goal priority as well. Otherwise, design productivity will eventually get stuck on the AMS design bottleneck.

In this scenario, the research reported in this book tries to demonstrate not only that reuse-based design in the AMS arena is possible, but also that by following such a design paradigm and making use of appropriate CAD tools, techniques, and methods, it is possible to break through the bottlenecks of AMS design and enhance the design productivity. The concept of reuse here cannot be simply based on plug-in pre-designed, fixed circuit blocks out of a design repository, but rather on recycling these blocks; that is, adopting a flexible methodology by which a circuit can be easily and seamlessly adapted to different design specifications, different environments, and different technology nodes and foundries, thereby completing a AMS design project in time.

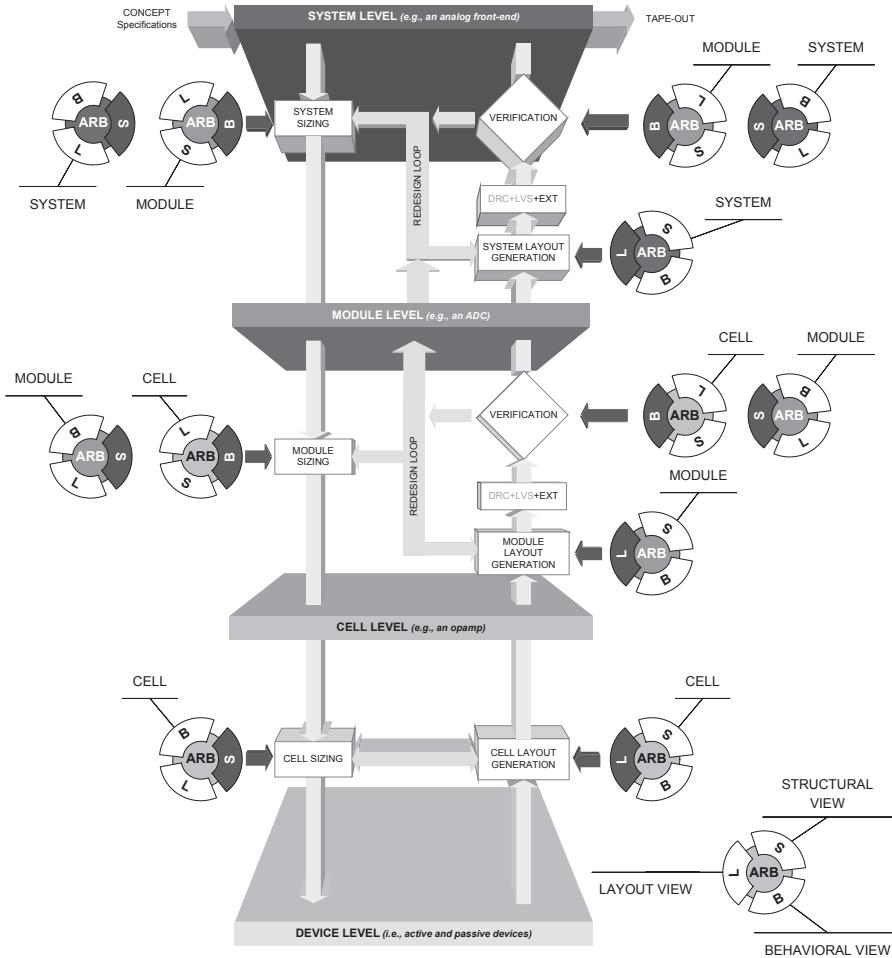

This book presents a framework for the reuse-based design of AMS integrated circuits. This framework is founded on three key elements:

- first, a CAD-supported hierarchical design flow that facilitates the incorporation of AMS reusable blocks. Thanks to this design reuse flow, overall design time can be reduced and increasing AMS design complexity can be efficiently managed;

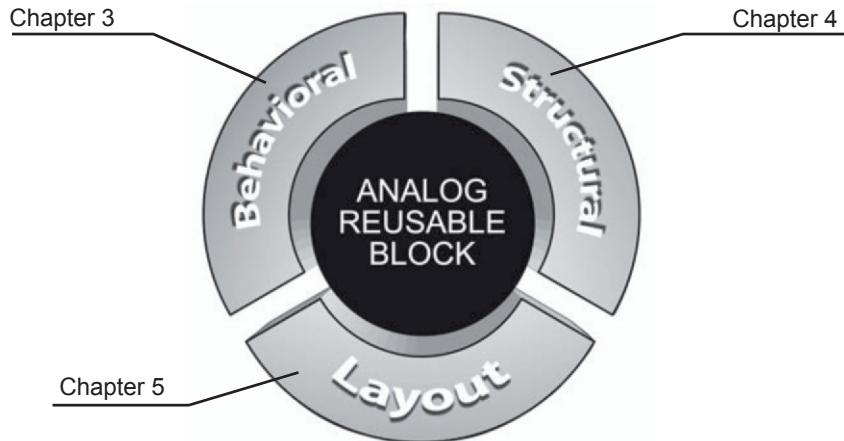

- second, a complete and clear definition of the AMS reusable block. Such definition is structured into three separate facets or views: the

behavioral, structural, and layout facets. Throughout block reuse, design information flows from one facet to another, progressively adapting it to the targeted performance and technology. Each facet is devised to suit a stage of the design reuse flow, at its corresponding hierarchical level. In this way, the behavioral and structural facets are used for top-down electrical synthesis and bottom-up verification, and the layout facet is used for bottom-up physical synthesis;

- third, the set of methods, tools, and guidelines composing the design for reusability methodology, which allows producing fully reusable AMS blocks. This methodology relies on intensive facet parameterization as well as on the capture and encapsulation of design knowledge within each facet.

Although the book undertakes the problem from a general perspective, covering all different stages of the design flow, it makes special emphasis on AMS physical design reuse, as this is one of the most (if not the most) crucial, knowledge-intensive stages of the AMS design flow, thus posing a greater challenge to reuse-based design.

The framework is completed with a synthesis technique that aims at speeding up the design process of AMS ICs by reducing the time-consuming, error-prone iterations between electrical and physical synthesis, traditionally considered as non-miscible design stages. In this so-called layout-aware electrical synthesis, a simulation-based optimization algorithm explores the design space while specific and detailed information of the circuit layout –its geometric features and its layout-induced degradation on the circuit’s performance– is used to improve the synthesized solution, yielding a correct-by-construction physical implementation of the circuit during the first pass.

The framework has been put into practice and assessed on a well-known, commercial design environment (*Design Framework II* from Cadence®). Furthermore, the framework has been validated through an industrial-scale, functional silicon prototype, consisting in an universal IQ transmit interface for wireless communications.

The contents of this book are organized in seven chapters as follows.

Chapter 1 introduces the problem rationale by examining the evolution of the semiconductor industry, analyzing the current challenges, and delving into the causes of the design productivity gap. To set the background of the research, the chapter then proceeds to clearly define the problem by resorting to several key concepts such as hierarchy, abstraction level, and circuit view,

and answering the question of why traditional AMS design methodologies cannot solve it.

Chapter 2 reviews the current state of AMS design automation technology and, in the light of this revision, presents the reuse-based design paradigm. The digital reuse scenario is then examined in order to give insight into the differing requirements of AMS reuse. Afterwards, the chapter surveys the state-of-the-art of AMS reuse-based design. Last, the reuse-based design framework proposed in this book is described.

Chapters 3, 4, and 5 respectively describe the behavioral, structural, and layout facets of the AMS reusable block. The description of each facet follows a three-part structure: what is and what is the facet used for, what requirements does reuse-based design impose on the facet, and how reusability can be built on the facet. Accompanying the descriptions, each chapter contains detailed illustrative examples.

Chapter 6 reports the experimental demonstration of the validity of the reuse-based design framework. This chapter comprises several design experiments, as well as the description and experimental verification results of the silicon prototype mentioned above, whose analog section has been designed under the proposed framework.

Finally, Chapter 7 presents and demonstrates the layout-aware synthesis technique.

The considerations presented in Chapters 4, 5, and 7 are complemented in Appendix A.

The work presented in this book has been partially supported by the TEC2004-01752 Project (funded by the Spanish Ministry of Education and Science with support from the European Regional Development Fund) and the MEDEA+ 2A101-SPIRIT Project.

# Chapter 1

## Introduction

### 1 PROBLEM OVERVIEW: THE DESIGN GAP

Nowadays, the semiconductor industry and the design community are facing some very exciting and difficult challenges. For this industry to continue with its phenomenal historical growth and the well-known Moore's law, advances in all fronts are necessary. Although the integration of more and more functionalities onto a single chip is being proven as an effective strategy in terms of fabrication costs, the design effort has been continuously increasing. Both tightening time-to-market pressures and increasing design complexity are widening the gap between the available number of transistors and the ability to design them. This is even more pronounced in the area of analog and mixed-signal design, since design automation is still very far from its digital counterpart. Furthermore, analog and mixed-signal design methodologies are unable to cope with time-to-market and design complexity, the two fundamental forces driving the semiconductor industry.

In this chapter, the problem is investigated and properly defined and for that purpose this section provides the main motivations of the research reported in the book. First, an overview of the evolution of the semiconductor industry is given to set the background. Then, the design gap problem is discussed and, finally, the impact on analog and mixed-signal design is analyzed.

#### 1.1 Evolution of the semiconductor industry

In the nineteenth century, there were more technology achievements than in the nine centuries preceding it. Then, in the first twenty years of the twentieth century, we saw more advancement than in all of the nineteenth century. Now, paradigm shifts occur in only a few years' time. In the twenty-first century,

it is expected that there will be almost 1000 times greater technological changes than in its predecessor. This fact also holds true for the industry of microelectronics, which, in the past 40 years, has experimented an incredible and rapid improvement in its products. Multiple evidences of this development are all around us. Semiconductor devices are becoming smaller, almost disappearing into the background. Computational power derived is being applied to many areas of human experience: communications, data storage, medicine, genomics, and so on. The electronic industry is now one of the largest industries in terms of output as well as employment in many nations. The importance of electronics in the economic, social, and even political development throughout the world will no doubt continue to increase.

Semiconductor devices have long been used in electronics. By 1947, the physics of semiconductors was sufficiently understood to allow Brattain and Bardeen to create an amplifying circuit utilizing a point-contact “transfer resistance” device that later became known as a transistor. In 1958, Kilby created the first integrated circuit (IC), ushering in the era of modern semiconductor industry.

The sustained growth of electronics has resulted principally from the industry’s ability to decrease exponentially the minimum feature size it uses to fabricate integrated circuits, commonly referred as Moore’s Law<sup>1</sup>. Gordon Moore made his famous observation in 1965, just six years after the first planar integrated circuit was completed. The press called his analysis the “Moore’s Law”, and the name has stuck. In his original paper [Moore65], Moore observed an exponential growth in the number of transistors per integrated circuit and predicted that this trend would continue. In his own words:

*The complexity for minimum component costs has increased at a rate of roughly a factor of two per year [...] Certainly over the short term this rate can be expected to continue, if not to increase. Over the longer term, the rate of increase is a bit more uncertain, although there is no reason to believe it will not remain nearly constant for at least 10 years. That means by 1975, the number of components per integrated circuit for minimum cost will be 65,000.*

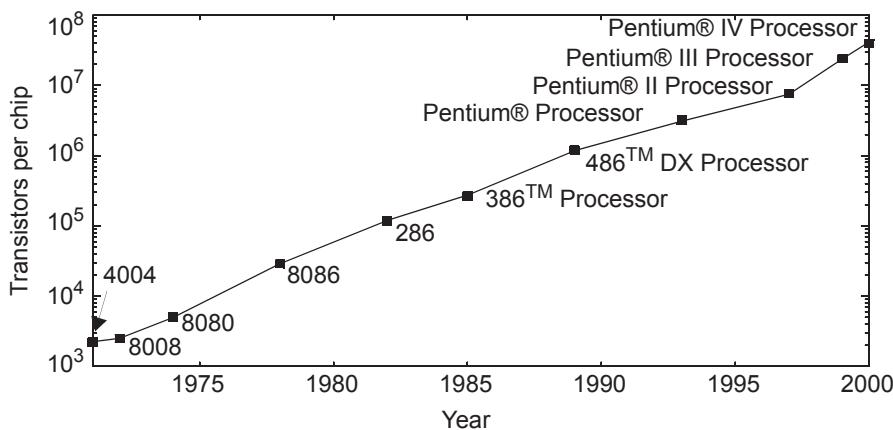

That is, Gordon Moore predicted that the number of transistors that can be fit into a chip would roughly double every year. Later, in 1975, he updated this figure, so the prediction was that the number of transistors would double every two years [Moore75]. The plot in Fig. 1 illustrates this progress. It

---

<sup>1</sup>. This Law actually refers to digital circuits implementing dynamic memories (DRAM), whose topological regularity allows a higher integration capacity, thus giving an idea of the maximum number of transistors that can be integrated in a given fabrication technology.

Figure 1. The Moore's Law with Intel® processors.

shows how the number of transistors of some of the Intel® microprocessors has evolved through time.

As said above, this huge progress in the chip density has been driven by the downsizing of the semiconductor components, such as the MOSFET<sup>2</sup> (also referred as just MOST). By such a downsizing, the number of transistors in the chip is enabled to increase and, therefore, the functionality of the product can be improved. This shrinking of the minimum feature size basically pursues two different goals [Hu93]. First, it is aimed at increasing the density, i.e., the maximum number of devices that can be integrated within a single chip. This requires both shorter transistor channel length and smaller channel width. Second, it is devised to increase the current density in order to enhance the speed of switching transistors, since the larger the transistor current, the smaller the time required to charge or discharge the parasitic capacitors associated to the circuit nodes. This implies short channels and high gate oxide field for higher inversion layer charge densities.

As integrated circuit technology has advanced, semiconductor industry has moved from single devices to small scale integration (SSI), with 5 to 20 logic blocks per chip, to medium scale integration (MSI), with 20 to 200 logic blocks per chip, to large scale integration (LSI), when thousands of transistors were put into a single integrated circuit, and, finally, to very large scale integration (VLSI), making integration of hundreds of thousands of transistors onto a single chip possible. In 2001, the Semiconductor Industry Association (SIA) published a technology roadmap of semiconductors (the ITRS report

<sup>2</sup>. The MOSFET, acronym for metal oxide semiconductor field effect transistor, is by far the most common field effect transistor in both digital and analog circuits.

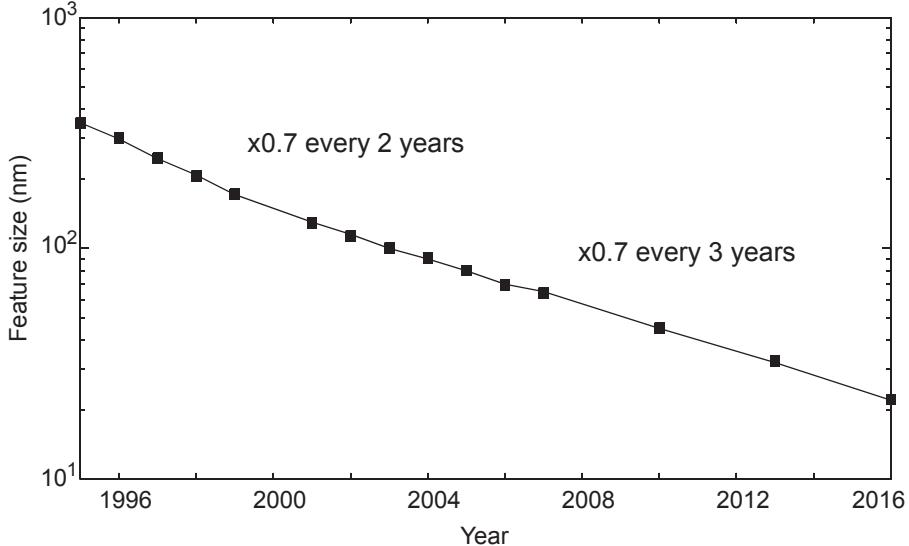

[Itrs01]) in which the dimension of every future generation is predicted, as shown in Fig. 2, until the year of 2016.

Figure 2. Minimum feature size evolution.

Note that the feature sizes used now and predicted for future chip fabrication are incredibly small: the human hair is 100,000-nm wide, a red blood cell is ‘just’ 7000-nm wide, and the human immunodeficiency virus (HIV) is 100-nm wide. From the plot in Fig. 2, it can be observed that the minimum feature size has shrunk at a rate of  $x0.7$  every 2 years, until 2001. Since then, the forecast is that such feature will be downsized by a factor of  $x0.7$  every 3 years. This represents the creation of a new technology node (i.e., a significant technology progress governed by the smallest feature printed) every 3 years.

Thanks to this capacity to integrate more functionality onto less silicon area, designers are putting entire systems on a single chip. Thus, chips that are self-contained systems, including processing, memory, and input-output functions, known as systems-on-a-chip (SoCs) [Abid99], are providing us with an overwhelming capability to create new products that will impact the way we work, live, learn, and play.

Basically, two types of SoC design exist: one coming from the application-specific integrated circuit, or ASIC<sup>3</sup>, and the other from the custom integrated circuit world. The former type of design is mostly digital, comprising programmable elements, such as control processors and digital signal

<sup>3</sup> An ASIC is a circuit designed to suit a customer’s particular requirement, as opposed to general-purpose designs, such as DRAMs or microprocessors.

processors or DSPs, memory sub-systems, complex bus architectures, an input/output interface to the external system, software elements, complex bus architectures, clock and power distributions, test structures, etc. The processor can be anything from an 8-bit 8051 to a 64-bit RISC. The memory sub-system could include SRAM and/or DRAM. Analog and mixed-signal blocks may also be present, but it is likewise possible that some of these AMS blocks, such as radio frequency components, remain as a separate chip for this type of design. The other type of SoC design is known as analog and mixed-signal SoC (AMS-SoC). This kind of SoCs inherits the custom analog and mixed-signal design style. These chips are high-performance circuits and typically have complex signal paths through both analog and digital components. Examples of these designs include xDSL front-ends, disk drive controllers, and RF front-ends. Unlike the case of ASIC-SoCs, the analog and mixed-signal part is no longer an “option”: it is the critical and probably the differentiating part of these integrated circuits with the digital part optional as to whether or not it is integrated [Kund00].

There are many reasons for using SoC concepts. Apart from the enhanced portability due to smaller system size, the system performance is improved, and the system power dissipation can be reduced as well. Despite these benefits, however, designers have to deal with a challenging issue: the increasing cost of designing SoCs. The following section explains the causes behind this increase and its impact on the design community, and, especially, on the analog design arena.

## 1.2 The design gap

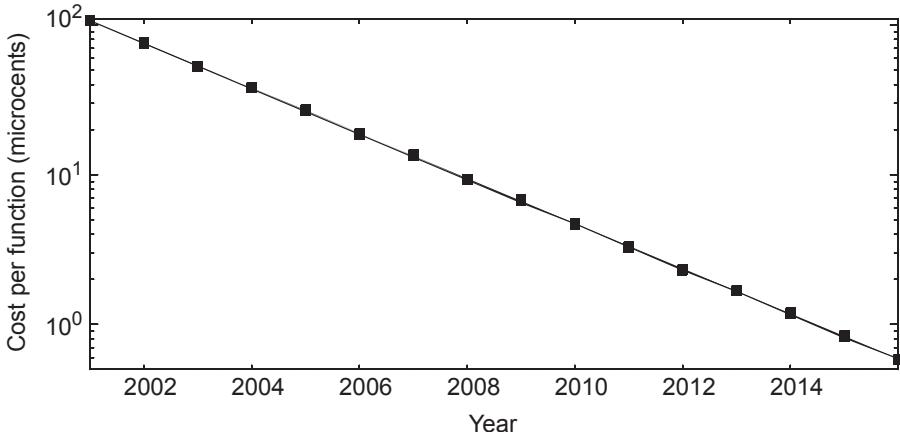

Although the wafer fabrication costs grow significantly between technology nodes, the fabrication cost per function has been traditionally dropping exponentially, as it is illustrated in Fig. 3 [Itrs01], mainly because more functions can be integrated into the same wafer. The historical trend has been reducing the cost per function ratio by 25 to 30 percent per year.

Unfortunately, the cost of a chip in terms of design procedures, design tools, and human resources, does not remain constant. Actually, while designer productivity has slightly improved with time, there are factors causing this productivity to be insufficient to cope with advances in chip density. Consequently, the cost of the chip design is growing with the complexity of the circuit: although the integration of a system onto a single chip may have attractive manufacturing costs, it also has “frightening” design costs.

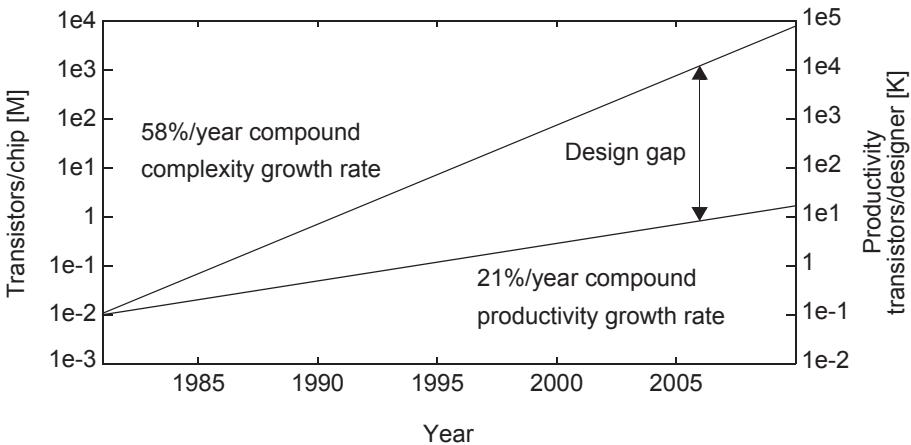

As a consequence, there exists a widening design productivity gap, in which the number of available transistors grows faster than the ability to design them meaningfully, as illustrated in Fig. 4 [Itrs99]. In this figure, it is visible that the separation between the chip density and designer’s productivity

Figure 3. Exponential drop of the cost per function.

Figure 4. Design Gap.

is growing as fabrication technology evolves. Actually, the overriding message in the 2001 ITRS report (still present in the 2003 report [Itrs03]) is that design cost is the greatest threat to continuation of the semiconductor industry's phenomenal growth [Itrs01].

In order to understand the causes of this design gap, that is, why the design community is unable to cope with the continuously increasing chip density, and, therefore, discern what possible solutions can be provided, it is first necessary to analyze the challenges and driving forces guiding the evolution of the design community. The first driving force is the availability of shrinking process technologies, introducing new problems and effects that need to be accounted for during the design process, being its more direct consequence

the rise of design complexity. The other fundamental driving force is the stress on reducing the time-to-market figure of a new chip product. Let us now examine in detail each one of these driving forces.

### 1.2.1 Time-to-market

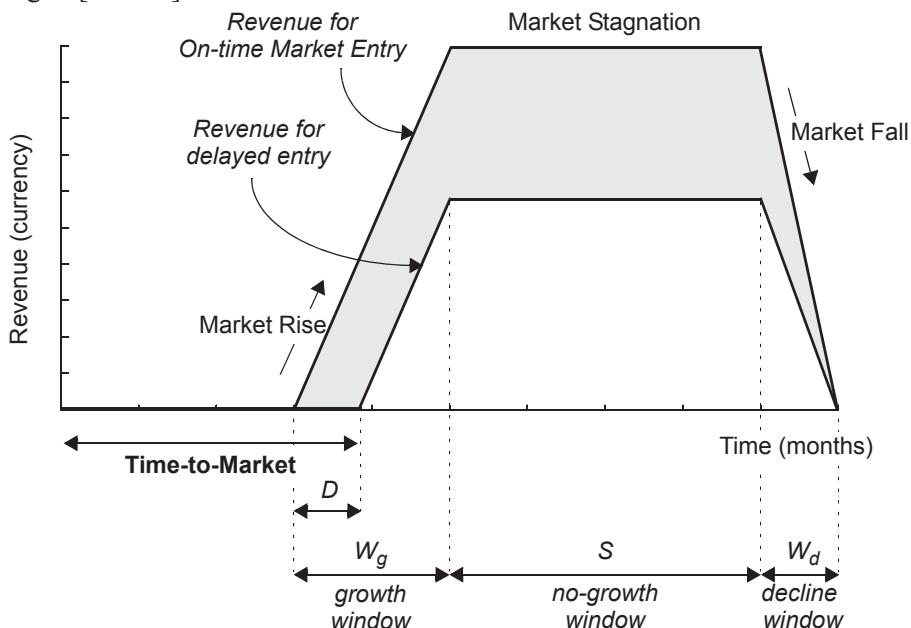

The time-to-market (TTM) can be defined as the time it takes to get a product from the concept to the marketplace. The TTM is a very critical factor for ASICs and SoCs that eventually end up in any market place: if the vendor misses the initial market window, prices, and, therefore, profit can be seriously eroded. The first vendor to market with a new product makes a profit, and obtains immediate feedback to improve the next product generation. The second vendor to market will only break even, but the third vendor will surely lose money. The importance of dealing with TTM constraints is illustrated in Fig. 5 [Levi92].

Figure 5. Importance of delayed market entry.

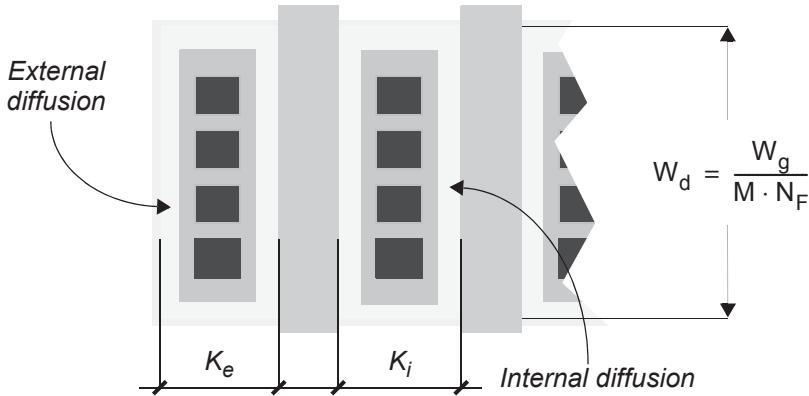

Every product has a market growth window,  $W_g$ , a period of no-growth or stagnation,  $S$ , and a market decline window,  $W_d$ , thus being the lifetime of the product equal to  $W_g + S + W_d$ . The product begins to gain market acceptance and sales grow rapidly as the product reaches the market. Then, as the product matures, the competence grows as other vendors enter the stage and the product becomes thereby depreciated, all resulting in a market stagnation. Finally, as technological process advances and superior products are

launched, product sales start declining. For an on-time market entry (that is, zero time delay  $D$ ), there is a total expected revenue,  $R_o$ . For a delayed product, however, there is a total revenue loss,  $R_L$ , which can be easily calculated by computing the area of the shaded region in Fig.5. The relative revenue loss,  $r_L = R_L/R_o$ , is then expressed by the following equation:

$$r_L = \left[ \frac{D(2W_g - D + 2S + W_d)}{W_g(W_g + W_d + 2S)} \right] \quad (1)$$

For instance, according to Eq. (1), a typical four-month delay over a growth window of 1 year, a stagnation period of 1 year, and a market decline window of half a year, corresponds to a relative loss of 40 percent of the total revenue corresponding to a product with zero time delay.

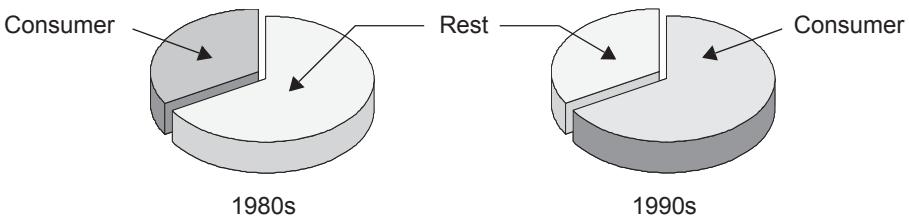

A major reason for hardening TTM pressures is the continued “consumerization” of the electronic marketplace [Kund00]. As shown in Fig.6, the continuous improvement in electronic products is accompanied by a migration away from traditional applications (military and industry) to the consumer products, which, actually, have the shortest development cycle times [Rash01], and product life cycles can be only three to six months long. Yet, to design a SoC chip of 10 million transistors or more can take several years [Rein02].

Figure 6. Consumerization of electronic products.

Another factor contributing to today’s TTM requirements is that time to volume has decreased significantly. It took about 12 years to sell 1 million color TVs, and 3 years to market 1 million mobile telephones, but only about 1 week to sell 1 million units of the latest video game console [Rein02]. This means that accomplishing TTM schedule must be accompanied by a first-time correct product. That is, circuit designers have to rely on methods and tools that guarantee a rapid transition from idea to market, and avoid, as much as possible, the presence of mistakes or bugs in the final product.

### 1.2.2 Design complexity

Design complexity means different things to different people. The first question to answer is what metric must be used to measure design complexity: the number of transistors or components, the area size, the size of the design

team, or even the number of several disciplines and types of expertise involved in a project. If we take the transistor count to measure design complexity, there is a significant difference upon the type of integrated circuit considered. For example, the difference in design cost or effort between a 256-kBytes and a 256-MBytes memory chip is not all that great, since there are many repetitive elements on a memory chip [Rein02]. However, ASIC-SoC and, especially AMS-SoC designs, may have many different components, digital, analog, and mixed-signal, the latter two requiring major design efforts. Therefore, design complexity for SoCs cannot be compared just in terms of the number of transistors. Actually, the main factors prompting an increase of the design complexity are the following [Giel00] [Itrs01]:

- Increasing number of transistors per chip: there are both analog and digital components that need to be co-designed, with numerous design issues (such as increasing leakage and crosstalk) involved.

- New signal processing algorithms and system architectures: emerging applications require new to-be-developed functionalities.

- Larger design teams: designing a SoC require larger design teams, simply because of the different nature the SoC components, which often require many kinds of expert knowledge.

- Shrinking processes: due to the fast evolution of the fabrication technology and provided that a circuit is planned to be implemented in upcoming fabrication technologies, the expectation for a change in the process parameters should be taken into account during its design phase.

As it can be easily noted, design time will surely increase when design complexity grows. This is in clear contrast with the need to market the product as quick as possible. Therefore, designers have to face the design challenge of managing the TTM-design complexity trade-off. The key to deal with this trade-off, i.e., correctly managing design complexity while meeting TTM goals, lies in adopting appropriate and well-structured design methodologies which must be supported by efficient computer-aided design (CAD) tools.

### 1.3 Analog design automation

According to the SIA definition, a CAD<sup>4</sup> resource is a sophisticated, computerized workstation and software used to design integrated circuit chips [Glos03], which encompasses not only separate and specific-purpose tools, but also global design methodologies with which human designers can build functionality while satisfying intended performance specifications [Chang97]. The goal of CAD is to reduce the manual design time required for circuit design. In this book, CAD tools and CAD methodologies will be referred as the two fundamental concepts of CAD. The CAD methodology must be consistent enough to properly guide the CAD tools towards the complete satisfaction of all chip performance requirements [Chang97].

In the digital circuit domain, where information is represented as numbers with discrete (non-continuous) values, usually expressed as a sequence of binary digits (ones and zeros), CAD tools are fairly well developed, widely used, and commercially available today. There are several reasons explaining this. The most important one comes as a consequence of the very nature of digital circuits. These circuits work by “flipping” transistors on and off to the 1 and 0 states. Thanks to this Boolean representation of the digital systems, their functionality can be easily translated to algorithmic constructs using programming languages. This eases the automation of many of the design tasks involved, certainly for the lowest levels of the design. In this way, digital systems can be described through high-level languages, and digital CAD tools perform the task of synthesizing this description into a structural representation. This representation can be then transformed into the final physical representation of the digital circuit, for the selected technological process. In addition, digital circuits have a great immunity to noise, because the signal values are associated to just discrete 1’s and 0’s. This noise margin further facilitates automation of every design step. Therefore, the design effort can be focused on creating more and better electronics, directing it towards trade-offs between power consumption, speed, and area. Lastly, it is necessary to note that the digital integrated circuit market is quite large, with numerous established vendors investing on CAD development, resulting in a steady stream of efficient digital CAD tools. Although the level of computer digital design automation is far from the push-button stage as design complexity is rapidly increasing, the development of digital CAD tools and methodologies are moderately keeping pace with chip density. Nevertheless, a limit is being reached in many areas (e.g., verification) and, consequently, the digital design gap is slowly but steadily widening.

---

<sup>4</sup>. CAD for microelectronics is also known with the name of electronic design automation (EDA).

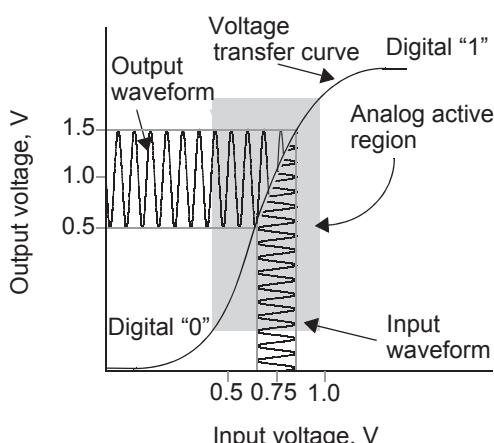

Figure 7. Analog vs. digital behavior.

log and mixed-signal design entails specialized knowledge and almost handicraft design skills, usually acquired after many years of experience. Some of the characteristics of analog and mixed-signal design making the automation of common analog design tasks so difficult are the following:

1. **Heterogeneity.** Analog and mixed-signal functionalities can be implemented through a **wide range of circuit blocks**, and the same function can be accomplished with several different circuit topologies, each one suited to specific applications. There are hundreds of circuit topologies for analog and mixed-signal circuits and systems (containing 10-5000 devices) in use today. Besides, the **spectrum of performance specifications** for any analog and mixed-signal circuit is much **larger** than for digital circuits. For instance, a simple operational amplifier (opamp) has, to say the least, 10 performance requirements which are typically continuous (such as small signal DC gain, bandwidth, phase margin, slew rate, settling time, output voltage swing, input offset, noise, area, power consumption, and so forth [Koh90]). On the other hand, digital standard<sup>5</sup> cells usually have 2 performance parameters, power and timing. A digital standard cell library probably contains around 1000 cells, arranged as the rough product of 10 logic functions (NAND, NOR, flip-flop, etc.), 10 different input/output alternatives (NAND2, NAND4, and so on), and 10 different timing and power alternatives per cell, while even a small

Unfortunately, for analog and mixed-signal designs, the picture, so far, is even worst. As illustrated in Fig. 7, an analog system carries signals in the form of, for instance, voltages, currents, and charges, which are continuous functions of the continuous time variable [Greg86]. Thus, in contrast to digital circuits, analog systems work by biasing the transistor somewhere between what digital designers would call fully on ("1"), and fully off ("0").

<sup>5</sup> A standard cell is a predefined circuit element that may be used to create an integrated circuit more easily than through design.

analog cell with 10 performance parameters, has  $2^{10} = 1024$  variants, even limiting the value of each parameter to a “low” and “high” value (which is not the usual case) [Leen01]. This is the reason why this analog diversity cannot be tackled just with a library containing all alternatives of a complete set of analog and mixed-signal cells. Last but not least, each individual device (active or passive) in any analog and mixed-signal circuit has a **wide range of size values** as well. Consider, for instance, the parameters defining a MOS transistor: length, width, number of fingers, layout style, drain and source area capacitances, number of contacts, etc., most of them bearing one or two orders of magnitude variations. A particular set of block performance specifications can be attained with multiple variants of the whole set of device size values, and, furthermore, there is a strong interaction between device sizes and the overall performance of the analog and mixed-signal circuit. Therefore, fine tuning of this set to obtain highly optimized circuits (e.g., in terms of area or power consumption) is a crucial task of analog and mixed-signal circuits.

2. **Sensitivity.** Analog and mixed-signal circuits are extremely sensitive to second and higher-order non-ideal effects. Some of these effects are caused by the imperfect nature of the fabrication process and materials involved: device mismatch, parasitic capacitances, and temperature or biasing variations, among others, may critically jeopardized the foreseen performance of the integrated circuit [Chang97]. Another source of high-order effects is the sensitivity of analog and mixed-signal to system-level interactions. Due to capacitive and inductive crosstalk and substrate and power-supply noise coupling, and the peaking nature of digital circuits, the desired performance of the analog and mixed-signal part of the chip can be easily worsened. A direct consequence is that layout precautions should be taken in order to isolate the analog and mixed-signal parts from the digital part. Another consequence is that the design of the digital and the analog and mixed-signal parts should not be separated. Besides, since design decisions must, to a large extent, change as the technological process is changed, direct process-to-process reuse of an integrated circuit is not feasible.

3. **Hierarchy.** As opposed to digital circuits, hierarchy is not so strictly and clearly defined for analog and mixed-signal designs. As it is well known, different hierarchical levels are described using different levels of abstraction in any digital application, whereas, in analog circuits, voltages, currents, and impedances must all be considered at all hierarchical levels. It is thus not possible to establish higher levels of

abstraction that shields all the device-level and process-level details when designing at higher levels of the hierarchy. This close interaction between hierarchical levels forces the designer to take into account how a single change in one level affects the higher or lower levels of the hierarchy. Consequently, no straight automated means to switching from one level to another exist.

4. **High-performance.** As increasingly demanding electronic applications call for more aggressive digital signal processing, the performance of the analog and mixed-signal components (progressively pushed to interface the inherently analog world with the digital signal processing cores) is consequently required to be higher. In most cases, such higher performance is achieved by taking into account the correlation between electrical parameters and their variations due to statistical fluctuations of the chip fabrication process [Chang97]. This requires extremely careful design, which cannot be easily translated into computation algorithms, and, therefore, easily automated.

Due to all these features, analog and mixed-signal design is still regarded as less systematic, far more knowledge-intensive, and heuristic<sup>6</sup> than digital design. Consequently, a large amount of analog and mixed-signal circuits are still designed without any really robust and commercial CAD tools but a SPICE-like simulation shell and an interactive and scarcely-automated layout environment [Giel00]. Therefore, analog design turns out to be a time-consuming, prone-to-errors effort. As fabrication technology progresses and new technology nodes appear (and feature size shrinks as well), analog and mixed-signal designers are unable to keep the pace and deal with increasing TTM pressures and design complexity.

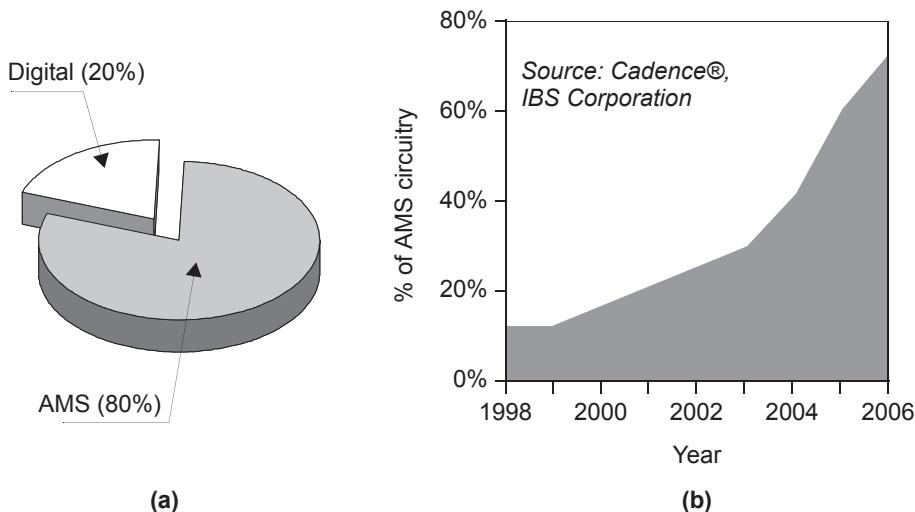

In AMS-SoCs, the design of the analog and mixed-signal components is a bottleneck of the overall design process, as shown in Fig. 8(a). Current estimates indicate that 60% of today's ICs include some analog or mixed-signal content, as illustrated in Fig. 8(b). In addition, the time required to design this analog or mixed-signal content usually dominates the total design time. For the semiconductor industry to maintain its design productivity and keep providing high-quality yet cheap electronic products, design time and cost of the analog circuitry, from the description of its specifications to first-pass silicon, has to be reduced. To this end, it is clear that an efficient CAD methodology and adequate CAD tools to design both analog and mixed-signal circuits are urgently required.

---

<sup>6</sup>. The word *heuristic* is derived from the Greek word *heuriskein* (ευρίσκειν), which means *to discover*. It refers to a common-sense set of rules intended to increase the probability of solving some problem.

Figure 8. (a) Relative design time for the analog and digital parts of an AMS-SoC. (b) Percentage of chips with some AMS content.

## 2 PROBLEM DEFINITION

As explained in the previous section, there exists an urgent need for CAD tools and methodologies specifically tailored for analog and mixed-signal integrated circuits that render a design process significantly enhanced in these two aspects:

- **Rapidness**, by reducing the overall design time, thus improving design productivity and meeting TTM requirements.

- **Correctness**, by increasing the likelihood of first-pass right silicon with an adequate management of the increasing complexity of analog and mixed-signal designs.

In order to correctly define the problem, it is necessary to examine the currently available methodologies and tools in detail, and then analyze where do they fail to cope with the goals of rapidness and correctness. But prior to such analysis it is useful to revisit some important concepts.

### 2.1 Hierarchy, abstraction, and views

To master the ever increasing design complexity of both the digital and analog parts of integrated circuits, there are two concepts, **hierarchy** and

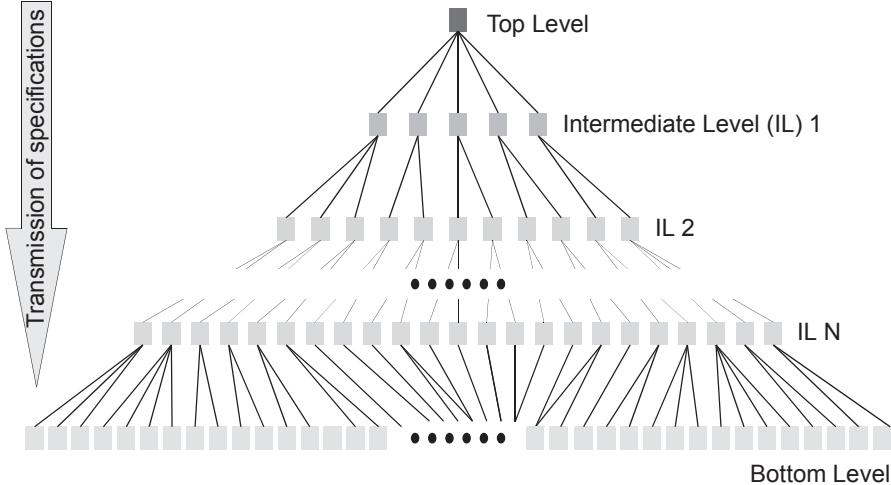

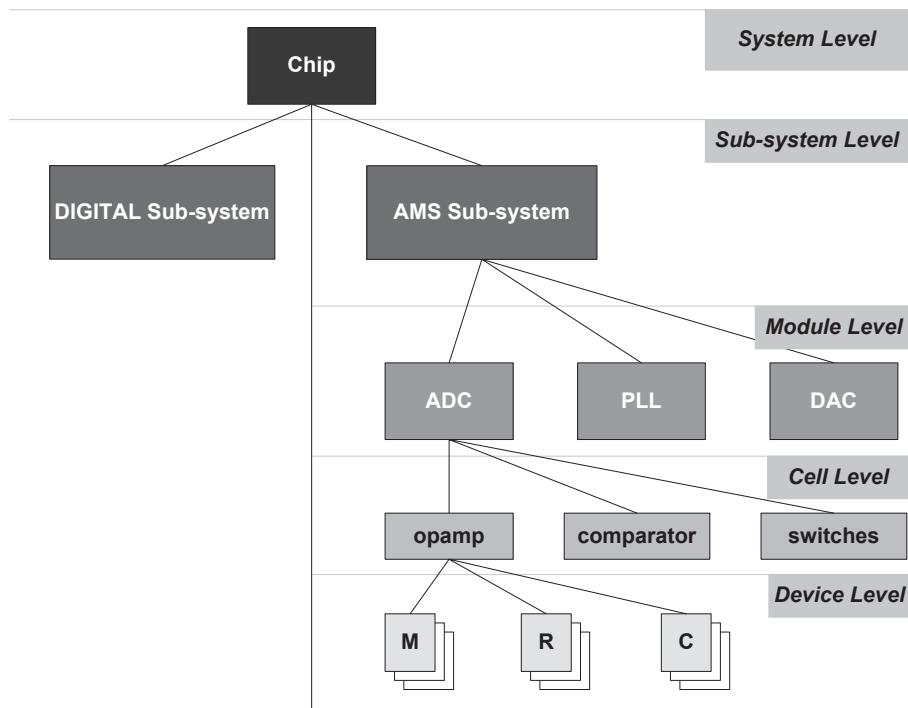

**abstraction**, that are commonly used throughout the entire design process [Donn94a]. Hierarchical design is commonly used in programming as a procedure in which the whole list of primitive statements is managed through proper calls to simpler procedures, possibly involving many of the primitive statements. Each procedure breaks down the task into smaller operations until each step is refined into a procedure simple enough to be written directly. This *divide-and-conquer* technique reduces the complexity of the whole process by recursively breaking it into manageable pieces. Chip designers also use this approach: it is then easier to understand a 1,000,000-transistors hierarchical SoC design than the same design expressed directly as a million transistors wired together. In this way, the required specifications for the complete design behavior can be passed down the hierarchy, reducing the overall complexity of the chip design process, as it is illustrated in Fig. 9.

Figure 9. Design hierarchy.

A crucial benefit from hierarchical design is that, as it will be explained in following chapters, hierarchy permits reusability of design knowledge [Toum95]. For instance, the knowledge and expertise used to design a voltage comparator (a building block in the hierarchy of, for instance, an analog-to-digital converter) can be used later when designing any other circuit using that comparator. An important related idea is that a modification that takes place at a certain level of the hierarchy is effectively propagated to all the hierarchical levels above the modified one.

But, as it was said in the previous section, there is a relevant difference of digital and analog hierarchies. Whereas digital hierarchy is well defined (with RTL, structural, and gate levels), the analog hierarchy has no strictly defined levels (and, certainly, not generally accepted). The main reason for this lack

of any rigid, formal hierarchy is that the different levels are not based on different levels of signal abstraction, but rather on different and not always standardized structural decompositions over different levels.

Therefore, design abstraction turns out to be a critical concept to integrated circuit design, too. The level of abstraction measures the magnitude of the link between the model and each one of the physical devices contained in it. As physical effects become more important and increase design complexity, the total range of abstraction levels encountered in a single design flow is continuously growing and pulling abstraction and detail in opposite directions [Kund00]. Like programmers, chip designers use multiple levels of design abstraction to meet performance goals for very large designs. For digital designs, the simplest example of abstraction is the logic gate, which is just a simplification of the nonlinear circuits used to build the gate: the logic gate accepts binary boolean values and has a unit delay. Some design tasks (e.g., accurate delay calculation) are hard or impossible when cast in terms of logic gates; others (e.g., logic optimization) are, however, easier if logic gate abstraction is used. In other words, each design task requires a particular abstraction level. For analog designs, different hierarchy levels do not always have a different abstraction level; on the contrary, it is more than likely that a number of levels share the same description method. For example, several abstraction levels can be used in the same hierarchical level, depending upon the design tasks involved.

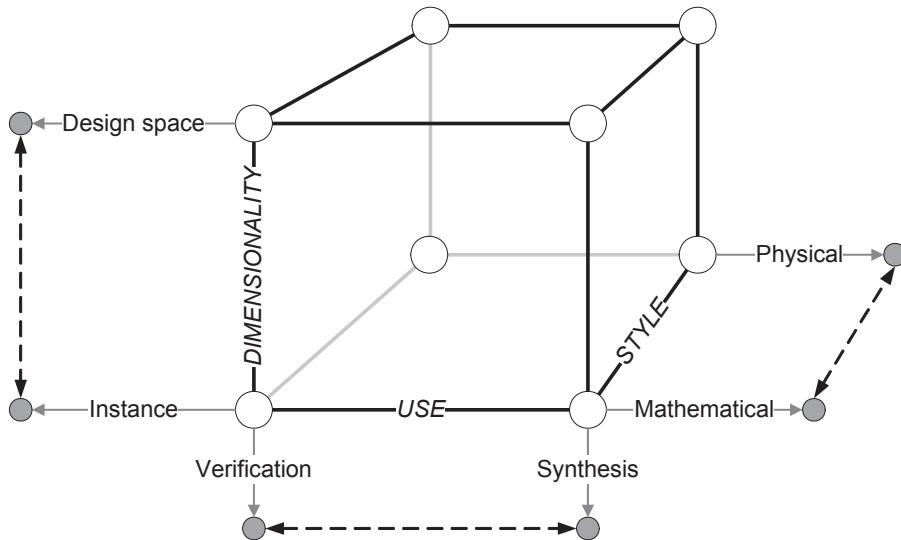

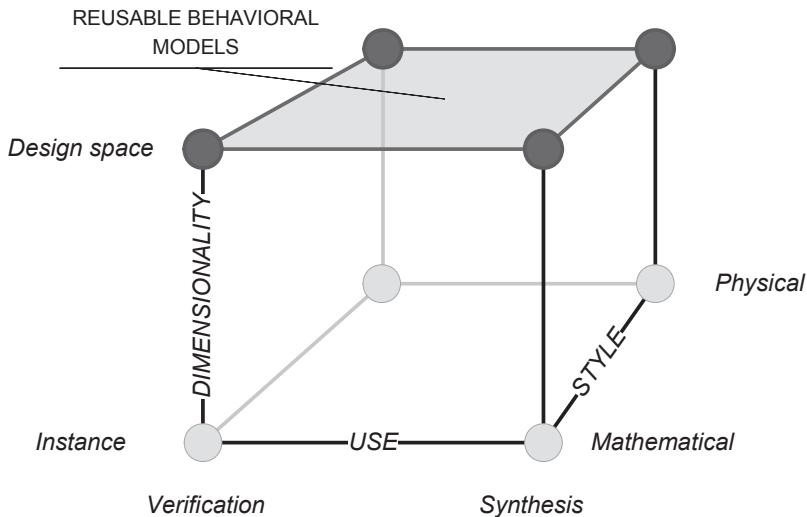

Another common concept is the use of multiple **views** to provide differing perspectives [Rubin87]. Each view contains an abstraction of the circuit, which is useful in aggregating only the information relevant to a particular facet of its design process. A circuit can be viewed physically as a collection of polygons on different layers of a chip, structurally as a collection of transistors, resistors, capacitors, etc., or behaviorally as a set of operational restrictions in a behavioral-description language. It is useful to be able to flip among these views when building a circuit because each has its own merit in aiding design.

## 2.2 The AMS design flow

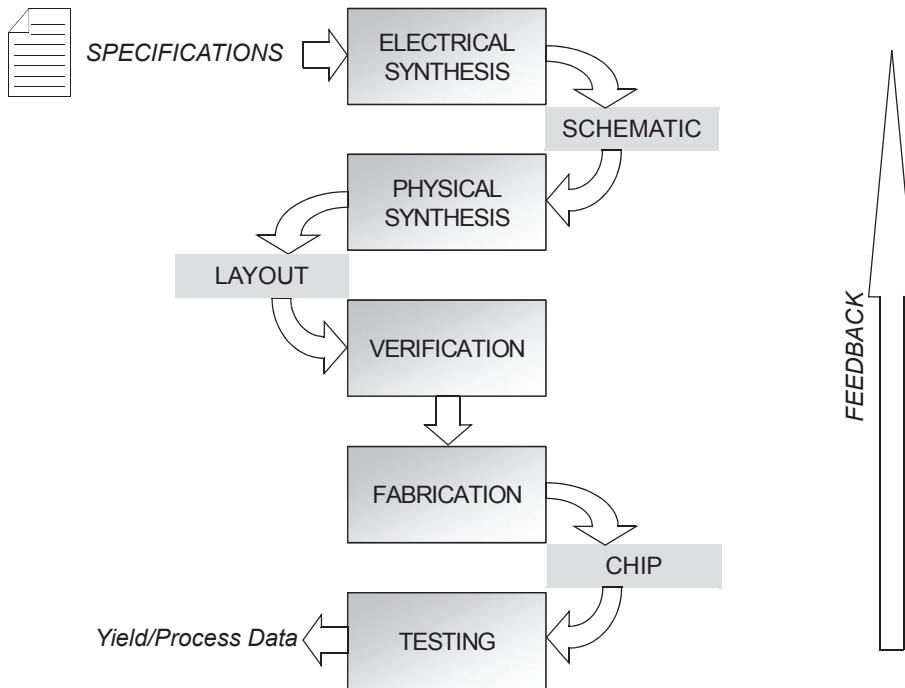

Figure 10 shows a general design flow illustrating the main stages of the creation of integrated circuits, both digital and analog [Donn94a] [Chang97].

The five stages of the flow are described below:

1. **Electrical synthesis:** the design process starts with the specification of the circuit's performance that has to be realized. A typical example is to specify the maximum power consumption or minimize the area occupation, minimizing thus the overall production cost. The output

Figure 10. Typical design flow of an integrated circuit.

to this process is a *schematic*, a list of all the devices (transistors, resistors, capacitors, etc.) composing the circuit which specifies not also how they are connected (a list of nets), but also the characteristics of each single device (e.g., transistor width and length).

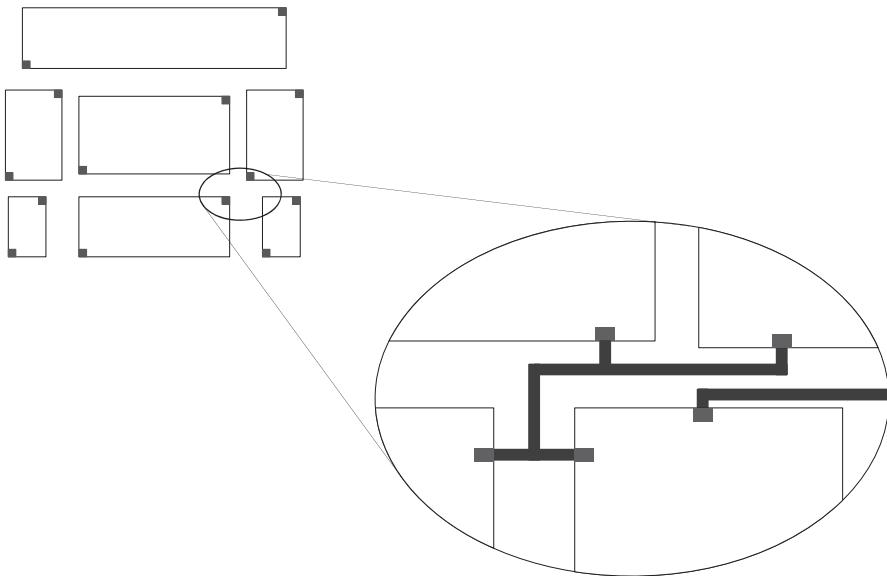

2. **Physical synthesis:** the goal of this phase is to obtain the physical representation of the circuit schematic, known as layout, a collection of geometric shapes and layers, later used in the fabrication process. Layouts can be generated either manually or automatically. The layout must be checked for errors with respect to the collection of design rules dictated by the technological process, and for its complete correspondence with the intended schematic.

3. **Verification:** after completion of the layout, it must be verified that the initial specifications have been met. This verification is usually carried out through simulation of the whole circuit, which may include the unavoidable layout-induced degradation<sup>7</sup>.

<sup>7</sup>. Strictly speaking, verification is also required at many other places of the design flow, for instance, after completing the electrical synthesis of every circuit's building block. The aim of Fig. 10, however, is just to highlight the various tasks of the IC design flow, which, to keep things simple enough, have been clearly separated. The role of verification will be specified in the next pages.

4. **Fabrication:** once the layout has passed the verification phase, it is sent for fabrication. This process typically takes two to six weeks. The output of the fabrication process is the encapsulated circuit (chip).

5. **Test:** the final step of the design process is the test of the chip. Yield and process information are gathered to determine the actual cost of the product for improving future designs.

During the entire process, feedback can take place at any time when the design fails to meet the initial required specifications. The number of synthesis-verification-synthesis loops can be small (only two or three iterations) or large, depending upon how much redesign is necessary. In this book, only the first three stages, electrical synthesis, layout synthesis, and verification, will be considered.

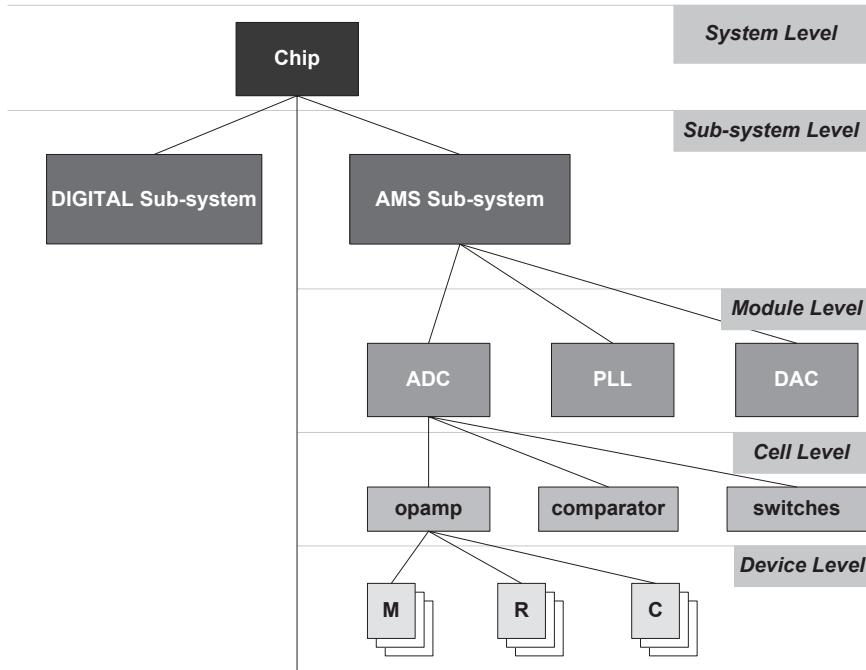

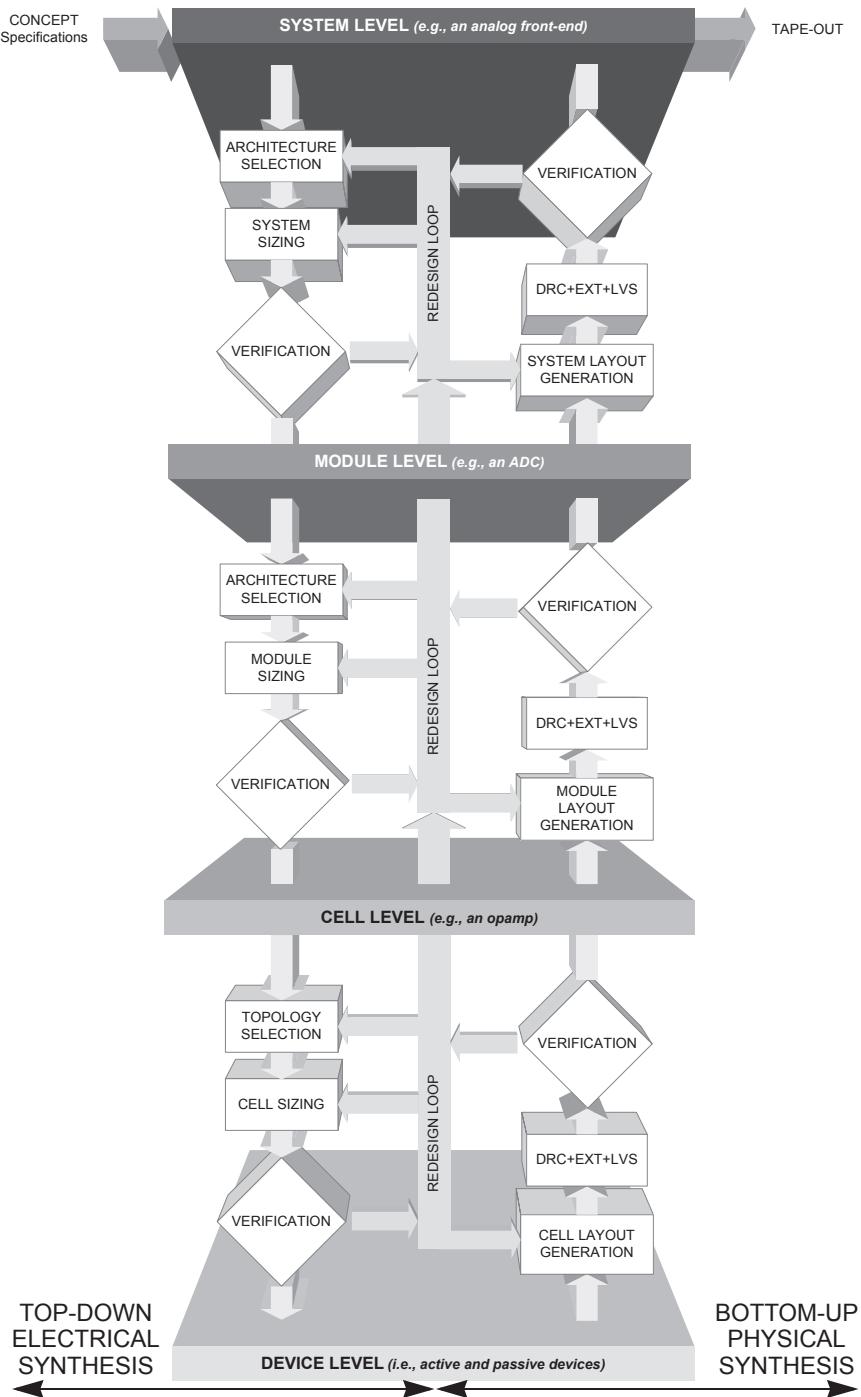

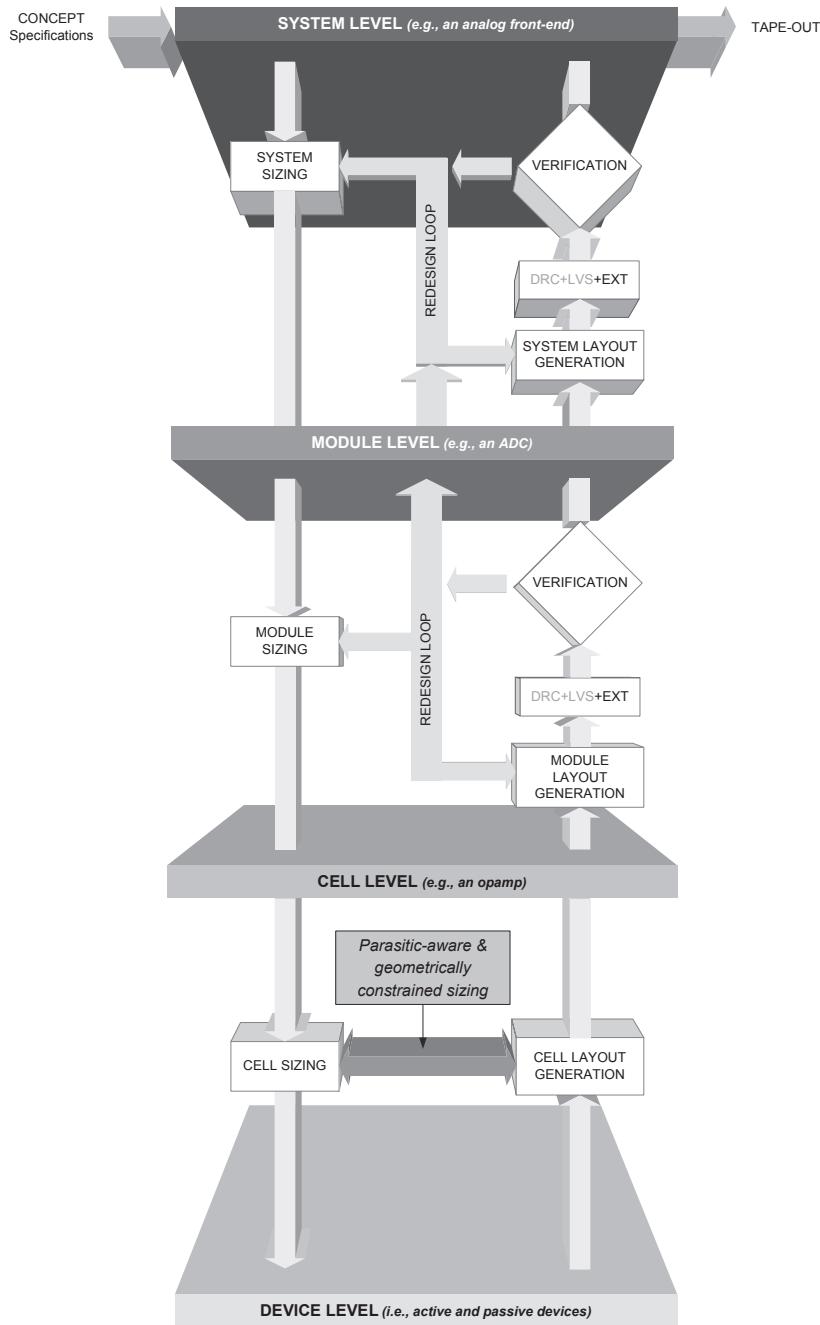

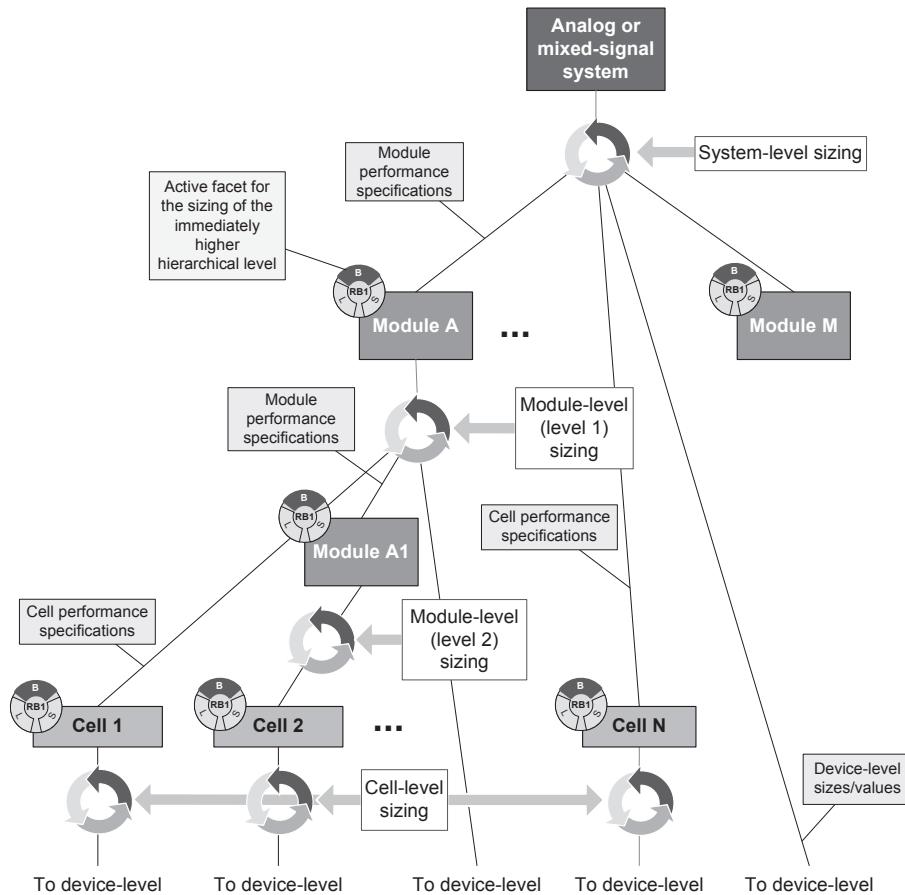

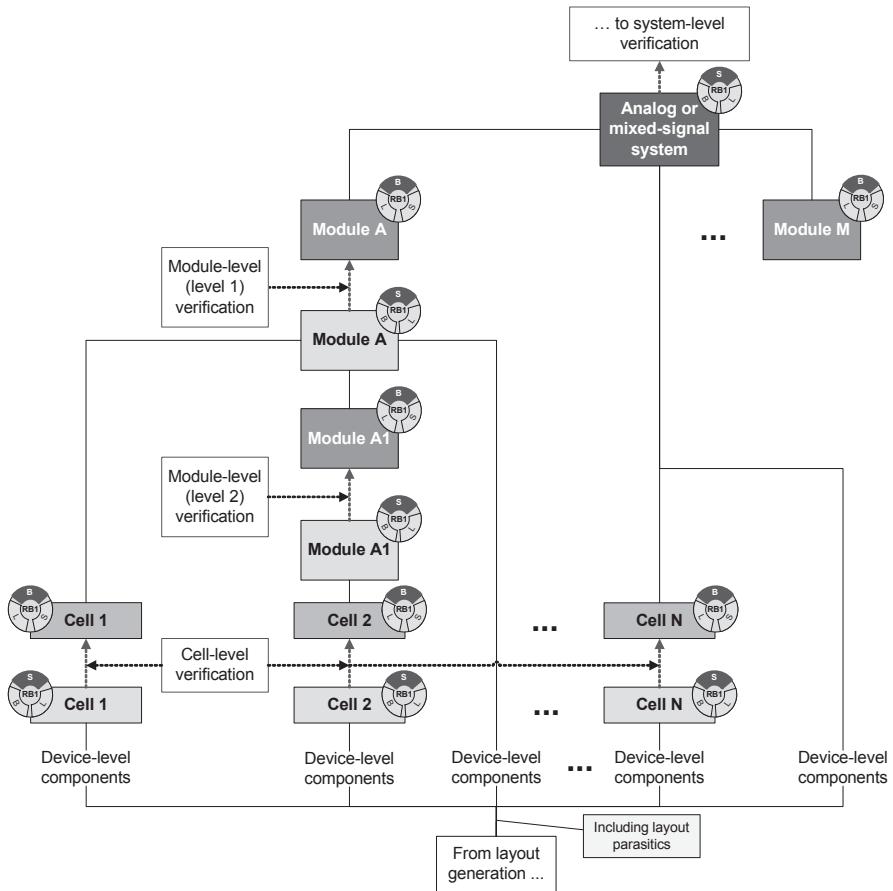

As said earlier, hierarchy is used when the circuit is too complex to be designed as one single block. Fig. 11 presents the structural decomposition of an AMS-SoC design, illustrating also the hierarchical levels more commonly considered in previously reported analog design methodologies [Dess01a] [Chang97] [Giel00].

Figure 11. Hierarchical structure of an AMS-SoC design.

These levels are:

- Digital and mixed-signal **sub-systems**<sup>8</sup>, placed at the top level of the hierarchy.

- **Module** level, defined as stand-alone functions with robust interface that can be clearly distinguished from its environment [Dess01a].

- **Cell** level, where blocks are basic functions (e.g., opamp, comparator, or switches) used to build the module-level blocks and are solely composed of device-level components.

- **Device** level, composed of active and passive devices, described by means of specific technological models.

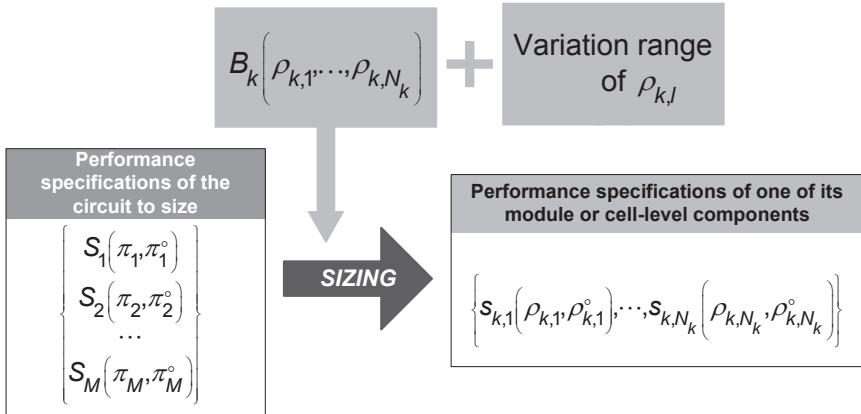

Although not explicitly indicated in Fig. 11, module-level blocks may also comprise device-level components that are not part of any cell-level block (e.g., the RC components of a biquad filter –the module-level block– whose active components are opamps –the cell-level blocks–). What differentiates cell from module-level blocks is that all components of a cell-level block are devices (e.g., transistors, resistors, capacitors, and so on) whereas a module-level block can be composed of cell-level blocks as well as of individual devices. In the same way, a system or sub-system level may comprise instances of each of the lower hierarchical levels (i.e., module-level blocks and separate cell and device-level components). For the sake of generality, we will additionally suppose that the hierarchy between the system (or sub-system) and the cell levels can be further divided into one or more module levels. That is, whereas there is only one system (or sub-system) level –to define the highest hierarchical level and whose performance requirements we will consider as externally set–, only one cell level, and only one device level –from which the physical implementation can be realized–, each module may include other modules as well as other cell and device building blocks.

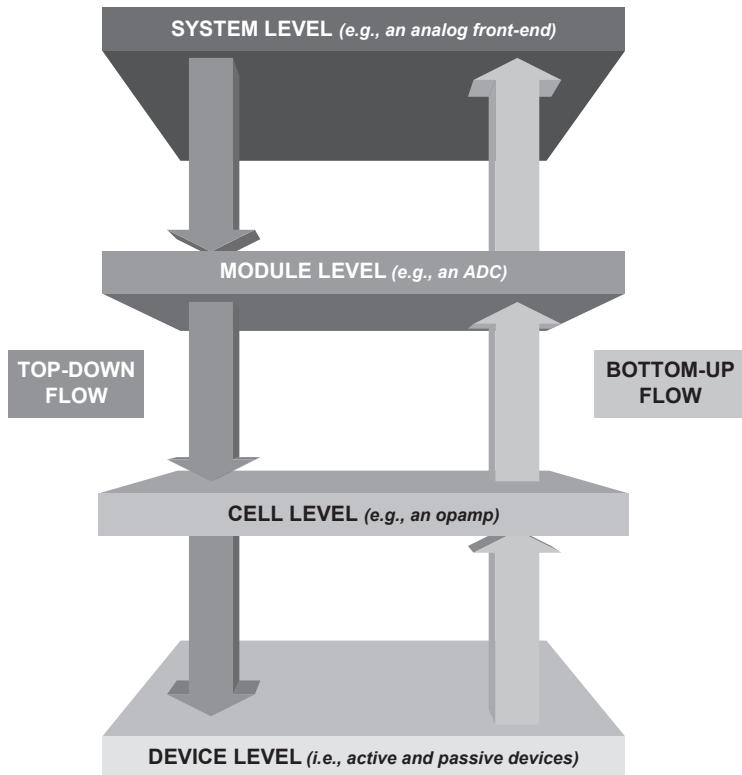

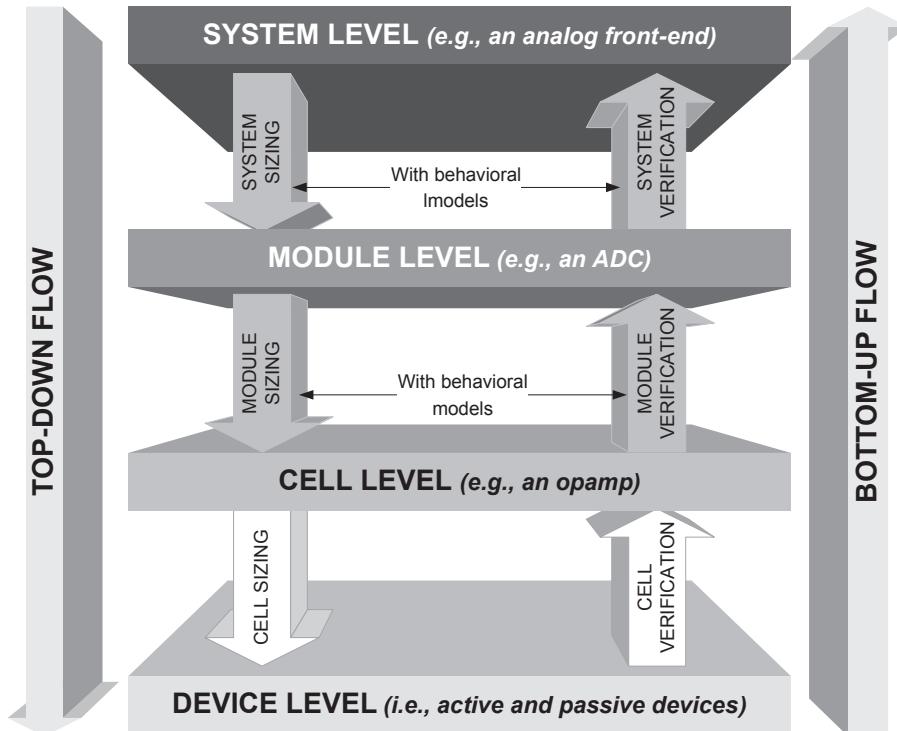

Many analog design methodologies exist, but despite different on the surface, most current design paradigms for analog circuits are similar. The first issue to consider is that of **top-down** versus **bottom-up** design. In the former, a circuit is designed with successively more detail; in the latter, a circuit is viewed with successively less detail. Fig. 12 illustrates the top-down and bottom-up concepts. Top-down design starts with the decomposition of the system specifications into a sub-set of specifications for each system's building block, which is known as *translation* or *mapping* of specifications. In doing so, the interactions between the blocks are approximated to allow a certain

---

<sup>8</sup>. Hereinafter, the word *sub-system* is to be replaced by *system* provided that the analog or mixed-signal circuit is the top-most hierarchical level (i.e., there is no digital section).

Figure 12. Top-down vs. bottom-up design processes.

independence of the design [Chang97]. The top-down process ends at the bottom level, where active and passive devices (transistors, resistors, and capacitors) compose the lower level of abstraction of the blocks. The reverse style, the bottom-up design process, begins by designing the individual cell-level blocks and ends with the assembly of the system-level circuit.

The main advantage of the top-down design flow described above is that system performance is verified early in the process, attaining thus a higher chance of first-time success, while obtaining a better overall system design. On the other hand, if some circuit specifications cannot be met at any hierarchical level, the designer has to go back and change the system architecture, which can be a costly operation at that point. Clear disadvantages of bottom-up approaches are that the architecture cannot be optimized for best system performance and that system performance cannot be verified until all the blocks have been designed, which can lead to major design changes late in the design process.

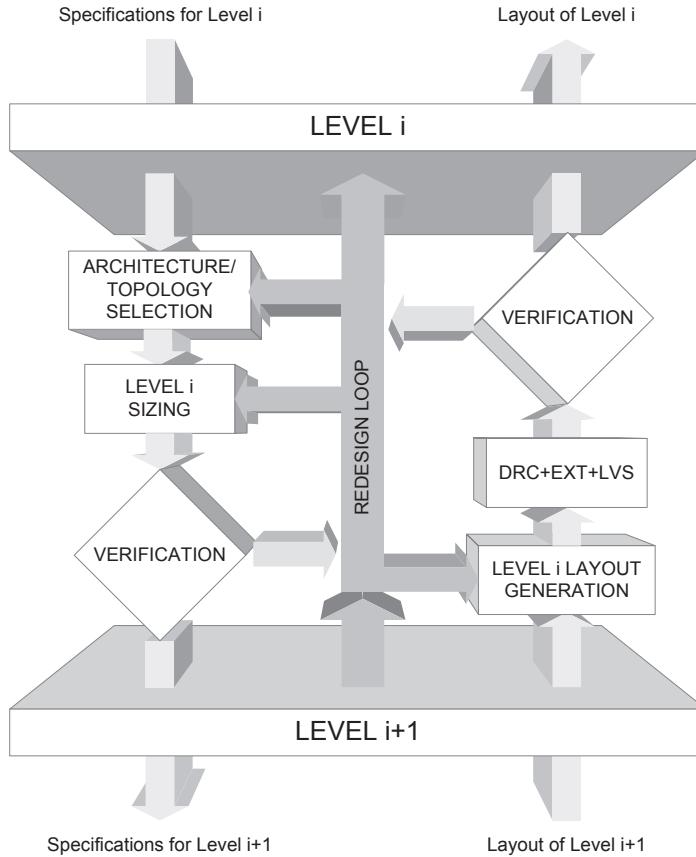

Thereby, a hierarchical design flow combining the top-down and bottom-up paths, together with redesign or backtracking iteration loops is preferred [Chang97] [Giel00]. As illustrated in Fig. 13, in between any two hierarchical levels  $i$  and  $i + 1$ , this design methodology consists of a sequence of steps.

Figure 13. Hierarchical top-down bottom-up design flow.

These steps are:

a. Top-down electrical synthesis:

- **Architecture/topology selection**<sup>9</sup>: starting with the performance specifications from the immediately higher level, the user selects the most promising architecture/topology that can address these specifications.

<sup>9</sup>. *Architecture* is hereinafter referred as the internal structure and connectivity of module, sub-system, and system-level circuits; the term *topology* is related to the cell-level circuits.

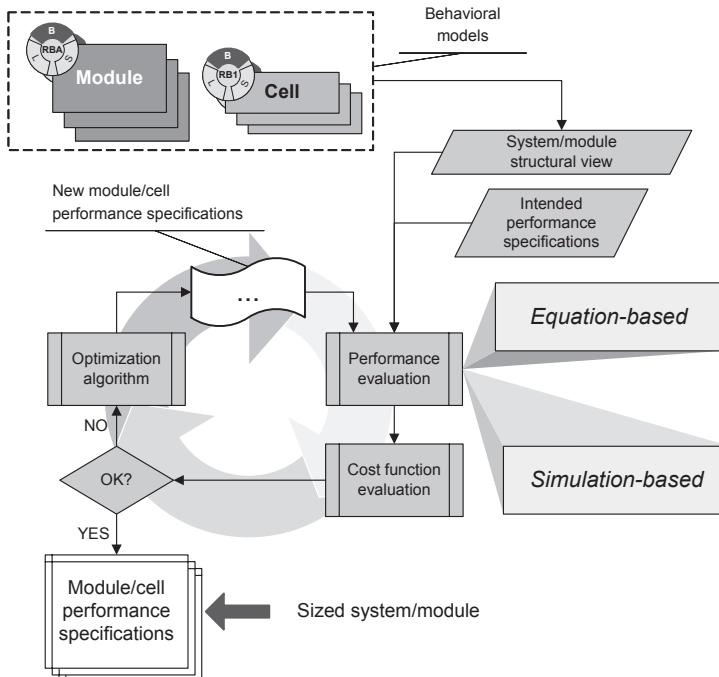

- **Sizing:** the architecture/topology is optimally sized such that the circuit meets the required specifications. This means that either the specifications from level  $i-1$  are mapped into specifications for the building blocks of the architecture (e.g., opamps of a filter architecture), or the circuit dimensioning is carried out if the topology is defined in terms of primitive components (transistors, resistors, capacitors) at the lowest level of the hierarchy.

- **Verification:** the resulting design is simulated and verified against initial specifications. If these are not met, any of the previous design steps (architecture/topology selection or sizing), even at previous hierarchical levels, have to be repeated/redesigned (this process is also known as *backtracking*). If the verification step assesses correct performance, the design process progresses down to each one of the building blocks of the architecture/topology at the following lower hierarchy level, or, if already at the lowest level of the hierarchy, the bottom-up physical synthesis takes place.

**b.** Bottom-up physical synthesis:

- **Layout generation:** the optimal layout of the block, taking into account analog specific constraints, is generated.

- **Layout verification:** the layout is first checked for violations of the process-specific design rules (an operation known as design rule checking, or DRC), then it is *extracted* (labeled 'EXT' in Fig. 13) to find out which has been the actually implemented circuit schematic (the laid out devices are extracted, from there the operation name). This schematic is then compared to the intended circuit schematic (an operation known as layout versus schematic, or LVS). Extraction is also used to obtain the layout-induced effects in terms of added devices –typically capacitances and resistances–, known as layout *parasitics*<sup>10</sup>. The whole process (i.e., DRC+EXT+LVS) is known as *formal verification* in contrast to the subsequent performance verification.

- **Performance verification:** the extracted layout (i.e., the circuit schematic plus the layout parasitics) is then simulated and, as in the top-down verification phase, if unacceptable

---

<sup>10</sup>. In general, a layout *parasitic* can be defined as every cause of performance degradation which is not intended by the circuit designer and whose value is determined by the circuit layout [Lamp99].

deviations from the required performance are uncovered, the design process is repeated.

The illustration of the hierarchical design methodology for analog and mixed-signal circuits, with the levels of abstraction explained above is given in Fig. 14. It is worth noting that every step of the hierarchical top-down bottom-up synthesis methodology (architecture/topology selection, sizing or specification translation, layout generation, simulation, and verification) can be, in principle, automated with CAD approaches. Such an automation can range from merely relieving the designer from long, repetitive tasks to performing the complete design flow with minimal designer intervention.

Although hierarchical design represents a substantial improvement of the time-to-market figure and the ability to handle complexity when compared with plain bottom-up or top-down approaches, there still are some points where this methodology needs improvement in order for it to cope entirely with those two design challenges. In this sense, a number of goals have been defined in the 2001 ITRS report [Ittrs01]. Among them, the work presented in this book aims at the following:

- 1. Avoid iterations.** Iterations between layout generation and sizing –a direct consequence of the complete separation of the bottom-up layout generation and the top-down electrical synthesis–, incur repeating the related synthesis processes and other interfacing costs, which altogether may eventually lead into product-to-market failure. Therefore, these spins should be reduced as much as possible.

- 2. Improve synthesis.** AMS circuit design typically requires very specific expert knowledge that should be incorporated into the various automated synthesis processes in order to enhance their efficiency.

- 3. Reuse.** To extend the notion of library-based approaches, and thereby reduce overall design time, reuse of captured designers' expertise should be also a major concern. Therefore, methods for reusing stored expertise must be defined and developed that improve the hierarchical methodology for AMS circuits.

The problem, and, hence, the goal of the research here reported, consists in the improvement of the analog and mixed-signal design process by means of the definition, development, and demonstration of appropriate CAD methodologies and tools, which, attending to the issues mentioned above, help to reduce the design cost and, hereby, to bridge the design gap described in Section 1.2.

Figure 14. Hierarchical design flow for the hierarchy in Fig. 11.

### **3 SUMMARY**

In the first part of this chapter, the motivations driving the research reported in this book have been introduced. The ever-widening gap between the silicon transistor capacity and the available design rate is posing a major, serious challenge in the semiconductor industry. Although the design capacity has been moderately improving thanks to design methodologies and computer-aided design tools so far, the situation is becoming critical as time-to-market pressures tighten and design complexity increases. If this scenario is worrying enough in the digital arena, where design methodologies and tools are relatively well-advanced, it turns alarming with regard to analog or mixed-signal circuits. It is concluded that further development of the design methodologies and design tools, and even the working out of new design paradigms in the area of analog and mixed-signal integrated circuits are, altogether, urgently required.

In the second part of the chapter, the problem is carefully analyzed. Concepts involved such as abstraction, hierarchy, and views have been revisited in the context of the analog and mixed-signal design flow. This flow has also been examined in detail in order to find out where it fails to cope with present design requirements.

In the following chapter, several approaches attempting to bridge the design gap are revised.

## Chapter 2

# A Reuse-based Design Framework for Analog ICs

The preceding chapter introduced the motivation for further improvement in modern analog and AMS circuit design methodologies. A first important effort towards such enhancement is automating the several steps involved in the AMS synthesis problem, especially the sizing and layout generation design steps. Commonly known as design automation, it can be carried out by following either a knowledge-based approach or an algorithmic, optimization-based approach. Both have their advantages and limitations. Increasing the efficiency of synthesis, however, can be achieved if a way to capture and at a later time use the reliable design knowledge that analog and mixed-signal designers insist on is devised. Circuit reuse, a new paradigm, is seen as a promising solution that, combined with the appropriate synthesis tools, can bridge the increasing design gap between what we can fabricate and what we can design and that calls for advances in AMS design methodologies.

This chapter presents a novel reuse-based design framework for AMS ICs. The cornerstone of such framework is the analog and mixed-signal reusable block and a clear, structured definition of this type of blocks is thus provided here. Furthermore, the development of these special blocks is supported with a systematic methodology for reusability. Last but not least, this reuse-based framework comprises a design reuse flow, by which reusable blocks are incorporated into the hierarchical top-down bottom-up flow introduced in the previous chapter.

## 1 DESIGN AUTOMATION

An important conclusion of the previous chapter was that there are still some aspects where the hierarchical methodology can be improved in order to bridge the existing design gap and, in doing so, efficiently cope with more and more stringent time-to-market pressures and increased analog design complexity.

The work presented in this book, aiming at three of these aspects (i.e., avoid iterations, improve synthesis, and exploit reuse) starts off by analyzing the existing synthesis approaches for AMS designs. A thorough understanding of their advantages and limitations is essential to find out why synthesis alone does not suffice to bridge the design gap, and how new design paradigms can help closing the gap.

## 1.1 Preliminary definitions

As explained in Chapter 1, a typical design flow for AMS circuits is composed of a number of design steps repeated top-down, from the system hierarchical level to the device level, and bottom-up for composition and verification. The steps between any two of these hierarchical levels are:

- architecture/topology selection,

- sizing,

- layout generation, and

- verification.

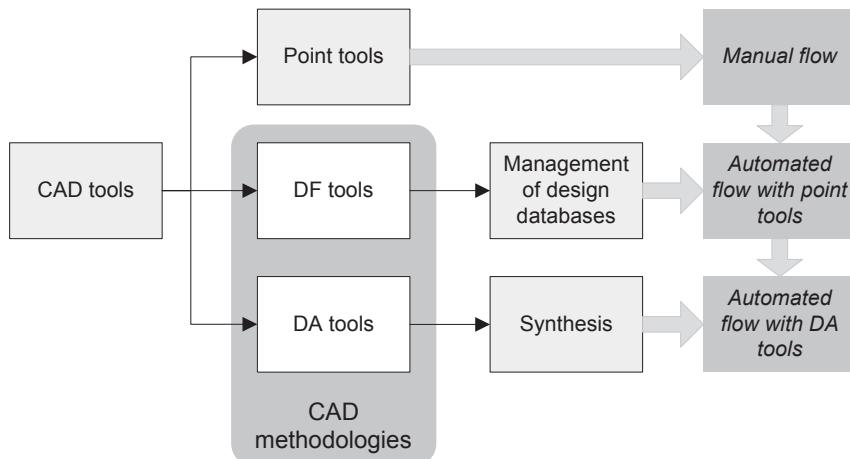

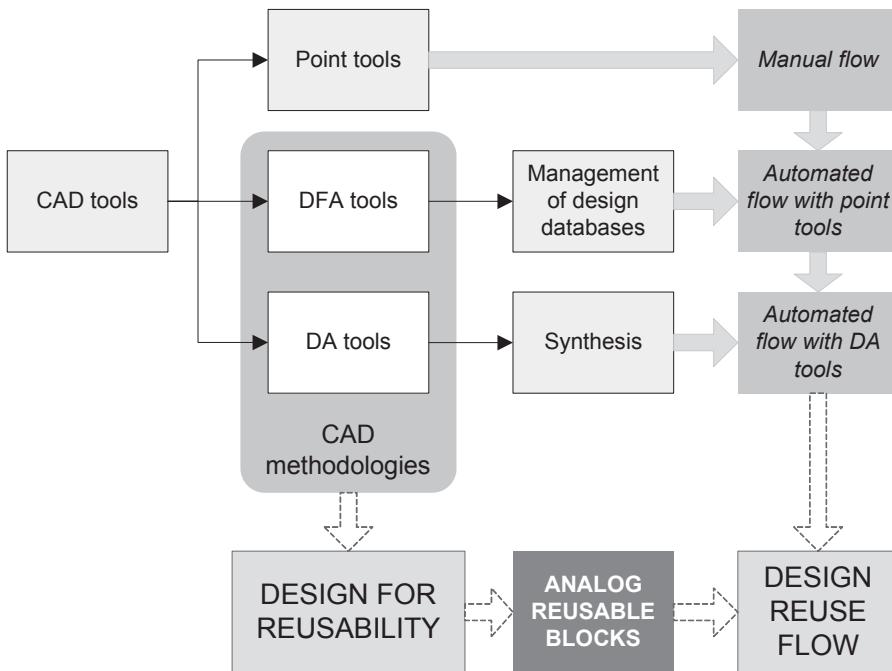

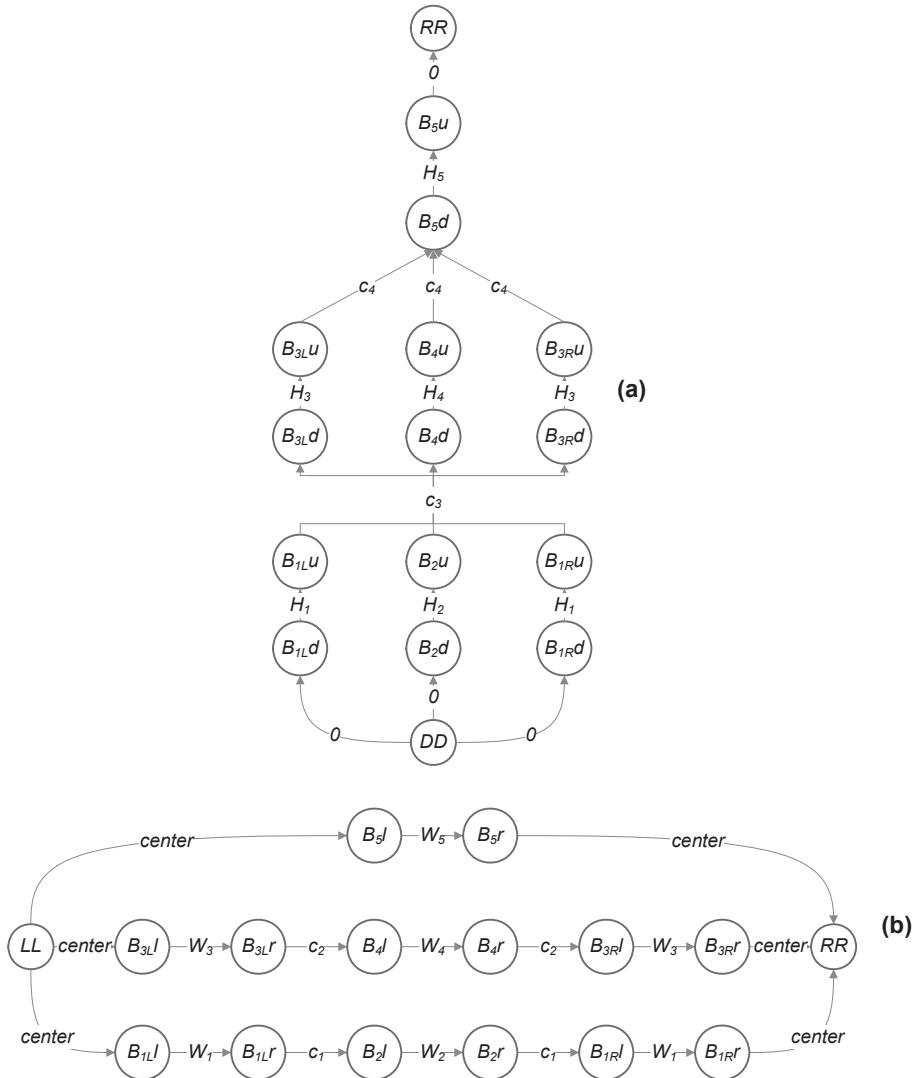

A **computer-aided design methodology** for AMS circuits aims at automating the different steps of the design methodology. Such a CAD methodology entails the integration of one or more CAD tools into a flow providing a specific level of automation. Here, automation refers to the ratio of the time it takes to manually complete the entire design for the first time, to the time it takes with the CAD methodology [Ocho98]. The CAD tools that can be used in any CAD methodology are explained below<sup>1</sup> (see Fig. 1):

- **Point** tools, to help the designer in a single particular task, relieving him from tedious, error-prone jobs. Examples are simulators (e.g., HSPICE® [Hspi04]), layout tools (e.g., Cadence® Virtuoso® [Virt00a]), and verification tools (e.g., Cadence® Diva® [Diva05]).

- **Design flow** (DF) tools, to manage the design database and the transformations the database undergoes from concept to *tapeout*. The scope is not restricted to a single design step, or between two point tools, but it may rather spread over the whole design flow as well.

- **Design automation** (DA) tools, supporting the automation of a particular design step, such as a decision-making algorithm for circuit sizing. These tools are also known as synthesis tools, and can be used for (system, module, or cell) sizing and layout generation.

---

<sup>1</sup>. The definitions given here have been adapted from the ones found in [Daems02].

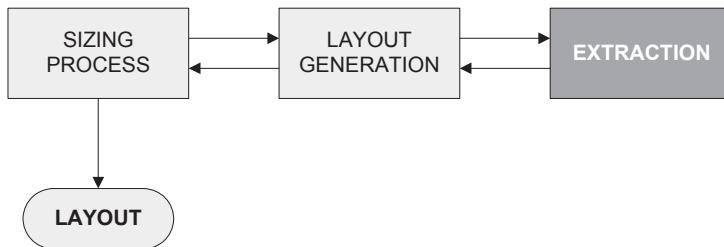

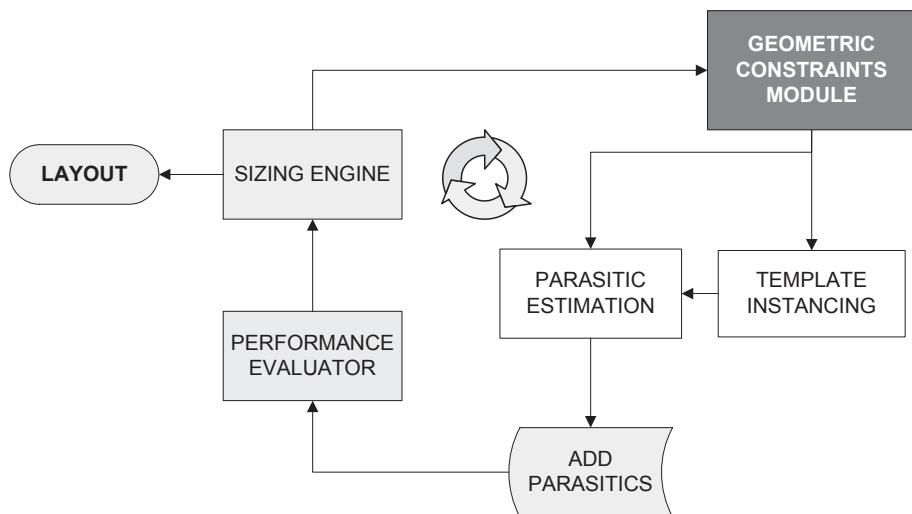

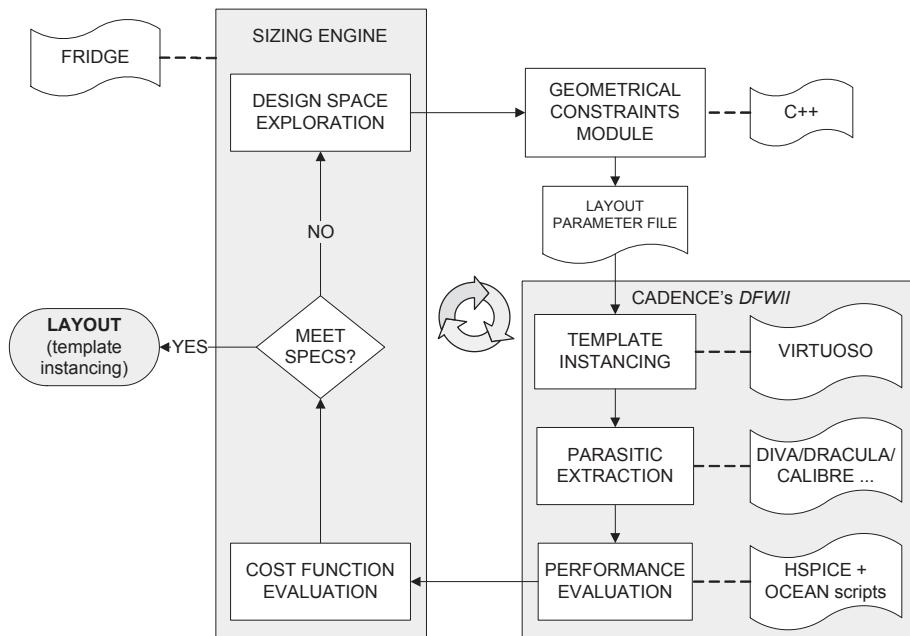

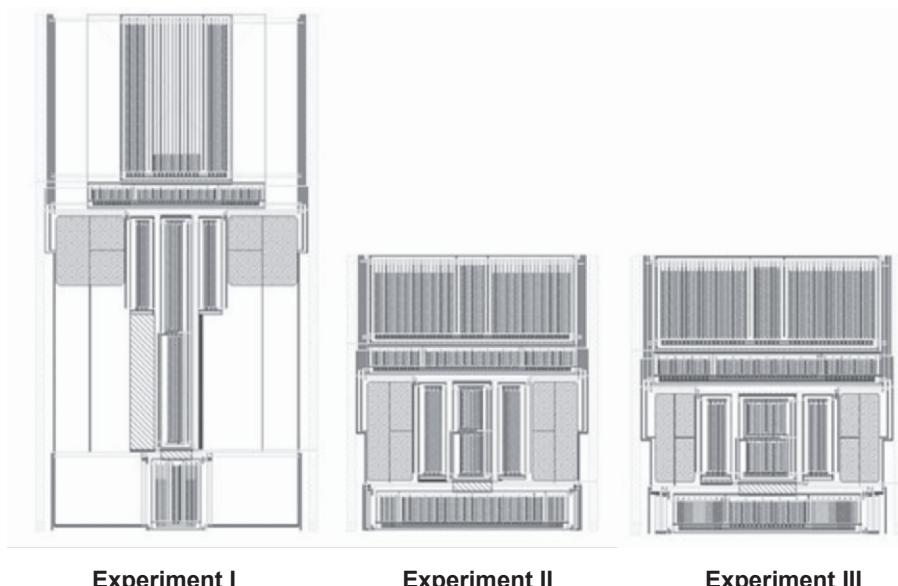

Figure 1. Design automation concepts.

A CAD methodology aims at automating either the design flow or a design step by means of DF tools and DA tools, respectively. A flow solely supported by point tools is called **manual design flow**, as the only existing degree of automation is that of the separate point tools used. When DF tools manage the input and output data of the point tools, the flow is known as an **automated design flow with point tools**. Examples of these flows are electronic database management systems such as Cadence® *Design Framework II* ([www.cadence.com](http://www.cadence.com)) and the *Falcon Framework®* from Mentor Graphics® ([www.mentor.com](http://www.mentor.com)). Last, when DA tools are incorporated, the resulting flow, denoted here as **automated design flow with DA tools**, achieves a higher degree of automation, enabling the designer to focus on other key tasks, such as the working out of new, better AMS architectures and topologies.

For the remainder of this book, the term *automation* is used to mean design automation, i.e., automation achieved by means of synthesis tools.

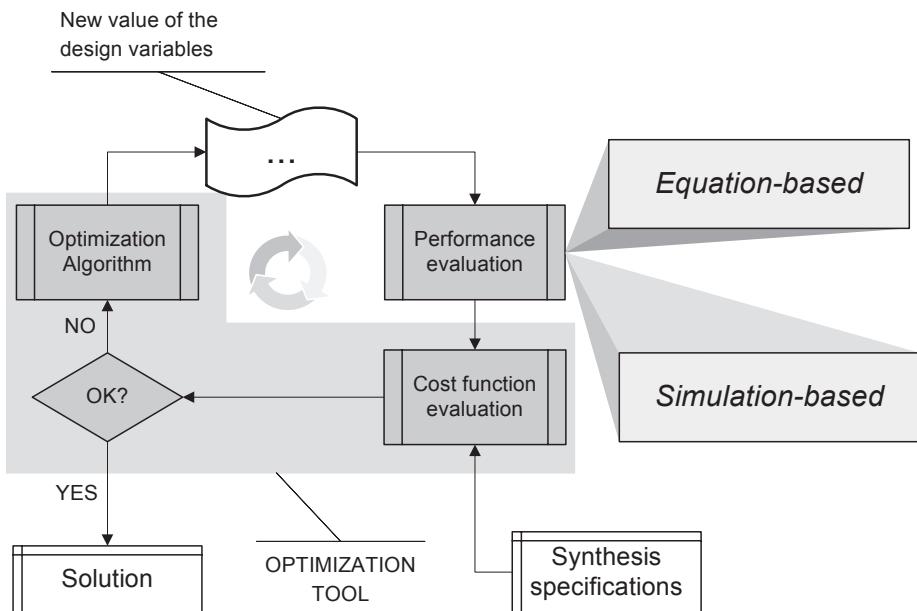

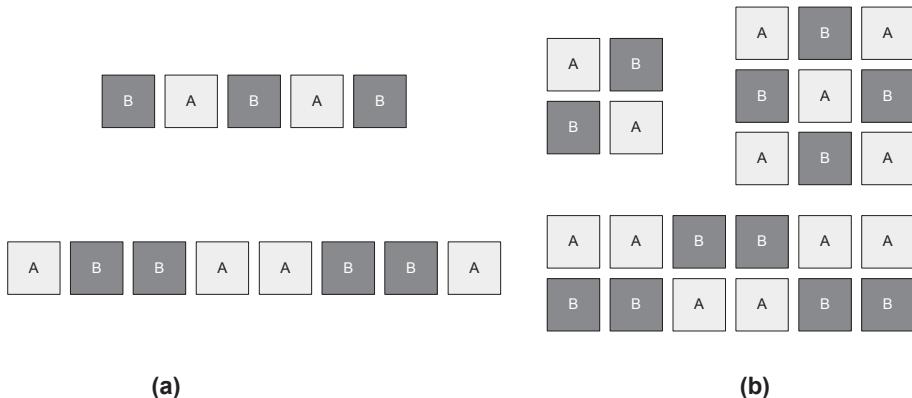

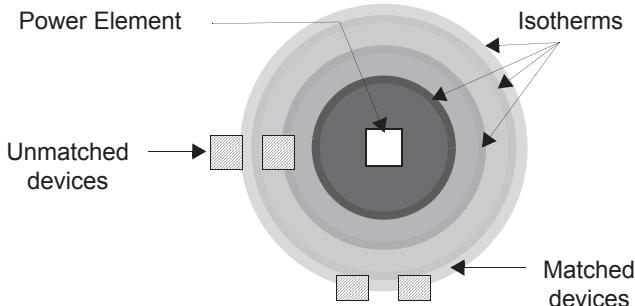

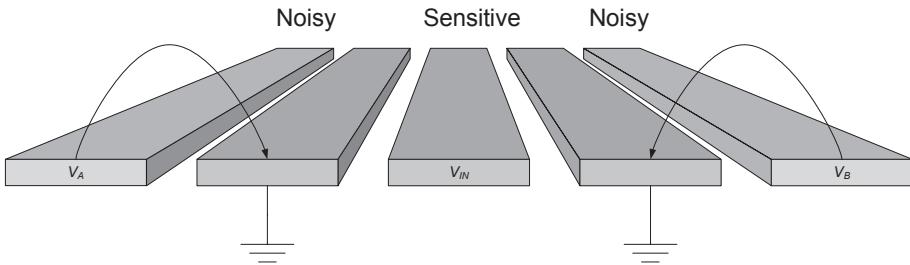

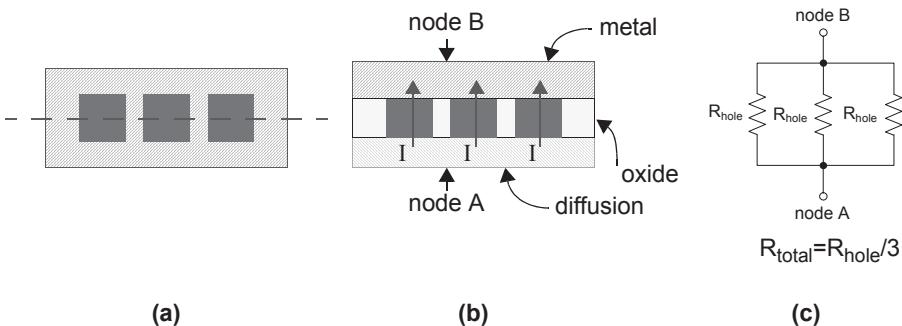

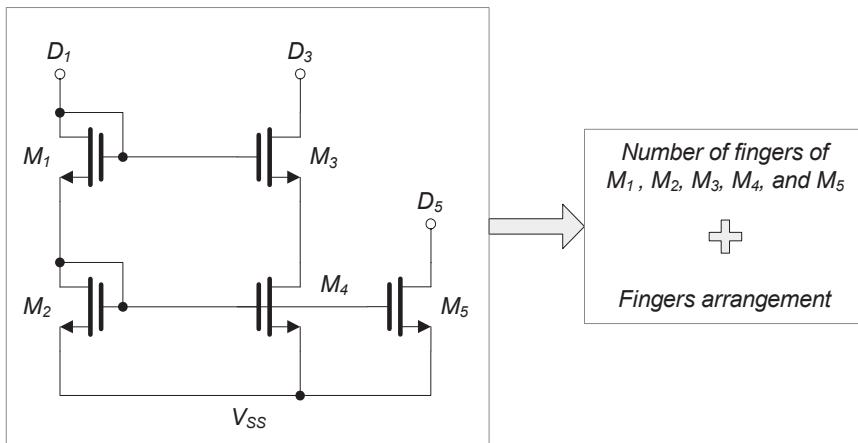

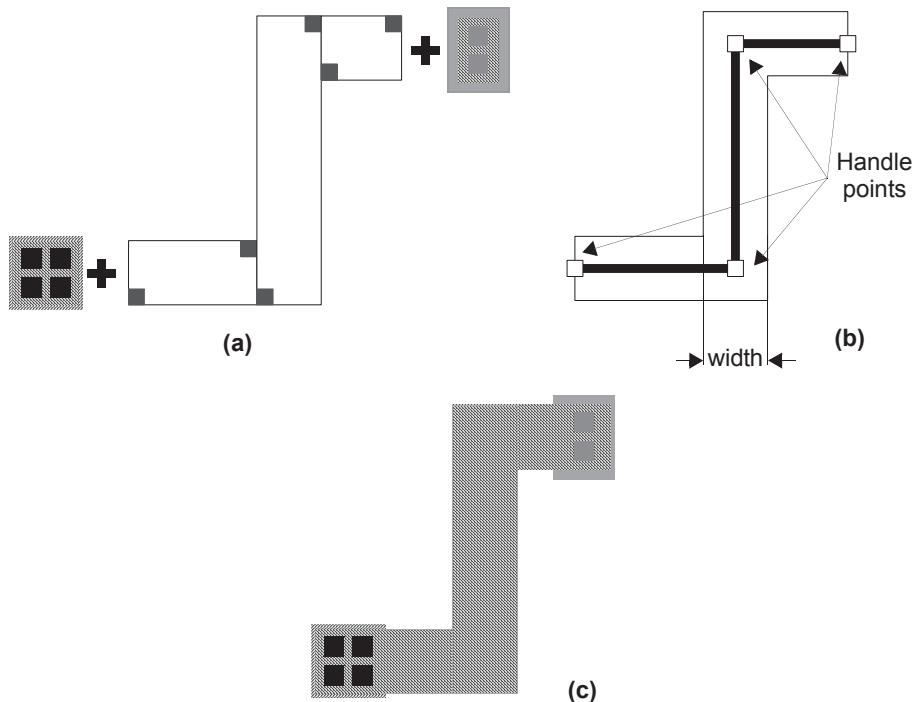

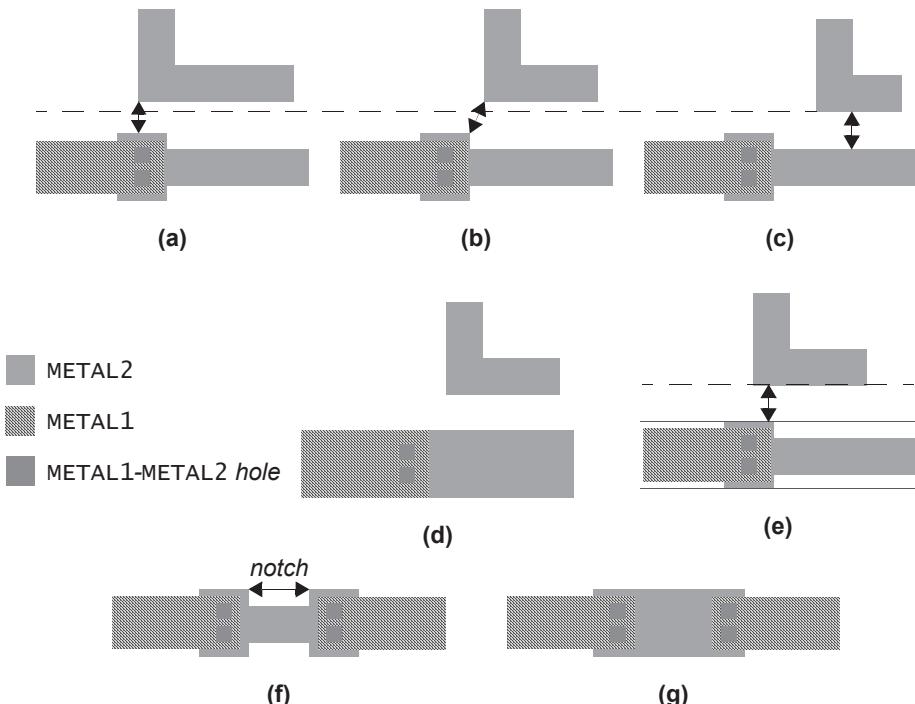

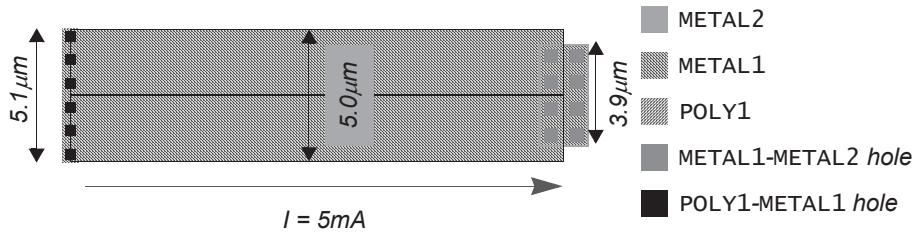

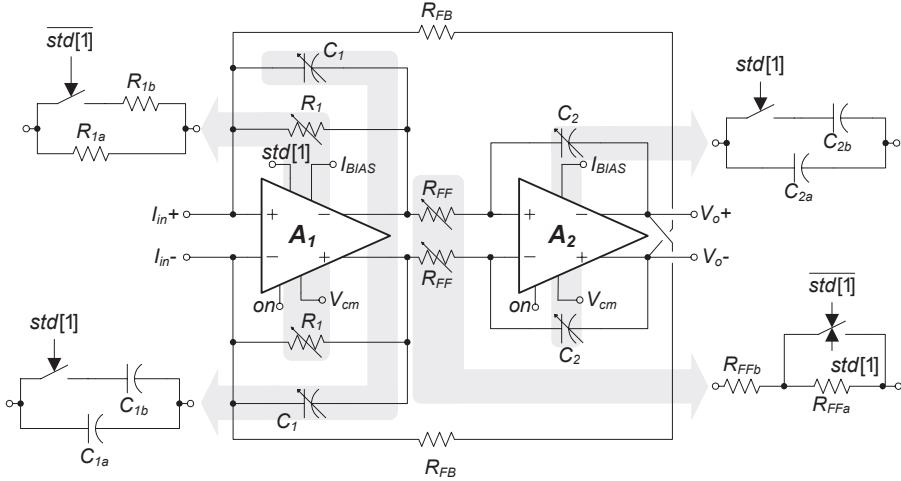

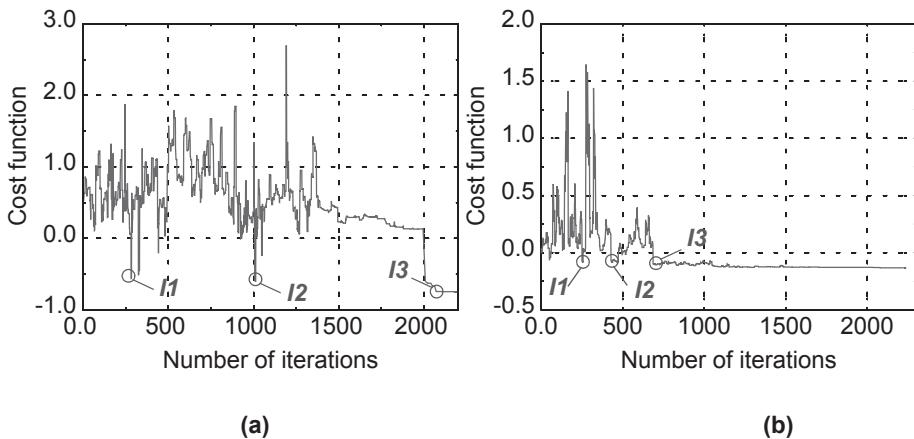

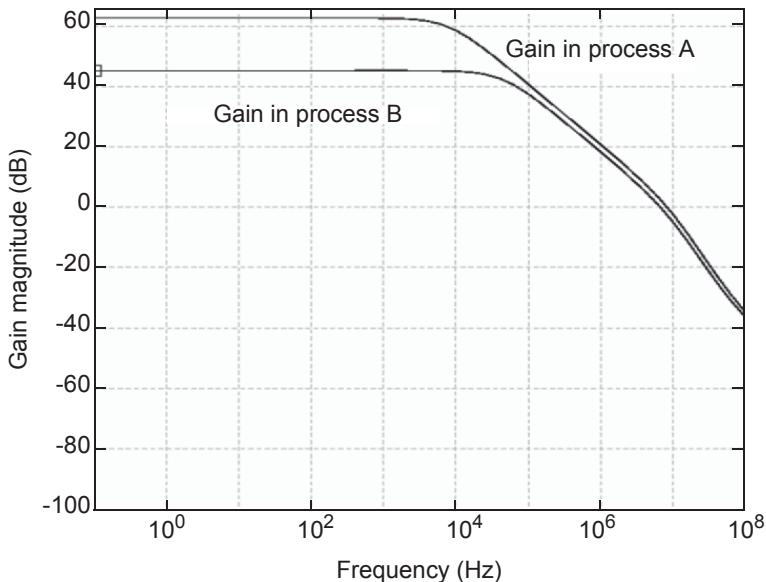

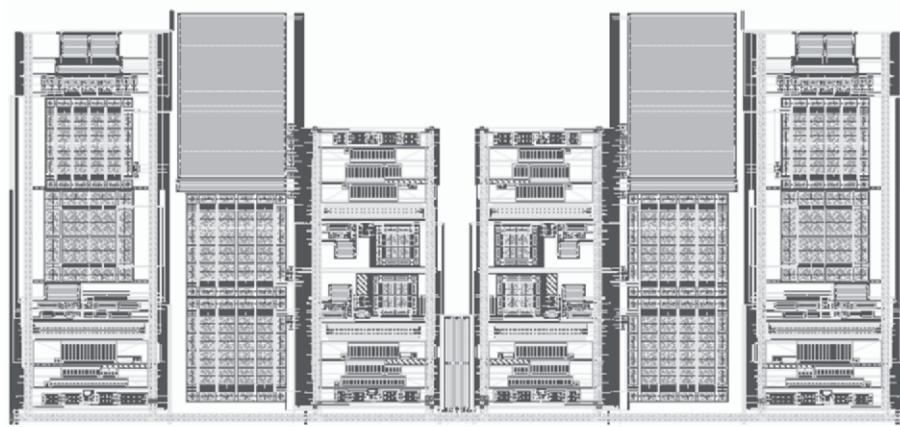

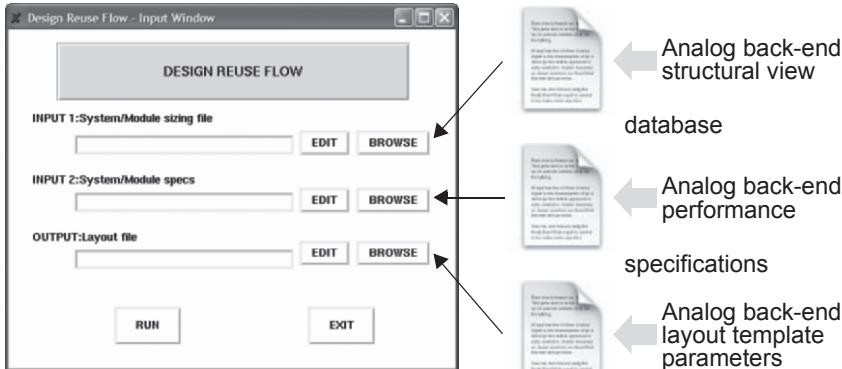

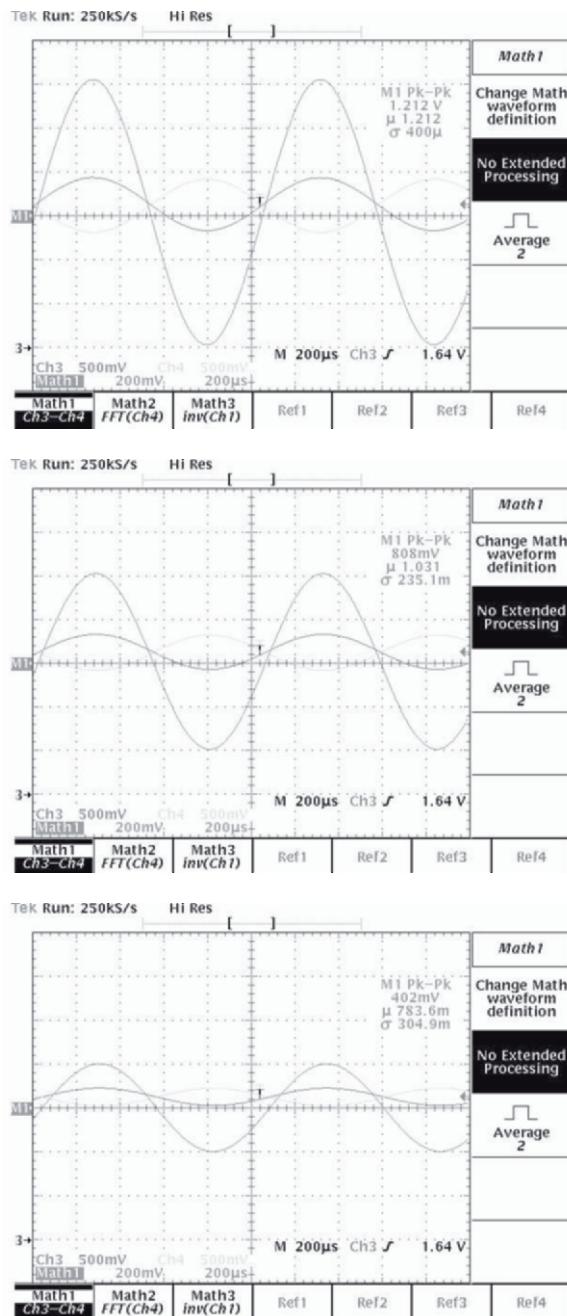

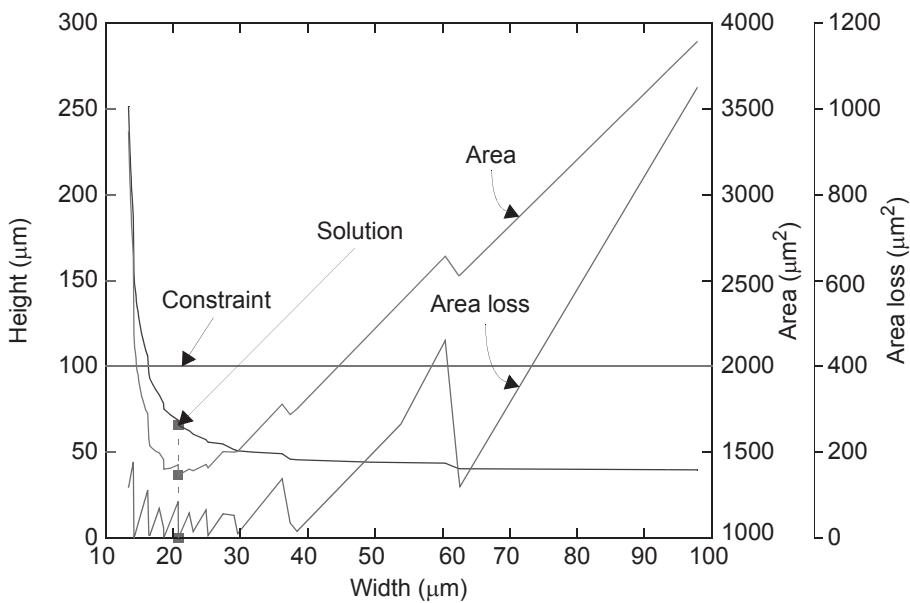

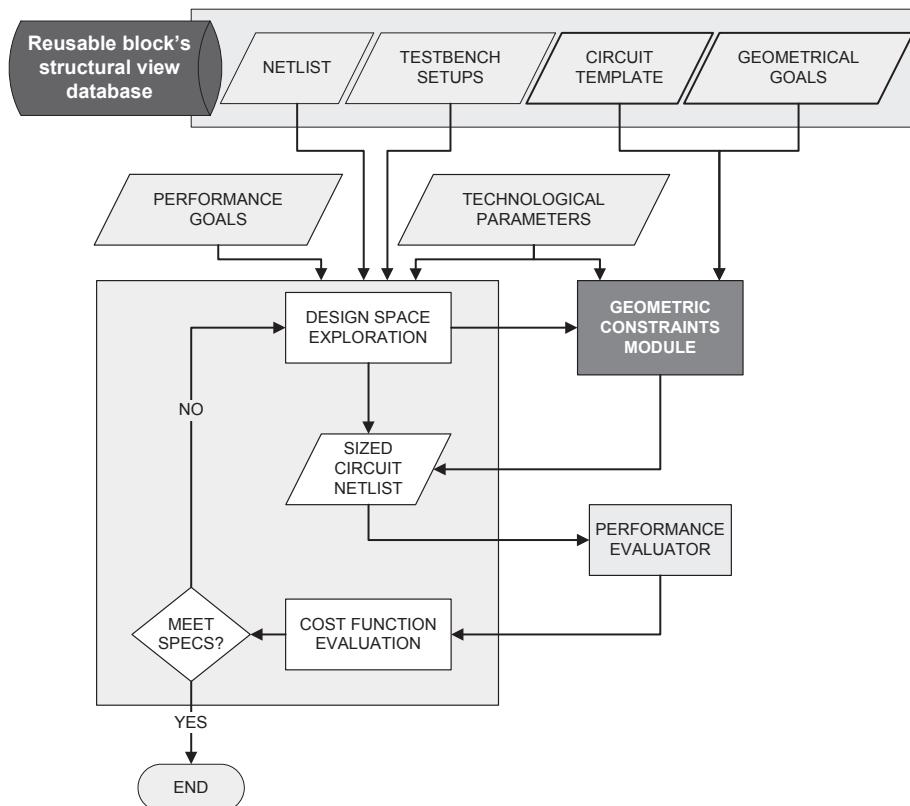

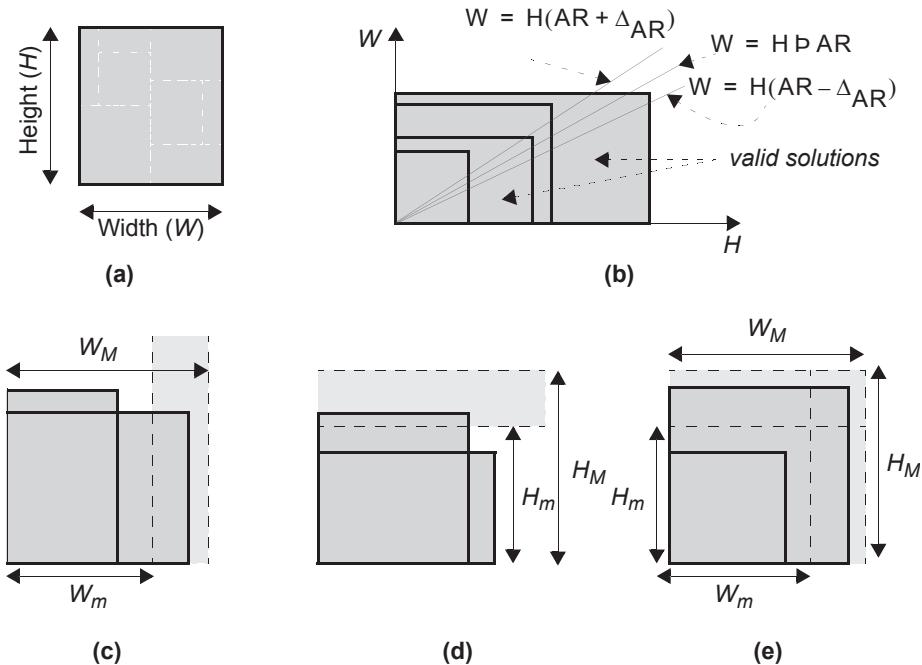

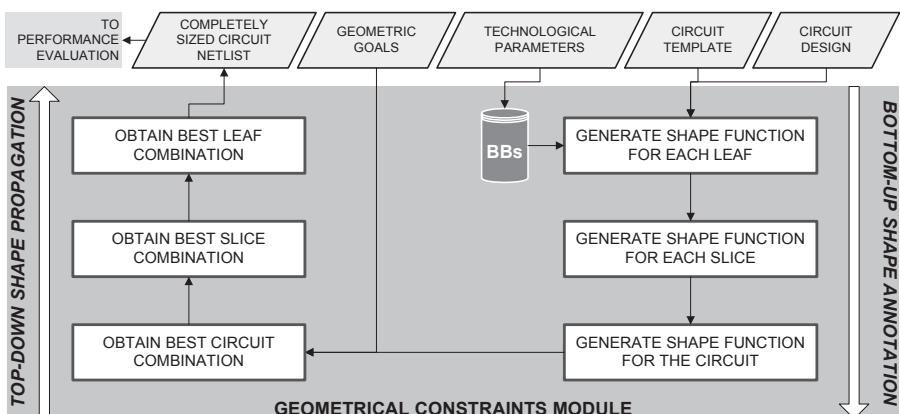

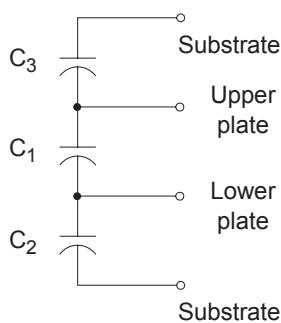

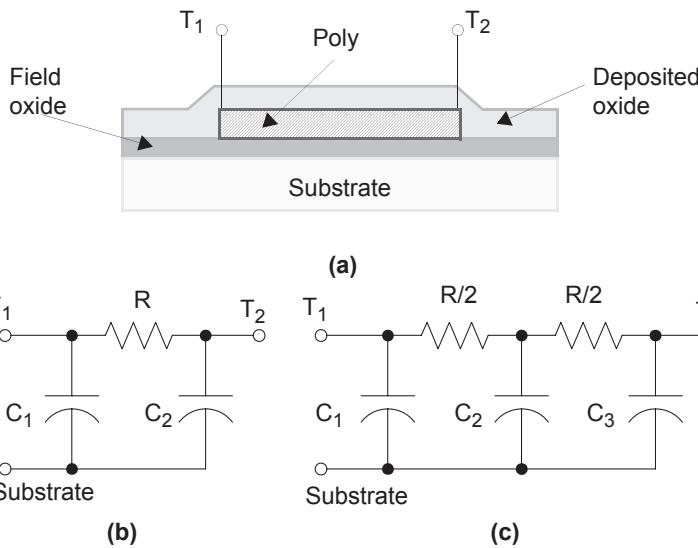

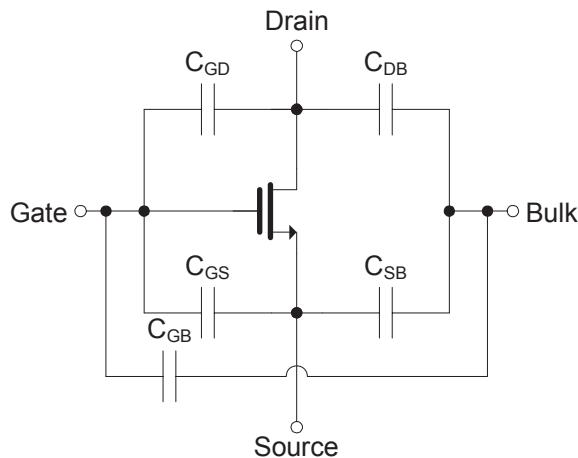

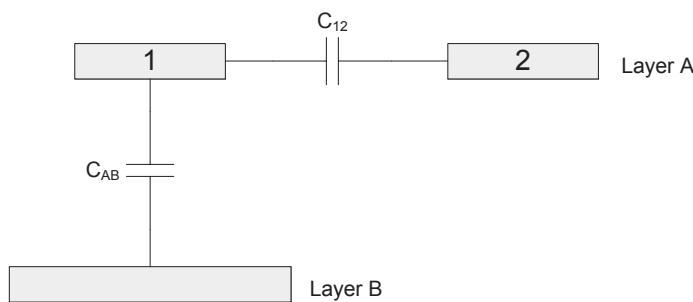

## 1.2 The two sides of automation