CLOSING THE POWER GAP BETWEEN

**ASIC & Custom**

Tools and Techniques

for Low Power Design

**David Chinnery**

**Kurt Keutzer**

# **Closing the Power Gap Between ASIC & Custom Tools and Techniques for Low Power Design**

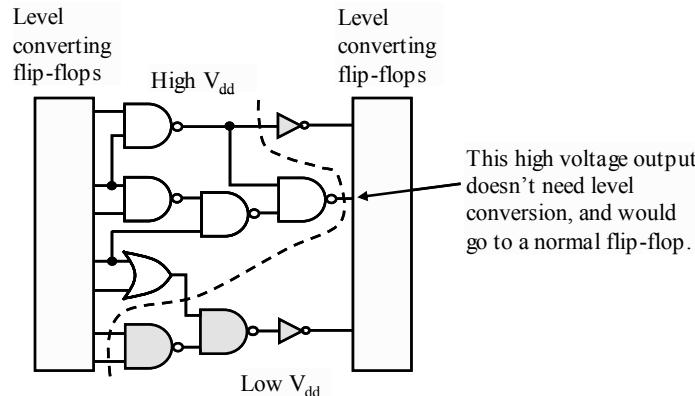

David Chinnery • Kurt Keutzer

# Closing the Power Gap Between ASIC & Custom

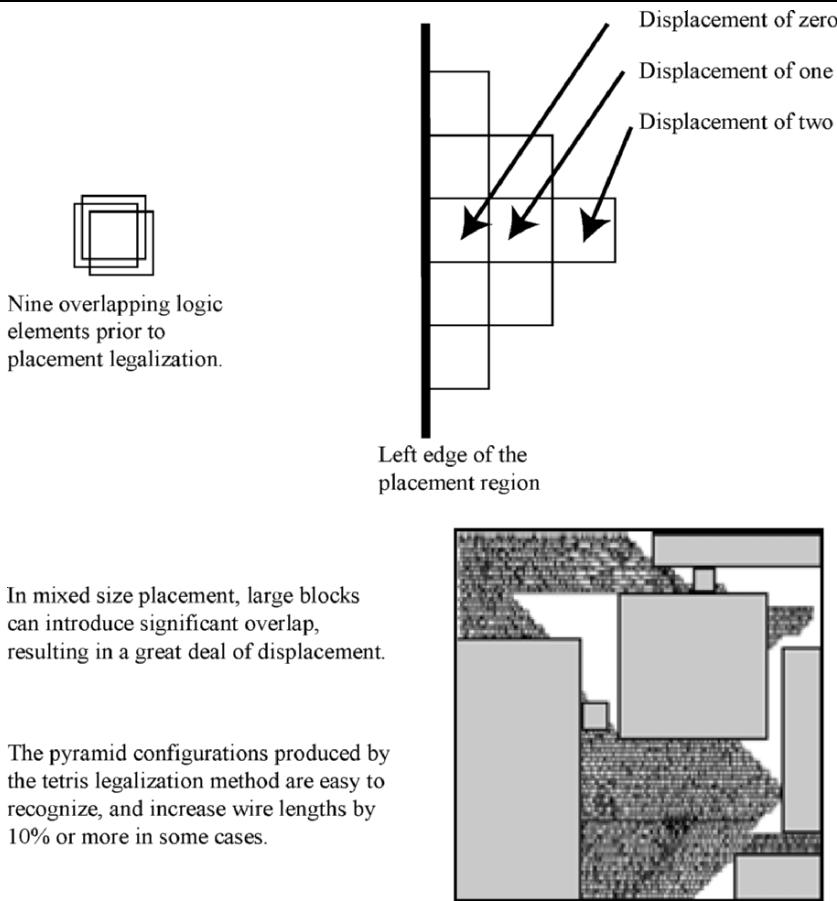

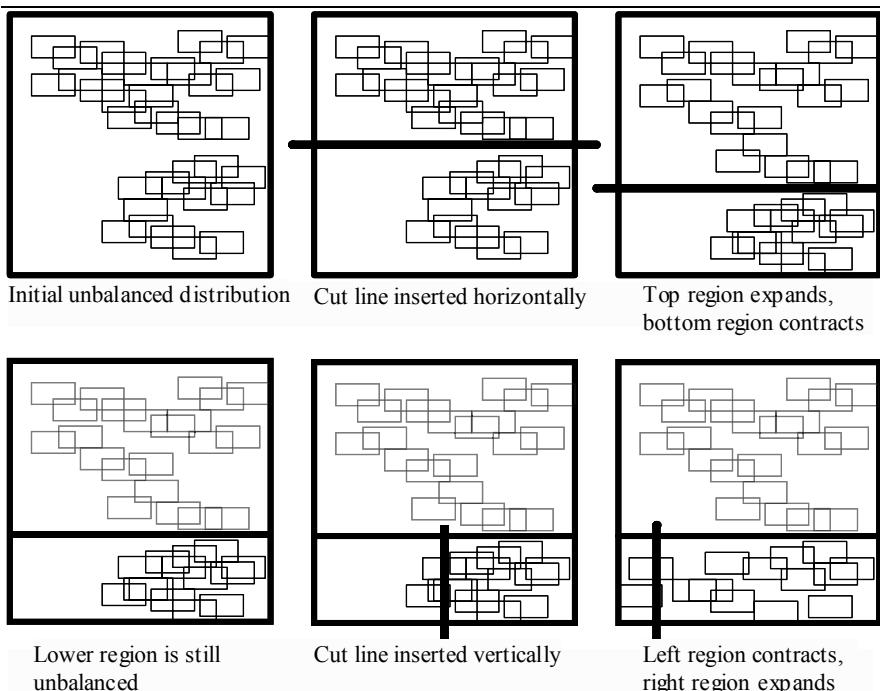

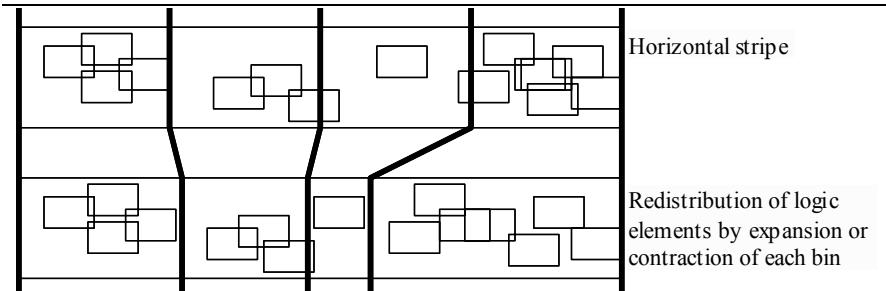

## Tools and Techniques for Low Power Design

Springer

David Chinnery

AMD

Sunnyvale, CA

USA

Kurt Keutzer

University of California, Berkeley

Berkeley, CA

USA

Library of Congress Control Number: 2007929117

ISBN 978-0-387-25763-1      e-ISBN 978-0-387-68953-1

Printed on acid-free paper.

© 2007 Springer Science+Business Media, LLC

All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden. The use in this publication of trade names, trademarks, service marks and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

9 8 7 6 5 4 3 2 1

[springer.com](http://springer.com)

# PREFACE

We were very pleased with the warm reception that industry analysts, the trade press, and most importantly, hard working circuit designers, gave to our book entitled *Closing the Gap Between ASIC and Custom* that was first published in 2002. In that book, we focused on identifying the factors that cause a significant speed differential between circuits designed in an ASIC methodology and those designed with a “no holds barred” custom approach. We also sought to identify and describe design tools and techniques that could close the gap between the speeds of ASIC and custom circuits. That book wasn’t even in press before designers and fellow researchers came forward to challenge us to investigate a gap of growing importance: the gap in power dissipation and energy efficiency between circuits designed in ASIC and custom methodologies.

We learned a lot from our first book. In the content of our work we learned that circuit design and layout tricks were unlikely to be the source of sustained advantages of custom design. Instead clocking methodologies and microarchitecture were more likely to be areas where custom circuits sustained their advantage over ASICs. In our presentation of our research we found that technical conferences such as the Design Automation Conference were good venues for trying out our material and getting valuable feedback. Finally, in the production of the book itself we learned that putting high-level surveys and detailed descriptions of current research together with illustrative design examples was a good formula for creating a book of broad interest.

Like its predecessor we envision three main audiences for this book. The first audience is ASIC and ASSP designers who are restricted to a high productivity ASIC design methodology but still need to produce low-power circuits with high-energy efficiency. The second audience is custom designers who are seeking to design low power circuits with a more productive design flow. While the perspective of these two groups is different, the solutions they are seeking are very similar. In this book we account for the relative power impact of different elements of a custom-design methodology. We believe that this analysis should help custom design groups to determine where their limited design resources are best spent and help ASIC-oriented design groups understand where they most need improvement. Secondly, we identify specific tools and methodologies targeted to reduce the power of ASICs that are consistent with an ASIC design methodology, but which can also be usefully employed in custom circuit design.

The third audience for this book is researchers in electronic design automation who are looking for a broader survey of contemporary low-power

tools, methodologies, and design techniques. We hope that this book offers a more complete presentation of the battery of techniques that can be brought to bear to save power than is typically offered in conference publications or even survey articles. We also hope that the design examples used in this book will help researchers to contextualize their own research.

Occasionally at technical conferences you will hear someone say: “Another power paper? Isn’t that a solved problem?” Low power design has indeed been a focal research area for fifteen years. However, a look at the power challenges of today’s industrial designs indicates that the topic of this book has never been timelier.

*David Chinnery

Kurt Keutzer*

## ACKNOWLEDGMENTS

Many people have given us advice, feedback and support over the years. We will endeavor to acknowledge the majority of those people here, but there are also numerous others with whom we have discussed research and who have made helpful suggestions.

The Semiconductor Research Corporation supported our research on low power. Our thanks to STMicroelectronics for access to their 0.13um process technology and to the contacts at STMicroelectronics, Bhusan Gupta and Ernesto Perea. For the algorithmic portion of our research, we collaborated extensively with David Blaauw, Sarvesh Kulkarni, Ashish Srivastava, and Dennis Sylvester. Sarvesh Kulkarni and Ashish Srivastava provided characterized asynchronous level converters and Synopsys PowerArc characterized libraries for STMicroelectronics 0.13um process. We would like to thank the Intel industrial liaisons, in particular Vijay Pitchumani and Desmond Kirkpatrick, for their advice.

We would like to thank researchers at the Berkeley Wireless Research Center: Stephanie Augsburger, Rhett Davis, Sohrab Emami-Neyestanak, Borivoje Nikolić, Fujio Ishihara, Dejan Markovic, Brian Richards, Farhana Sheikh, and Radu Zlatanovici. Laurent El Ghaoui also helped with convex optimization research.

We would like to acknowledge the contributors to sessions on Closing the Gap between ASIC and Custom and the two books on the topic. Fruitful discussions with them have helped clarify our assumptions and delve into the details: Ameya Agnihotri, Debashis Bhattacharya, Subhrajit Bhattacharya, Vamsi Boppana, Andrew Chang, Pinhong Chen, John Cohn, Michel Cote, Michel Courtoy, Wayne Dai, William Dally, David Flynn, Jerry Frenkil, Eliot Gerstner, Ricardo Gonzalez, Razak Hossain, Lun Bin Huang, Bill Huffman, Philippe Hurat, Anand Iyer, Srikanth Jadcherla, Michael Keating, Earl Killian, George Kuo, Yuji Kukimoto, Julian Lewis, Pong-Fei Lu, Patrick Madden, Murari Mani, Borivoje Nikolić, Greg Northrop, Satoshi Ono, Michael Orshansky, Barry Pangrle, Matthew Parker, Ruchir Puri, Stephen Rich, Nick Richardson, Jagesh Sanghavi, Kaushik Sheth, Jim Schwartz, Naresh Soni, David Staepelaere, Leon Stok, Xiaoping Tang, Chin-Chi Teng, Srinivasa Venkatraman, Radu Zlatanovici, and Tommy Zoune.

We would also like to thank others within our department who have helped with low power research and editing: Abhijit Davare, Masayuki Ito, Trevor Meyerowitz, Matthew Moskewicz, David Nguyen, Kaushik Ravindran, Nadathur Satish, and Brandon Thompson.

David thanks his wife, Eleyda Negron, for her help and support. Kurt thanks Barbara Creech for her patience and support.

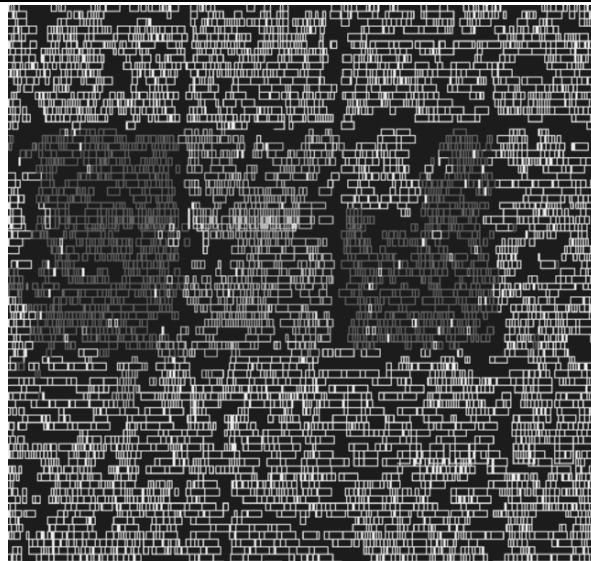

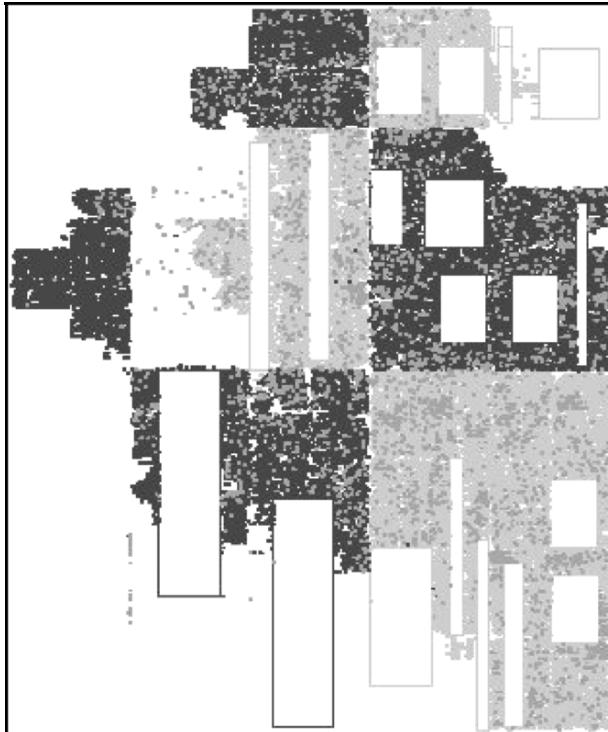

The cover was designed by Steven Chan. It shows the Soft-Output Viterbi Algorithm (SOVA) chip morphed with a custom 64-bit datapath. The SOVA chip picture is courtesy of Stephanie Ausberger, Rhett Davis, Borivoje Nikolić, Tina Smilkstein, and Engling Yeo. The SOVA chip was fabricated with STMicroelectronics. The 64-bit datapath is courtesy of Andrew Chang and William Dally. GSRC and MARCO logos were added.

# CONTENTS

|                                                                    |            |

|--------------------------------------------------------------------|------------|

| <b>Preface</b>                                                     | <b>v</b>   |

| <b>Acknowledgments</b>                                             | <b>vii</b> |

| <b>1. Introduction</b>                                             | <b>1</b>   |

| <i>David Chinnery, Kurt Keutzer</i>                                |            |

| 1.1 Definitions: ASIC and custom.....                              | 1          |

| 1.2 What is a standard cell ASIC methodology?.....                 | 3          |

| 1.3 Who should care about this book?.....                          | 6          |

| 1.4 Organization of the rest of the book .....                     | 8          |

| 1.5 What's not in this book.....                                   | 9          |

| <b>CONTRIBUTING FACTORS</b>                                        |            |

| <b>2. Overview of the Factors Affecting the Power Consumption</b>  | <b>11</b>  |

| <i>David Chinnery, Kurt Keutzer</i>                                |            |

| 2.1 Introduction.....                                              | 11         |

| 2.2 Process technology independent FO4 delay metric .....          | 12         |

| 2.3 Components of power consumption .....                          | 14         |

| 2.4 ASIC and custom power comparison .....                         | 15         |

| 2.5 Factors contributing to ASICs being higher power.....          | 19         |

| 2.6 Summary .....                                                  | 47         |

| <b>3. Pipelining to Reduce the Power</b>                           | <b>55</b>  |

| <i>David Chinnery, Kurt Keutzer</i>                                |            |

| 3.1 Introduction.....                                              | 57         |

| 3.2 Pipelining overheads.....                                      | 61         |

| 3.3 Pipelining power and delay model .....                         | 67         |

| 3.4 ASIC versus custom pipelining .....                            | 74         |

| 3.5 Other factors affecting the power gap .....                    | 81         |

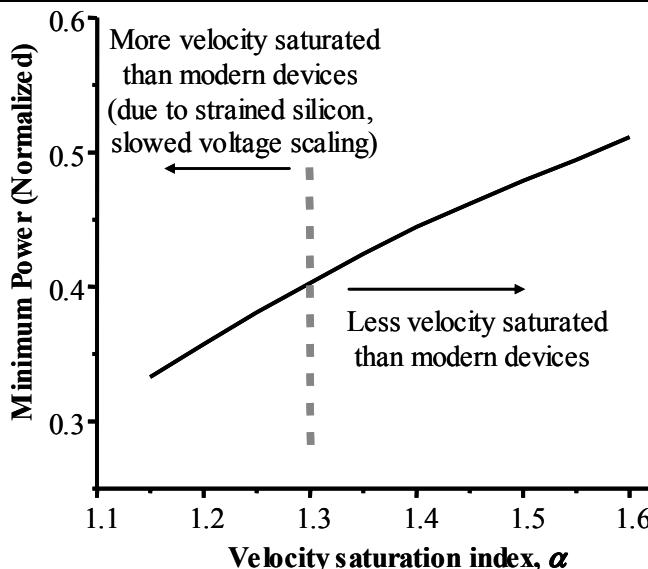

| 3.6 Other factors affecting the minimum energy per operation ..... | 81         |

| 3.7 Summary .....                                                  | 84         |

| <b>4. Voltage Scaling</b>                                          | <b>89</b>  |

| <i>David Chinnery, Kurt Keutzer</i>                                |            |

| 4.1 Introduction.....                                              | 89         |

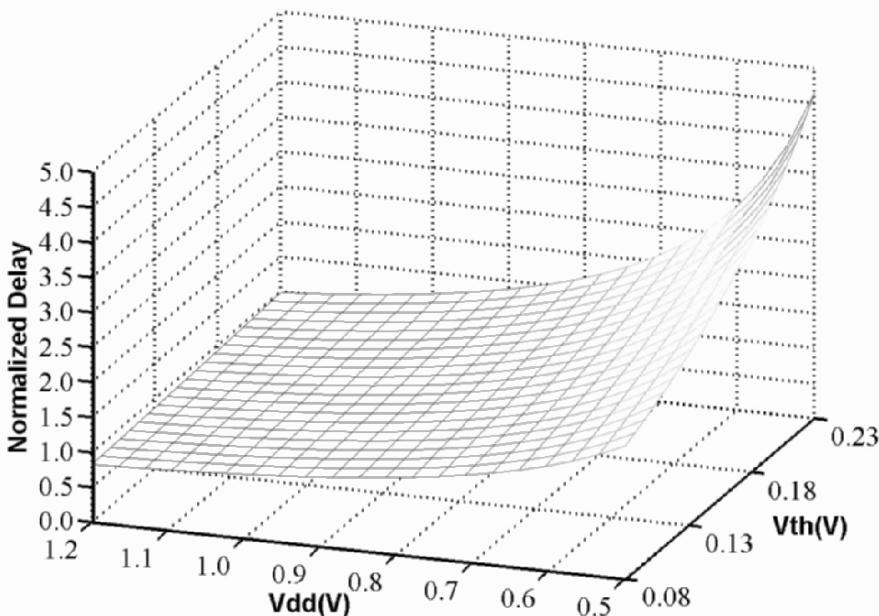

| 4.2 Delay .....                                                    | 90         |

| 4.3 Switching power .....                                          | 94         |

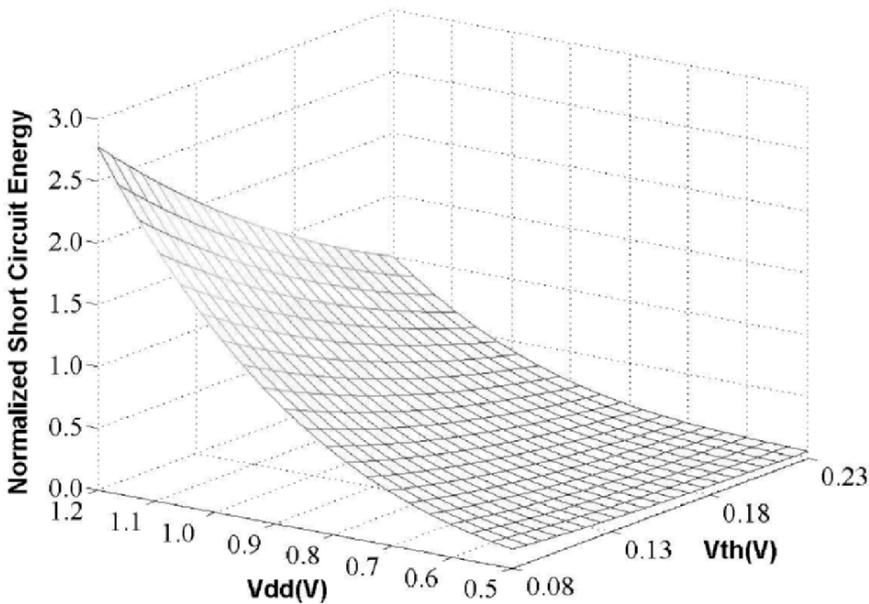

| 4.4 Short circuit power .....                                      | 95         |

| 4.5 Leakage power.....                                             | 97         |

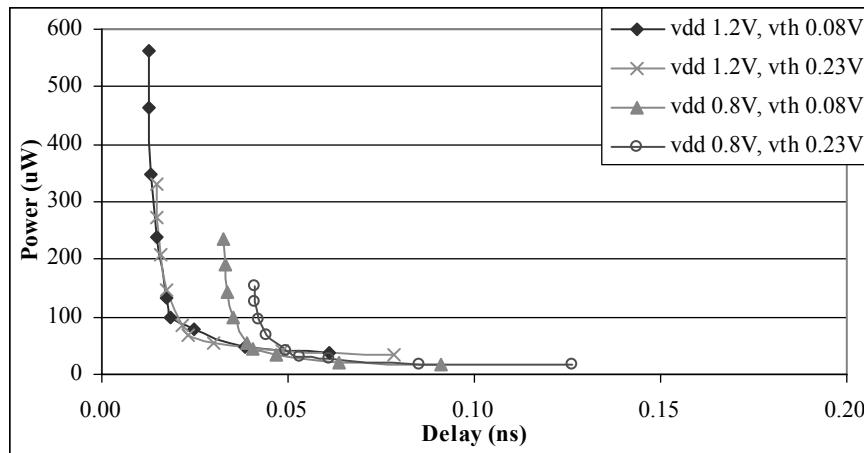

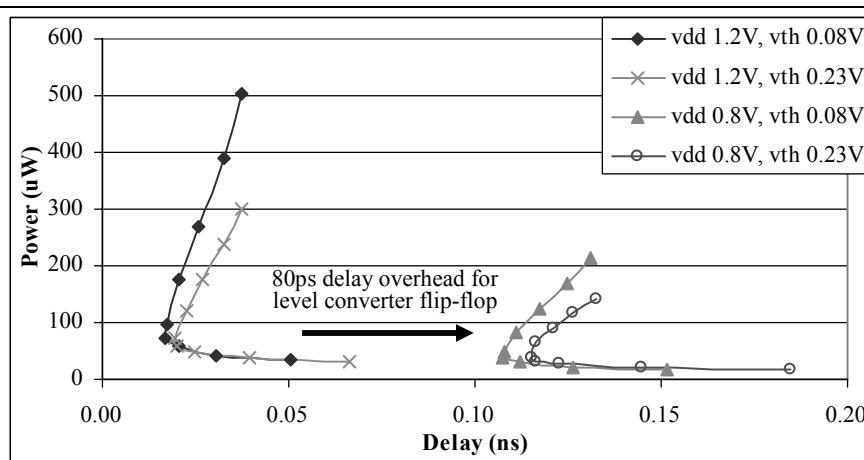

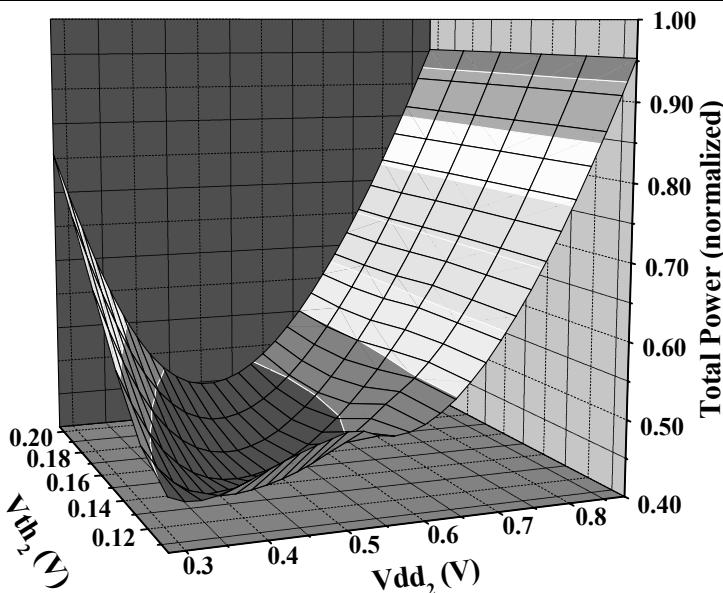

| 4.6 0.13um data for total power.....                               | 99         |

| 4.7 Summary .....                                                  | 104        |

## DESIGN TECHNIQUES

|                                                                                |            |

|--------------------------------------------------------------------------------|------------|

| <b>5. Methodology to Optimize Energy of Computation for SOCs</b>               | <b>107</b> |

| <i>Jagesh Sanghavi, Eliot Gerstner</i>                                         |            |

| 5.1 Introduction.....                                                          | 107        |

| 5.2 Problem definition and solution approach.....                              | 109        |

| 5.3 Optimization methodology .....                                             | 110        |

| 5.4 Experimental results .....                                                 | 113        |

| 5.5 Summary .....                                                              | 119        |

| <b>6. Linear Programming for Gate Sizing</b>                                   | <b>121</b> |

| <i>David Chinnery, Kurt Keutzer</i>                                            |            |

| 6.1 Introduction.....                                                          | 121        |

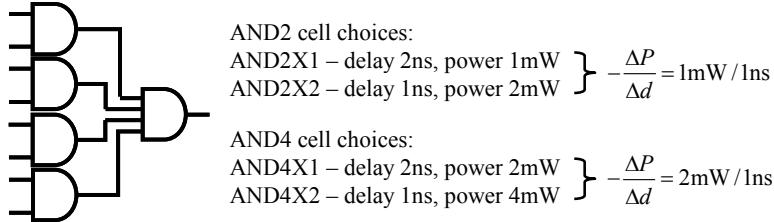

| 6.2 Overview of TILOS gate sizing.....                                         | 124        |

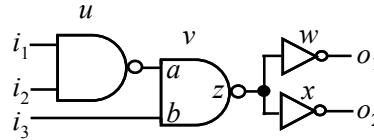

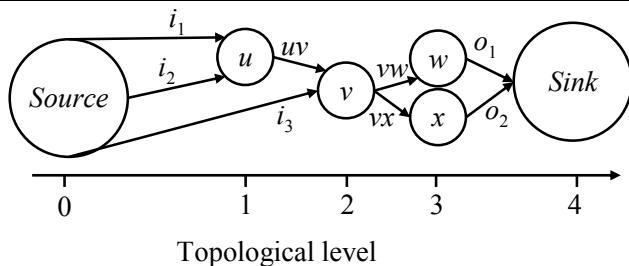

| 6.3 Linear programming formulation .....                                       | 126        |

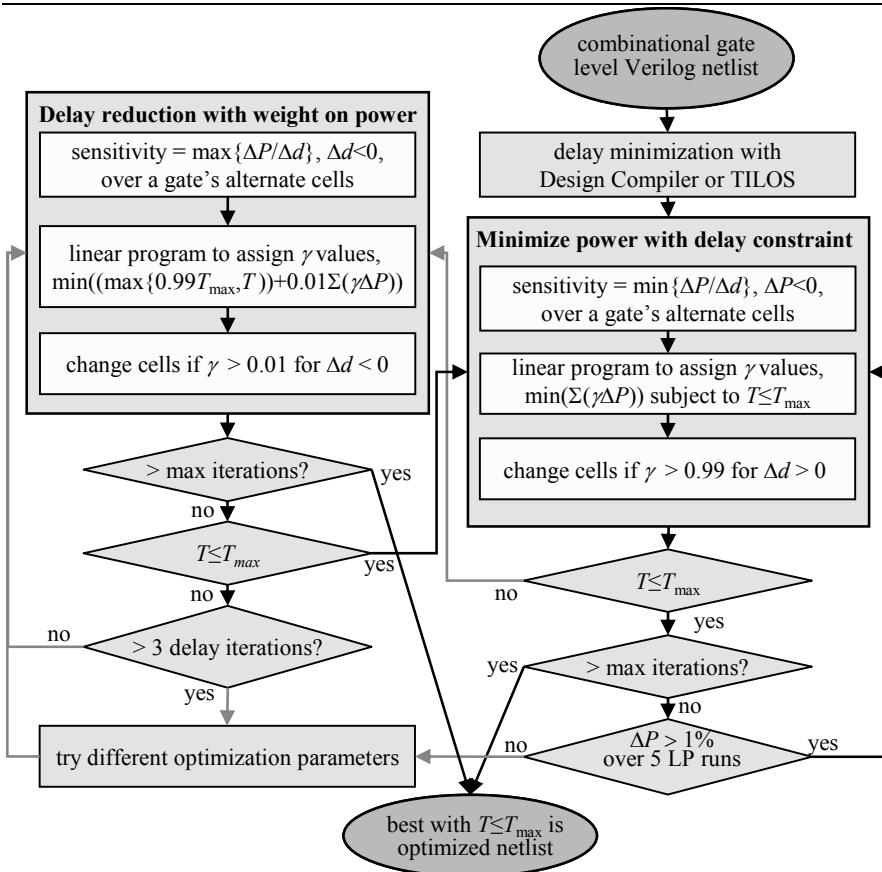

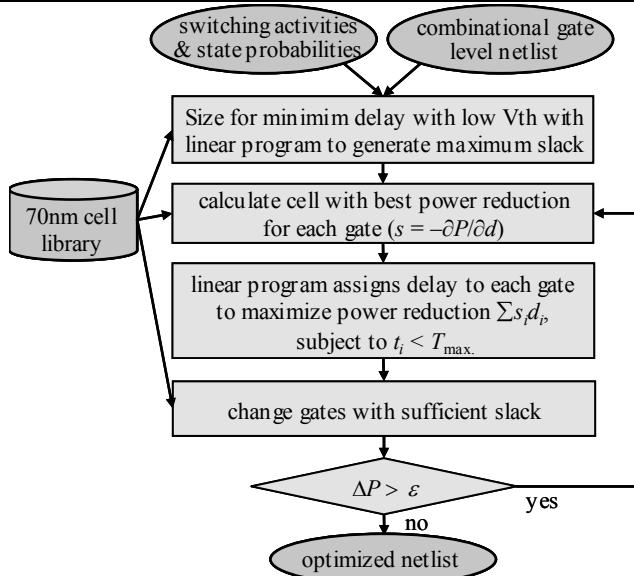

| 6.4 Optimization flow .....                                                    | 137        |

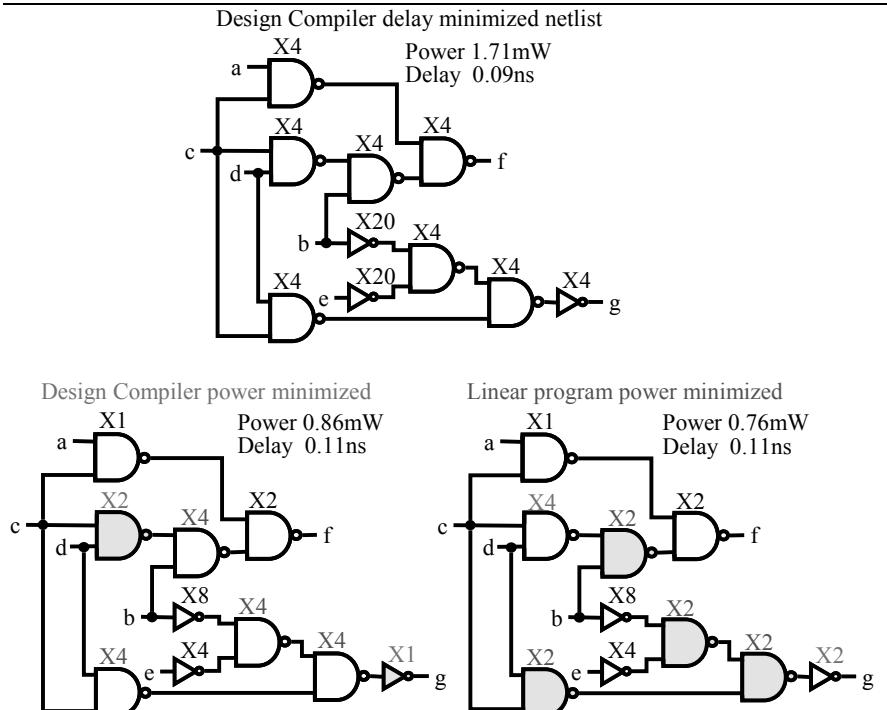

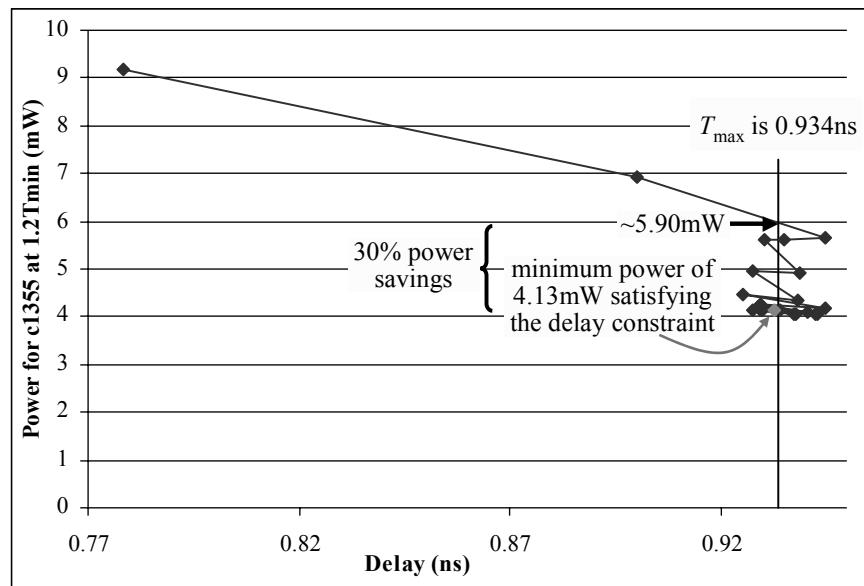

| 6.5 Comparison of gate sizing results.....                                     | 140        |

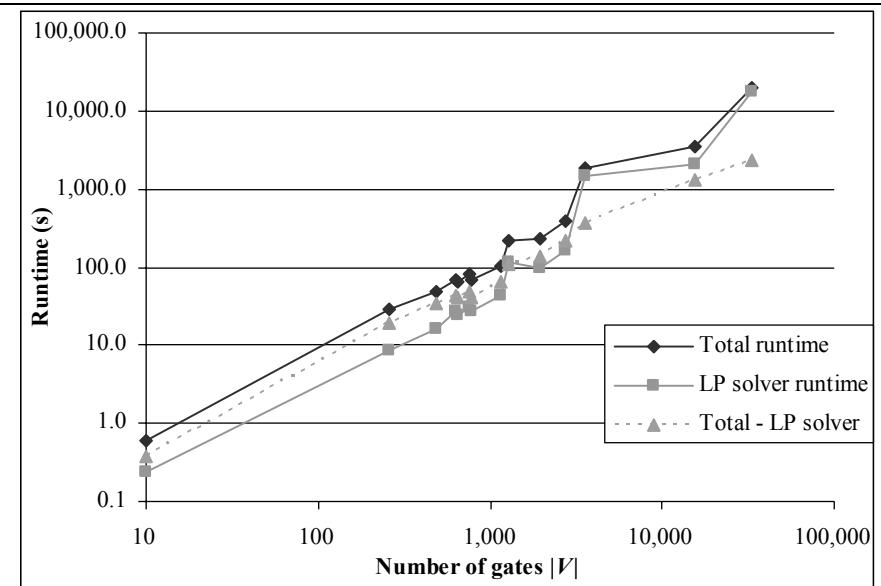

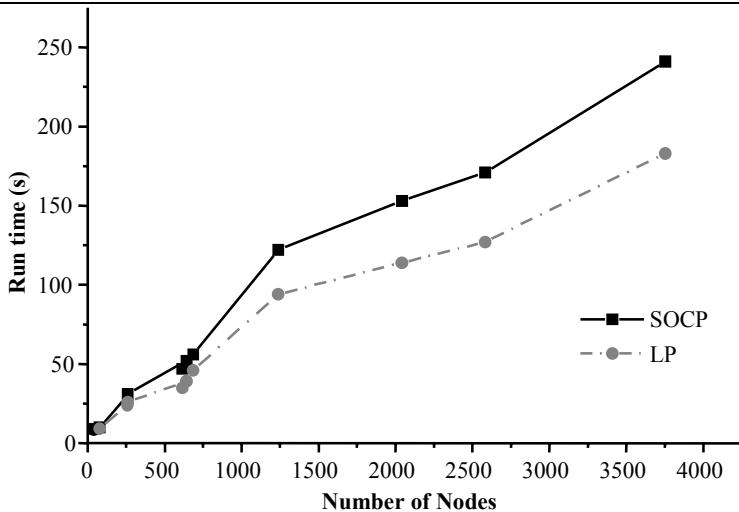

| 6.6 Computational runtime .....                                                | 143        |

| 6.7 Summary .....                                                              | 147        |

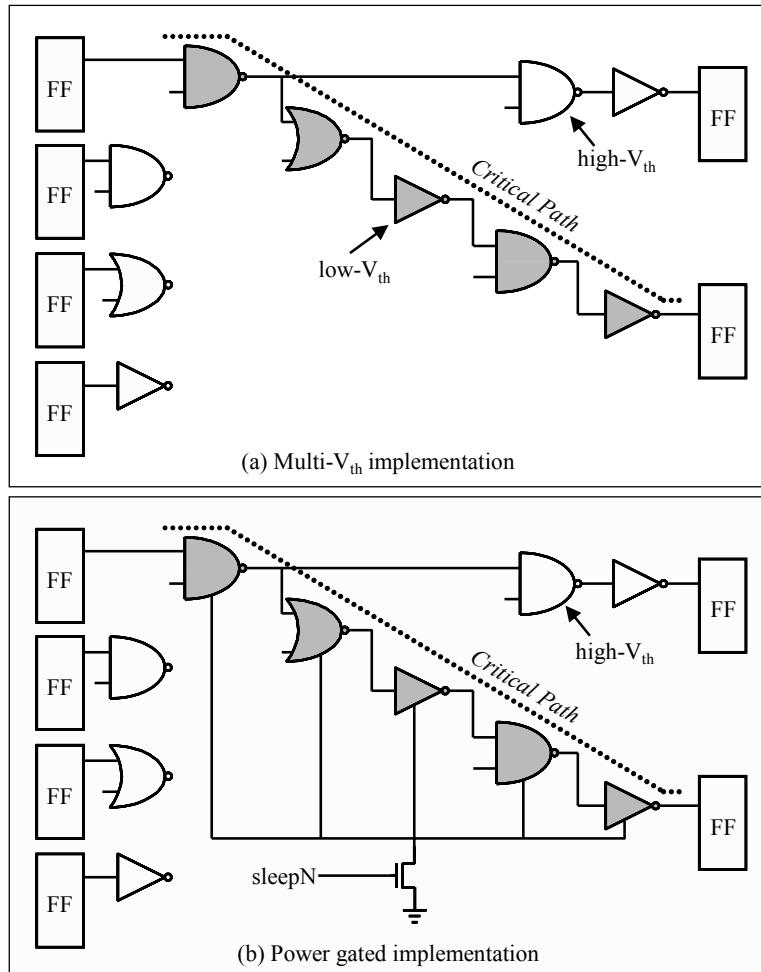

| <b>7. Linear Programming for Multi-Vth and Multi-Vdd Assignment</b>            | <b>151</b> |

| <i>David Chinnery, Kurt Keutzer</i>                                            |            |

| 7.1 Introduction.....                                                          | 151        |

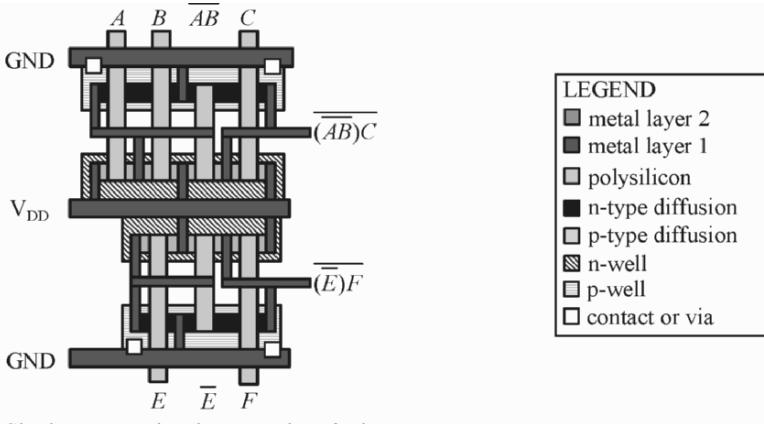

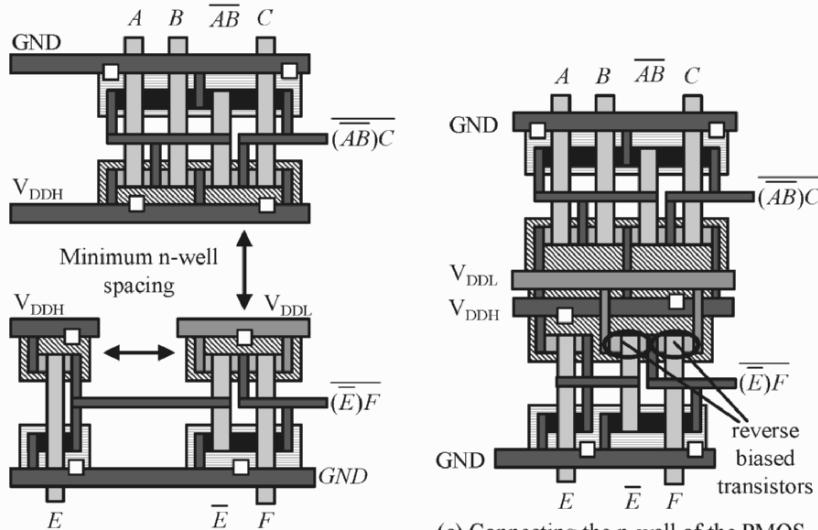

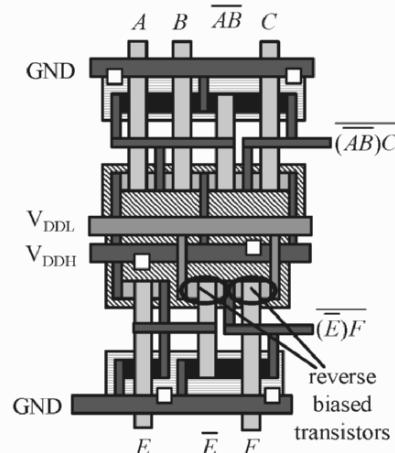

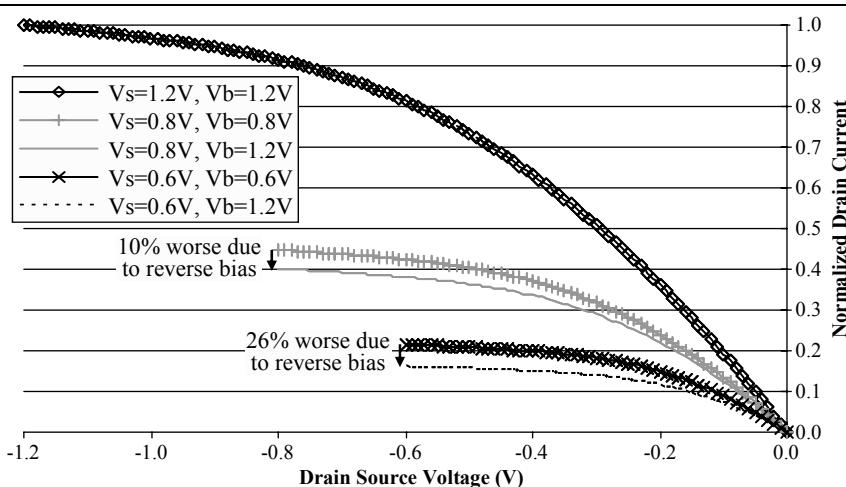

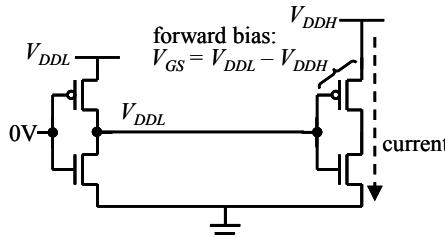

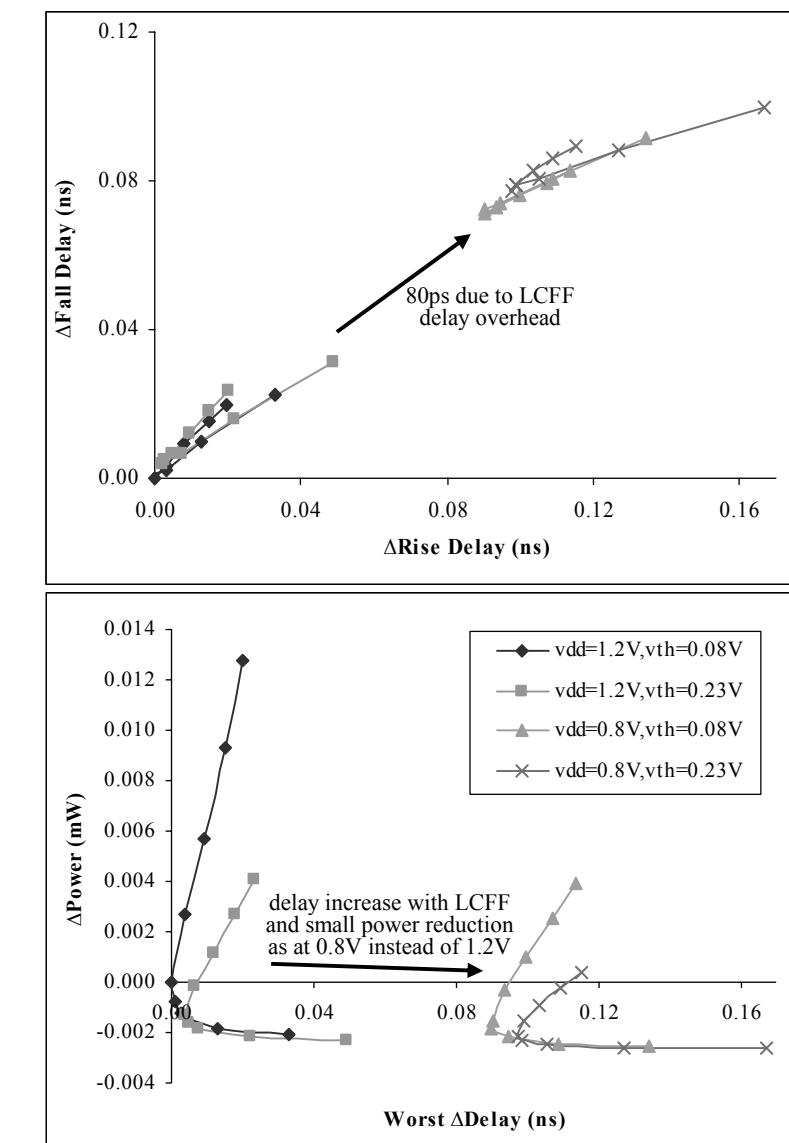

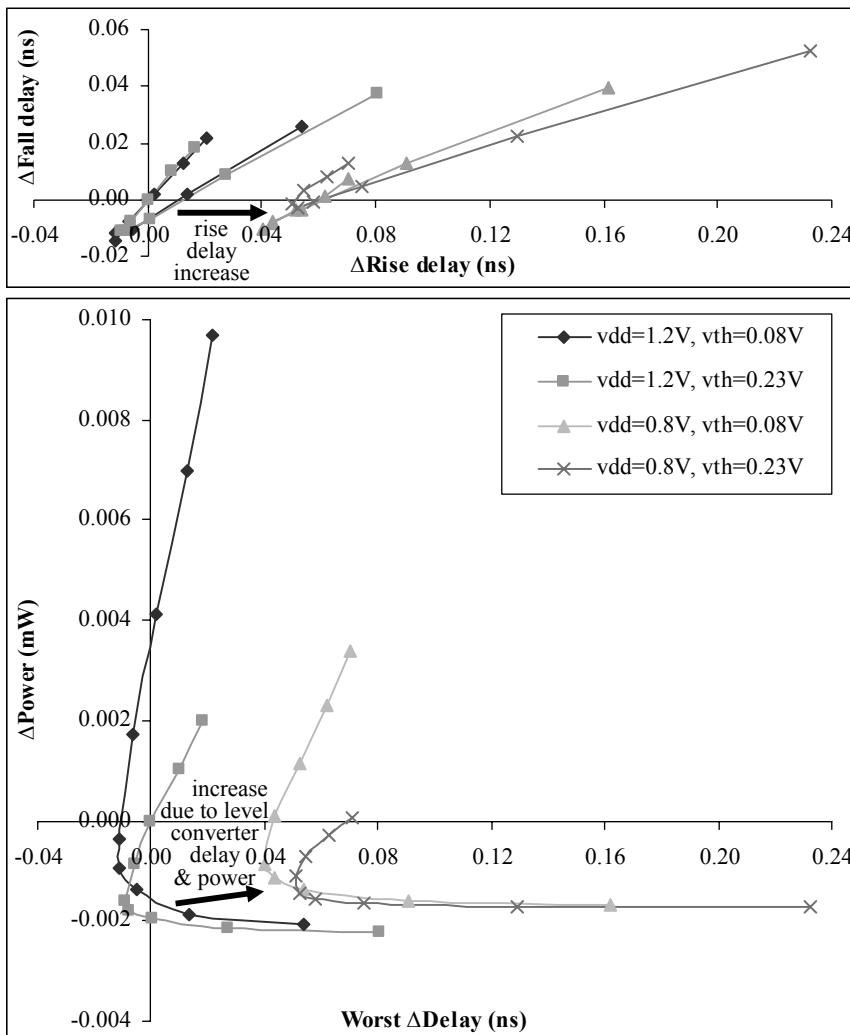

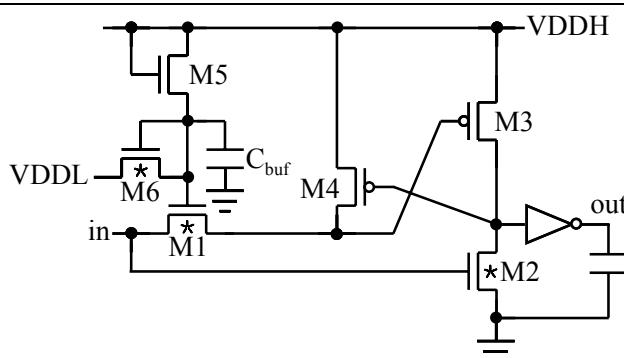

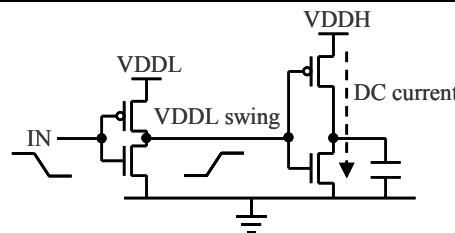

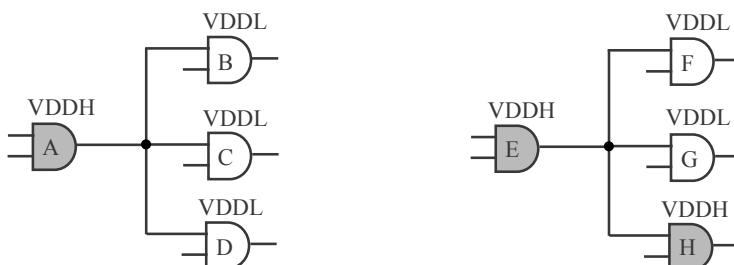

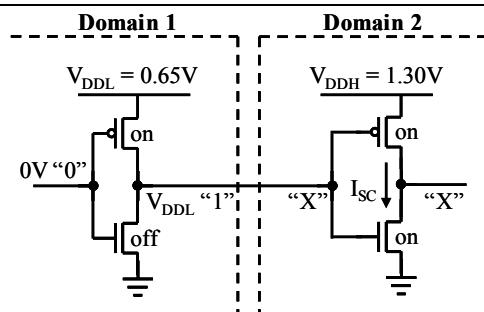

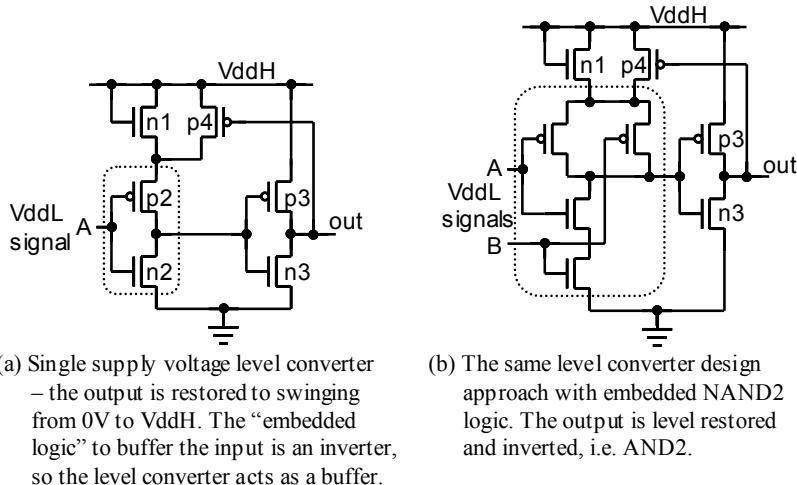

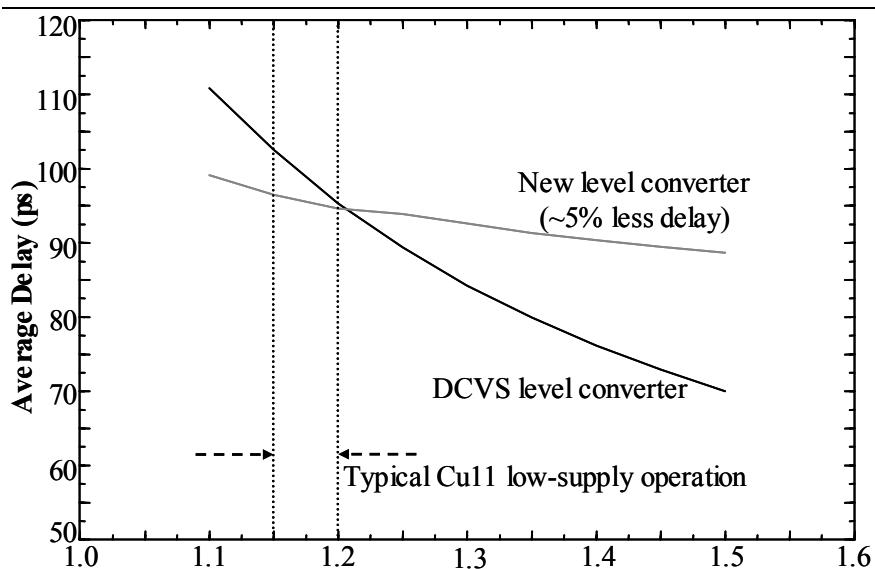

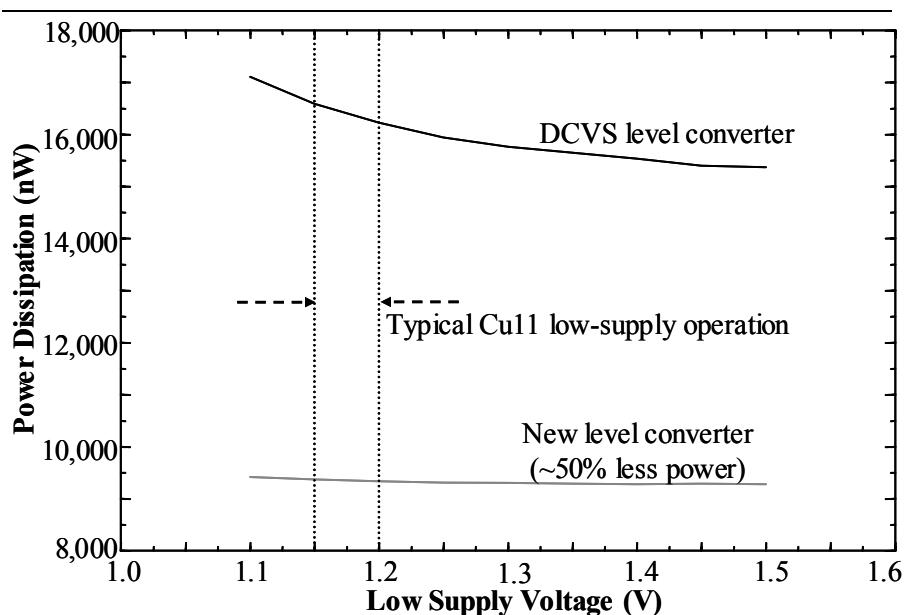

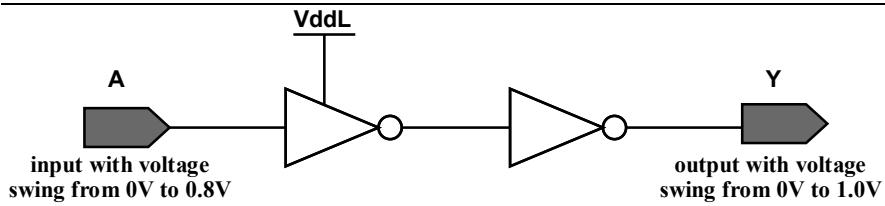

| 7.2 Voltage level restoration for multi-Vdd .....                              | 155        |

| 7.3 Previous multi-Vdd and multi-Vth optimization research .....               | 156        |

| 7.4 Optimizing with multiple supply and threshold voltages.....                | 160        |

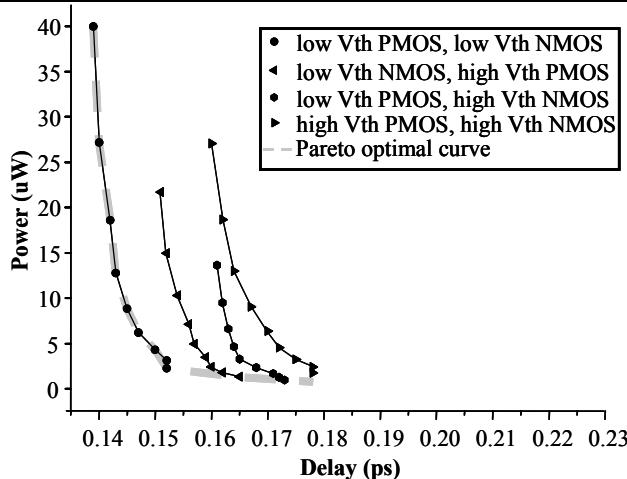

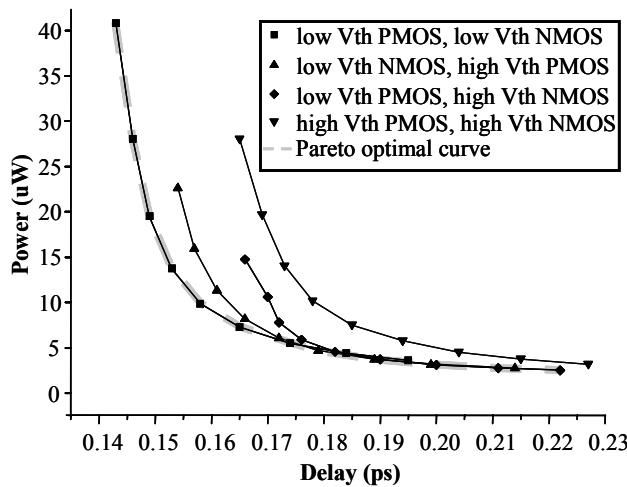

| 7.5 Comparison of multi-Vdd and multi-Vth results .....                        | 167        |

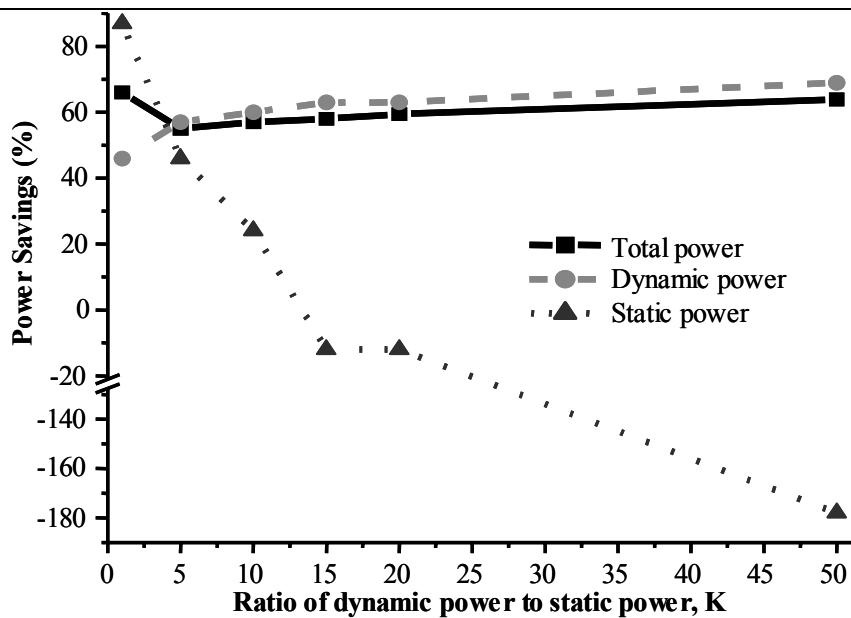

| 7.6 Analysis of power savings with multi-Vth and multi-Vdd .....               | 171        |

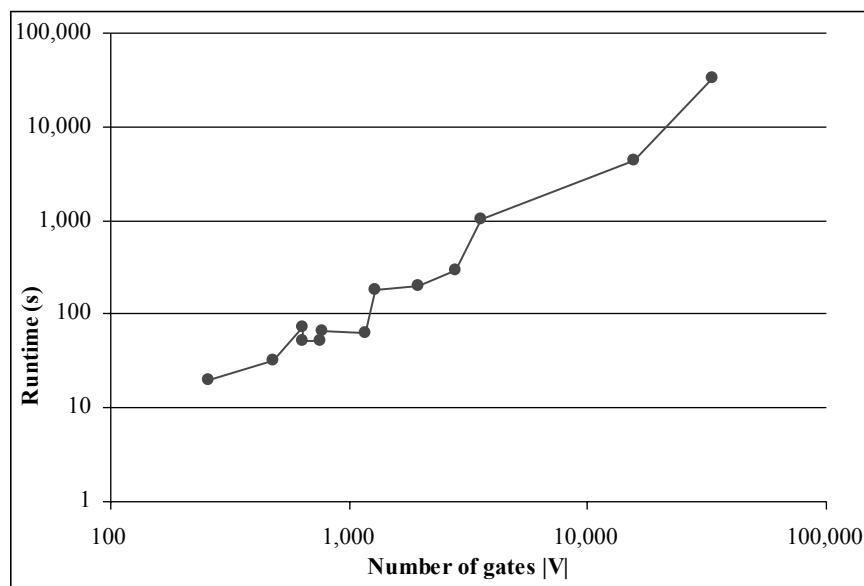

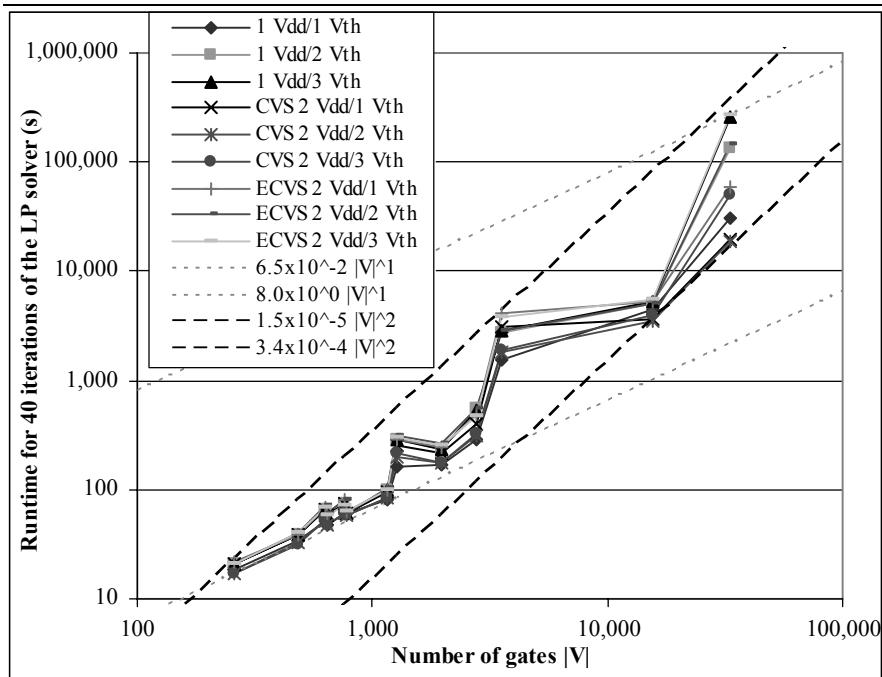

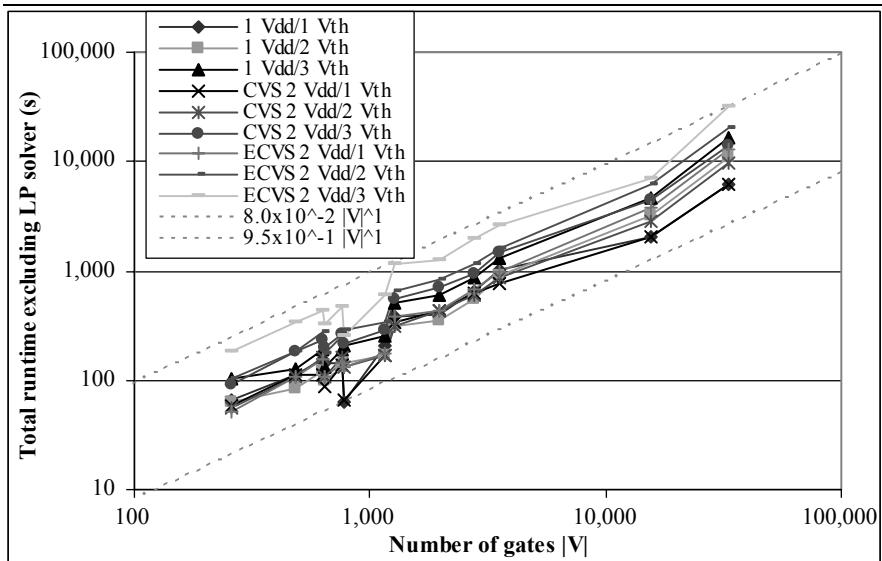

| 7.7 Computational runtimes with multi-Vdd and multi-Vth.....                   | 185        |

| 7.8 Summary .....                                                              | 186        |

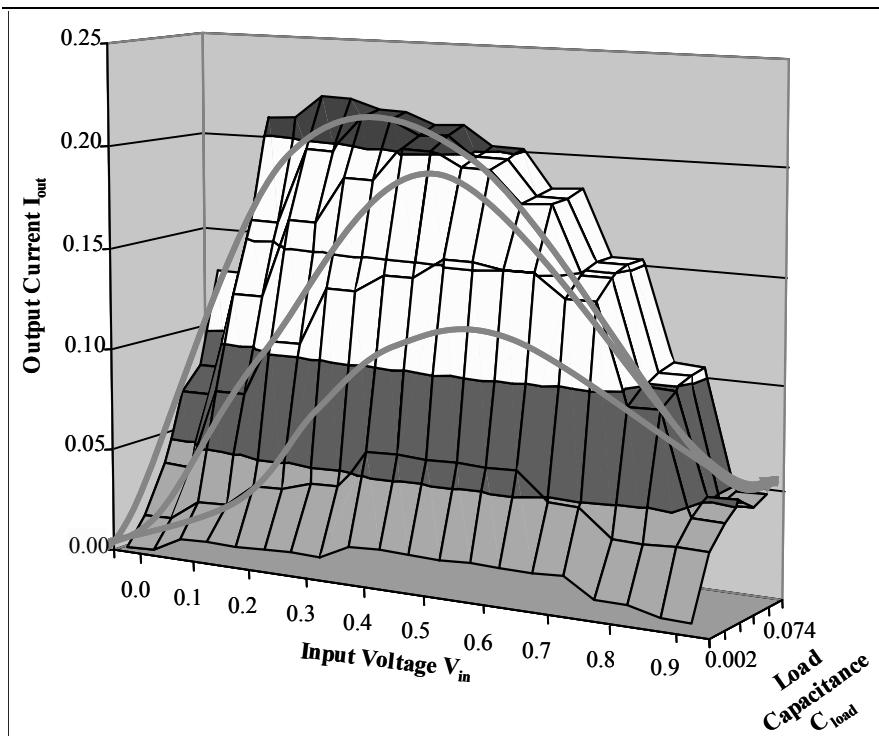

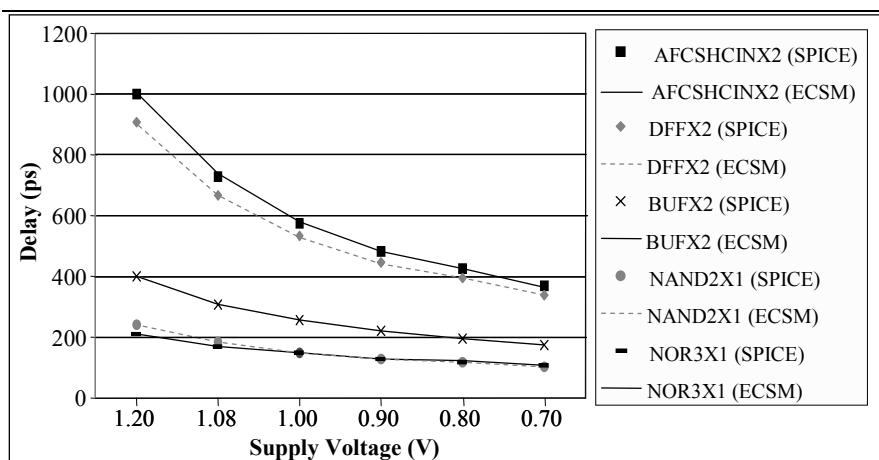

| <b>8. Power Optimization using Multiple Supply Voltages</b>                    | <b>189</b> |

| <i>Sarvesh Kulkarni, Ashish Srivastava,<br/>Dennis Sylvester, David Blaauw</i> |            |

| 8.1 Introduction.....                                                          | 189        |

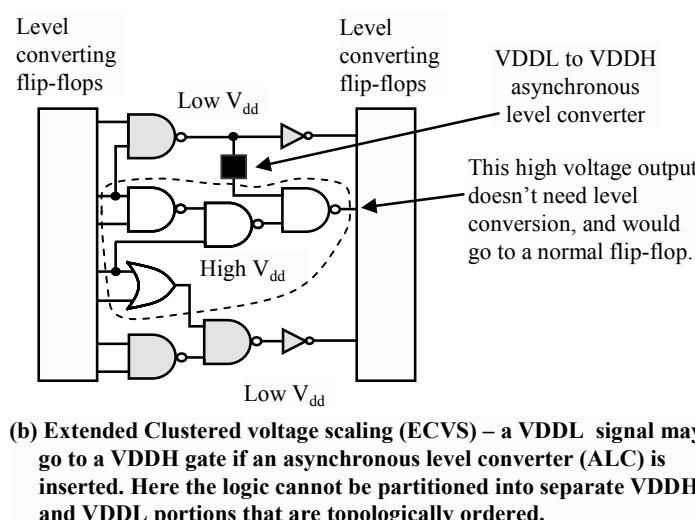

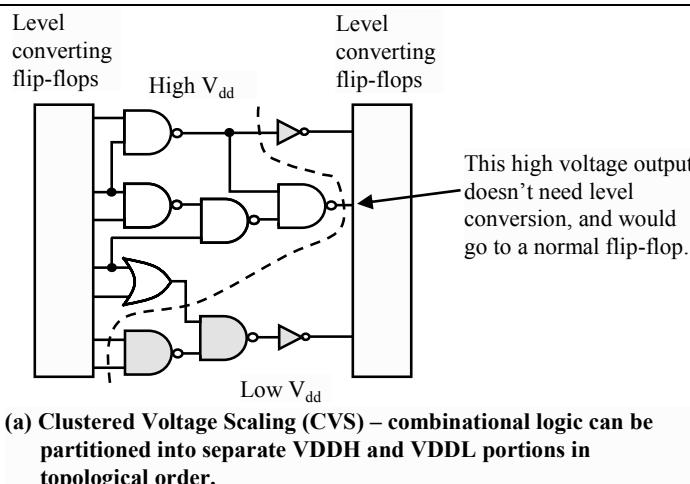

| 8.2 Overview of CVS and ECVS .....                                             | 192        |

| 8.3 Greedy ECVS: a new dual-VDD assignment algorithm.....                      | 196        |

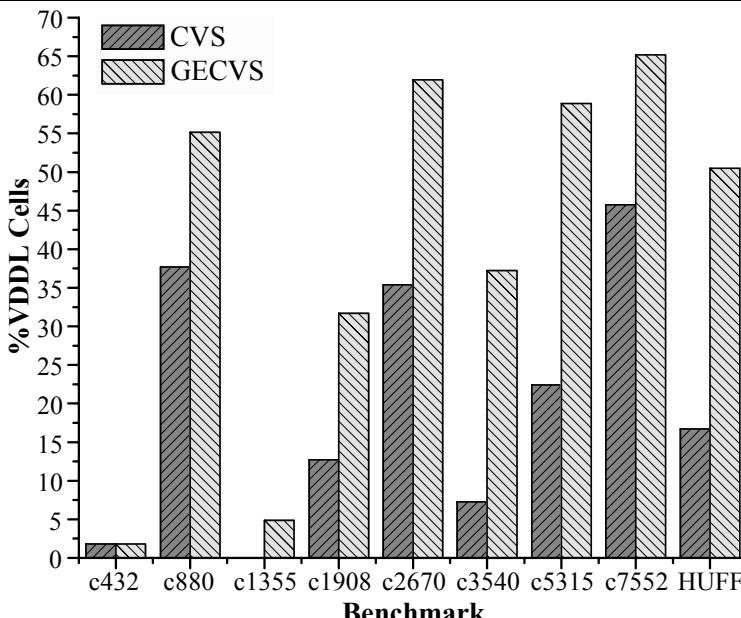

| 8.4 Power savings with CVS and GECVS .....                                     | 199        |

| 8.5 Gate sizing and dual-Vth assignment.....                                   | 201        |

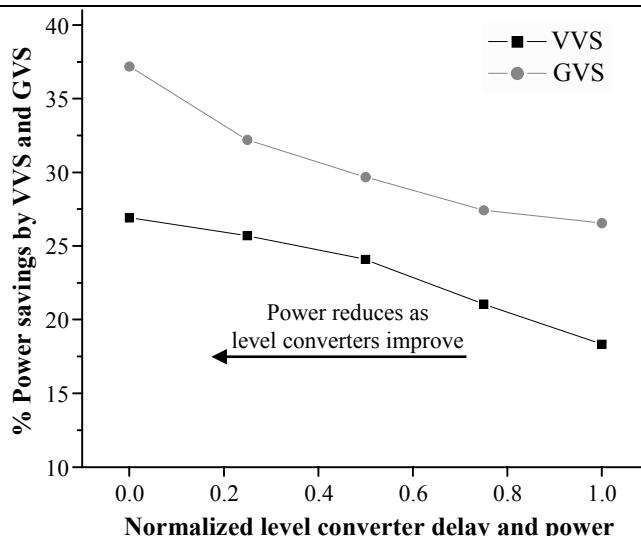

| 8.6 Power savings with VVS and GVS .....                                       | 211        |

| 8.7 Summary .....                                                              | 214        |

| <b>9. Placement for Power Optimization</b>                                     | <b>219</b> |

| <i>Ameya R. Agnihotri, Satoshi Ono, Patrick H. Madden</i>                      |            |

| 9.1 Introduction.....                                                          | 219        |

|                        |                                                                                                                         |            |

|------------------------|-------------------------------------------------------------------------------------------------------------------------|------------|

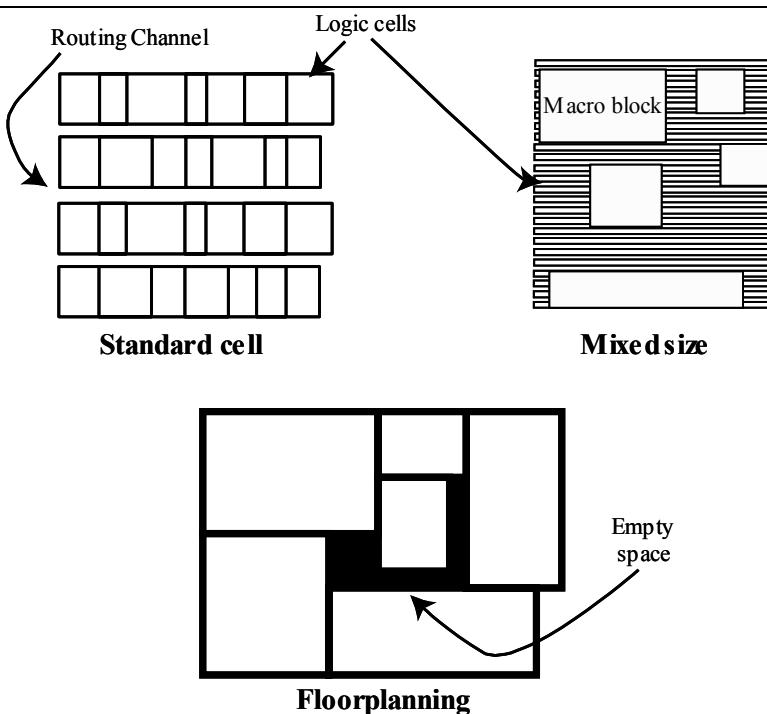

| 9.2                    | Placement basics .....                                                                                                  | 221        |

| 9.3                    | Physical synthesis .....                                                                                                | 226        |

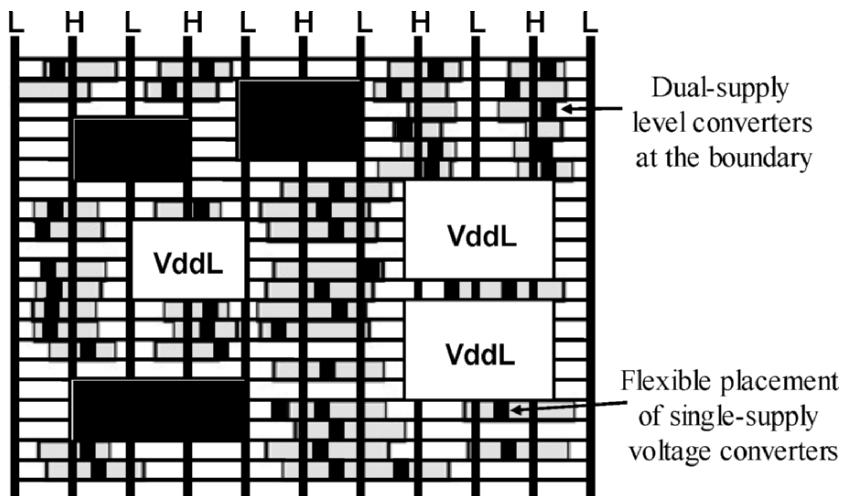

| 9.4                    | Multiple supply voltage placement .....                                                                                 | 239        |

| 9.5                    | State of the art .....                                                                                                  | 242        |

| 9.6                    | Summary .....                                                                                                           | 246        |

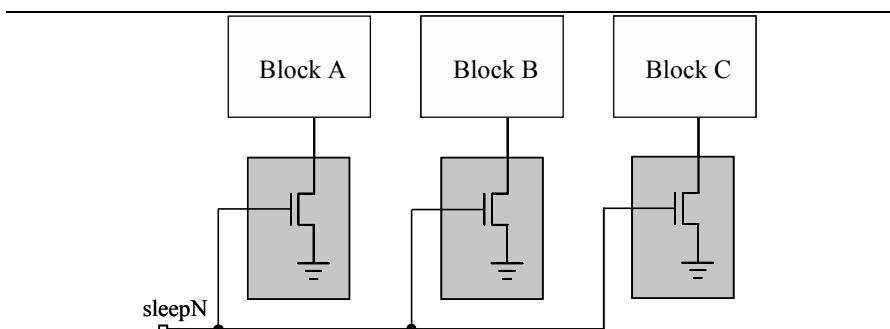

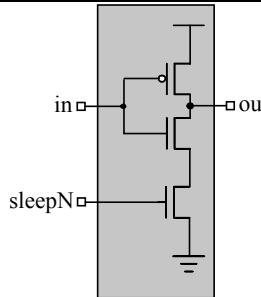

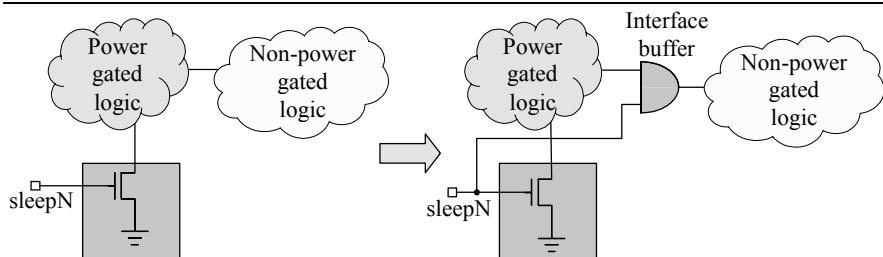

| <b>10.</b>             | <b>Power Gating Design Automation</b>                                                                                   | <b>251</b> |

|                        | <i>Jerry Frenkil, Srinivasa Venkatraman</i>                                                                             |            |

| 10.1                   | Introduction .....                                                                                                      | 251        |

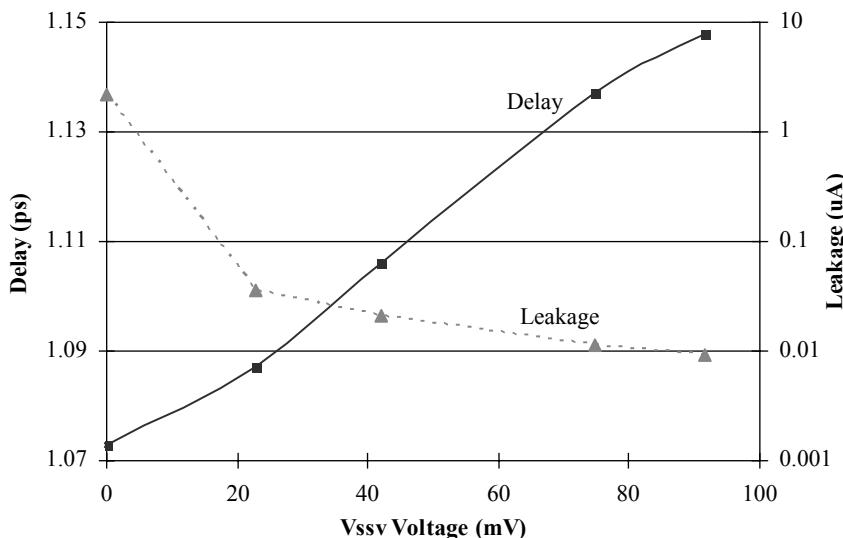

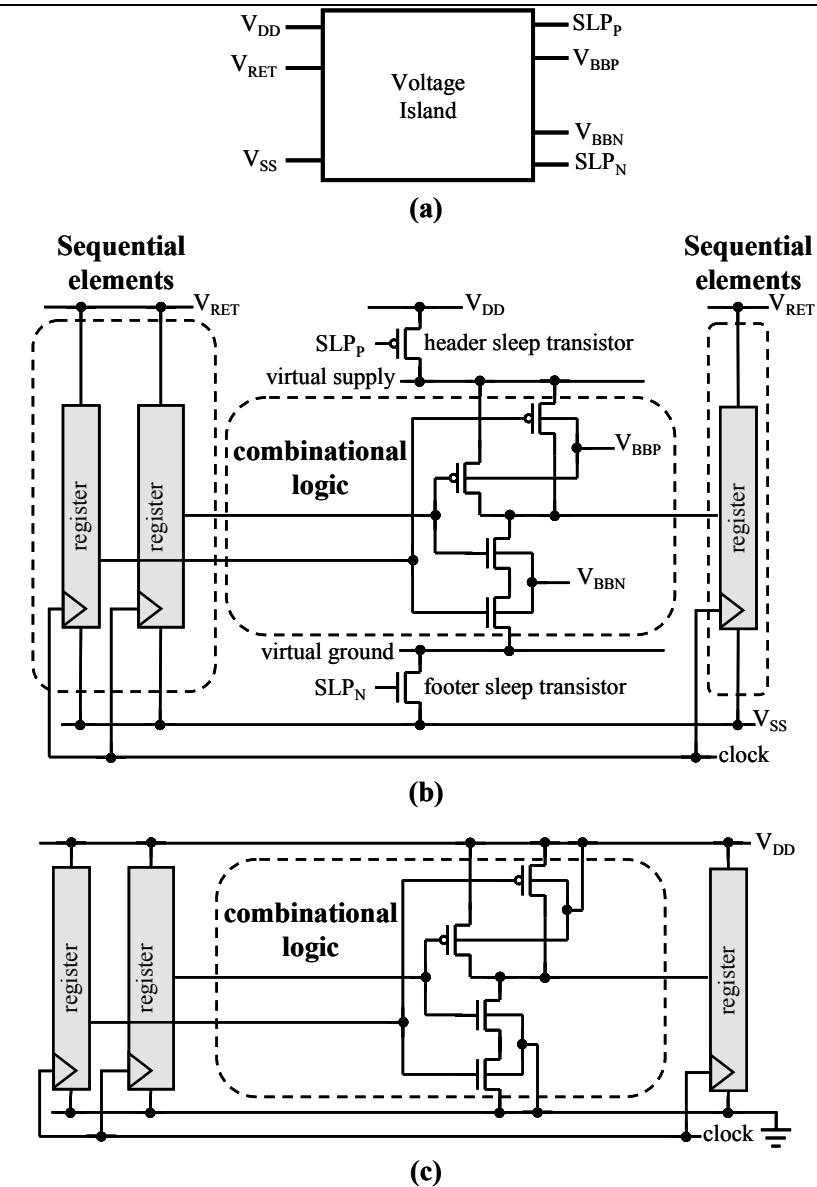

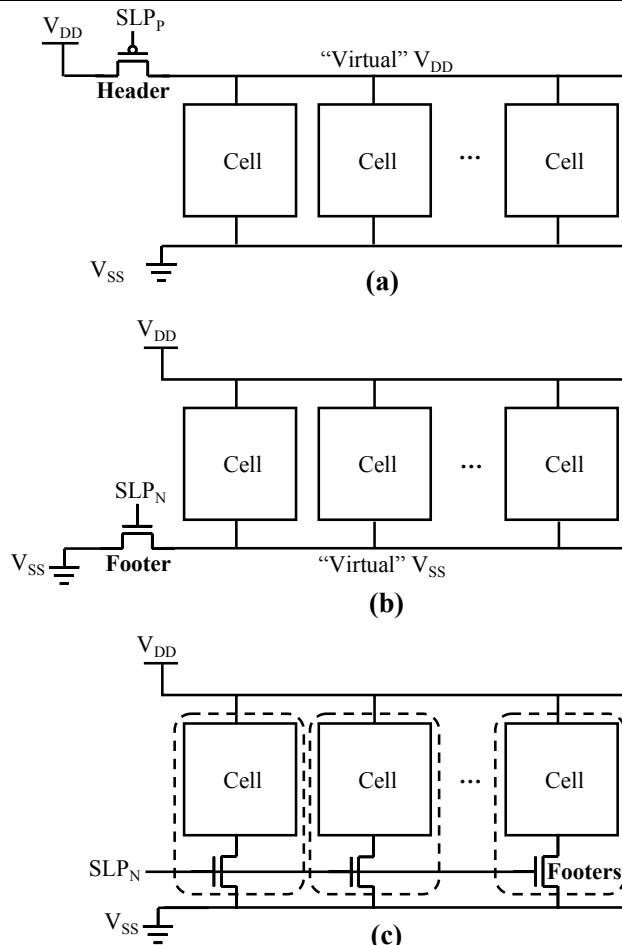

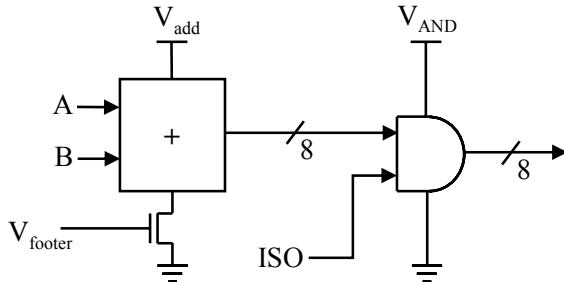

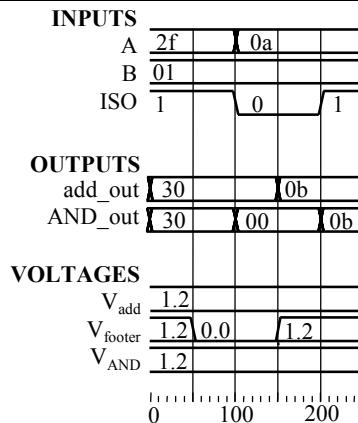

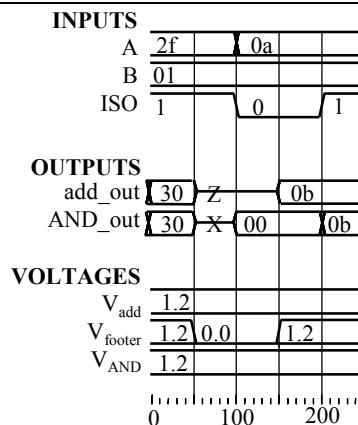

| 10.2                   | Leakage control techniques .....                                                                                        | 252        |

| 10.3                   | Power gating design issues .....                                                                                        | 255        |

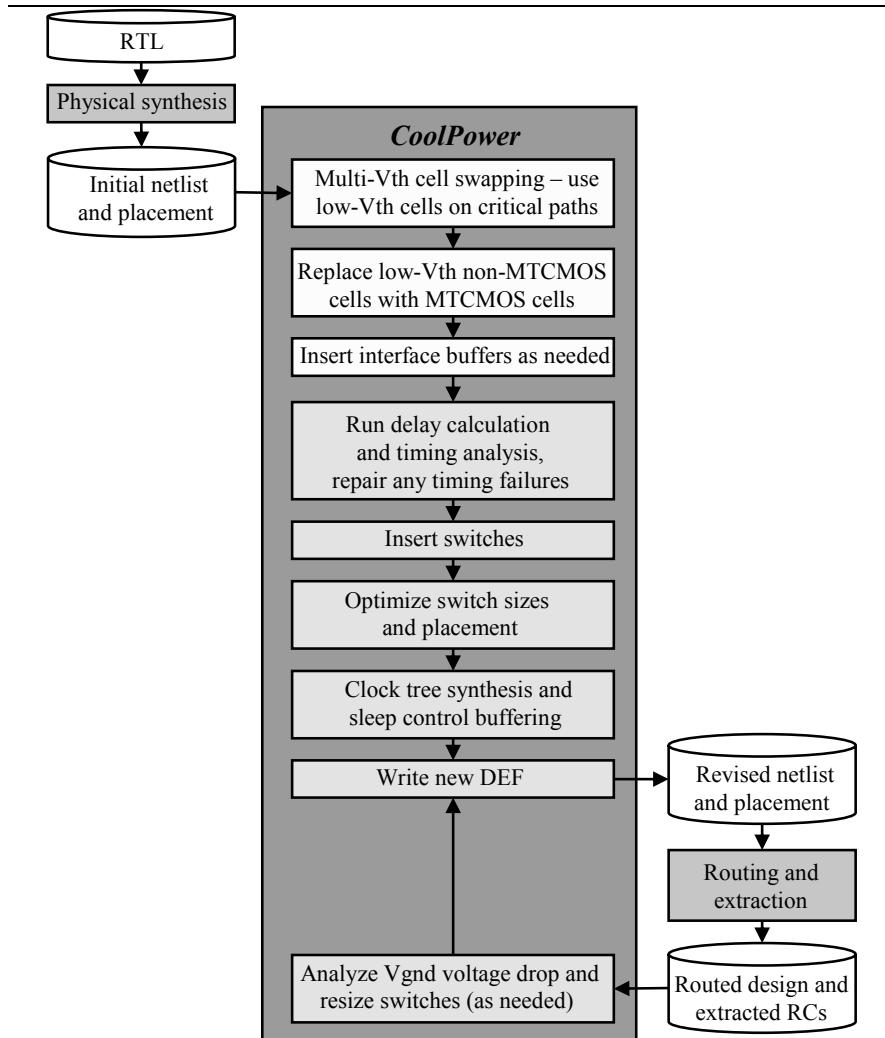

| 10.4                   | Coolpower design automation .....                                                                                       | 262        |

| 10.5                   | Application flows .....                                                                                                 | 269        |

| 10.6                   | Results .....                                                                                                           | 272        |

| 10.7                   | Future work .....                                                                                                       | 277        |

| 10.8                   | Summary .....                                                                                                           | 278        |

| <b>11.</b>             | <b>Verification for Multiple Supply Voltage Designs</b>                                                                 | <b>281</b> |

|                        | <i>Barry Pangrle, Srikanth Jadcherla</i>                                                                                |            |

| 11.1                   | Introduction .....                                                                                                      | 281        |

| 11.2                   | Multiple voltage definitions and scenarios .....                                                                        | 283        |

| 11.3                   | Design examples .....                                                                                                   | 290        |

| 11.4                   | Summary .....                                                                                                           | 297        |

| <b>12.</b>             | <b>Winning the Power Struggle in an Uncertain Era</b>                                                                   | <b>299</b> |

|                        | <i>Murari Mani, Michael Orshansky</i>                                                                                   |            |

| 12.1                   | Introduction .....                                                                                                      | 299        |

| 12.2                   | Process variability and its impact on power .....                                                                       | 300        |

| 12.3                   | Parametric yield estimation .....                                                                                       | 303        |

| 12.4                   | Optimization techniques for yield: an overview .....                                                                    | 305        |

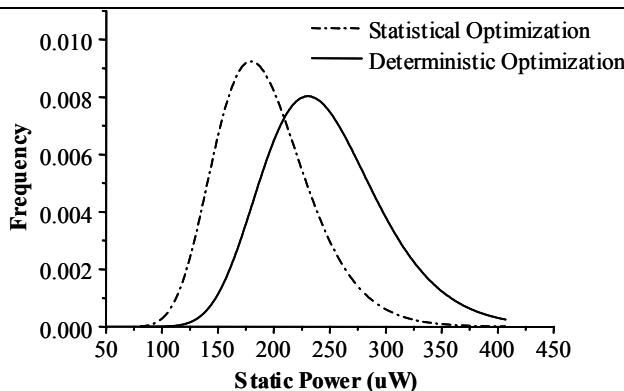

| 12.5                   | Efficient statistical parametric yield maximization .....                                                               | 308        |

| 12.6                   | Summary .....                                                                                                           | 319        |

| <b>DESIGN EXAMPLES</b> |                                                                                                                         |            |

| <b>13.</b>             | <b>Pushing ASIC Performance in a Power Envelope</b>                                                                     | <b>323</b> |

|                        | <i>Leon Stok, Ruchir Puri, Subhrajit Bhattacharya, John Cohn, Dennis Sylvester, Ashish Srivastava, Sarvesh Kulkarni</i> |            |

| 13.1                   | Introduction .....                                                                                                      | 324        |

| 13.2                   | Power-performance trade-off with multi-Vdd and multi-Vth .....                                                          | 324        |

| 13.3                   | Design issues in multi-Vdd ASICs .....                                                                                  | 332        |

| 13.4                   | Case study .....                                                                                                        | 344        |

| 13.5                   | Summary .....                                                                                                           | 353        |

|                                             |            |

|---------------------------------------------|------------|

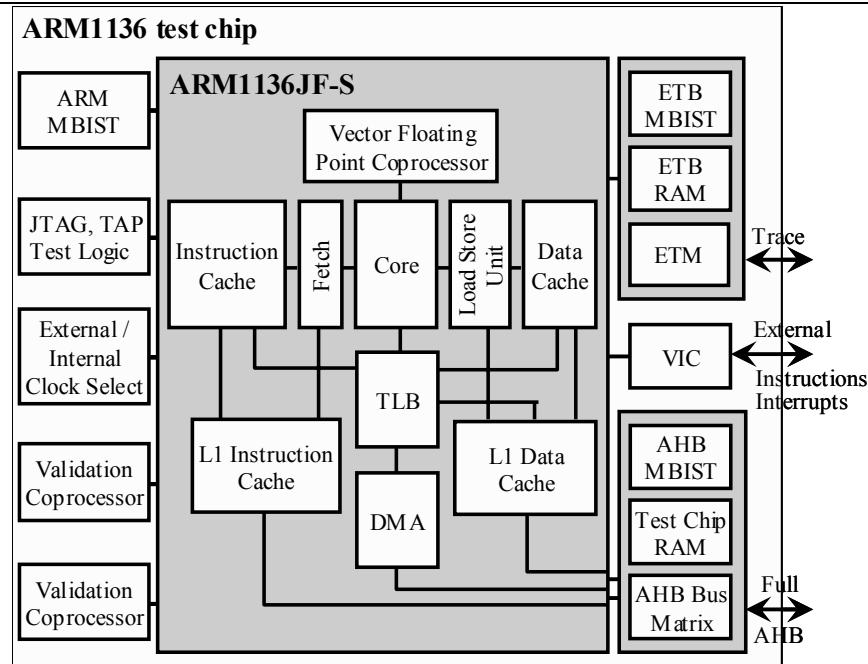

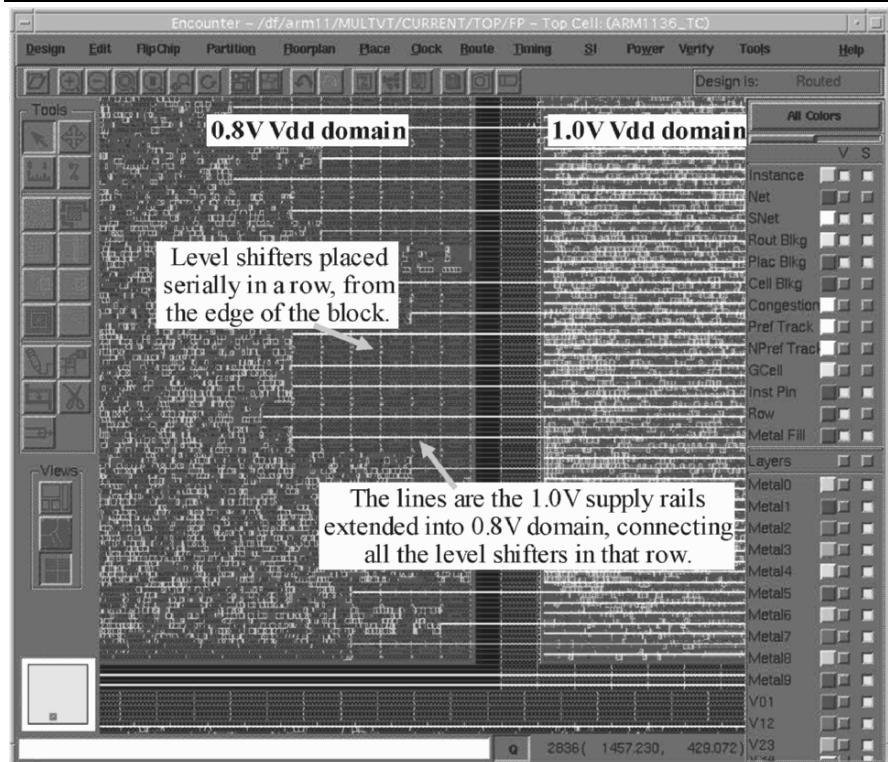

| <b>14. Low Power ARM 1136JF-S Design</b>    | <b>357</b> |

| <i>George Kuo, Anand Iyer</i>               |            |

| 14.1 Introduction.....                      | 357        |

| 14.2 Project objective .....                | 358        |

| 14.3 Key decisions and implemenations ..... | 362        |

| 14.4 Results.....                           | 377        |

| 14.5 Summary .....                          | 381        |

| <b>Index</b>                                | <b>383</b> |

# Chapter 1

## INTRODUCTION

David Chinnery, Kurt Keutzer

*Department of Electrical Engineering and Computer Sciences

University of California at Berkeley

Berkeley, CA 94720, USA*

This book examines the power consumption of ASIC and custom integrated-circuits. In particular, we examine the relationship between custom circuits designed without any significant restriction in design methodology and ASIC circuits designed in a high-productivity EDA tool methodology. From analysis of similar ASIC and custom designs, we estimate that the power consumption of typical ASICs may be 3 to 7 $\times$  that of custom ICs fabricated in process technology of the same generation. We consider ways to augment and enhance an ASIC methodology to bridge this power gap between ASIC and custom.

Reducing circuit power consumption has been a hot topic for some time; however, there has not been detailed analysis of the power gap between an automated design methodology and custom design. This work gives a quantitative analysis of the factors contributing to the power gap. By identifying the largest contributing factors, and which of these can be automated, we aim to help close the power gap.

We examine design approaches and tools to reduce the power consumption of designs produced in an automated design flow. In particular, we focus on microarchitectural techniques, improvements in algorithms for gate sizing and place and route, voltage scaling and use of multiple supply voltages to reduce dynamic power, power gating to reduce leakage power, and statistical power minimization. Design examples illustrate the use of these techniques and show that energy efficiency can be improved by a factor of 2 to 3 $\times$ .

### 1.1 DEFINITIONS: ASIC AND CUSTOM

The term *application-specific integrated-circuit* (ASIC), has a wide variety of associations. Strictly speaking, it simply refers to an *integrated*

*circuit* (IC) that has been designed for a particular *application*. This defines a portion of the semiconductor market. Other market segments include memories, microprocessors, and field programmable gate arrays (FPGAs).

Two industries grew to support the development of ASICs: vendors fabricating chips, and companies offering electronic design automation (EDA) software. The ASIC semiconductor-vendor industry, established by companies such as LSI Logic, provides the service of fabricating ASICs designed by other independent design groups. EDA companies such as Cadence and Synopsys provide commercial tools for designing these ASICs. Another key element of the ASIC design process is *ASIC libraries*. ASIC libraries are carefully characterized descriptions of the primitive logic-level building blocks provided by the ASIC vendors. Initially these libraries targeted gate-array implementations, but in time the higher-performance standard-cell targets became more popular.

ASIC vendors then offered complete design flows for their fabrication process. These consisted of ASIC tools, ASIC libraries for the process, and a particular design methodology. These embodied an *ASIC methodology* and were known as *ASIC design kits*. Smith's book on ASICs [6] is a great one-stop reference for ASICs.

Generally, ASICs are designed at the register-transfer level (RTL) in Verilog or VHDL, specifying the flow of data between registers and the state to store in registers. Commercial EDA tools are used to map the higher level RTL description to standard cells in an ASIC library, and then place the cells and route wires. It is much easier to migrate ASIC designs to a new process technology, compared to custom designs which have been optimized for a specific process at the gate or transistor-level. ASIC designers generally focus on high level designs choices, at the microarchitectural level for example.

With this broader context, let us pause to note that the use of the term ASIC can be misleading: it most often refers to an IC produced through a standard cell ASIC methodology and fabricated by an ASIC vendor. That IC may belong to the application-specific standard product (ASSP) portion of the semiconductor market. ASSPs are sold to many different system vendors [6], and often may be purchased as standard parts from a catalog, unlike ASICs.

The term *custom integrated-circuit*, or *custom IC*, also has a variety of associations, but it principally means a circuit produced through a custom-design methodology. More generally, custom IC is used synonymously with the semiconductor market segments of high-performance microprocessors and digital signal processors.

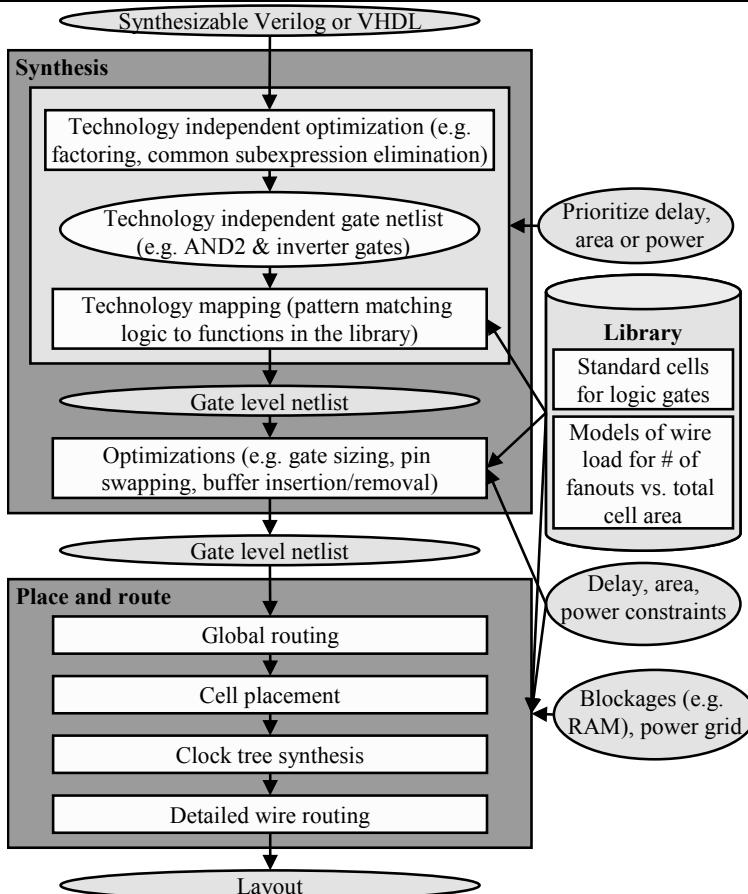

Figure 1.1 A typical EDA flow from a high level hardware design language (HDL) description through to layout.

Custom ICs are typically optimized for a specific process technology and take significantly more time to design than ASICs, but can achieve higher performance and lower power by higher quality design and use of techniques that are not generally available to ASICs. For example, custom designers may design logic gates at the transistor-level to provide implementations that are optimal for that specific design; whereas an ASIC designer is limited by what is available in the standard cell library.

## 1.2 WHAT IS A STANDARD CELL ASIC METHODOLOGY?

A standard cell ASIC methodology incorporates a standard cell library and automated design tools to utilize this library, in order to achieve higher

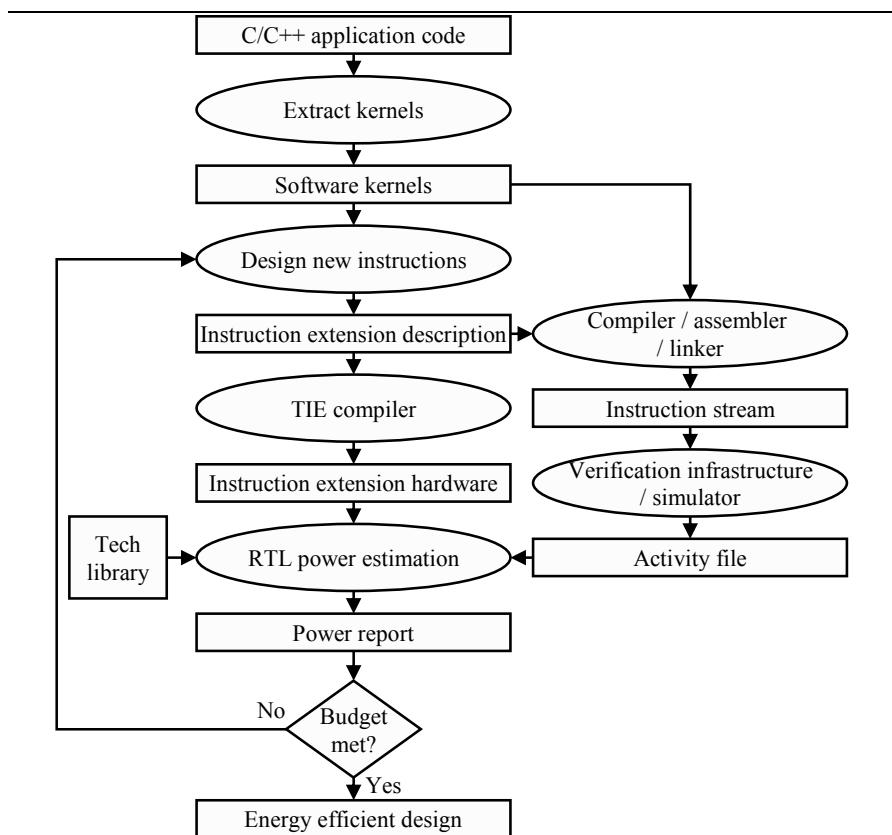

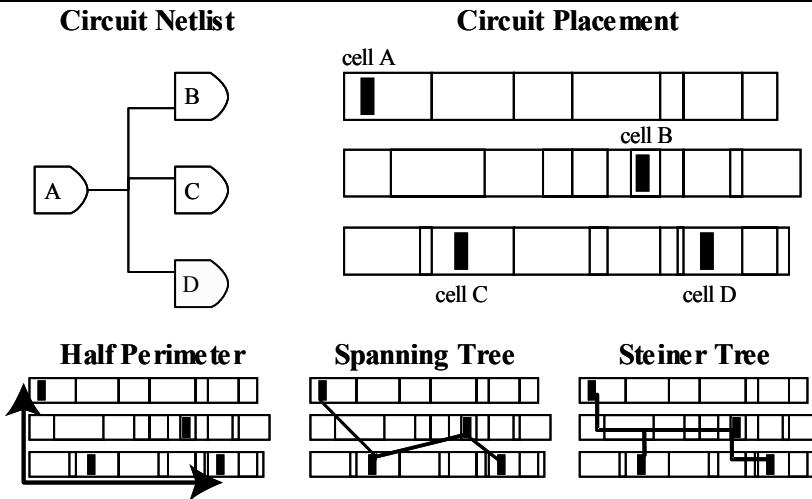

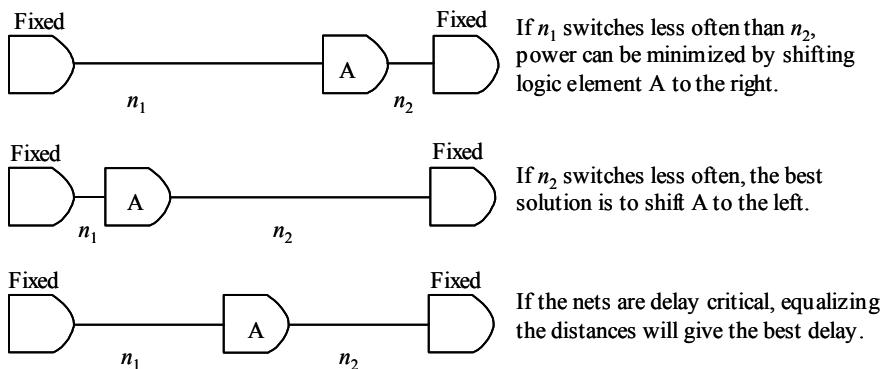

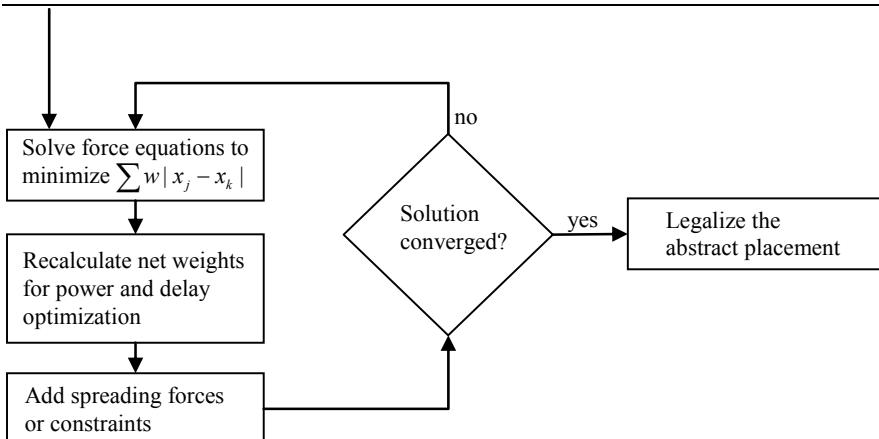

designer productivity. The designer specifies the circuit behavior in a hardware description language (HDL) such as Verilog or VHDL [5]. This high level description is then mapped to a library of standard cells that implement various logic functions, as shown in Figure 1.1. Various optimizations are performed to try and meet delay, power, or area constraints specified by the designer. The final layout of the chip is not known at the synthesis stage, so the wire capacitances are estimated using a wire load model. Then the standard cells are placed, wires are routed between them, and a clock tree network is inserted to distribute the clock signal.

The EDA flow may be iterated through many times as a design is changed to meet performance constraints. Small changes may be made at the layout level, but significant changes like resizing gates on a delay-critical path may require redoing place and route. After place and route, wire load models for later iterations may be updated based on the resulting layout.

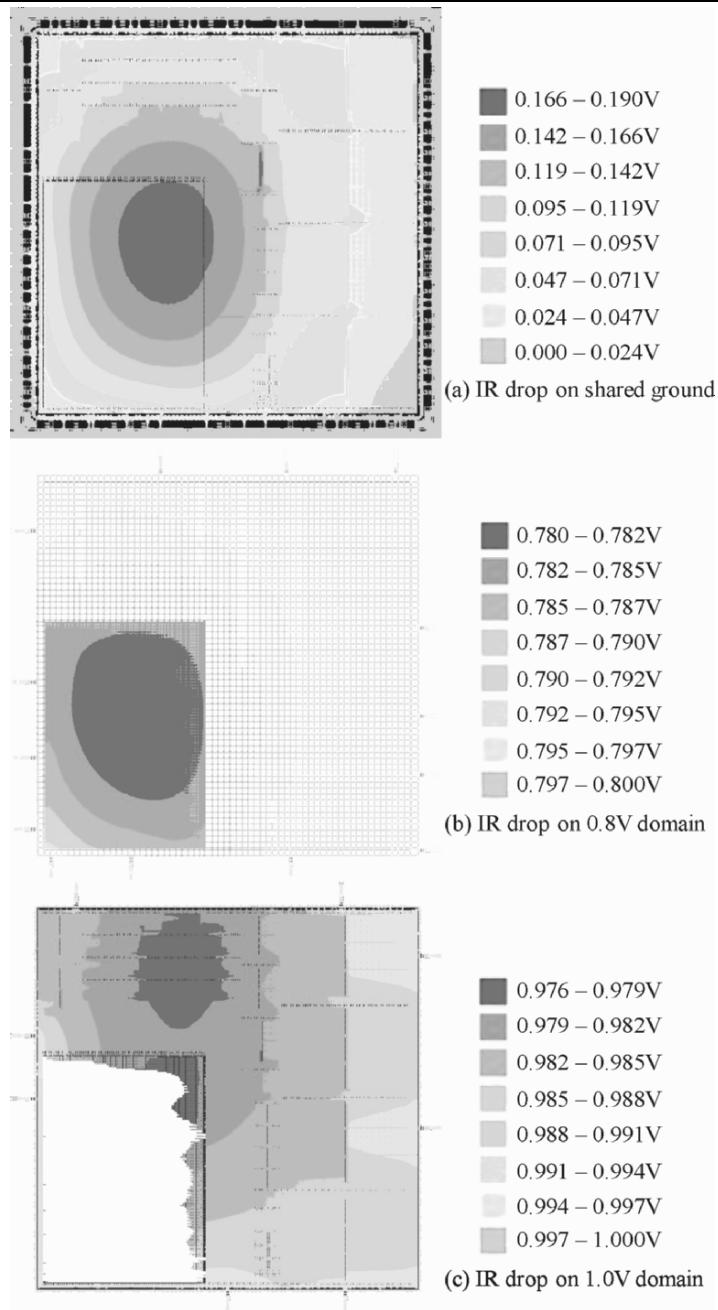

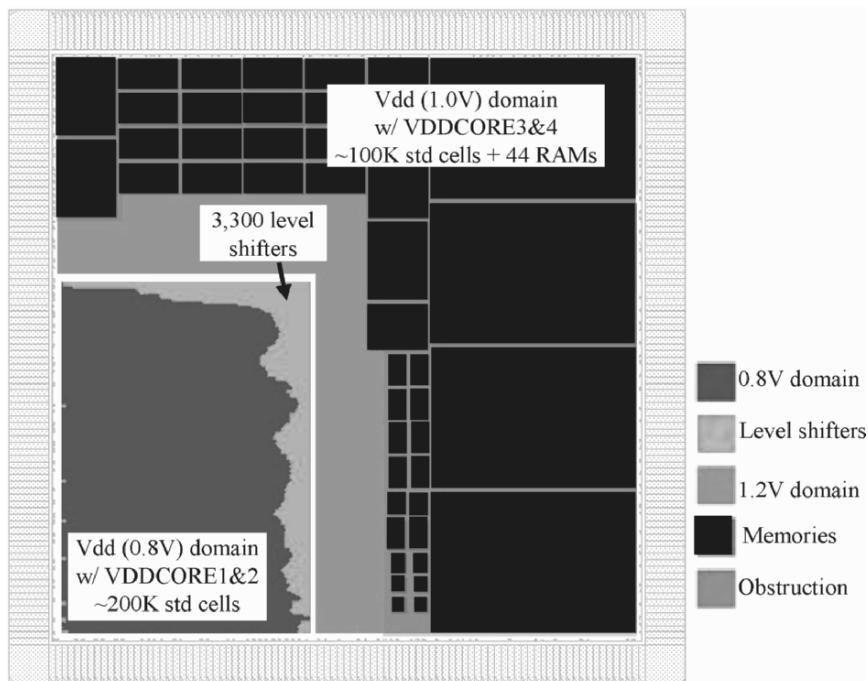

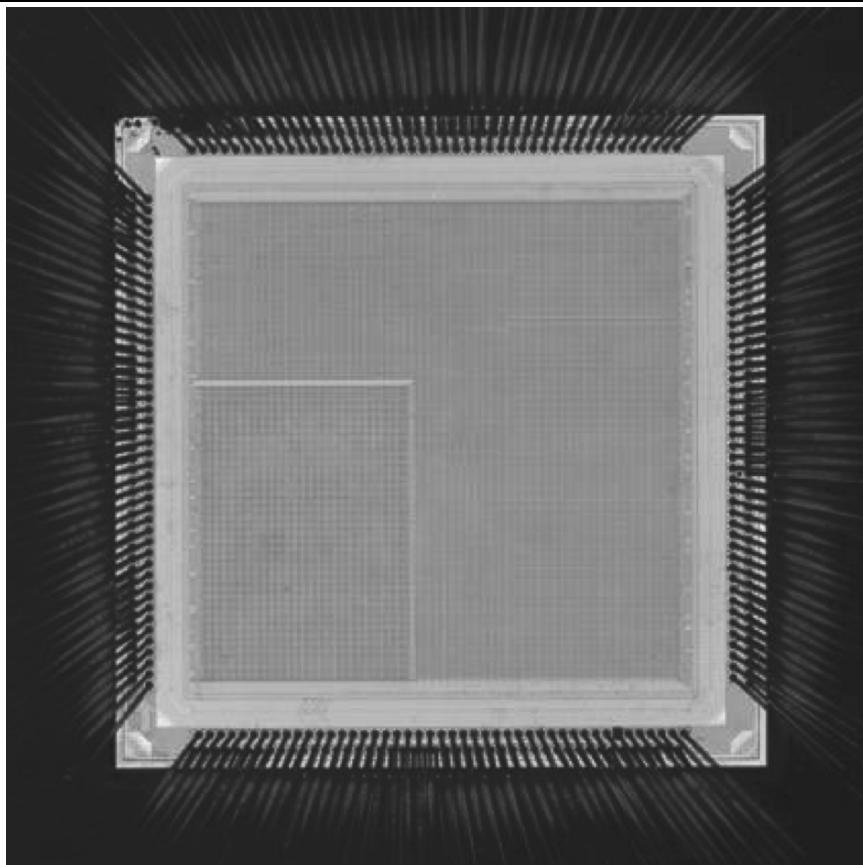

There are also verification steps to try to ensure that the final circuit that is fabricated performs correctly. These include verifying that the gate level logic corresponds to the HDL description; gate level simulation to check correct functional behavior; verifying the layout meets design rules; checking that supply and ground voltage (IR) drops are within tolerances for the standard cell library or design; cross-talk analysis to check signal interference between wires on the chip; and electromagnetic interference analysis to check signal interference with the surrounding environment.

Custom designers sometimes use an ASIC methodology, in particular for portions of the chip that are not timing critical, such as control logic. For performance-critical datapath logic, it is highly advantageous in terms of speed, power, and area to manually lay out the semi-regular logic. If their position is known, cells can have less guard banding, or input and output ports in a particular place to reduce wire lengths, and so forth. Custom design of individual cells and manual placement is laborious, increasing the time-to-market and requiring much larger design teams. Such design-specific optimizations are seldom useful on other designs except for commonly used structures such as memory, and also may not be usable if the technology for the design changes. There have been several attempts by EDA companies to sell datapath synthesis tools, but they have not been successful. It is very difficult for tools to identify the appropriate layout, as a datapath does not usually a regular structure that can be identified by a general purpose tool, though some design companies do have in-house datapath generation tools.

Using a vendor-provided standard cell library for a given fabrication process technology improves designer productivity. Lower transistor-level circuit design issues are abstracted to gate-level power and delay characteristics, and standard cells are designed robustly with guard-banding to ensure correct behavior. A library typically has several drive strengths of cells that implement a given logic function. These drive strengths correspond

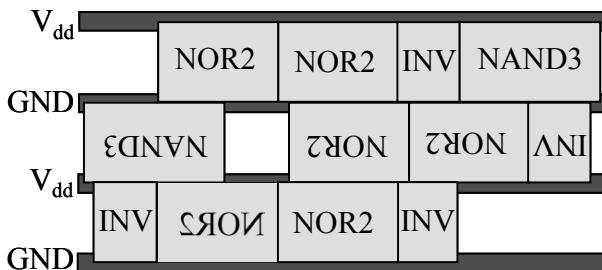

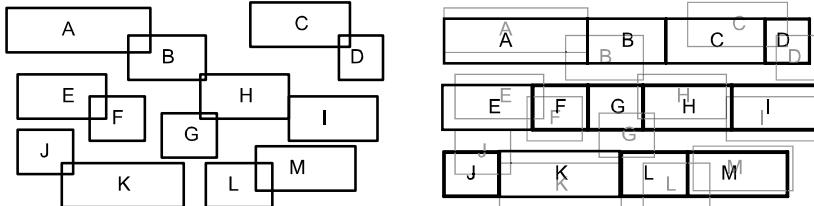

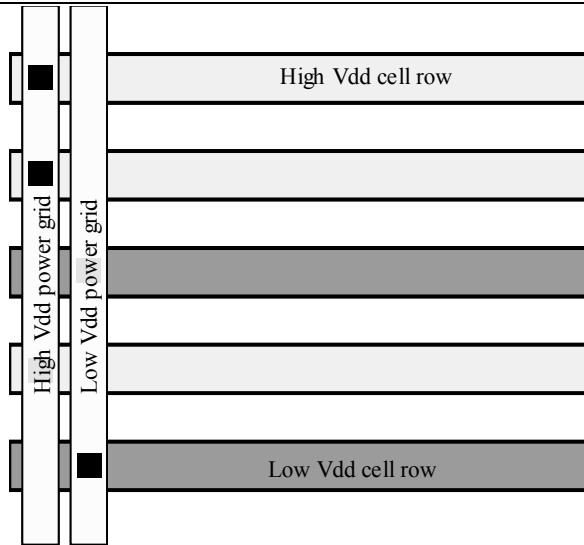

to the capacitive load that a cell can drive without excessive delay and with acceptable signal characteristics. Cell placement is simplified by using a fixed height for all the cells. Rows of cells are placed on the chip, with contiguous supply voltage ( $V_{dd}$ ) rails and ground voltage (GND) rails at the top and bottom of the rows. This makes it possible for automated placement of standard cells in the manner shown in Figure 1.2. A new standard cell library can be used by iterating an RTL design through the design flow again, which makes it much easier to migrate between process technologies.

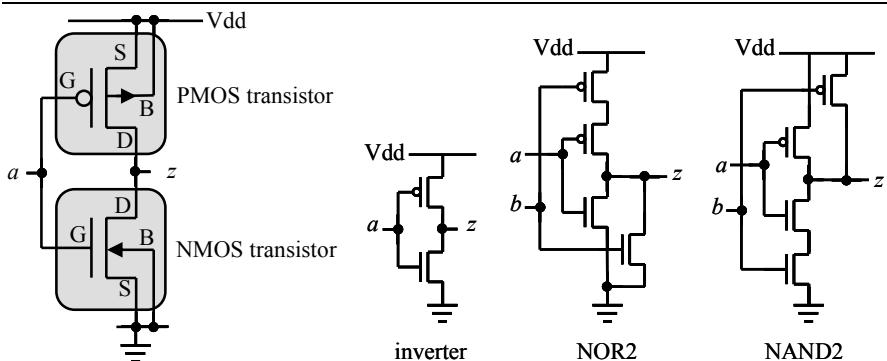

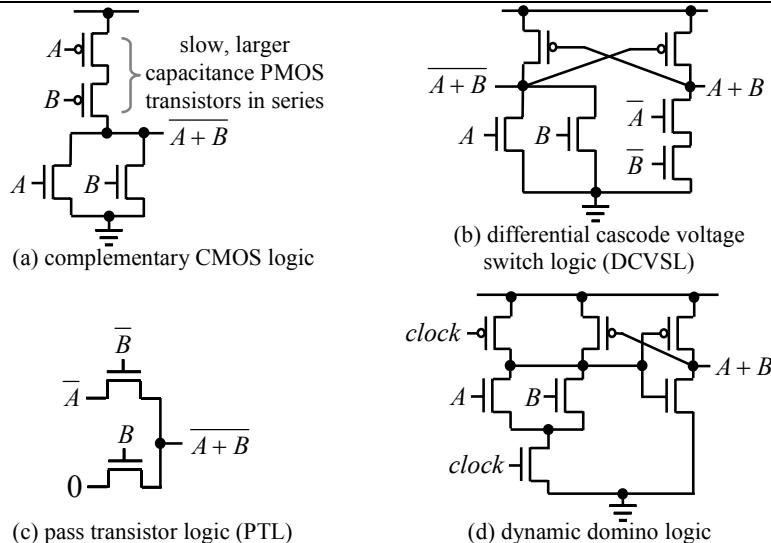

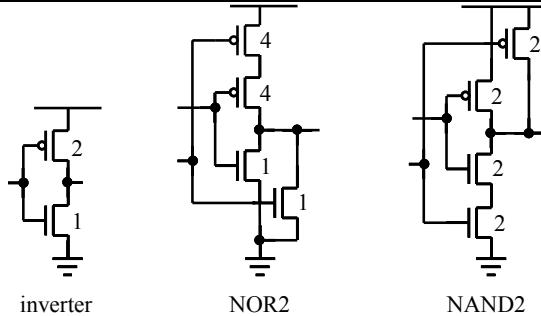

We will discuss later optimizing the drive strength of logic gates in a circuit and similar issues. Thus it is useful to briefly examine transistor-level layouts. The left of Figure 1.3 shows a detailed circuit schematic for an inverter. There is some ambiguity when we refer to a “gate”, whether it is a logic gate such as an inverter, or the transistor gate shown labeled  $G$  – this will be clarified where appropriate in the text.

Figure 1.2 Placement of standard cells on standard cell rows are shown, with cells on alternate rows rotated 180° to share power rails. Standard cell height is fixed, but width and placement along a row may vary, and cells may also be mirrored horizontally.

Figure 1.3 On the left is shown a detailed circuit schematic for an inverter. Transistor gate  $G$ , source  $S$ , drain  $D$  and bulk  $B$  (also referred to as substrate) nodes are noted. Connections to the substrate are generally omitted, in which case it is assumed that the NMOS p-well connects to ground (0V), and the PMOS n-well connects to the supply voltage ( $V_{dd}$ ). On the right are shown the circuit schematics for three logic gates.

In Figure 1.3, note that the NOR2 gate has two PMOS transistors in series in the pull-up portion, whereas the NAND2 gate has two NMOS transistors in series in the pull-down portion. The more transistors in series, the slower the logic gate is due to increased series resistance. PMOS transistors are slower than NMOS transistors, so the NOR2 is slower than a NAND2, assuming the same transistor sizes. Wider transistors may be used to reduce the delay. A typical inverter PMOS to NMOS ratio to have equal pull-up and pull-drive strengths is 2:1. To reduce the additional delay of transistors in series, for a NOR2 gate this becomes 4:1, and for a NAND2 gate this is 2:2. Skewed P to N ratios, substrate biasing, and other circuit issues will be discussed briefly in later chapters. However, increasing the transistor widths increases the power used in charging and discharging the logic gate.

This is an example of low-level power-performance trade-offs that would be considered by a custom circuit designer. To reduce the time to design a circuit, an ASIC circuit designer typically avoids such issues by using a fixed library of standard cells. It is assumed that the library has appropriate PMOS to NMOS ratios and a range of sizes for logic gates to optimally drive the circuit in different load capacitance conditions. However, this assumption is not necessarily true. Such factors may contribute to suboptimal ASIC designs. This and other power-performance trade-offs are examined in this book.

## 1.3 WHO SHOULD CARE ABOUT THIS BOOK?

### 1.3.1 ASIC and ASSP designers seeking high performance

Power consumption has become a major design constraint for high performance circuits and limits performance for high end microprocessor chips in today's technologies. Our book titled *Closing the Gap between ASIC & Custom* [1] detailed how to achieve high performance for ASICs in an EDA design flow, but we did not focus on the limitations imposed by power consumption. Some of the techniques used to achieve lower power in high performance custom designs can be automated for use in an ASIC design methodology.

While many ASIC designers may be power-budget limited when seeking higher performance, we quickly acknowledge that not all ASIC designers are seeking higher performance. Many ASIC designs need only to be cheaper than FPGAs (field programmable gate arrays) or faster than general-purpose processor solutions to be viable. For these designs, the desire for higher performance is dominated by final part cost, low non-recurring engineering cost, and time-to-market concerns. Non-recurring engineering costs for ASICs have grown substantially with increased transistor density and deep-

submicron design issues. Mask-set costs are now exceeding one million dollars. Both the number and cost of tools required to do ASIC design are rising. In order to recoup their massive investment in fabrication facilities, semiconductor vendors for ASICs are “raising the bar” for incoming ASIC designs. Specifically, ASIC semiconductor vendors are raising the minimum volumes and expected revenues required to enter into contract for fabricating ASICs. These different factors are causing more ASIC design groups to rethink their approach. Some groups are migrating to using FPGA solutions. Some groups are migrating to application-specific standard parts (ASSPs) that can be configured or programmed for their target application.

Those groups that retain their resolve to design ASICs have a few common characteristics. First, these groups aim to amortize increasing non-recurring engineering costs for ASIC designs by reusing a design across multiple applications. Thus they are no longer designing “point solution” ASICs, but are tending toward more sustainable IC *platforms* with software that can be updated as application requirements change [2]. Secondly, as transistor density increases with Moore’s law [4], more and more devices are integrated onto a single chip to reduce the net production cost. Multiple processor cores are integrated onto a chip to increase performance or allow for more programmability to achieve retargetable IC platforms. However, the power consumption also increases with more devices on a chip. Finally, given the effort and attention required to design a highly complex ASIC, design groups are demanding more out of their investment. In short, this book targets ASIC and ASSP designers seeking high-performance and low power within an automated design methodology, and we contend that this number is *increasing* over time.

### 1.3.2 ASIC and ASSP designers seeking lower power

Power consumption is of primary importance in chips designed for embedded and battery powered applications. To reduce part costs, cheap plastic packaging is preferred, which limits the maximum heat dissipation. For many applications such as mobile phones, a long battery lifetime is desirable, so low power is important. ASIC implementations are often chosen for low power, as they can be an order of magnitude or more lower power than applications implemented on an FPGA [3] or in software running on a general purpose processor.

The main approaches to reducing power consumption are scaling down supply voltage and using smaller gate sizes to reduce dynamic power, and increasing threshold voltage to reduce static leakage power; however, these techniques to reduce power also substantially slow down a circuit. Thus we focus on reducing the power gap between ASIC and custom designs subject to some performance constraint. In ASIC designs with tight performance

constraints and a tight power budget, ASIC designers must use high performance techniques to create some timing slack for power minimization.

### 1.3.3 Custom designers seeking higher productivity

An equally important audience for this book is custom designers seeking low power ICs in a design methodology that uses less human resources, such as an ASIC design methodology. Without methodological improvements, custom design teams can grow as fast as Moore's Law to design the most complex custom ICs. Even the design teams of the most commercially successful microprocessors cannot afford to grow at that rate.

We hope to serve this audience in two ways. First, we account for the relative power impact of different elements of a custom-design methodology. Projects have limited design resources and must be used judiciously. Therefore, design effort should be applied where it offers the greatest benefit. We believe that our analysis should help to determine where limited design resources are best spent.

Secondly, specific tools targeted to reduce the power of ASICs can be applied to custom design. The custom designer has always lacked adequate tool support. Electronic Design Automation (EDA) companies have never successfully found a way to tie their revenues to the revenues of the devices they help design. Instead, EDA tool vendors get their revenues from licensing design tools for each designer, known as a "design seat". It doesn't matter if the chip designed with an EDA tool sells in volumes of ten million parts or one, the revenue to the EDA company is the same. It has been estimated that there are more than ten times as many ASIC designers (50,000 – 100,000 worldwide) as custom designers (3,000 – 5,000 worldwide). As a result EDA tool vendors naturally "follow the seats" and therefore have focused on tools to support ASIC designers rather than custom designers. Companies using custom design augment tools from EDA vendors with their own in-house tools. These in-house tools can be improved by identifying where gaps exist in the standard approaches that have been used for circuit design, or replaced in cases where EDA tools perform sufficiently well.

## 1.4 ORGANIZATION OF THE REST OF THE BOOK

This book examines the power gap between ASIC and custom design methodologies, techniques to reduce the power gap, and design examples illustrating these techniques. The remaining chapters in this book are organized into these three groups.

The first set of chapters discusses the contributing factors to power consumption in ASICs being larger than in custom designs, with power and performance models. The power gap is estimated in Chapter 2, then we

provide a detailed overview of the contributing factors, and discuss the design difficulties associated with exploiting these methods in an automated design flow and the extent to which they may be automated. A high-level pipeline power-performance model is combined with a low-level model of gate sizing and voltage scaling power-delay trade-offs in Chapter 3. This enables estimates of the benefit of using microarchitectural techniques to provide timing slack for power minimization at later design stages, and quantitative analysis of the influence of different design factors. Chapter 4 compares analytical and empirical models of circuit power and delay with voltage scaling, discussing the dynamic power, leakage power and delay trade-offs with gate sizing and optimization of supply and threshold voltages.

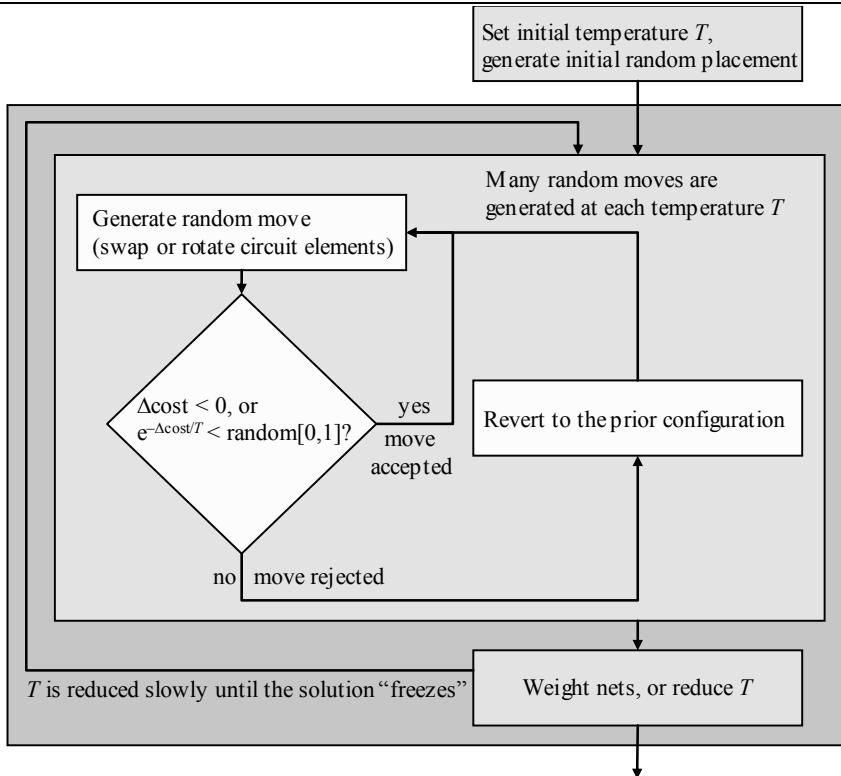

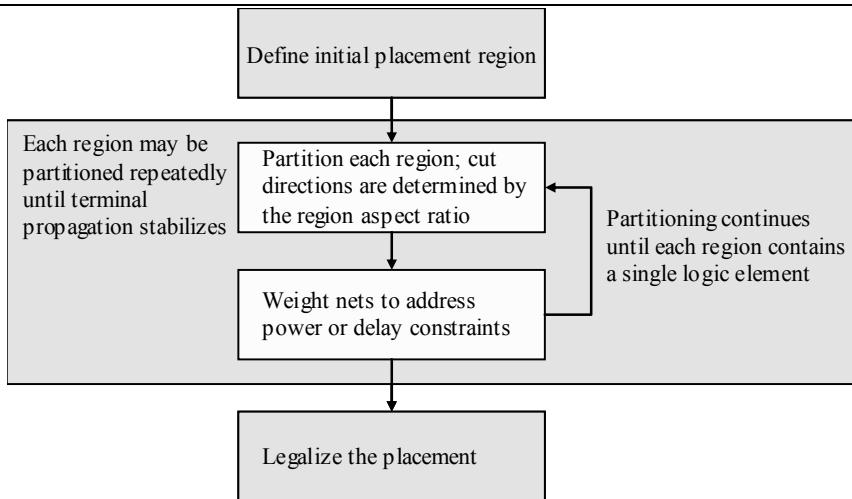

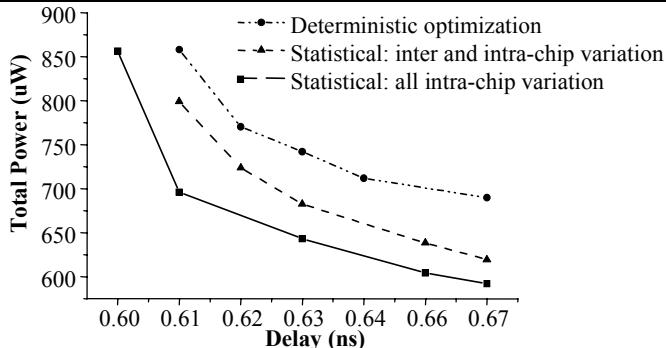

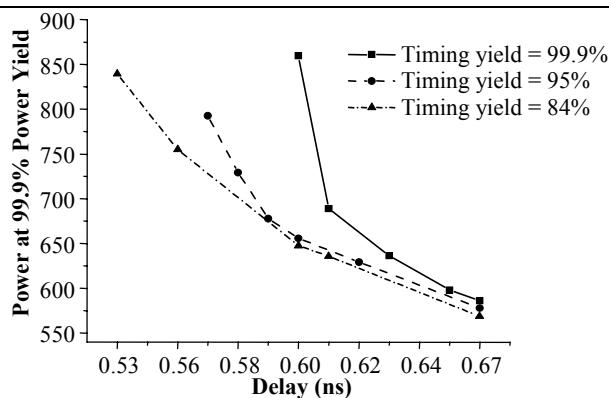

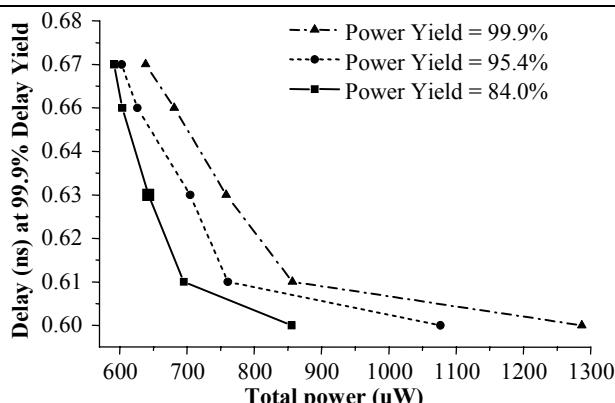

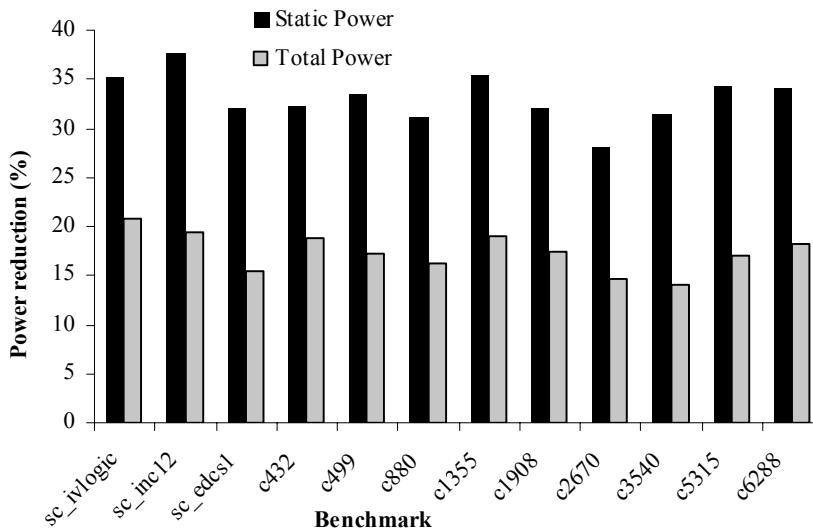

The second group of chapters details a variety of design techniques and tools to help minimize power consumption. Chapter 5 gives examples of microarchitectural optimizations that can increase energy efficiency by more than  $10\times$  for specific applications. Chapter 6 shows that the typical greedy heuristics for gate sizing are suboptimal, and that a linear programming formulation with a global circuit can provide greater power reductions. The linear programming approach is applied to gate-level supply and threshold voltage assignment in Chapter 7 to analyze how much power may be saved by using these approaches. Alternative algorithms for supply voltage assignment are examined in Chapter 8. Chapter 9 details improved tools for automated placement and discusses the placement issues when using multiple supply voltages. Results for reducing leakage power with an automated tool for power gating are presented in Chapter 10. Design verification issues and verification tool support needed for use of multiple voltage and sleep domains are examined in Chapter 11. Then Chapter 12 details power minimization with statistical timing and power analysis.

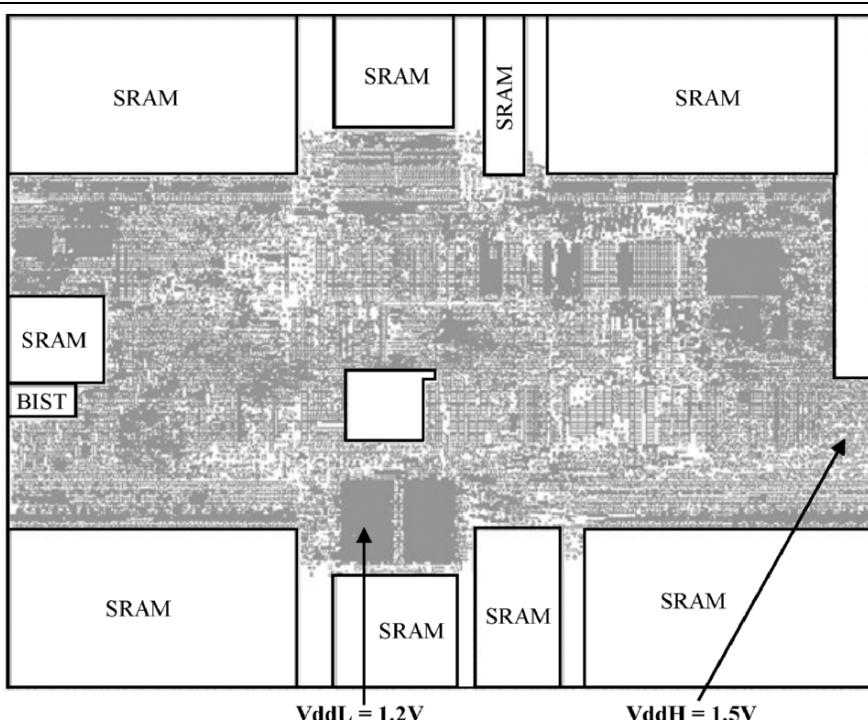

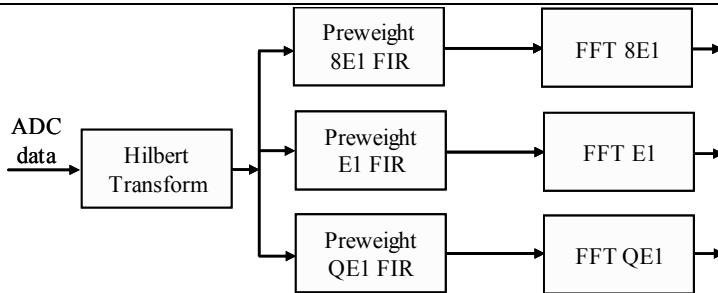

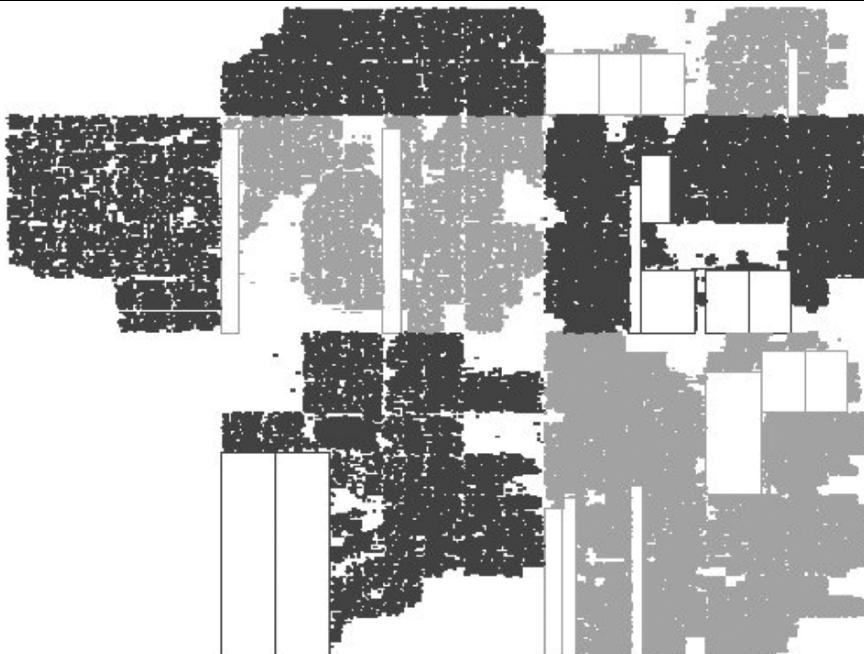

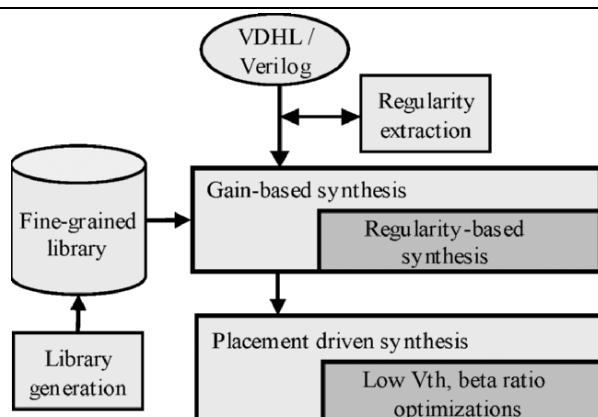

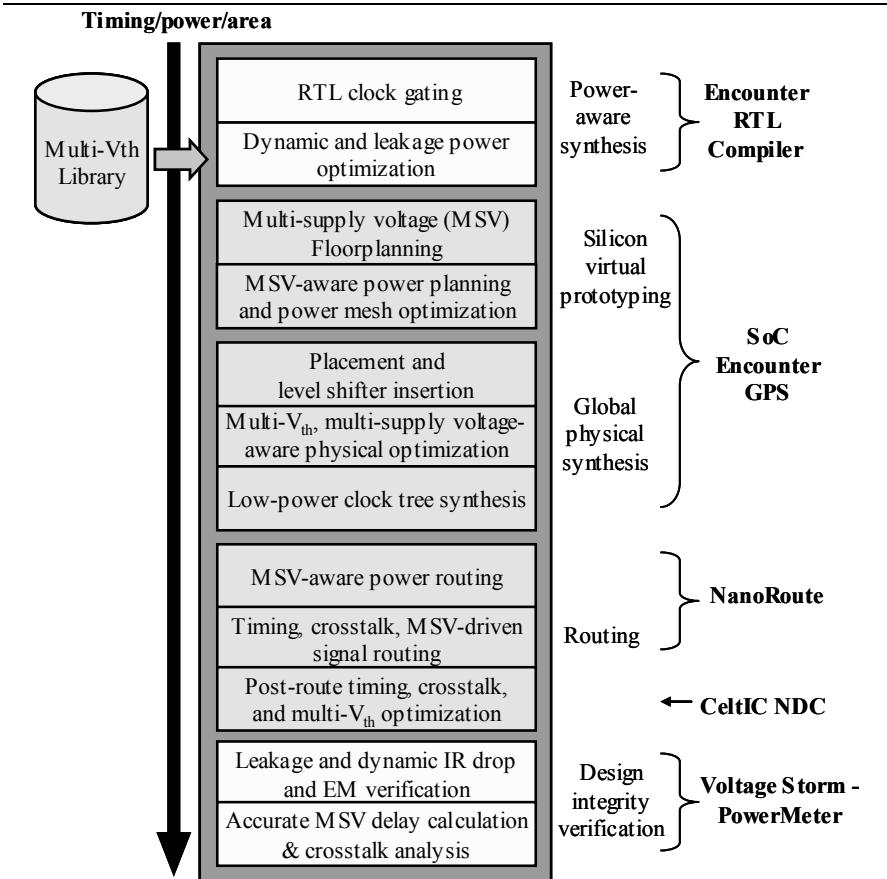

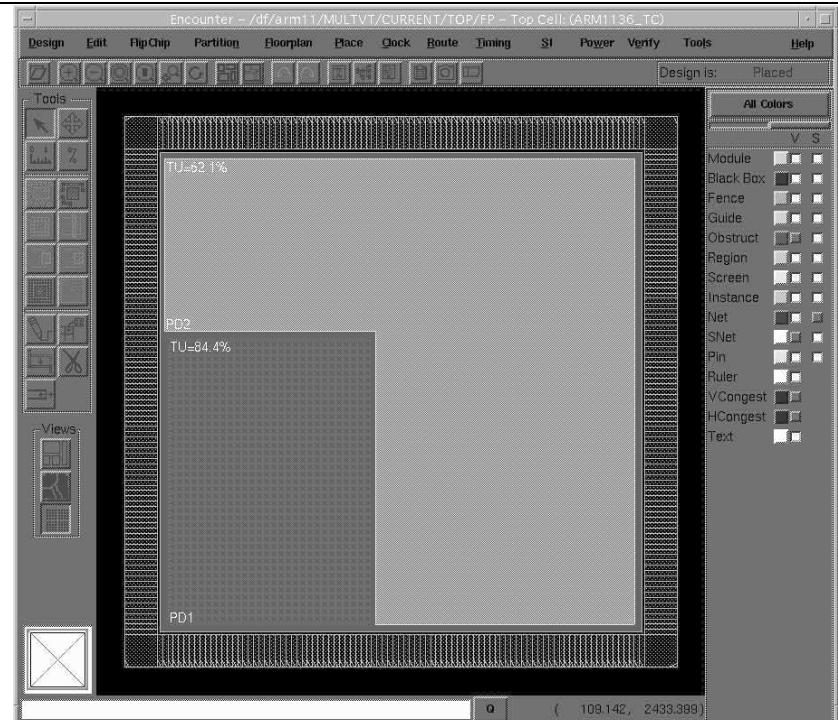

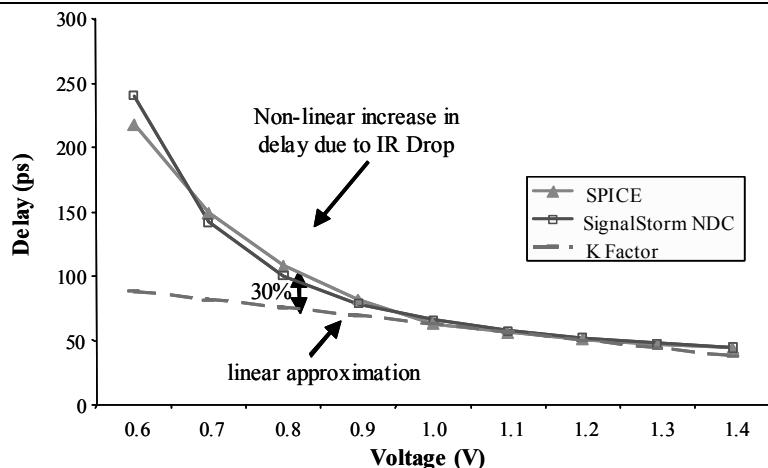

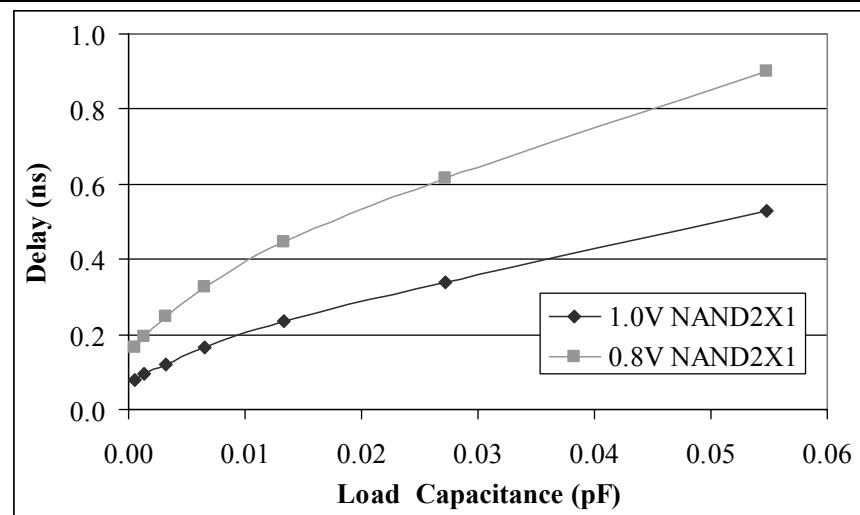

The last set of chapters presents two design examples utilizing low power techniques. Chapter 13 reports the power savings achieved with standard cell library improvements, arithmetic optimizations, bit slicing, and voltage scaling on DSP (digital signal processor) blocks for a satellite communications chip. Chapter 14 presents a low power design flow that was used to minimize power consumption of an ARM 1136JF-S processor, utilizing multiple supply and threshold voltages. These design examples show that using the low power techniques discussed in this book can provide increased energy efficiency by a factor of 2 to  $3\times$ .

## 1.5 WHAT'S NOT IN THIS BOOK

This book focuses on power consumption of integrated circuits and the tools and techniques by which lower power can be achieved. ASIC and custom performance and approaches to increase circuit speed were discussed extensively in our book on the topic [1]. Other than in the context of place

and route tools in Chapter 11, area minimization is not a direct focus, as that is a less critical design constraint compared to speed and power in today's technologies that allow billions of transistors on a chip. Where the power minimization techniques that we suggest here negatively impact on circuit delay or area we have made every effort to point that out.

## 1.6 REFERENCES

- [1] Chinnery, D., and Keutzer, K., *Closing the Gap Between ASIC & Custom: Tools and Techniques for High-Performance ASIC Design*, Kluwer Academic Publishers, 2002, 432 pp.

- [2] Keutzer, K. et al., "System-level Design: Orthogonalization of Concerns and Platform-Based Design," *IEEE Transactions on Computer-Aided Design*, vol. 19, no. 12, December 2000, pp. 1523-1543.

- [3] Kuon, I., and Rose, J., "Measuring the Gap Between FPGAs and ASICs," *International Symposium on Field Programmable Gate Arrays*, 2006, pp. 21-30.

- [4] Moore, G., "Cramming more components onto integrated circuits," *Electronics*, vol. 38, no. 8, 1965, pp. 114-117.

- [5] Smith, D., *HDL Chip Design: A Practical Guide for Designing, Synthesizing and Simulating ASICs and FPGAs Using VHDL or Verilog*, Doone Publications, 1998, 464 pp.

- [6] Smith, M., *Application-specific Integrated Circuits*, Addison-Wesley, Berkeley, CA, 1997.

## Chapter 2

# OVERVIEW OF THE FACTORS AFFECTING THE POWER CONSUMPTION

David Chinnery, Kurt Keutzer

*Department of Electrical Engineering and Computer Sciences*

*University of California at Berkeley*

*Berkeley, CA 94720, USA*

We investigate differences in power between application-specific integrated circuits (ASICs) and custom integrated circuits, with examples from 0.6um to 0.13um CMOS. A variety of factors cause synthesizable designs to consume 3 to 7 $\times$  more power. We discuss the shortcomings of typical synthesis flows, and changes to tools and standard cell libraries needed to reduce power. Using these methods, we believe that the power gap between ASICs and custom circuits can be closed to within 2.6 $\times$  at a tight performance constraint for a typical ASIC design.

### 2.1 INTRODUCTION

In the same technology generation, custom designs can achieve 3 to 8 $\times$  higher clock frequency than ASICs [18]. Custom techniques that are used to achieve high speed can also be used to achieve low power [62]. Custom designers can optimize the individual logic cells, the layout and wiring between the cells, and other aspects of the design. In contrast, ASIC designers generally focus on optimization at the RTL level, relying on EDA tools to map RTL to cells in a standard cell library and then automatically place and route the design. Automation reduces the design time, but the resulting circuitry may not be optimal.

Low power consumption is essential for embedded applications. Power affects battery life and the heat dissipated by hand-held applications must be limited. Passive cooling is often required, as using a heat sink and/or fan is larger and more expensive.

Power is also becoming a design constraint for high-end applications due to reliability, and costs for electricity usage and cooling. As technology scales, power density has increased with transistor density, and leakage power is

becoming a significant issue even for high end processors. Power consumption is now a major problem even for high end microprocessors. Intel canceled the next generation Tejas Pentium 4 chips due to power consumption issues [100].

In this chapter, we will discuss the impact of manual and automated design on the power consumption, and also the impact of process technology and process variation. Our aim is to quantify the influence of individual design factors on the power gap. Thus, we begin by discussing a process technology independent delay metric in Section 2.2. Section 2.3 discusses the contribution to a chip’s power consumption from memory, control and datapath logic, and clocking, and also provides an overview of dynamic and leakage power.

In Section 2.4, we compare full custom and synthesizable ARM processors and a digital signal processor (DSP) functional unit. We show that ASICs range from 3 to 7× higher power than custom designs for a similar performance target. To date the contribution of various factors to this gap has been unclear. While automated design flows are often blamed for poor performance and poor energy efficiency, process technology is also significant. Section 2.5 outlines factors contributing to the power gap. We then examine each factor, describing the differences between custom and ASIC design methodologies, and account for its impact on the power gap. Finally, we detail approaches that can reduce this power gap. We summarize our analysis in Section 2.6.

## 2.2 PROCESS TECHNOLOGY INDEPENDENT FO4 DELAY METRIC

At times we will discuss delay in terms of FO4 delays. It is a useful metric for normalizing out process technology dependent scaling of the delay of circuit elements.

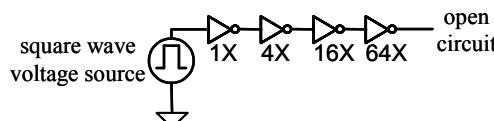

The fanout-of-4 inverter delay is the delay of an inverter driving a load capacitance that has four times the inverter’s input capacitance [38]. This is shown in Figure 2.1. The FO4 metric is not substantially changed by process technology or operating conditions. In terms of FO4 delays, other fanout-of-4 gates have at most 30% range in delay over a wide variety of process and operating conditions, for both static logic and domino logic [38].

If it has not been simulated in SPICE or tested silicon, the FO4 delay in a given process technology can be estimated from the channel length. Based on the effective gate length  $L_{eff}$ , the rule of thumb for FO4 delay is [39].

$$360 \times L_{eff} \text{ ps for typical operating and typical process conditions} \quad (2.1)$$

$$500 \times L_{eff} \text{ ps for worst case operating and typical process conditions} \quad (2.2)$$

where the effective gate length  $L_{eff}$  has units of micrometers. Typical process conditions give high yield, but are not overly pessimistic. Worst case operating conditions are lower supply voltage and higher temperature than typical operating conditions. Typical operating conditions for ASICs may assume a temperature of 25°C, which is optimistic for most applications. Equation (2.2) can be used to estimate the FO4 delay in silicon for realistic operating conditions [39].

$L_{eff}$  is often assumed to be about 0.7 of the drawn gate length for a process technology – for example, 0.13um for a 0.18um process technology. However, many foundries are aggressively scaling the channel length to increase the speed. Thus, the FO4 delay should be calculated from the effective gate length, if it is known, rather than from the process technology generation.

From previous analysis [18], typical process conditions are between 17% and 28% faster than worst case process conditions. Derating worst case process conditions by a factor of 1.2× gives

$$600 \times L_{eff} \text{ ps for worst case operating and worst case process conditions (2.3)}$$

Equation (2.3) was used for estimating the FO4 delays of synthesized ASICs, which have been characterized for worst case operating and worst case process conditions. This allows analysis of the delay per pipeline stage, independent of the process technology, and independent of the process and operating conditions.

**Note:** these rules of thumb give approximate values for the FO4 delay in a technology. They may be inaccurate by as much as 50% compared to simulated or measured FO4 delays in silicon. These equations do not accurately account for operating conditions. Speed-binning and process improvements that do not affect the effective channel length are not accounted for. Accurate analysis with FO4 delays requires proper calibration of the metric: simulating or measuring the actual FO4 delays for the given process and operating conditions.

Figure 2.1 This illustrates a circuit to measure FO4 delays. The delay of the 4X drive strength inverter gives the FO4 delay. The other inverters are required to appropriately shape the input waveform to the 4X inverter and reduce the switching time of the 16X inverter, which affect the delay of the 4X inverter [38].

## 2.3 COMPONENTS OF POWER CONSUMPTION

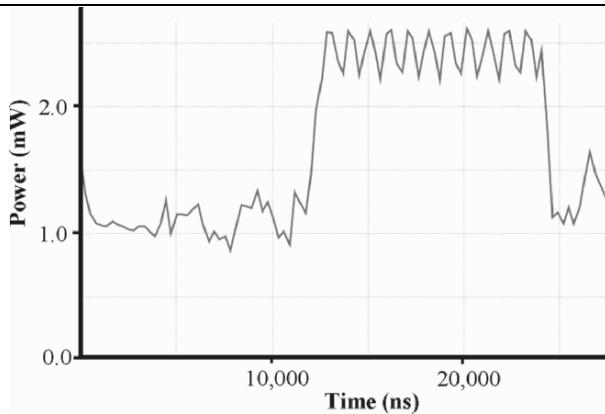

Designers typically focus on reducing both the total power when a circuit is active and its standby power. There is usually a minimum performance target, for example 30 frames/s for MPEG. When performance is less important, the energy per operation to perform a given task can be minimized.

Active power includes both dynamic power consumption, when the logic evaluates or the clock transitions, and current leakage when logic is not switching. There is no computation in logic in standby, the clock must be gated to prevent it switching, and leakage is the dominant source of power consumption in standby.

The major sources of power consumption in circuitry are the clock tree and registers, control and datapath logic, and memory. The breakdown of power consumption between these is very application and design dependent. The power consumption of the clock tree and registers ranged from 18% to 36% of the total power for some typical embedded processors and microprocessors (see Section 3.2.4). In custom cores for discrete cosine transform (DCT) and its inverse (IDCT), contributions to the total power were 5% to 10% from control logic, about 40% from the clock tree and clock buffers, and about 40% from datapath logic [101][102]. Memory can also account for a substantial portion of the power consumption. For example, in the StrongARM caches consume 43% of the power [62].

### 2.3.1 Dynamic power

Dynamic power is due to switching capacitances and short circuit power when there is a current path from supply to ground.

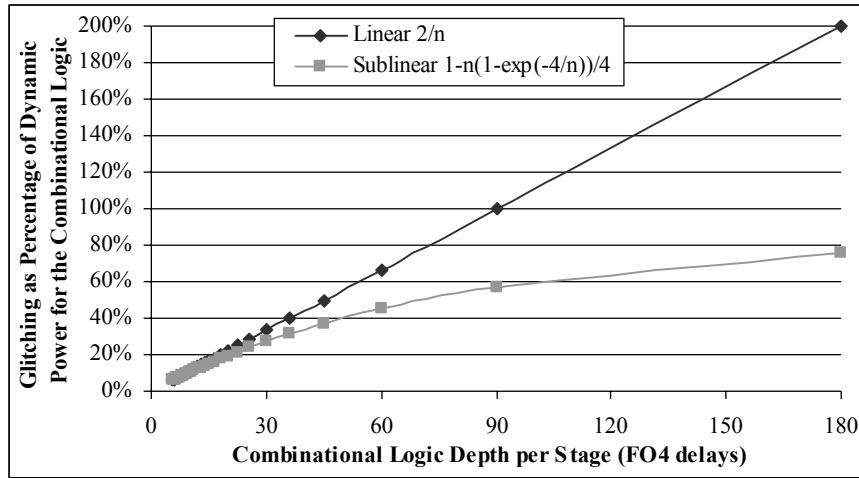

The switching power is proportional to  $\alpha f C V_{dd}^2$ , where  $\alpha$  is the switching activity per clock cycle,  $f$  is the clock frequency,  $C$  is the capacitance that is (dis)charged, and  $V_{dd}$  is the voltage swing. The switching activity is increased by glitches, which typically cause 15% to 20% of the activity in complementary static CMOS logic [77].

Short circuit power typically contributes less than 10% of the total dynamic power [14], and increases with increasing  $V_{dd}$ , and with decreasing  $V_{th}$ . Short circuit power can be reduced by matching input and output rise and fall times [96].

As the dynamic power depends quadratically on  $V_{dd}$ , methods for reducing active power often focus on reducing  $V_{dd}$ . Reducing the capacitance by downsizing gates and reducing wire lengths is also important.

### 2.3.2 Leakage power

In today's processes, leakage can account for 10% to 30% of the total power when a chip is active. Leakage can contribute a large portion of the average power consumption for low performance applications, particularly when a chip has long idle modes without being fully off.

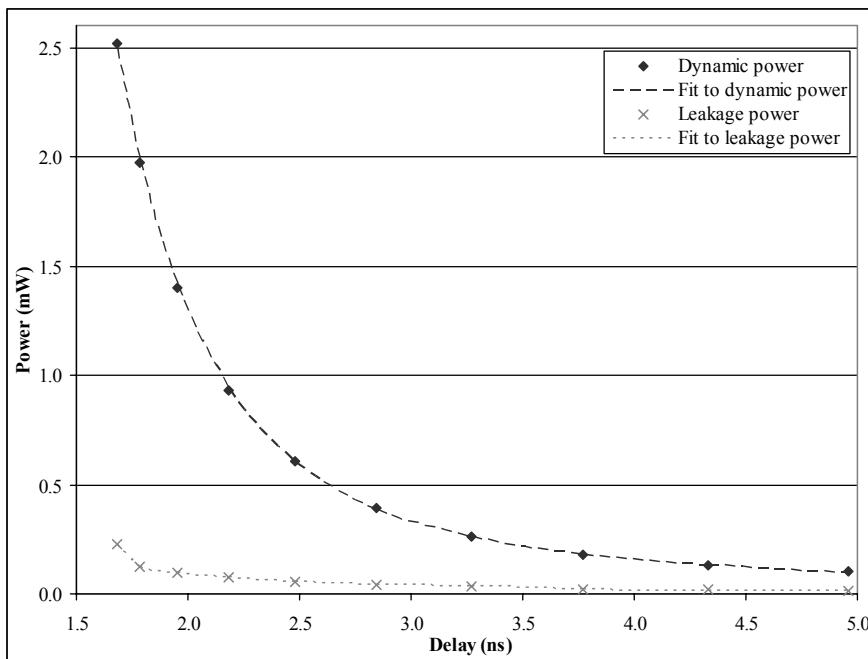

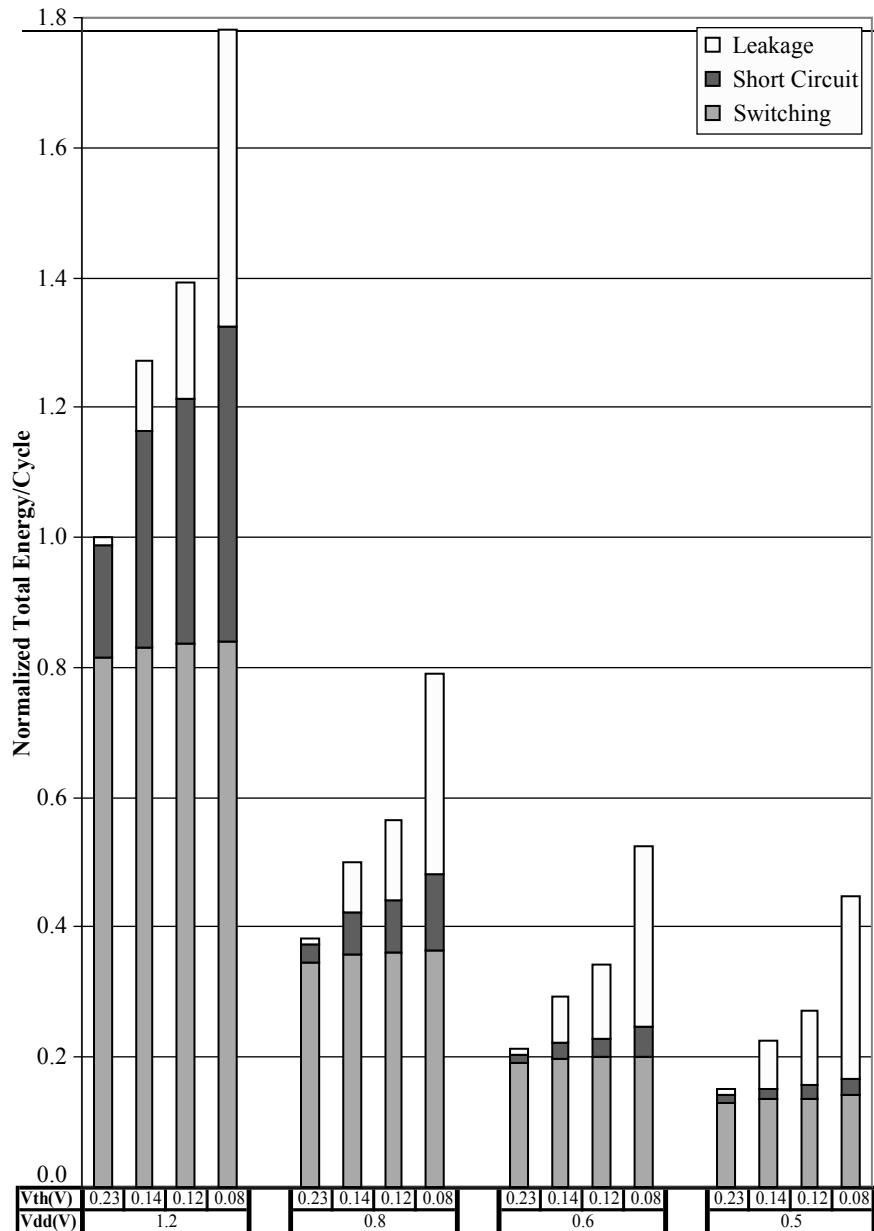

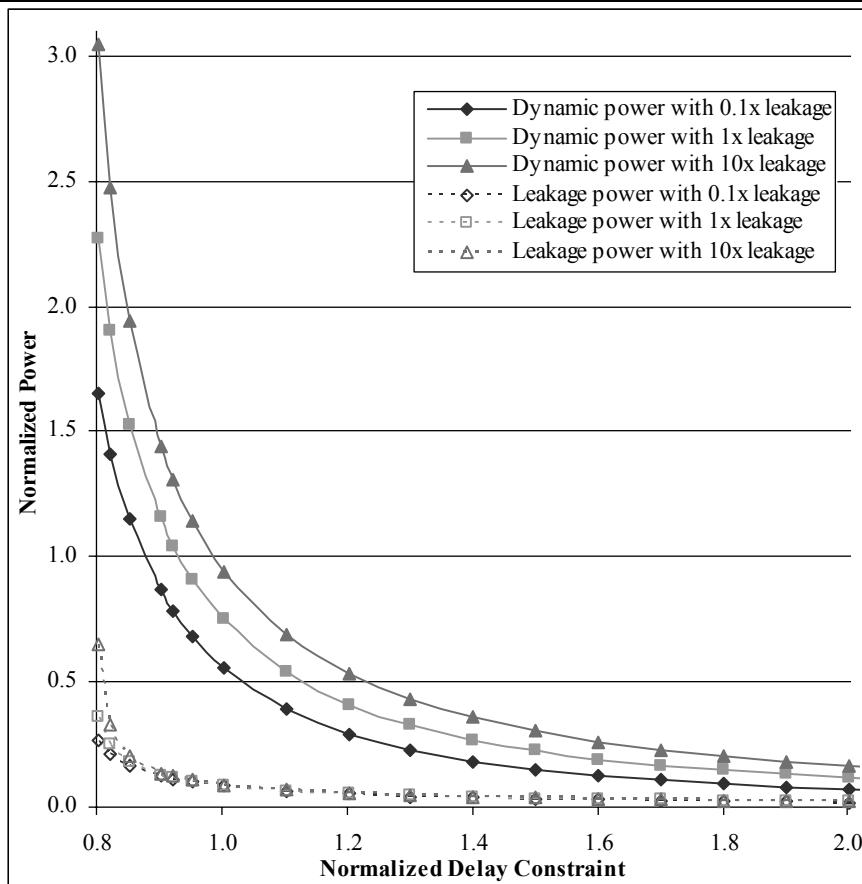

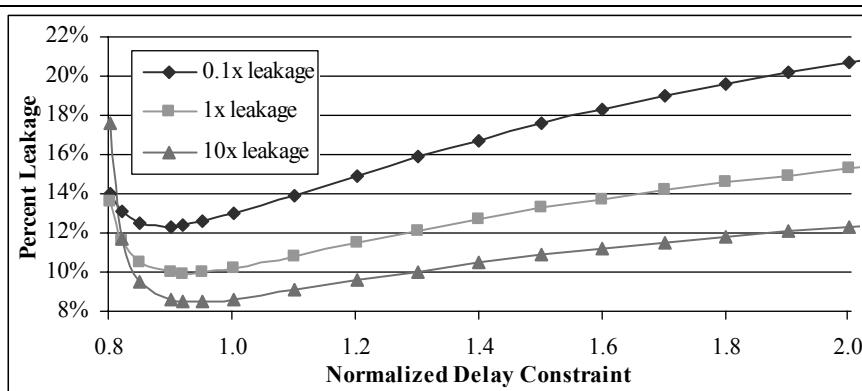

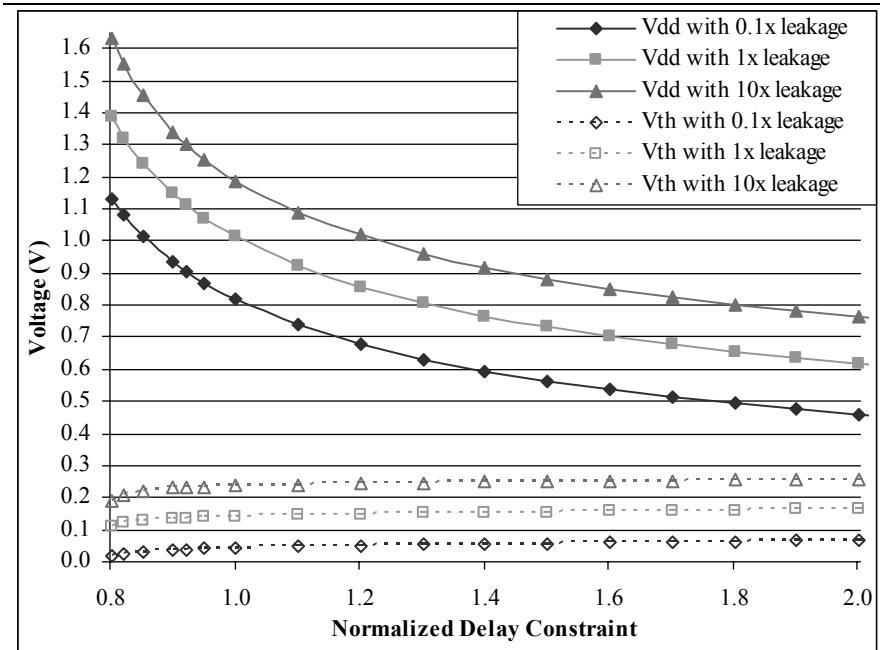

Optimally choosing Vdd and Vth to minimize the total power consumption for a range of delay constraints in 0.13um technology, the leakage varied from 8% to 21% of the total power consumption in combinational logic, as discussed later in Section 4.6.1. However, the possible Vdd and Vth values depend on the particular process technology and standard cell libraries available. For example for a delay constraint of  $1.2 \times$  the minimum delay, the best library choice had Vdd of 0.8V and Vth of 0.08V (see Table 7.7 with 0.8V input drivers), and leakage contributed on average 40% of total power.

Leakage power in complementary static CMOS logic in bulk CMOS is primarily due to subthreshold leakage and gate leakage. Subthreshold leakage increases exponentially with decrease in Vth and increase in temperature. It can also be strongly dependent on transistor channel length in short channel devices. Gate leakage has increased exponentially with reduction in gate oxide thickness. There is also substrate leakage. Leakage has become increasingly significant in deep submicron process technologies.

## 2.4 ASIC AND CUSTOM POWER COMPARISON

To illustrate the power gap, we examine custom and ASIC implementations of ARM processors and dedicated hardware to implement discrete cosine transform (DCT) and its inverse (IDCT). ARM processors are general purpose processors for embedded applications. ASICs often have dedicated functional blocks to achieve low power and high performance on specific applications – for example, media processing. JPEG and MPEG compression and decompression of pictures and video use DCT and IDCT. There is a similar power gap between ASIC and custom for the ARM processors and for DCT and IDCT blocks.

### 2.4.1 ARM processors from 0.6 to 0.13um

We compare chips with full custom ARM processors, soft, and hard ARM cores. Soft macros of RTL code may be sold as individual IP (intellectual property) blocks and are portable between fabrication processes. In a hard macro, the standard cell logic used, layout and wiring have been specified and optimized then fixed for a particular fabrication process. A hard macro may be custom, or it may be “hardened” from a soft core. A complete chip includes additional memory, I/O logic, and so forth.

Table 2.1 Full custom and hard macro ARMs [11][31][32][43][70]. The highlighted full custom chips have 2 to 3 $\times$  MIPS/mW.

| Processor | Technology (um) | Voltage (V) | Frequency (MHz) | MIPS | Power (mW) | MIPS/mW |

|-----------|-----------------|-------------|-----------------|------|------------|---------|

| ARM710    | 0.60            | 5.0         | 40              | 36   | 424        | 0.08    |

| Burd      | 0.60            | 1.2         | 5               | 6    | 3          | 1.85    |

| Burd      | 0.60            | 3.8         | 80              | 85   | 476        | 0.18    |

| ARM810    | 0.50            | 3.3         | 72              | 86   | 500        | 0.17    |

| ARM910T   | 0.35            | 3.3         | 120             | 133  | 600        | 0.22    |

| StrongARM | 0.35            | 1.5         | 175             | 210  | 334        | 0.63    |

| StrongARM | 0.35            | 2.0         | 233             | 360  | 950        | 0.38    |

| ARM920T   | 0.25            | 2.5         | 200             | 220  | 560        | 0.39    |

| ARM1020E  | 0.18            | 1.5         | 400             | 500  | 400        | 1.25    |

| XScale    | 0.18            | 1.0         | 400             | 510  | 150        | 3.40    |

| XScale    | 0.18            | 1.8         | 1000            | 1250 | 1600       | 0.78    |

| ARM1020E  | 0.13            | 1.1         | 400             | 500  | 240        | 2.08    |

Table 2.2 The highlighted ARM7TDMI hard macros have 1.3 to 1.4 $\times$  MIPS/mW versus the synthesizable ARM7TDMI-S cores [5].

| ARM Core   | Technology (um) | Frequency (MHz) | Power (mW) | MIPS/mW |

|------------|-----------------|-----------------|------------|---------|

| ARM7TDMI   | 0.25            | 66              | 51         | 1.17    |

| ARM7TDMI-S | 0.25            | 60              | 66         | 0.83    |

| ARM7TDMI   | 0.18            | 100             | 30         | 3.00    |

| ARM7TDMI-S | 0.18            | 90              | 35         | 2.28    |

| ARM7TDMI   | 0.13            | 130             | 10         | 11.06   |

| ARM7TDMI-S | 0.13            | 120             | 13         | 8.33    |

To quantify the power gap between ASIC and custom, we first examined hard macro and full custom ARMs, listed in Table 2.1. Compared to the other designs, the three full custom chips in bold achieved 2 to 3 $\times$  millions of instructions per second per milliwatt (MIPS/mW) at similar MIPS, as shown in Figure 2.2. The inverse of this metric, mW/MIPS, is the energy per operation. The Dhrystone 2.1 MIPS benchmark is the performance metric [98]. It fits in the cache of these designs, so there are no performance hits for cache misses or additional power to read off-chip memory.

Lower power was achieved in several ways. The DEC StrongARM used clock-gating and cache sub-banking to substantially reduce the dynamic power [62]. The Intel XScale and DEC StrongARM used high speed logic styles to reduce critical path delay, at the price of higher power consumption on these paths. To reduce pipeline register delay, the StrongARM used pulse-triggered flip-flops [62] and the XScale used clock pulsed latches [22]. Shorter critical paths allow the same performance to be achieved with a lower supply voltage (Vdd), which can lower the total power consumption. Longer channel lengths were used in the StrongARM caches to reduce the

leakage power, as the two 16kB caches occupy 90% of the chip area [62]. The XScale used substrate biasing to reduce the leakage [24].

For the same technology and similar performance (MIPS), the Vdd of the full custom chips is lower than that of the hard macros – reducing Vdd gives a quadratic reduction in dynamic power. The StrongARM can operate at up to 233MHz at 2.0V and the XScale can operate at up to 1GHz at 1.65V [43]. If operating at higher performance was not required, it is likely that even higher MIPS/mW could have been achieved.

Energy efficiency can be improved substantially if performance is sacrificed. Burd's 0.6um ARM8 had software controlled dynamic voltage scaling based on the processor load. It scaled from 0.18MIPS/mW at 80MHz and 3.8V, to 2.14MIPS/mW at 5MHz and 1.2V [11]. Voltage scaling increased the energy efficiency by 1.1 $\times$  for MPEG decompression which required an average clock frequency of 50MHz, and increased the energy efficiency by 4.5 $\times$  for audio processing which required a clock frequency of only 17MHz [12].

There is an additional factor of 1.3 to 1.4 $\times$  between hard macro and synthesizable ARM7 soft cores, as shown in Table 2.2. These MIPS/mW are higher than those in Table 2.1, as they exclude caches and other essential units. The ARM7TDMI cores are also lower performance, and thus can achieve higher energy efficiency.

Overall, there is a factor of 3 to 4 $\times$  between synthesizable ARMs and the best full custom ARM implementations.

Figure 2.2 This graph compares MIPS/mW of custom and hard macro ARMs in Table 2.1.

### 2.4.1.1 Other full custom ARM implementations

There are two other noteworthy higher performance full custom ARMs, though they are less energy efficient than the 0.18um XScale.

Samsung's Halla is a full custom 0.13um implementation of the ARM1020E with power consumption from 0.26W at 400MHz and Vdd of 0.7V to 1.8W at 1200MHz and Vdd of 1.1V [50]. Achieving 1480MIPS at 1200MHz clock frequency, the energy efficiency ranged from 0.82MIPS/mW at 1200MHz to 1.90MIPS/mW at 400MHz. Differential cascode voltage switch logic (DCVSL) was used for high performance, but DCVSL has substantial power consumption compared to complementary static CMOS logic that is used in ASICs. Sense amplifiers were used with the low voltage swing dual rail bus to detect voltage swings of less than 200mV, achieving high bus speeds at lower power consumption [60]. The die area of the Halla was 74% more than ARM's 0.13um ARM1020E.

Intel's 90nm implementation of the XScale, codenamed Monahans, has 770mW dynamic power consumption at 1500MHz and Vdd of 1.5V with performance of 1200MIPS at this point [72]. The energy efficiency of Monahans is 1.56MIPS/mW at 1500MHz – data for improved energy efficiencies at lower Vdd has not been published. Clock pulsed latches were also used in this implementation of the XScale. The hold time for the clock gating enable signal was the duration of the clock pulse, and thus did not require latching. Domino logic was used for high performance in the shifter and cache tag NOR comparators. 75% of instruction cache tag accesses were avoided by checking if the instruction cache request line was the same as the previous one. Selective accesses and avoiding repeated accesses reduced power by 42% in the dynamic memory management unit [21].

### 2.4.2 Comparison of DCT/IDCT cores

Application-specific circuits can reduce power by an order of magnitude compared to using general purpose hardware [77]. Two 0.18um ARM9 cores were required to decode 30 frames/s for MPEG2, consuming 15× the power of a synthesizable DCT/IDCT design [28]. However, the synthesizable DCT/IDCT significantly lags its custom counterparts in energy efficiency.

Table 2.3 Comparison of ASIC and custom DCT/IDCT core power consumption at 30 frames/s for MPEG2 [28][101][102].

| Design      | Technology (um)            | Voltage (V) | DCT (mW) | IDCT (mW) |

|-------------|----------------------------|-------------|----------|-----------|

| ASIC        | 0.18                       | 1.60        | 8.70     | 7.20      |

| custom DCT  | 0.6 (L <sub>eff</sub> 0.6) | 1.56        | 4.38     |           |

| custom IDCT | 0.7 (L <sub>eff</sub> 0.5) | 1.32        |          | 4.65      |

Fanucci and Saponara designed a low power synthesizable DCT/IDCT core, using similar techniques to prior custom designs. Despite being three technology generations ahead, the synthesizable core was 1.5 to 2.0 $\times$  higher power [28]. Accounting for the technology difference by conservatively assuming power scales linearly with device dimensions [71], the gap is a factor of 4.3 to 6.6 $\times$ . The data is shown in Table 2.3.

## 2.5 FACTORS CONTRIBUTING TO ASICS BEING HIGHER POWER

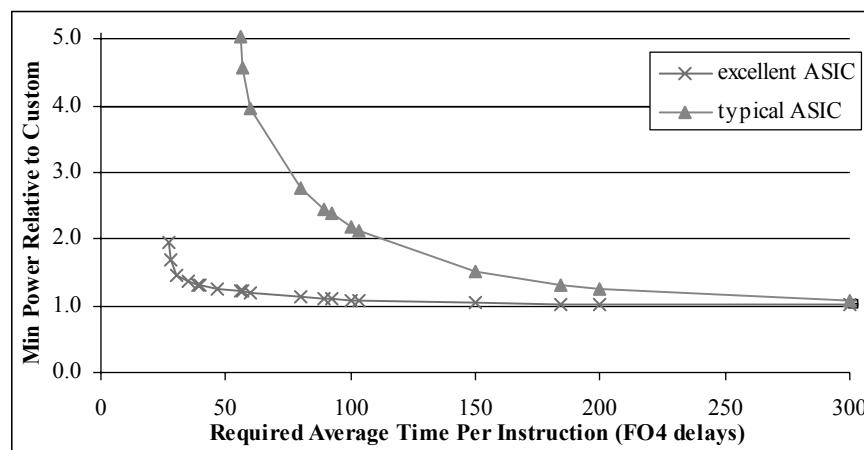

Various parts of the circuit design and fabrication process contribute to the gap between ASIC and custom power. Our analysis of the most significant design factors and their impact on the total power when a chip is active is outlined in Table 2.4. The “typical” column shows the maximum contribution of individual factors comparing a typical ASIC to a custom design. In total these factors can make power an order of magnitude worse. In practice, even the best custom designs can’t fully exploit all these factors simultaneously. Low power design techniques that can be incorporated within an EDA flow can reduce the impact of these factors in a carefully designed ASIC as per the “excellent” column in Table 2.4.

Most low power EDA tools focus on reducing the dynamic power in control logic, datapath logic, and the clock tree. The design cost for custom memory is low, because of the high regularity. Several companies provide custom memory for ASIC processes. Optimization of memory hierarchy, memory size, caching policies, and so forth is application dependent and beyond the scope of this book, though they have a substantial impact on the system-level performance and power consumption. We will focus on the power consumption in a processor core.

Table 2.4 Factors contributing to ASICs being higher power than custom. The excellent column is what ASICs may achieve using low power and high performance techniques. This table focuses on the total power when a circuit is active, so power gating and other standby leakage reduction techniques are omitted. The combined impact of these factors is not multiplicative – see discussion in Section 2.5.1.

| Contributing Factor         | Typical ASIC | Excellent ASIC |

|-----------------------------|--------------|----------------|

| microarchitecture           | 5.1 $\times$ | 1.9 $\times$   |

| clock gating                | 1.6 $\times$ | 1.0 $\times$   |

| logic style                 | 2.0 $\times$ | 2.0 $\times$   |

| logic design                | 1.2 $\times$ | 1.0 $\times$   |

| technology mapping          | 1.4 $\times$ | 1.0 $\times$   |

| cell and wire sizing        | 1.6 $\times$ | 1.1 $\times$   |

| voltage scaling             | 4.0 $\times$ | 1.0 $\times$   |

| floorplanning and placement | 1.5 $\times$ | 1.1 $\times$   |

| process technology          | 1.6 $\times$ | 1.0 $\times$   |

| process variation           | 2.0 $\times$ | 1.3 $\times$   |

Microarchitectural techniques such as pipelining and parallelism increase throughput, allowing timing slack for gate downsizing and voltage scaling. The microarchitecture also affects the average instructions per cycle (IPC), and hence energy efficiency. The power and delay overheads for microarchitectural techniques must be considered. With sufficient timing slack, reducing the supply voltage can greatly increase the energy efficiency. For example in Table 2.1, scaling the XScale from Vdd of 1.8V to 1.0V increases the efficiency from 0.78MIPS/mW to 3.40MIPS/mW, a factor of 4.4 $\times$ , but the performance decreases from 1250MIPS to 510MIPS.

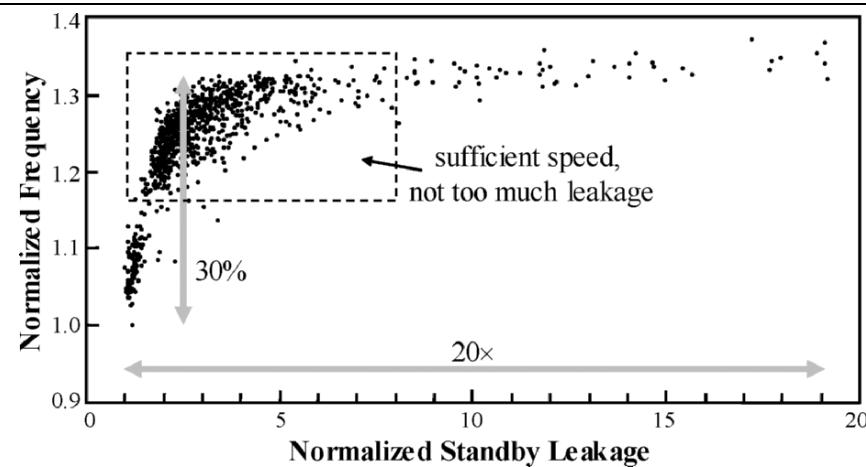

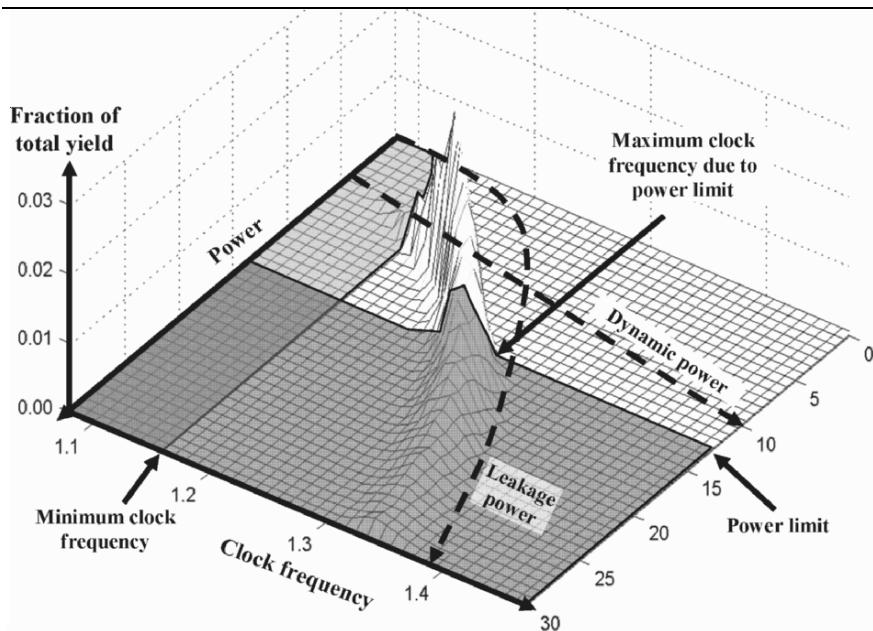

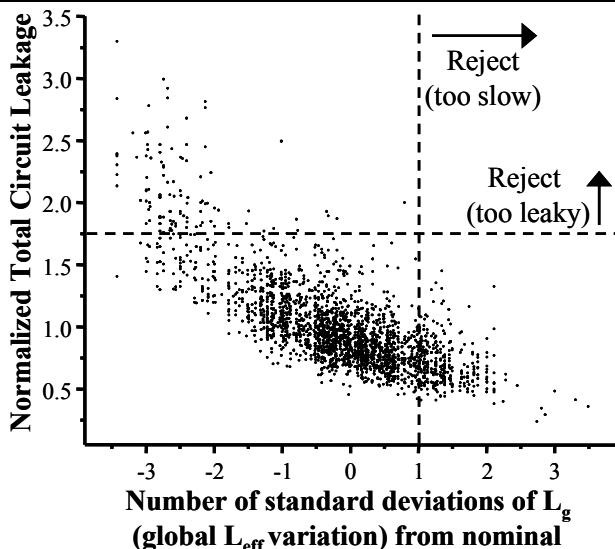

Process technology can reduce leakage by more than an order of magnitude. It also has a large impact on dynamic power. Process variation results in a wide range of the leakage power for chips and some variation in the maximum operating clock frequency for a given supply voltage. For high yield, a higher supply voltage may be needed to ensure parts meet the desired performance target, resulting in a significant spread in power consumption. Limiting process variation and guard-banding for it without being overly conservative help reduce the power consumption.

Using a high speed logic style on critical paths can increase the speed by 1.5 $\times$  [18]. Circuitry using only slower complementary static CMOS logic at a tight performance constraint may be 2.0 $\times$  higher power than circuitry using a high speed logic style to provide timing slack for power reduction by voltage scaling and gate downsizing.

Other factors in Table 2.4 have smaller contributions to the power gap. We will discuss the combined impact of the factors and then look at the individual factors and low power techniques to reduce their impact.

## 2.5.1 Combined impact of the contributing factors

The combined impact of the factors is complicated. The estimate of the contribution from voltage scaling assumes that timing slack is provided by pipelining, so this portion is double counted. The timing slack depends on the tightness of the performance constraint, which has a large impact on the power gap. We assumed a tight performance constraint for both the typical ASIC and excellent ASIC for the contributions from microarchitecture, logic style, and voltage scaling in Table 2.4. If the performance constraint is relaxed, then the power gap is less. For example, from our model of pipelining to provide timing slack for voltage scaling and gate sizing, the power gap between a typical ASIC and custom decreases from 5.1 $\times$  at a tight performance constraint for the typical ASIC to 4.0 $\times$  if the constraint is relaxed by 7%.

Chapter 3 details our power and delay model that incorporates pipelining, logic delay, voltage scaling and gate sizing. The logic delay is determined by factors such as the logic style, wire lengths, process technology, and process variation which affects the worse case delay.

From analysis with this model, an excellent ASIC using the low power techniques that we recommend below may close the power gap to a factor of 2.6 at a tight performance constraint for a typical ASIC [16].

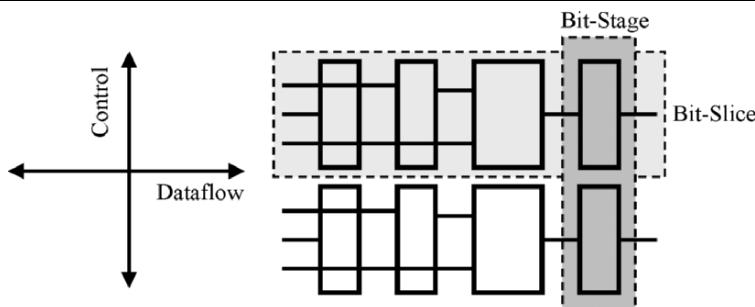

## 2.5.2 Microarchitecture

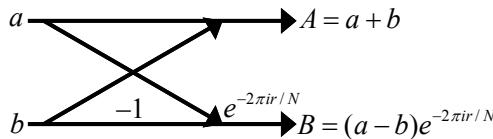

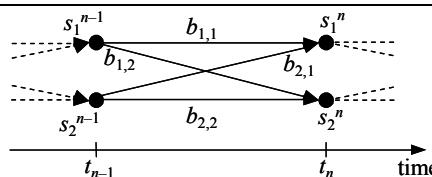

Algorithmic and architectural choices can reduce the power by an order of magnitude [77]. We assume that ASIC and custom designers make similar algorithmic and architectural choices to find a low power implementation that is appropriate for the required performance and target application. Pipelining and parallelism are the two major microarchitectural techniques that can be used to maintain throughput (see Figure 2.3), when other power reduction techniques increase critical path delay. With similar microarchitectures, how do ASIC and custom pipelining and parallelism compare?

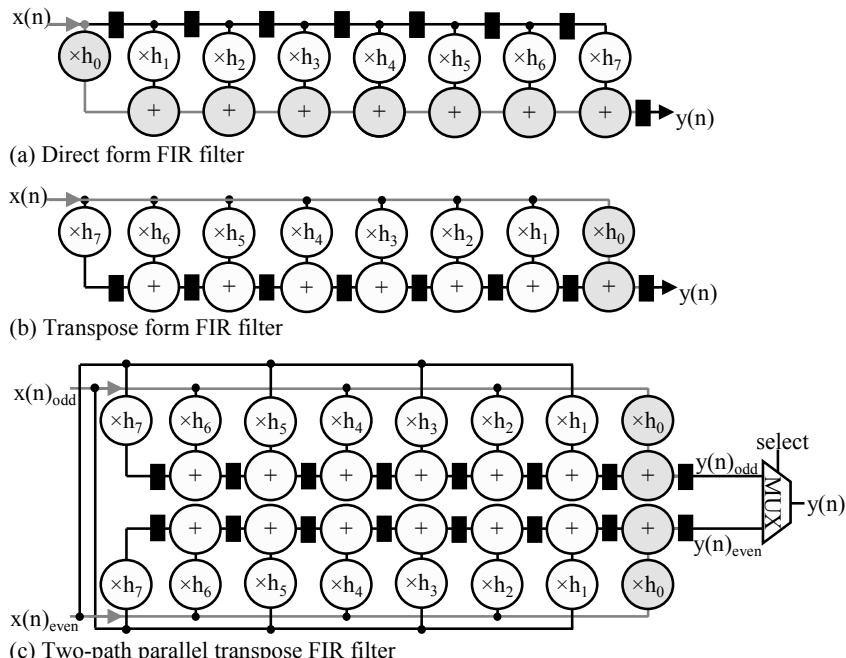

Figure 2.3 This diagram shows pipelined (b) and parallel implementations (c) of the unpipelined direct form finite input response (FIR) filter in (a) [19][79]. The FIR filter calculates  $y_n = h_0x_n + h_1x_{n-1} + \dots + h_7x_{n-7}$ . The critical paths are shown in grey. The minimum clock period decreases as the registers break the critical path up into separate pipeline stages. Computation in each pipeline stage proceeds concurrently. The parallel implementation doubles the throughput, but the area is more than doubled. The multiplexer to select the odd or even result from the two parallel datapaths at each clock cycle is denoted by MUX.

On their own, pipelining and parallelism do not reduce power. Pipelining reduces the critical path delay by inserting registers between combinational logic. Glitches may not propagate through pipeline registers, but the switching activity of the combinational logic is otherwise unchanged. Additional pipeline registers add to the leakage power and especially to the dynamic power, because the clock signal going to the registers has high activity. Pipelining may reduce the instructions per cycle (IPC) due to branch misprediction and other hazards; in turn this reduces the energy efficiency. Parallelism trades off area for increased throughput, with overheads for multiplexing and additional wiring [6]. Both techniques enable the same performance to be met at lower supply voltage with smaller gate sizes, which can provide a net reduction in power.

Bhavnagarwala et al. [6] predict a 2 to 4 $\times$  reduction in power with voltage scaling by using 2 to 4 parallel datapaths. Generally, ASICs can make as full use of parallelism as custom designs, but careful layout is required to minimize additional wiring overheads.

Delay overheads for pipelining include: register delay; register setup time; clock skew; clock jitter; and any imbalance in pipeline stage delays that cannot be compensated for by slack passing or useful clock skew. For a given performance constraint, the pipelining delay overheads reduce the slack available to perform downsizing and voltage scaling.

In the IDCT, the cost of pipelining was about a 20% increase in total power, but pipelining reduced the critical path length by a factor of 4. For the same performance without pipelining, Vdd would have to be increased from 1.32V to 2.2V. Thus pipelining helped reduce power by 50% [102].

### 2.5.2.1 What's the problem?

The timing overhead per pipeline stage for a custom design is about 3 FO4 delays, but it may be 20 FO4 delays for an ASIC, substantially reducing the timing slack available for power reduction. For a typical ASIC, the budget for the register delay, register setup time, clock skew and clock jitter is about 10 FO4 delays. Unbalanced critical path delays in different pipeline stages can contribute an additional 10 FO4 delays in ASICs. If the delay constraint is tight, a little extra timing slack can provide substantial power savings from downsizing gates – for example, a 3% increase in delay gave a 20% reduction in energy for a 64-bit adder [104].

For pipeline registers, most ASICs use slow edge-triggered D-type flip-flops that present a hard timing boundary between pipeline stages, preventing slack passing. The clock skew between clock signal arrivals at different points on the chip must be accounted for. Faster pulse-triggered flip-flops were used in the custom StrongARM [62]. Some pulse-triggered flip-flops have greater clock skew tolerance [80]. Custom designs may use

level-sensitive latches to allow slack passing, and latches are also less sensitive to clock skew [19].

The custom XScale used clock-pulsed transparent latches [22]. A D-type flip-flop is composed of a master-slave latch pair. Thus a clock-pulsed latch has about half the delay of a D-type flip-flop and has a smaller clock load, which reduced the clock power by 33%. Clock-pulsed latches have increased hold time and thus more problems with races. The pulse width had to be carefully controlled and buffers were inserted to prevent races. The clock duty cycle also needs to be carefully balanced.

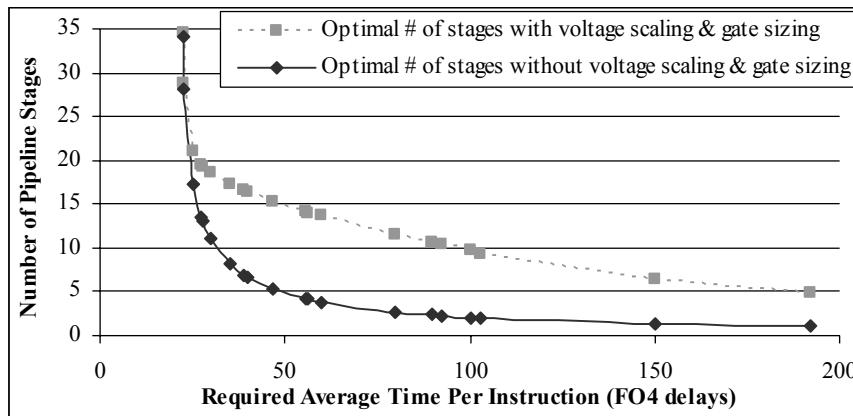

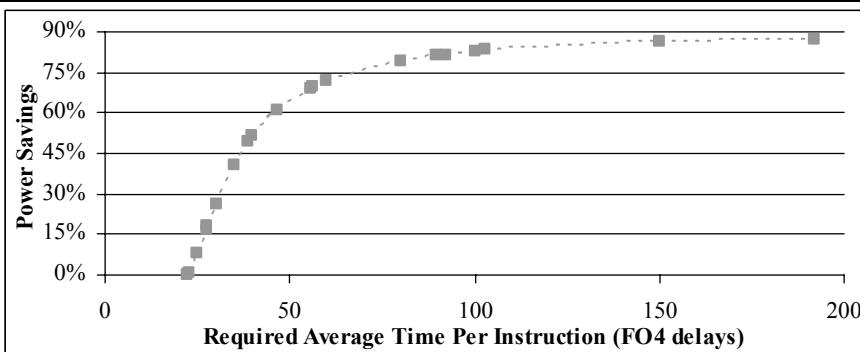

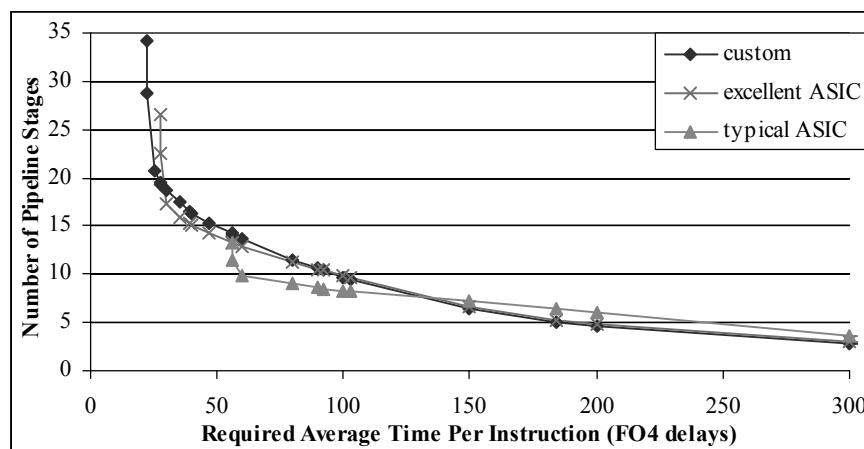

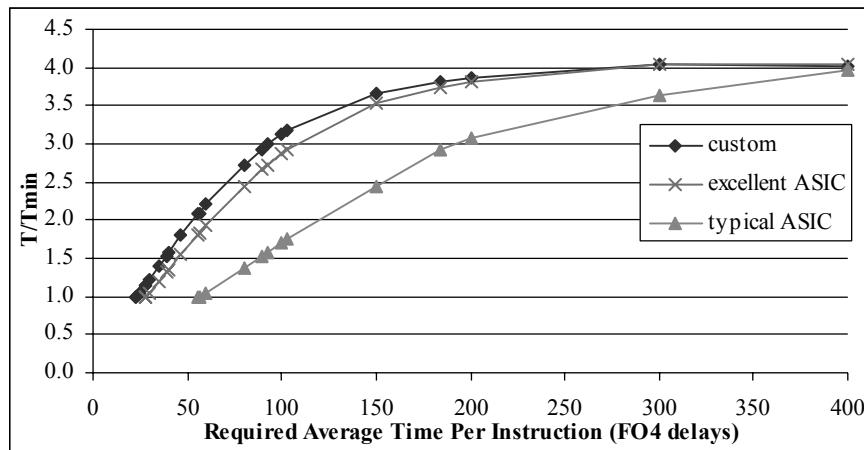

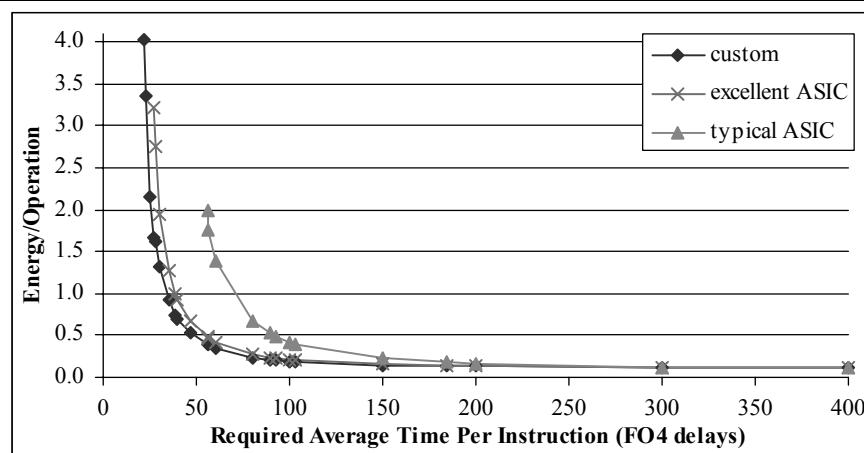

To estimate the impact of worse ASIC pipelining delay overhead, we developed a pipeline performance and power model, with power reduction from gate downsizing and voltage scaling versus timing slack (see Chapter 3). At a tight performance constraint for the ASIC design, we estimate that ASIC power consumption can be  $5.1\times$  that of custom, despite using a similar number of pipeline stages. While there is no timing slack available to the ASIC design, the lower custom pipeline delay overhead allows significant power reduction by gate downsizing and voltage scaling.

### 2.5.2.2 What can we do about it?

Latches are well-supported by synthesis tools [83], but are rarely used other than in custom designs. Scripts can be used to convert timing critical portions of an ASIC to use latches instead of flip-flops [17]. High-speed flip-flops are now available in some standard cell libraries and can be used in an automated design methodology to replace slower D-type flip-flops on critical paths [33]. Useful clock skew tailors the arrival time of the clock signal to different registers by adjusting buffers in the clock tree and can be used in ASIC designs for pipeline balancing [26]. With these methods, the pipeline delay overhead in ASICs can be reduced to as low as 5 FO4 delays [18]. This enables more slack to be used for downsizing, voltage scaling, or increasing the clock frequency. From our pipeline model, ASICs can close the gap for the microarchitecture and timing overhead factor to within  $1.9\times$  of custom.

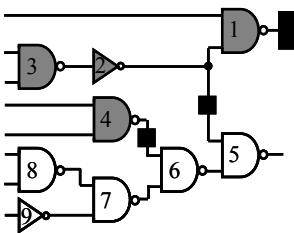

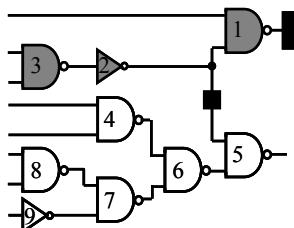

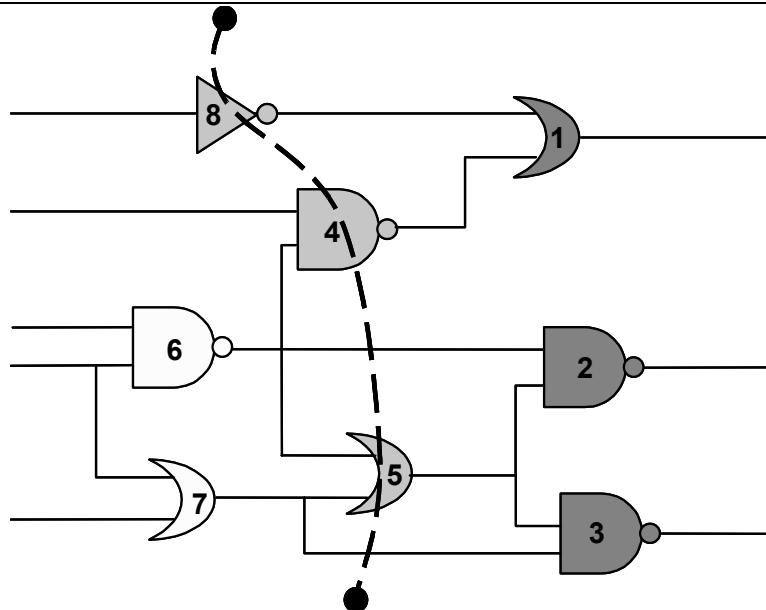

### 2.5.3 Clock gating

In typical operation, pipeline stages and functional units are not always in use. For example, during a sequence of integer operations, the floating point unit may be idle. Providing the logical inputs to the idle unit are held constant, there are only two sources of power dissipation in the idle unit: static leakage; and switching activity at registers and any other clocked elements due to the clock signal – for example, precharge of domino logic.

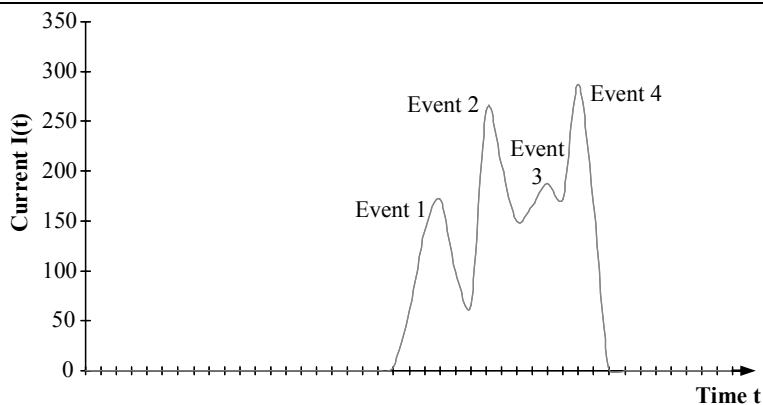

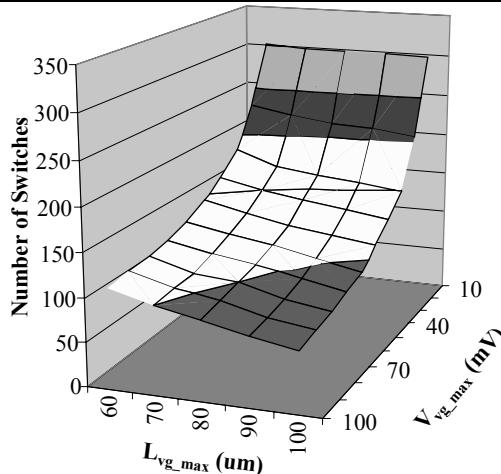

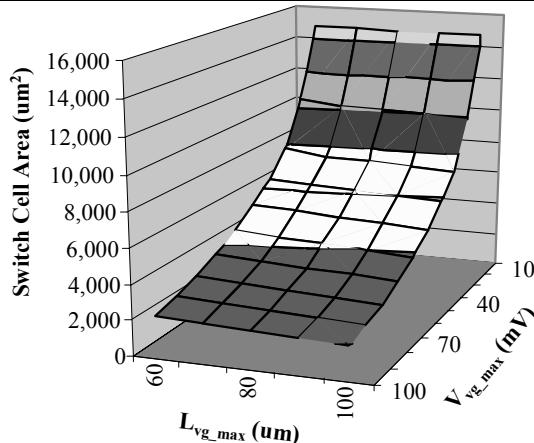

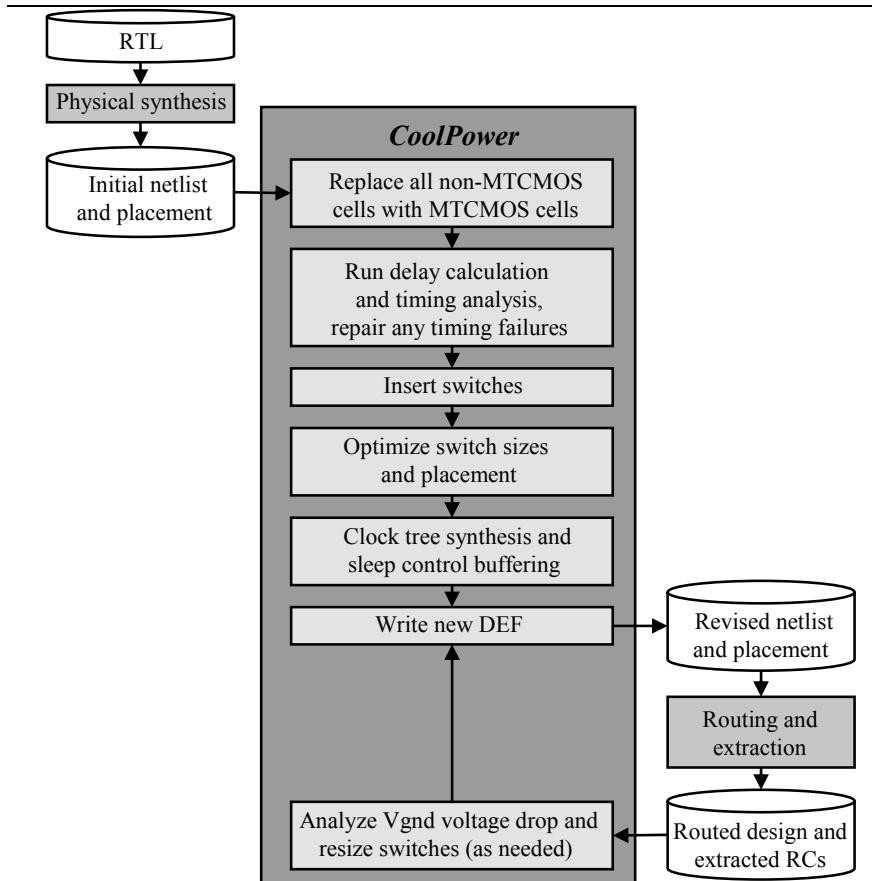

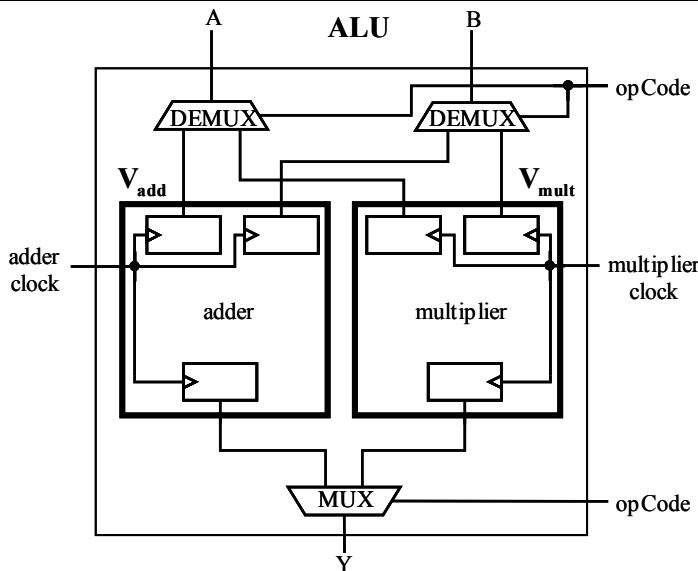

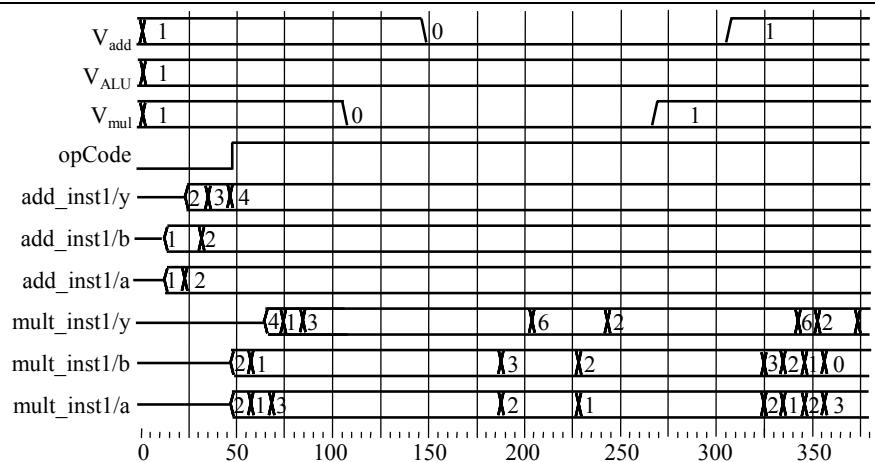

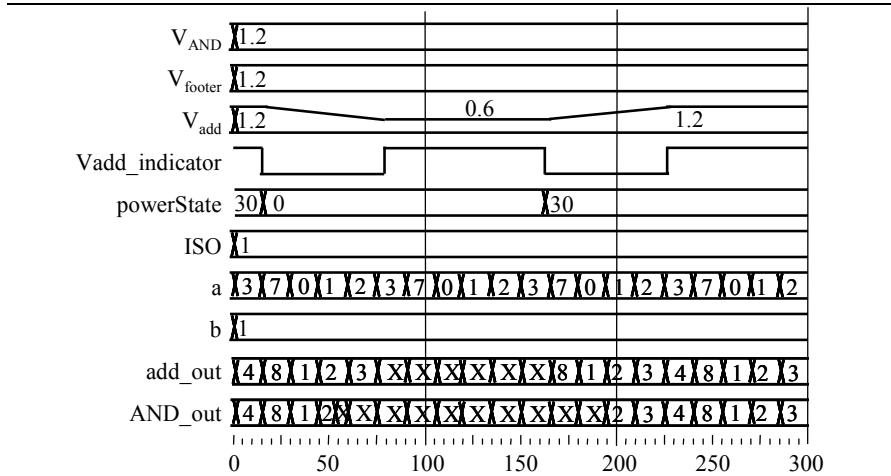

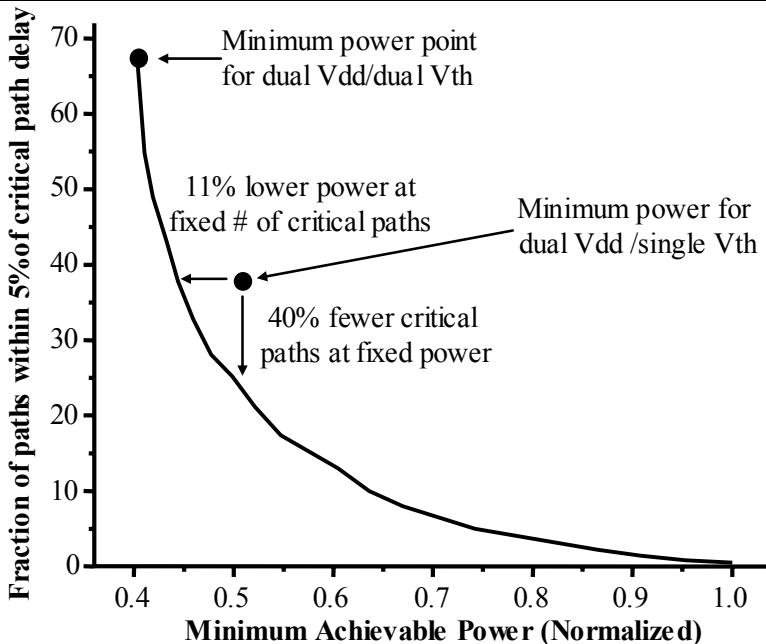

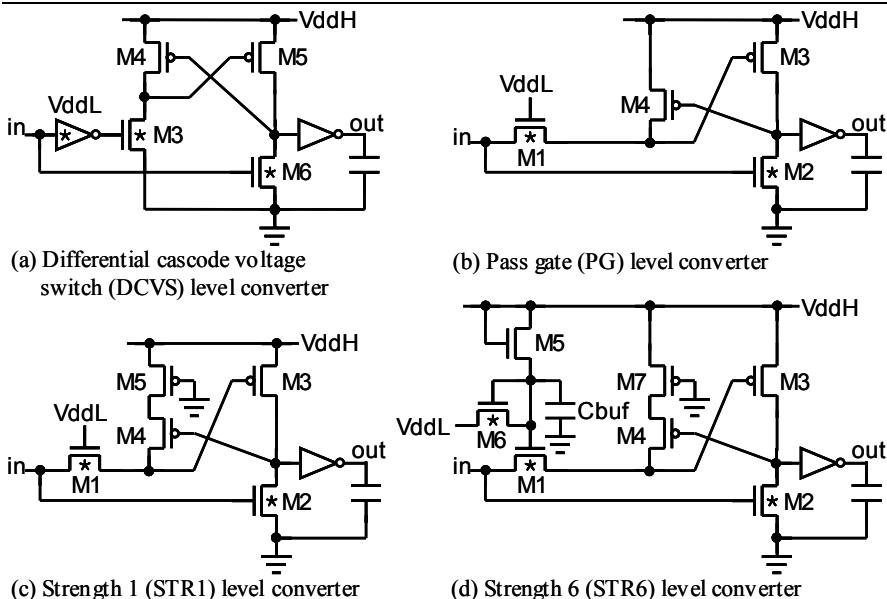

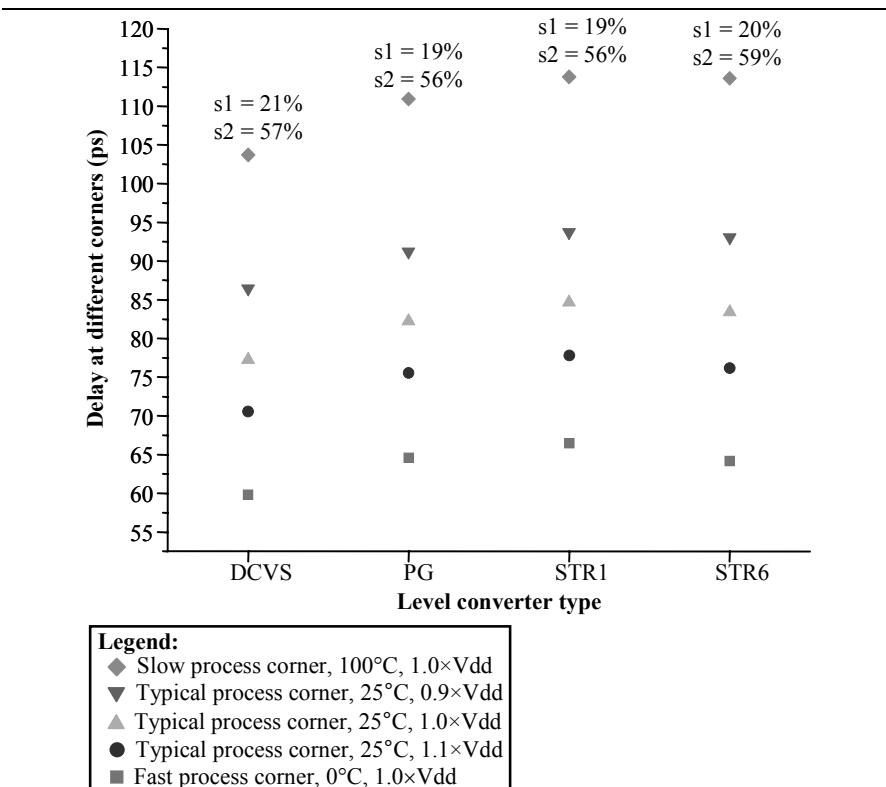

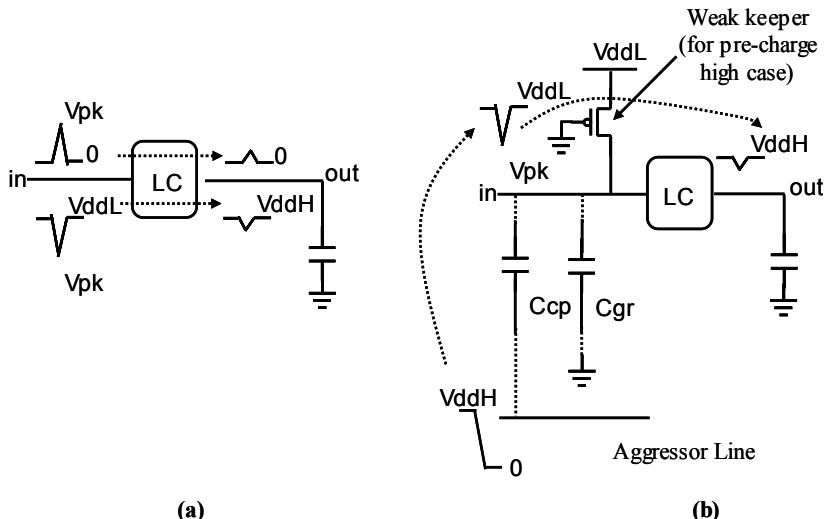

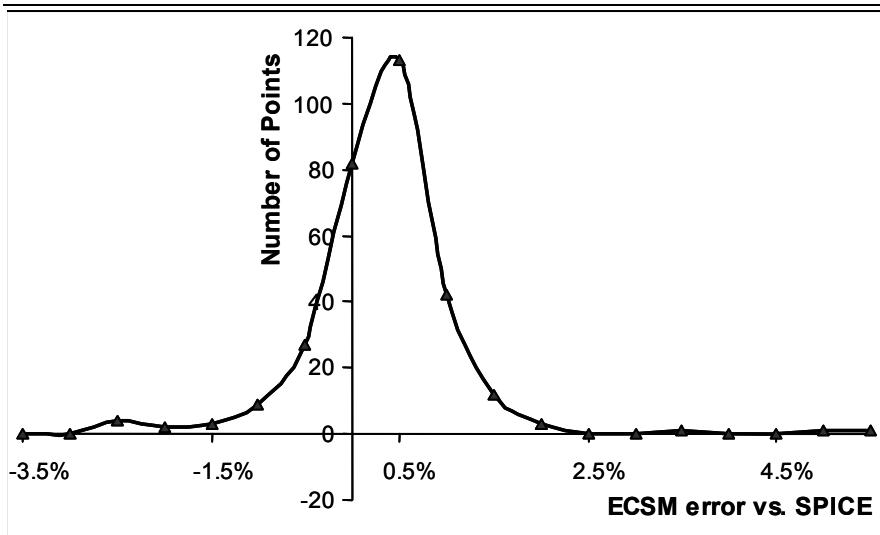

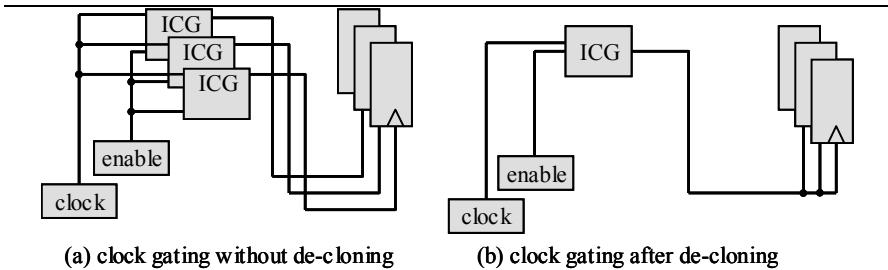

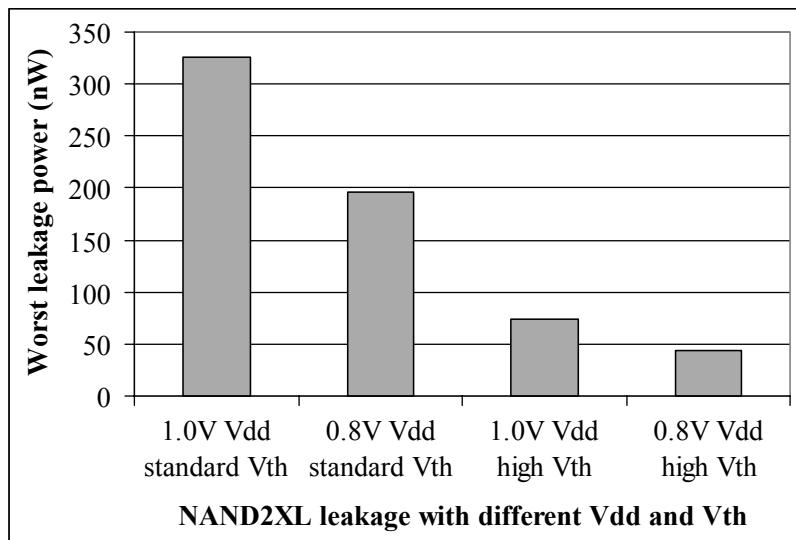

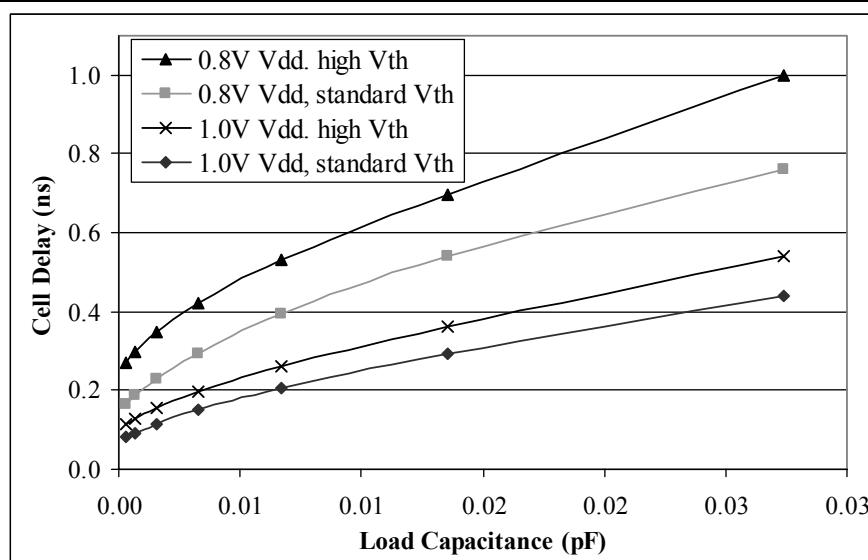

Figure 2.4 This is a simple illustration of clock gating. The clock signal to the registers is gated with a control signal that selects which functional unit is in use. A transparent low latch is usually inserted to de-glitch the enable signal [51].