Christophe Labb 

Subhananda Chakrabarti

Gargi Raina

B. Bindu

*Editors*

# Nanoelectronic Materials and Devices

Select Proceedings of ICNETS2,

Volume III

# **Lecture Notes in Electrical Engineering**

## **Volume 466**

### **Board of Series editors**

Leopoldo Angrisani, Napoli, Italy

Marco Arteaga, Coyoacán, México

Samarjit Chakraborty, München, Germany

Jiming Chen, Hangzhou, P.R. China

Tan Kay Chen, Singapore, Singapore

Rüdiger Dillmann, Karlsruhe, Germany

Haibin Duan, Beijing, China

Gianluigi Ferrari, Parma, Italy

Manuel Ferre, Madrid, Spain

Sandra Hirche, München, Germany

Faryar Jabbari, Irvine, USA

Janusz Kacprzyk, Warsaw, Poland

Alaa Khamis, New Cairo City, Egypt

Torsten Kroeger, Stanford, USA

Tan Cher Ming, Singapore, Singapore

Wolfgang Minker, Ulm, Germany

Pradeep Misra, Dayton, USA

Sebastian Möller, Berlin, Germany

Subhas Mukhopadhyay, Palmerston, New Zealand

Cun-Zheng Ning, Tempe, USA

Toyoaki Nishida, Sakyo-ku, Japan

Bijaya Ketan Panigrahi, New Delhi, India

Federica Pascucci, Roma, Italy

Tariq Samad, Minneapolis, USA

Gan Woon Seng, Nanyang Avenue, Singapore

Germano Veiga, Porto, Portugal

Haitao Wu, Beijing, China

Junjie James Zhang, Charlotte, USA

“Lecture Notes in Electrical Engineering (LNEE)” is a book series which reports the latest research and developments in Electrical Engineering, namely:

- Communication, Networks, and Information Theory

- Computer Engineering

- Signal, Image, Speech and Information Processing

- Circuits and Systems

- Bioengineering

LNEE publishes authored monographs and contributed volumes which present cutting edge research information as well as new perspectives on classical fields, while maintaining Springer’s high standards of academic excellence. Also considered for publication are lecture materials, proceedings, and other related materials of exceptionally high quality and interest. The subject matter should be original and timely, reporting the latest research and developments in all areas of electrical engineering.

The audience for the books in LNEE consists of advanced level students, researchers, and industry professionals working at the forefront of their fields. Much like Springer’s other Lecture Notes series, LNEE will be distributed through Springer’s print and electronic publishing channels.

More information about this series at <http://www.springer.com/series/7818>

*Editors*

Christophe Labb 

CIMAP - Caen

 cole Nationale Sup rieure d'ing nieurs

Caen

France

Subhananda Chakrabarti

Department of Electrical Engineering

Indian Institute of Technology Bombay

Mumbai, Maharashtra

India

Gargi Raina

School of Electronics Engineering

VIT University, Vellore

Vellore, Tamil Nadu

India

B. Bindu

School of Electronics Engineering

VIT University, Chennai

Chennai, Tamil Nadu

India

ISSN 1876-1100

ISSN 1876-1119 (electronic)

Lecture Notes in Electrical Engineering

ISBN 978-981-10-7190-4

ISBN 978-981-10-7191-1 (eBook)

<https://doi.org/10.1007/978-981-10-7191-1>

Library of Congress Control Number: 2017957702

  Springer Nature Singapore Pte Ltd. 2018

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Printed on acid-free paper

This Springer imprint is published by Springer Nature

The registered company is Springer Nature Singapore Pte Ltd.

The registered company address is: 152 Beach Road, #21-01/04 Gateway East, Singapore 189721, Singapore

# Preface

This book volume is based on the talks delivered in Symposium C entitled Nanoelectronic Materials and Devices at “International Conference on NextGen Electronic Technologies—Silicon to Software” (ICNETS2). The theme of this symposium relates to the advances and emerging directions made in the fabrication, application as well as simulation of novel nanoelectronic materials and their impact on diverse electronic device technologies. The articles in this book volume focus on diverse topics encompassing functional electronic nanomaterials, nanocomposites for energy application, sensing and high-strength materials and simulation of novel device design structures for ultra-low-power applications.

Nanotechnology has been perceived as an enabler of extending the Moore’s law in nanoelectronic domain in the present technology era. This symposium brought together experts from across international and national academic communities as well as industries to discuss fabrication, characterization and computational aspects in the field of nanoelectronics.

This book volume provides a compilation of different functional nanoelectronic materials such as graphene oxide-based metal oxide nanoparticles, nanocomposites and InAs/GaAs quantum dots and their device application in memristors, MEMs, CNTFETs, TFETs and memory circuits. We hope this book provides insight into and perspective on the domain of nanoelectronic materials to upcoming young researchers and non-specialists.

Mumbai, India

Caen, France

Chennai, India

Chennai, India

Dr. Subhananda Chakrabarti

Dr. Christophe Labb  

Dr. Gargi Raina

Dr. B. Bindu

# **Acknowledgements**

We are extremely grateful for the valuable advice, guidance and opportunity provided by Dr. S. R. S. Prabharan, Dean, SENSE, and Chairman of ICNETS2 to participate in and contribute to the organization of the Symposium C entitled “Nanoelectronic Materials and Device Applications”. We are thankful to various committee heads and conference/symposia managers for all their efforts and all the support received towards the successful and smooth conduct of the symposium sessions.

We are thankful to the VIT management for all the support and encouragement for the successful conduct of this conference and enabling our participation.

We express our heartfelt thanks to the invited speakers and keynote speakers for taking time off from their busy schedule and travelling long distance to share with us their research insights in the upcoming domain of nanoelectronic materials and device applications. We are thankful to all the authors who participated and contributed their research findings towards bringing out this book volume.

The editors wish to acknowledge the important contributions of Dr. Mohanaprasad and Dr. Annis in coordinating and assembling the contributions for the book. Last but not least, we would like to thank and appreciate our publication partners at Springer, especially Swati Meherishi and Aparajita Singh, for helping us bring out this special volume comprising invited and keynote talks.

# Contents

|                                                                                                                                               |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

| <b>The Effect of Functionalized MWCNT on Mechanical and Electrical Properties of PMMA Nanocomposites .....</b>                                | 1  |

| Amrit Mallick, Punyapriya Mishra and Sarat Kumar Swain                                                                                        |    |

| <b>Performance Analysis of Dual Metal Double Gate Tunnel-FETs for Ultralow Power Applications .....</b>                                       | 11 |

| D. Gracia and D. Nirmal                                                                                                                       |    |

| <b>Films of Reduced Graphene Oxide-Based Metal Oxide Nanoparticles .....</b>                                                                  | 19 |

| Neena S. John, K. Bramhaiah, Indu Pandey and C. Kavitha                                                                                       |    |

| <b>Size Optimization of InAs/GaAs Quantum Dots for Longer Storage Memory Applications .....</b>                                               | 29 |

| V. Damodaran and Kaustab Ghosh                                                                                                                |    |

| <b>Design and Analysis of a CMOS 180-nm Fractional-N Frequency Synthesizer .....</b>                                                          | 37 |

| P. Parvathy and N. Saraswathi                                                                                                                 |    |

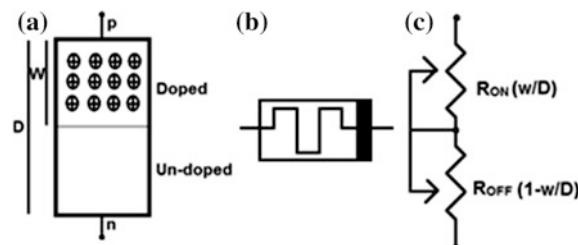

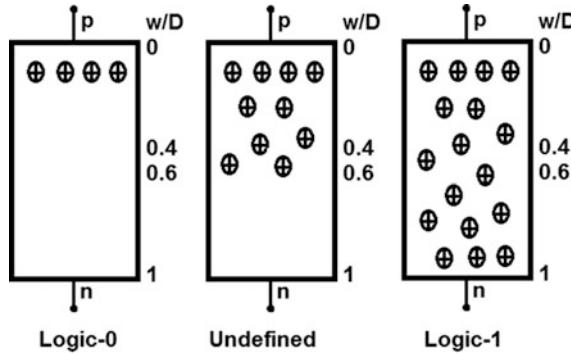

| <b>Memristor-Based Approximate Adders for Error Resilient Applications .....</b>                                                              | 51 |

| S. Muthulakshmi, Chandra Sekhar Dash and S. R. S. Prabaharan                                                                                  |    |

| <b>Integrated MEMS Capacitive Pressure Sensor with On-Chip CDC for a Wide Operating Temperature Range .....</b>                               | 61 |

| Y. G. S. S. Sai Charan and Ananiah Durai Sundararajan                                                                                         |    |

| <b>A High SNDR and Wider Signal Bandwidth CT <math>\Sigma\Delta</math> Modulator with a Single Loop Nonlinear Feedback Compensation .....</b> | 81 |

| Simhadri Chandra Sekhar and Ananiah Durai Sundararajan                                                                                        |    |

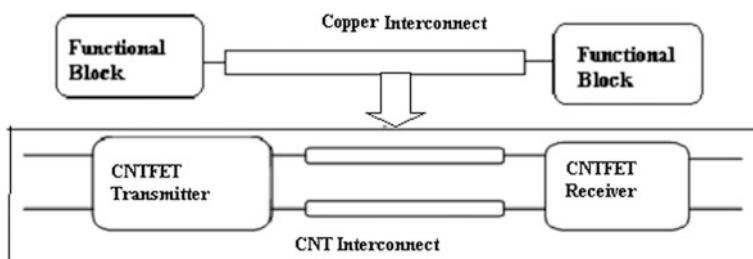

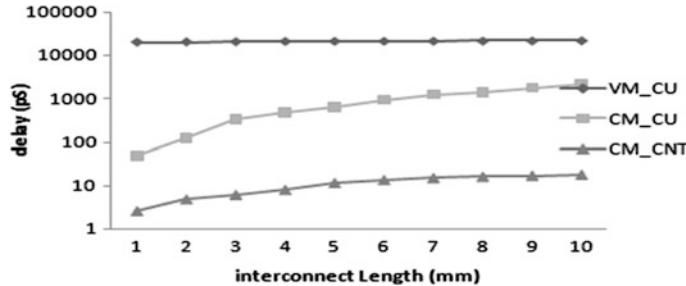

| <b>Design of Current-Mode CNTFET Transceiver for Bundled Carbon Nanotube Interconnect .....</b>                                               | 91 |

| P. Murugeswari, A. P. Kabilan and V. E. Jayanthi                                                                                              |    |

|                                                                                                                 |     |

|-----------------------------------------------------------------------------------------------------------------|-----|

| <b>Weak Cell Detection Techniques for Memristor-Based Memories . . . . .</b>                                    | 101 |

| V. Ravi and S. R. S. Prabaharan                                                                                 |     |

| <b>Enhancement of Transconductance Using Multi-Recycle Folded Cascode Amplifier . . . . .</b>                   | 111 |

| Mayur T. Kalkote and S. Ananiah Durai                                                                           |     |

| <b>Nondestructive Read Circuit for Memristor-Based Memories . . . . .</b>                                       | 123 |

| Marreddy Guru Sai Prasad Reddy and V. Ravi                                                                      |     |

| <b>A Built-in Self-Repair Architecture for Random Access Memories . . . . .</b>                                 | 133 |

| Sanjay Patnaik and V. Ravi                                                                                      |     |

| <b>A Current-Mode DC-DC Boost Converter with Fast Transient and On-Chip Current-Sensing Technique . . . . .</b> | 147 |

| S. Sudheer Sagar and P. Reena Monica                                                                            |     |

| <b>A Modified GDI-Based Low-Power and High Read Stability 8-T SRAM Memory with CNTFET Technology . . . . .</b>  | 165 |

| Apoorva Amdapurkar, Dinesh Wani, Pooja Shinde and P. Reena Monica                                               |     |

| <b>High Performance Trench Gate Power MOSFET of Indium Phosphide . . . . .</b>                                  | 175 |

| Geeta Tahalyani, Raghvendra Sahai Saxena and T. Vigneswaran                                                     |     |

| <b>Memristor Equipped Error Detection Technique . . . . .</b>                                                   | 183 |

| Anindita Nayak, Satyajeet Sahoo and S. R. S. Prabaharan                                                         |     |

| <b>28 nm FD-SOI SRAM Design Using Read Stable Bit Cell Architecture . . . . .</b>                               | 193 |

| A. Lourts Deepak, Mrinal Gandotra, Shailja Yadav, Himani Gandhi and S. Umadevi                                  |     |

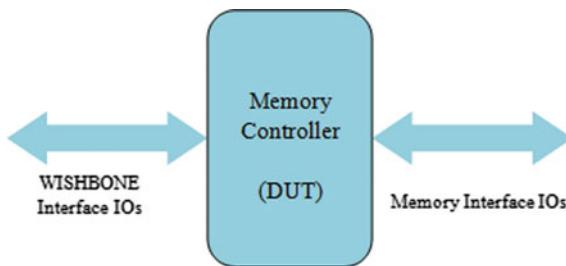

| <b>Design and Verification of Memory Controller with Host Wishbone Interface . . . . .</b>                      | 207 |

| Dinesh Katuri and S. Umadevi                                                                                    |     |

| <b>8-Bit Asynchronous Wave-Pipelined Arithmetic Logic Unit . . . . .</b>                                        | 233 |

| Polani Rahul, Korada Prudhvi Raj and S. Umadevi                                                                 |     |

| <b>Author Index . . . . .</b>                                                                                   | 245 |

# About the Editors

**Dr. Christophe Labb  ** is an Associate Professor at CIMAP Lab (Centre de Recherche sur les Ions, les Mat  riaux et la Photonique), Caen, France, in the engineering school ENSICAEN. He obtained his PhD in Rare Earth Lasers at the Interdisciplinary Research Center Laser Ions, Caen, in 1999. After a postgraduate position at the Laser Arava Laboratory of the Ben-Gurion University of the Negev, Israel, on ionic matrix lasers pumped by diode, he became an Assistant Professor at the Laboratory of Optical Functions for Telecommunications (FOTON Lab) in Rennes, France, in 2002. His ongoing research focuses on photon sources for telecommunications or visible light applications and on photovoltaic cells.

**Dr. Subhananda Chakrabarti** received his MSc and PhD from the Department of Electronic Science, University of Calcutta, India, in 1993 and 2000, respectively. He was a Lecturer at the Department of Physics, St. Xavier's College, Kolkata. He served as a Senior Research Fellow at the University of Michigan, Ann Arbor, USA, from 2001 to 2005, as a Senior Researcher at Dublin City University, Ireland, from 2005 to 2006 and as a Senior Researcher (RA2) at the University of Glasgow, UK, from 2006 to 2007. He became an Assistant Professor at the Department of Electrical Engineering, Indian Institute of Technology Bombay (IIT Bombay), India, in 2007, where he currently serves as a Professor. He is a Fellow of the Institution of Electrical and Telecommunication Engineers (IETE), India, and a Member of IEEE, MRS USA, SPIE USA, etc. His research interests lie in compound (III-V and II-VI) semiconductor-based optoelectronic materials and devices.

**Dr. Gargi Raina** is a Professor at the School of Electronics Engineering (SENSE), VIT University, India. She completed her MS in Condensed Matter Physics at the Department of Physics and Astronomy, University of Hawaii, Manoa, USA (1991). She obtained her PhD from Jawaharlal Nehru Centre for Advanced Scientific Research (JNCASR), Bangalore, India, in 2004. She worked as an "Application Scientist" and helped set up the Advanced Metrology Application Lab of Digital Instruments/Veeco Inc., USA, at JNCASR, Bangalore. She joined the Vellore Institute of Technology in 2006 as an Associate Professor and has been a professor since 2008, while also serving as Director of the Center for Nanotechnology

Research from June 2014 to September 2015. Her current research interests include functional nanomaterials, nanopatterning and assembly techniques, scanning probe microscopy (SPM)-based nanolithography, patterning and lithography for graphene, graphene and nanocarbon materials for energy applications, simulation of carbon nanotube (CNT)/graphene-based nanoscale devices and plasmonic nanolithography.

**Dr. B. Bindu** received her MTech in Digital Electronics from Cochin University of Science and Technology, India, and PhD in Electrical Engineering from the Indian Institute of Technology Madras (IIT Madras), Chennai, India. Her specialization is in nanoelectronics and very large-scale integration (VLSI). She worked as a post-doctoral researcher for 3 years with the Device Modelling Group, University of Glasgow, UK, and at the Institute for Microelectronics, Technical University of Vienna, Austria. Currently, she is an Associate Professor at VIT University, Chennai. Her current research interests include the modelling of various issues in nanoscaled metal oxide semiconductor field-effect transistors (MOSFETs), compact modelling of non-classical MOSFETs and power semiconductor devices for analog and digital VLSI circuit design.

# The Effect of Functionalized MWCNT on Mechanical and Electrical Properties of PMMA Nanocomposites

Amrit Mallick, Punyapriya Mishra and Sarat Kumar Swain

**Abstract** Proper assortment of compatible reinforcement and matrix could improve the mechanical strength and electrical properties of the nanocomposites. This chapter proposes a novel sequential approach of fabrication and testing for mechanical strength and electrical conductivity of the multiwall carbon nanotube (MWCNT) reinforced PMMA composite by extrusion technique along with their morphological analysis by field emission scanning electron microscope (FESEM). The MWCNT dispersion is a major challenge; encountered particularly in the thermoplastic polymer nanocomposites. Functionalized MWCNTs (f-MWCNTs) in varying weight proportions of 0.1, 0.3, 0.5, 0.7, and 1.0 wt% were added to the thermoplastic polymer matrix such as polymethyl methacrylate (PMMA) and then extruded into ASTM standard specimens. The mechanical properties such as tensile stress, tensile strain, tensile modulus at maximum load, and impact strength were measured, and their improved magnitudes reaffirmed effective dispersion of f-MWCNTs in matrix. Composites replacing the conventional engineering materials in electronic devices should have better electrical conductivity for various applications. Hence, the conductance of specimens was measured and showed a very low percolation threshold for electrical conductivity.

**Keywords** f-MWCNT · PMMA · Nanocomposite · FESEM · Tensile strength · Flexural strength · Impact strength · Electrical conductivity

---

A. Mallick (✉)

Department of Mechanical Engineering, Centurion University of Technology and Management, Paralakhemundi 761211, India

e-mail: amritmallick28@gmail.com

P. Mishra

Department of Mechanical Engineering, Veer Surendra Sai University of Technology, Burla, Sambalpur 768018, India

e-mail: priya.punya@gmail.com

S. K. Swain (✉)

Department of Chemistry, Veer Surendra Sai University of Technology, Burla, Sambalpur 768018, India

e-mail: swainsk2@yahoo.co.in

## 1 Introduction

Composite materials are the paramount substitute of the conventional engineering materials in terms of ease of manufacture, reliability, higher physical property, and biodegradability. The potential uses of the composites in aerospace and electronics have drawn attention to develop the new materials to cater the domestic and industrial needs. Composite materials are fabricated as that desired properties are tailored based upon the requirement. Nanocomposites reinforced with functionalized carbon nanotubes in metal matrix reveal strong interfacial bonding [1]. The nanoplatelets of graphite and multiwall carbon nanotubes substantially increase the electrical conductivity and thermal stability of the polymer composites [2, 3]. Short glass fibers/multiwall carbon nanotube composites show significant improvement in the electrical, rheological, and mechanical characteristics [4].

## 2 Materials and Fabrication Technique

### 2.1 Materials

The multiwall carbon nanotubes, procured from Sisco Research Laboratory, Mumbai, India, with an average diameter of 10–20 nm and length of 10–30 nm were chosen as suitable reinforcement for nanocomposite. Transparent thermoplastic polymer such as polymethyl methacrylate was used as matrix, which was purchased from HIMEDIA, Mumbai, India, with an average molecular weight of 15,000.

### 2.2 Functionalization of MWCNTs

To enhance the interfacial adhesion to polymer matrix, functionalization of pristine MWCNTs is carried out prior to fabrication. Nanotubes are treated with concentrated sulfuric acid ( $H_2SO_4$ ) and concentrated nitric acid ( $HNO_3$ ) mixture in ratio of 3:1 v/v, stirred at room temperature [5], and then again treated with oxidizing agents such as concentrated sulfuric acid ( $H_2SO_4$ ) and hydrogen peroxide ( $H_2O_2$ ) that cut the edges and adds carboxyl groups to the surfaces of MWCNTs. Chemically treated f-MWCNTs were dehydrated in oven at 80 °C for 24 h followed by cryomilling at low frequency.

### 2.3 Fabrication Method

f-MWCNTs in various weight percentages of 0.1, 0.3, 0.5, 0.7, and 1.0% of the total composite were taken in five batches. The DSM XPLORE 5 Microcompounder is used for compounding this small quantity mixture of 10 gm weight containing both the f-MWCNTs and the PMMA. The mixture is heated up to 220 °C temperature with 13–15 revolutions per minute of twin screws for 20 min of compounding time [6]. DSM micro 10 cm<sup>3</sup> mini injection molding machine used for injection molding of ASTM standard specimens with the pressure of 0.8 bar [7].

### 2.4 Specimen Preparation

Tensile test standard specimens of f-MWCNT/PMMA composite as per ASTM D638 were fabricated. The flexural test standard specimens of f-MWCNT/PMMA composite as per ASTM D790-99 were fabricated for a three-point bending test. Similarly, the impact test standard specimen ASTM D-256 was also prepared with varying weight proportions of f-MWCNTs 0.1, 0.3, 0.5, 0.7, and 1.0 wt% in the nanocomposites. The fabricated tensile, flexural, and impact test standard specimens are shown in Figs. 1, 2, and 3 respectively.

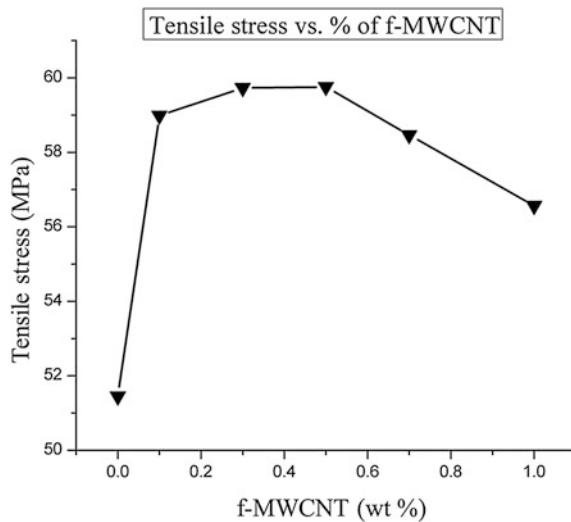

**Fig. 1** Tensile stress of f-MWCNT/PMMA composites as a function of wt% of f-MWCNTs

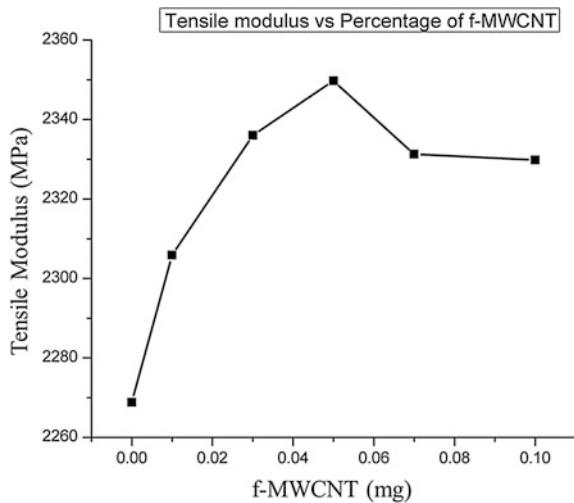

**Fig. 2** Tensile modulus of f-MWCNT/PMMA composites as a function of f-MWCNTs weight

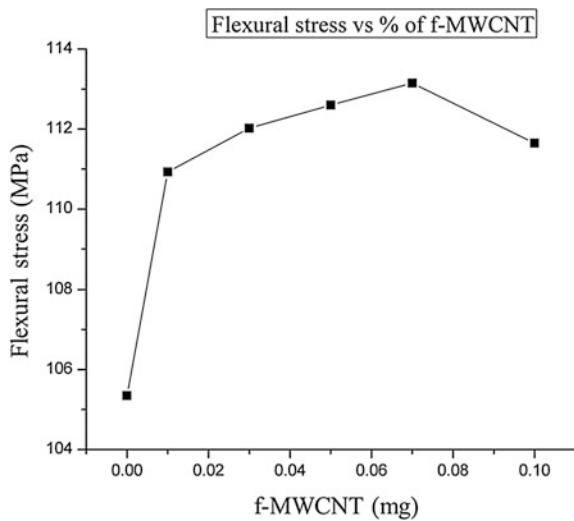

**Fig. 3** Flexural stress of f-MWCNT/PMMA composites as a function of f-MWCNTs weight

## 2.5 Testing of Specimens

The tensile strength, tensile modulus, and tensile strain were measured by the INSTRON-3382 universal testing machine. The displacement was measured with 50-mm extensometer at a rate of 1 mm per minute at room temperature with loading of 5 KN. The stress versus strain curve was plotted. The flexural test was carried out using INSTRON-3382 by three-point bending method at a cross-head speed of 1.38 mm per minute. The flexural stress and flexural modulus for each of the f-MWCNT/PMMA nanocomposite samples were recorded. Impact testing and

Izod test of the specimens with varying weight percentages of f-MWCNTs were carried out using the Tinius Olsen impact tester with pendulum energy 2.7475 J. The notch depth of 2.5 mm with radius of 0.25 mm was maintained as per ASTM D-256 standard.

### 3 Experimental Results

Table 1 shows the stress-strain curves of f-MWCNT/PMMA composite for a different f-MWCNT percentages, i.e., 0, 0.1, 0.3, 0.5, 0.7, and 1.0%, respectively. From the plots, it is observed that tensile stress increases with the increase in percentage of reinforcement [8]. This trend of increase in the tensile stress is found up to 0.5% (0.05 mg) of f-MWCNT content which has a maximum tensile stress value of 59.755 MPa and then decreases for the further addition of reinforcement to the polymer. This trend is evident from tensile stress versus wt% of f-MWCNTs and tensile modulus versus weight of f-MWCNTs from Figs. 1 and 2.

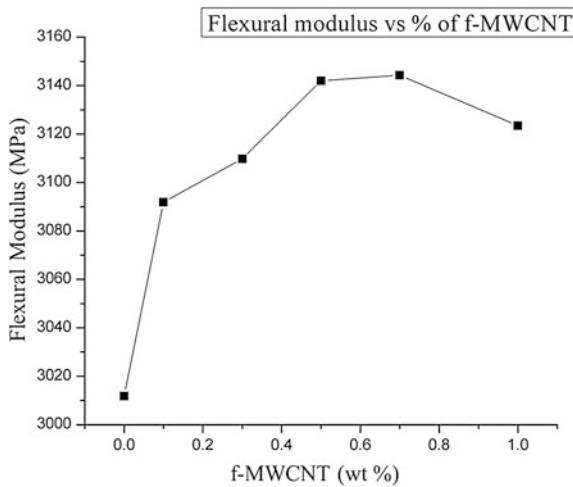

It is also observed from Table 1 that the flexural stress increases for 0.1–0.7% and then decreases for 1.0%. This shows a sharp increase and then slightly decreasing trend from Figs. 2 and 3. The maximum value of flexural stress and modulus is 113.15 and 3144.28 MPa at 0.7% of f-MWCNT, which is much larger in comparison with tensile stress and tensile modulus at maximum load. This indicates that by sacrificing the tensile strength, the flexural strength has been increased. Similarly, composite samples showed increased flexural modulus than pure PMMA. There is 7.4% and 4.4% increase in flexural stress and flexural modulus of composite than pure PMMA sample (Fig. 4).

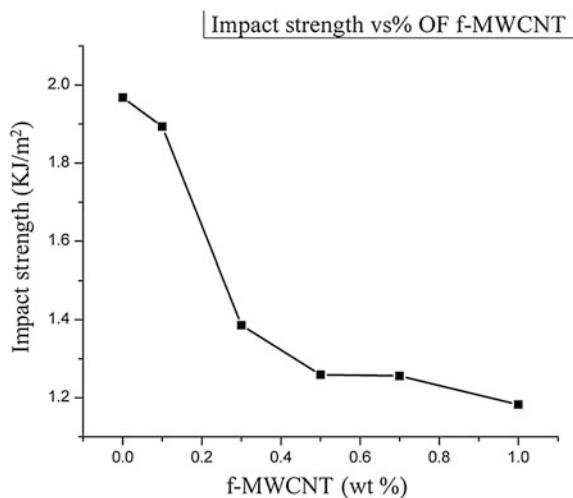

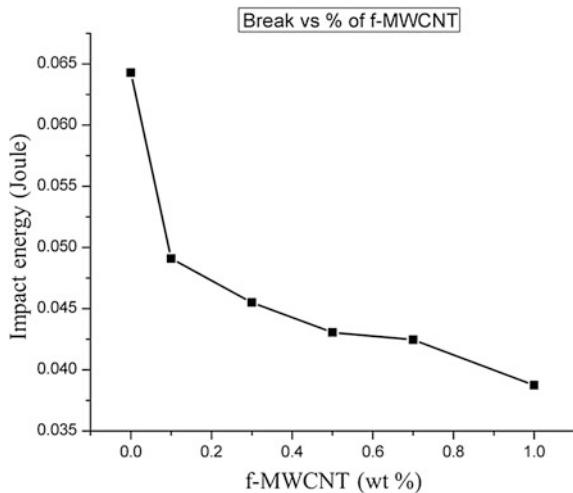

The energy absorbed by the composite during Izod impact test is measured. The variation of impact strength with percentage of f-MWCNT witnessed decrease in the impact strength with the increase in f-MWCNT from the plotted values in Figs. 5 and 6. The cause for decrease in impact strength is attributed to the percentage increase of f-MWCNT in composite that makes the composite more and more brittle and inadequate adhesion between matrix and reinforcement.

**Table 1** Mechanical properties of f-MWCNT/PMMA composites as a function of wt% of f-MWCNTs

| wt%<br>CNTs | Mechanical properties   |                             |                          |                           |                   |                                        |

|-------------|-------------------------|-----------------------------|--------------------------|---------------------------|-------------------|----------------------------------------|

|             | Tensile<br>stress (Mpa) | Tensile<br>modulus<br>(Mpa) | Flexural<br>stress (Mpa) | Flexural<br>modulus (Mpa) | Break<br>in Joule | Impact strength<br>in J/m <sup>2</sup> |

| 0           | 51.47                   | 2268.86                     | 105.35                   | 3011.79                   | 0.0643            | 1.97                                   |

| 0.1         | 58.99                   | 2305.85                     | 110.93                   | 3091.84                   | 0.049             | 1.89                                   |

| 0.3         | 59.73                   | 2336.04                     | 112.02                   | 3109.72                   | 0.0450            | 1.39                                   |

| 0.5         | 59.75                   | 2349.75                     | 112.60                   | 3141.98                   | 0.0430            | 1.26                                   |

| 0.7         | 58.47                   | 2331.26                     | 113.15                   | 3144.28                   | 0.0424            | 1.25                                   |

| 1.0         | 56.56                   | 2329.83                     | 111.65                   | 3123.42                   | 0.0388            | 1.18                                   |

**Fig. 4** Flexural modulus of f-MWCNT/PMMA composites as a function of wt% of f-MWCNTs

**Fig. 5** Impact strength of f-MWCNT/PMMA composites as a function of wt% of f-MWCNTs

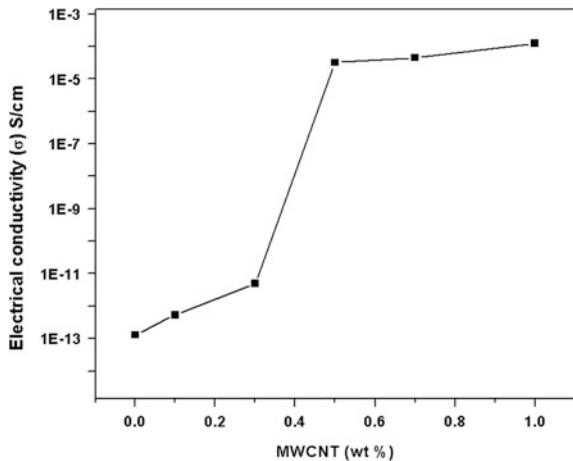

Electrical properties of nanocomposites generally depend upon the structure, extent of dispersion, and particle size of conducting fillers along with the properties of host polymers. The conductivity of nanocomposites found to be increased with the increasing f-MWCNTs wt% in the composites as shown in Fig. 7.

The conductivity of PMMA is about  $1.3 \times 10^{-13}$  S/cm in the initial stage, and this is consistent with the magnitude of an insulator. At slightly higher filler concentration, the nanocomposites experience a transition from low conductivity to a rapid increase in conductivity. The sharp increase in conductivity observed in case of PMMA/f-MWCNT nanocomposite as compared to virgin PMMA and it was due to the percolation threshold.

**Fig. 6** Impact energy of f-MWCNT/PMMA composites as a function of wt% of f-MWCNTs

**Fig. 7** Electrical conductivity of f-MWCNT/PMMA composites as a function of wt% of f-MWCNTs

The f-MWCNT/PMMA composite shows a very low percolation threshold for electrical conductivity due to high aspect ratio, nanoscale structure, and dispersion f-MWCNT in the polymer [19].

The Electrical conductivity versus f-MWCNT wt% was plotted at constant frequency of 1 MHz. The sharp increase in conductivity from 0.3 to 0.5 wt% is due to exceeding of percolation threshold value and leading to increased conductivity. At this stage, the conductivity of the nanocomposite material is about  $1.24 \times 10^{-4}$  S/cm, which is nearly consistent with that of a conductor. The PMMA/f-MWCNT nanocomposites exhibited a very low percolation threshold for electrical conductivity because of large surface area and the nanoscale dimension of f-MWCNTs.

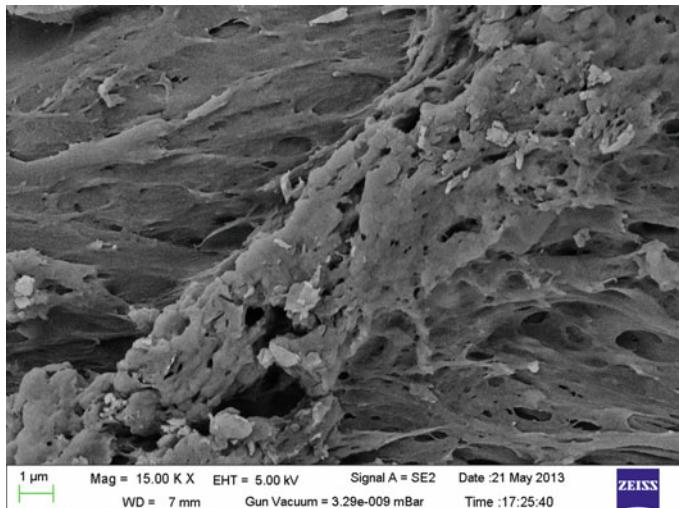

**Fig. 8** SEM image of f-MWCNT/PMMA composite with 0.3 wt% of f-MWCNTs

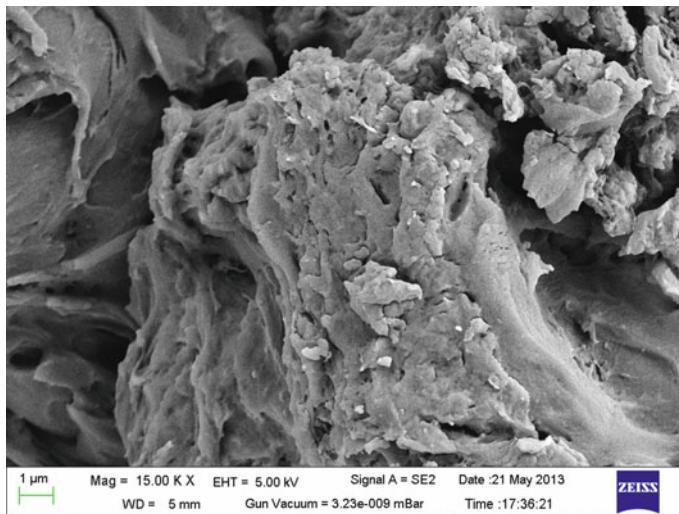

FESEM of the tensile cleavage of f-MWCNT/PMMA nanocomposite reinforced by 0.3 and 0.5 wt% of f-MWCNT is shown in Figs. 8 and 9. In Fig. 8, it is noticed that there is number of voids created in PMMA matrix, whereas these pores are minimized with the increase in percentage of f-MWCNT in 0.5% in Fig. 9. The average size of pores is 1  $\mu$ m. The nanodispersion of f-MWCNTs in the PMMA as in Fig. 9 shows lesser voids in composites. The lesser interfacial adhesion between f-MWCNT and PMMA matrixes and voids leads to local agglomeration of f-MWCNT on the matrix surface.

**Fig. 9** SEM image of f-MWCNT/PMMA composite with 0.5 wt% of f-MWCNTs

## 4 Conclusions

The tensile stress and modulus have been increased for the composites with the increase in percentage of the f-MWCNT. This trend is observed for up to a certain percentage with increase of f-MWCNT and then declined due to agglomeration in the viscous polymer. Similar fashion is also observed for flexural stress and flexural modulus. The impact test results show a declining trend of values for the increasing wt% of f-MWCNTs, showing that composites have low impact strength than pure polymer. The increase in electrical conductivity for 0.3–0.5 wt% addition of f-MWCNTs ascertains the electrical conductivity property of nanocomposite. The decrease in the mechanical strength after certain percentage of f-MWCNTs addition points toward the challenges in dispersion of CNTs.

## References

1. Singhal, S.K., and Renu Pasricha. 2011. Fabrication and characterization of Al-matrix composites reinforced with amino-functionalized carbon nanotubes. *Composites Science and Technology* 72: 103–111.

2. Prusty, G., and S.K. Swain. 2012. Dispersion of expanded graphite as nanoplatelets in a copolymer matrix and its effect on thermal stability, electrical conductivity and permeability. *New Carbon Materials* 27: 271–277.

3. Swain, Sarat K., Ajaya K. Pradhan, and Hari S. Sahu. 2013. Synthesis of gas barrier starch by dispersion of functionalized multiwalled carbon nanotubes. *Carbohydrate Polymers* 94: 663–668.

4. Salinier, Axel, and Sylvie Dagréou. 2013. Electrical, rheological and mechanical characterization of multiscale composite materials based on poly(etherimide)/short glass fibers/ multiwalled carbon nanotubes. *Composite Structures* 102: 81–89.

5. Pradhan, Ajaya K., and Sarat K. Swain. 2012. Electrical conductivity and oxygen permeability of polyacrylonitrile/multiwalled carbon nanotubes composites. *Polymer Composites* 33: 1114–1119.

6. Villnow, Tobias, Bernd Kretzschmar, and Petra Potschke. 2010. Influence of screw configuration, residence time, and specific mechanical energy in twin-screw extrusion of polycaprolactone/multi-walled carbon nanotube composites. *Composites Science and Technology* 70: 2045–2055.

7. Lee, Won-Jun, Sang-Eui Lee, and Chun-Gon Kim. 2006. The mechanical properties of MWNT/PMMA nanocomposites fabricated by modified injection molding. *Composite Structures* 76: 406–410.

8. Xiao-Feng Li, Kin-Tak Lau, and Yan-Sheng Yin. 2011. Mechanical properties of epoxy-based composites using coiled carbon nanotubes. *Composites Science and Technology* 68: 2876–2881.

9. González-Julian, J., Y. Iglesias, and A.C. Caballero. 2011. Multi-scale electrical response of silicon nitride/multi-walled carbon nanotubes composites. *Composites Science and Technology* 71: 60–66.

# Performance Analysis of Dual Metal Double Gate Tunnel-FETs for Ultralow Power Applications

D. Gracia and D. Nirmal

**Abstract** Dual metal double gate tunnel FET device has been presented to overcome the challenges in conventional TFET. This device gives a very good  $I_{on}/I_{off}$  ratio and an average subthreshold slope. The performance analysis is done for various values of oxide thickness and doping concentrations for the device. It has very low leakage current ( $9.27 \times 10^{-20} \text{ A}/\mu\text{m}$ ), a huge on-current ( $4.85 \times 10^{-7} \text{ A}/\mu\text{m}$ ),  $I_{on}/I_{off}$  ratio of  $10^{12}$ , and a steep subthreshold slope of 34 mV/dec.

**Keywords** Dual metal · Tunnel FET · High- $k$  dielectric · Subthreshold slope

## 1 Introduction

Tunnel field-effect transistors (TFETs) are the upcoming devices for its less leakage current and steep subthreshold slope and are much useful to applications which use less power [1–3]. TFETs are based on the passage of the majority charge carriers and an electric field formed in the channel region which is the switching mechanism for tunneling [2–5]. The conventional TFET is a p-i-n gated structure having non-uniformly doped source and drain, and the carrier passage takes place from one band to another.

The major challenges in TFET are small drive current and ambipolarity. To master these challenges, high- $k$  dielectrics in the double gate TFETs are proposed [6, 7]. It increases on-current and reduces the leakage current, and hence, on-to-off current ratio is increased [6]. Device analogue/RF characteristics are investigated for gate–drain underlap area [8]. The device uses non-local path (BTBT) model for

---

D. Gracia (✉) · D. Nirmal

Department of Electrical Technology, Karunya University, Coimbatore, India

e-mail: graciadevaraj@gmail.com

D. Nirmal

e-mail: nirmal@karunya.edu

simulation. Due to the tunneling process, the device requires a fine mesh around area where the switching mechanism takes place. In [9], the tunneling takes place from the source to drain depletion regions. The paper [10] discusses the device electrostatic role of three diverse TFET structures, i.e., tunnel FET with two gates, tunnel FET with different dielectrics, and tunnel FET with two metals with different dielectrics. The latter excels the other two TFET structures.

Several structures are proposed by the researches to enhance the on-current of the TFET. In [11–15, 16] dual-gate tunnel FET with different junction for applications that consumes less power is discussed. Vertical TFET with n- and p- type source underlapped structure with submicron 10-nm technology is discussed [17]. In [18], junctionless tunnel FET and [19] gate all around TFET have been discussed. In [20], a dopingless FET (DL-FET) source/drain (S/D) areas were created by metal work function engineering and show a fine control over short channel effects. The problem of ambipolarity is the device operates for both positive and negative values of gate voltage making the TFETs not suitable for digital circuits. Several techniques [21, 22] to control ambipolarity are reducing the drain electric field, reducing the doping concentration, and using large bandgap heterostructures in the drain end. Molybdenum has been shown as a potential candidate for the future metal gate technology in [23–25].

This paper deals with the performance analysis of dual metal double gate TFET for different doping concentrations, and oxide thickness has been analyzed. The dependence of on-current, off-current, SS on device parameters is studied in detail. Section 2 covers the structure design and simulation. Section 3 summarizes the findings and discussion. Section 4 provides the conclusion followed by acknowledgement and references.

## 2 Structure Architecture and Parameter Description

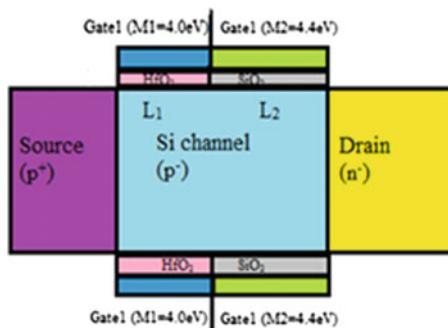

In Fig. 1, the 2-D structure of double metal dual-gate TFET is shown. The structure creation and the simulations are performed using Sentaurus Technology Computer-Aided Design (TCAD) software [26]. The gate oxide thickness ( $T_{ox}$ ) is 2 nm with channel thickness of 10 nm. Molybdenum and aluminum are used as metal with the minimum energy of 4.4 and 4.0 eV, respectively. In addition to conventional  $SiO_2$ , high- $k$  dielectric  $HfO_2$  is used as gate oxides. The source region is heavily doped with p-type material, while the drain is oppositely doped with n-type impurities. The most important models used for simulation are non-local BTBT model, bandgap narrowing model, SRH model. The transfer characteristics of dual metal gate with heterodielectric TFET have been investigated by varying doping concentrations and thickness of gate oxides.

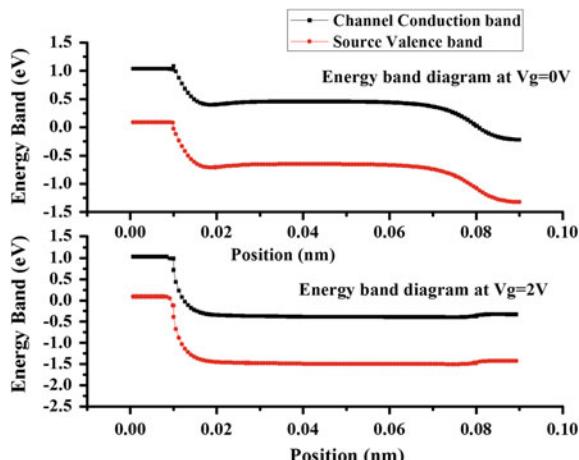

Table 1 gives the structure dimensions. Figure 2 gives the band diagram of the device in its active as well as in off state. The graph is plotted between the energy band and the position along the length of the device. In its put off state, tunneling

**Fig. 1** 2-D structure of dual metal double gate TFET

**Table 1** Device dimensions

| Parameter                          | Values                    |

|------------------------------------|---------------------------|

| Gate length ( $L_g$ )              | 50 nm                     |

| Oxide thickness ( $T_{ox}$ )       | 2 nm                      |

| Channel thickness ( $T_{si}$ )     | 10 nm                     |

| Source concentration ( $N_a$ )     | $1e^{20} \text{ cm}^{-3}$ |

| Channel concentration ( $N_{ch}$ ) | $1e^{15} \text{ cm}^{-3}$ |

| Drain concentration ( $N_d$ )      | $1e^{18} \text{ cm}^{-3}$ |

| Gate voltage ( $V_g$ )             | 2 V                       |

| Supply voltage ( $V_d$ )           | 0.5 V                     |

does not occur if the gate bias is very low due to the barrier width between the valence band of the source area and the conduction band of the channel area are high. Furthermore, in the active case, for positive gate bias, the barrier width, a potential boundary leading to tunneling of carriers, is reduced because the gate pulls down the barrier closer to each other.

**Fig. 2** Energy diagram of dual metal double gate TFET

### 3 Results and Discussion

#### 3.1 Transfer Characteristics

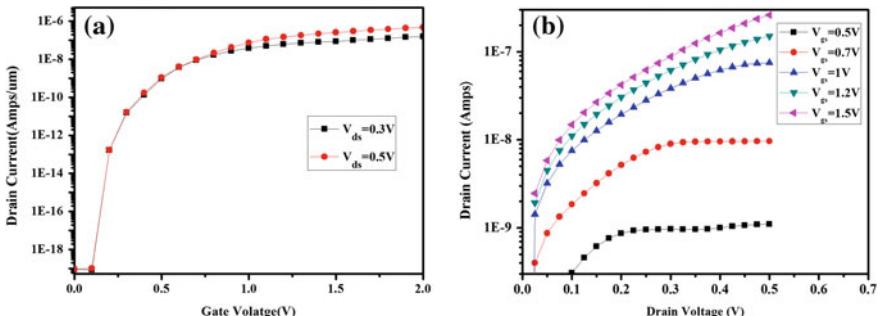

Figure 3a gives the dual metal double gate TFET transfer characteristics. The analysis has been carried out by swinging the  $V_g$  from 0 to 2 V, and the drain current variation is observed. The simulated on-current of the device is  $4.85 \times 10^{-7}$ , and the leakage current is  $9.27 \times 10^{-20}$  giving a very good  $I_{on}/I_{off}$  ratio in the order of  $10^{12}$  for a low supply voltage of  $V_{dd} = 0.5$  V. In TFET [27], BTBT is the primary device physics to be modeled. This is fundamental to all lateral BTBT devices. In the simple local BTBT model, the carrier generation rates are determined mainly from the local electric field only [27]. In one common expression, based on the Kane's derivation,

$$G^{\text{BTBT}} = A \cdot E^\alpha \exp\left(-\frac{B}{E}\right) \quad (1)$$

Figure 3b shows the  $I_d - V_d$  of the device. The analysis is carried out by swinging the drain voltage from 0 to 0.7 V for different gate voltages. The drain current is  $4.8457 \times 10^{-7}$  A.

#### 3.2 Steeper Switching Behavior

The subthreshold swing is the variation in voltage that is used in order to provide a change of one order of magnitude of the drain current. Subthreshold swing is given by

$$S = \frac{dv_g}{d(\log I_d)} [\text{mV/dec}] \quad (2)$$

Fig. 3 a  $I_d - V_d$  for different  $V_{ds}$ , b  $I_d - V_d$  for different  $V_{gs}$

The operating mechanism of MOSFET is based on thermionic injection where electrons travel over an energy barrier, which confines the SS by the Boltzmann distribution of charge to 60 mV/decade. For dual metal double gate TFET, sub-threshold swing is 34 mV/decade. Using high- $k$  in gate oxide provides a steeper slope.

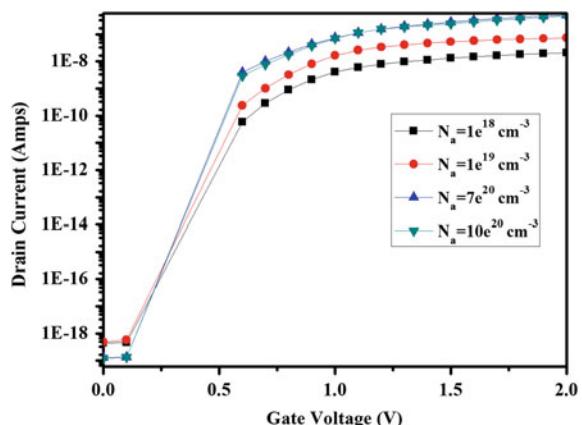

### 3.3 Effects of Various Doping Concentrations

Figure 4 shows the device characteristics for different doping concentrations. Doping concentration is proportional to on-current, and therefore, increasing source doping will enhance the drive current of the device even at low supply voltage, and hence, TFETs are promising candidates to low power applications.

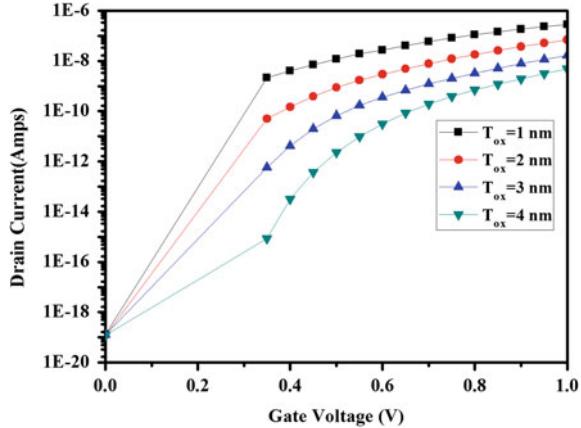

### 3.4 Effects of Different Oxide Thickness

Figure 5 shows the  $I_d - V_g$  for different oxide thickness keeping the supply voltage 0.5 V. Oxide thickness plays a vital role in the tunneling mechanism. According to the Eq. (3), the current in the active state (on-current) will increase by increasing the oxide thickness of the transistor.

$$I_d = \mu_n c_{\text{ox}} \frac{w}{l} \left[ \left( V_{\text{gs}} - V_t \right) V_{\text{ds}} - \frac{V_{\text{ds}}^2}{2} \right] \quad (3)$$

where mobility is given by  $\mu_n$ ,  $c_{\text{ox}}$  is the capacitance of the gate oxide,  $w/l$  is the scaling parameter.

**Fig. 4**  $I_d - V_g$  for different doping concentrations

**Fig. 5**  $I_d - V_g$  for different oxide thickness

where oxide capacitance is given by,

$$C_{ox} = \frac{\epsilon_{ox}}{t_{ox}} \quad (4)$$

## 4 Conclusion

The dual metal double gate TFET and their characteristics for different device parameter are discussed. This device gives excellent  $I_{on}/I_{off}$  ratio of  $10^{12}$  for a very small supply voltage of 0.5 V. Drive current can be increased by increasing the doping concentration and by using thin gate oxide. The dual metal double gate TFET device is a good candidate for applications that use less power. This work can be extended further by using Ge and III-V materials to enhance the mobility.

**Acknowledgements** The authors are very grateful for financially supporting this research under Visvesvaraya Ph.D. Scheme by Ministry of Electronics and Information Technology, Government of India, New Delhi. Also, we would like to thank Karunya University for providing laboratory facilities for this research.

## References

1. Seabaugh, A.C., and Q. Zhang. 2010. Low-voltage tunnel transistors for beyond CMOS logic. *Proceedings of the IEEE* 98 (12): 2095–2110.

2. Choi, W.Y., B.G. Park, J.D. Lee, and T.J.K. Liu. 2007. Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. *IEEE Electron Device Letters* 28 (8): 743–745.

3. Choi, W.Y., and W. Lee. 2010. Hetero-gate-dielectric tunneling fieldeffect transistors. *IEEE Transactions on Electron Devices* 57 (9): 2317–2319.

4. Ghosh, Bahniman, and Mohammad Waseem Akram. 2013. Junctionless Tunnel Field Effect Transistor. *IEEE Electron Device Letters* 34: 584–586.

5. Gandhi, Ramathan, Zhixian Chen, and Navab Singh. 2011. CMOS Compatible Vertical Silicon nanowire GAA p-type TFET with  $\leq 50$  mV/dec Sub threshold Swing. *IEEE Electron Device Letters* 32: 1504–1506.

6. Boucart, K., and A.M. Ionescu. 2007. Double-gate tunnel FET with high- $\kappa$  gate dielectric. *IEEE Transactions Electron Devices* 54 (7): 1725–1733.

7. Charles Pravin, J., D. Nirmal, P. Prajnoon, and J. Ajayan. 2016. Implementation of nanoscale circuits using dual metal gate engineered nanowire MOSFET with high-k dielectrics for low power applications. *Physica E Low-Dimensional Systems and Nanostructures* 83: 95–100.

8. Vijayvargiya, V.B.S., P. Singh Reniwal, and S.K. Vishvakarma. 2016. Analogue/RF performance attributes of underlap tunnel field effect transistor for low power applications. *Electronics Letters* 52 (7): 559–560.

9. Prabhat, Vishwa, and Aloke K. Dutta. 2016. Analytical surface potential and drain current models of dual-metal-gate double-gate tunnel-FETs. *IEEE Transactions on Electron Devices* 63 (5): 2190–2196.

10. Upasana, Rakhi Narang, Manoj Saxena, and Mridula Gupta. 2015. Modeling and TCAD assessment for gate material and gate dielectric engineered TFET architectures: circuit-level investigation for digital applications. *IEEE Transactions on Electron Devices* 62 (10): 3348–3356.

11. Ahish, Shylendra, Dheeraj Sharma, Yernad Balachandra Nithin Kumar, and Moodabettu Harishchandra Vasantha. 2016. Performance enhancement of novel InAs/Si hetero double-gate tunnel FET using gaussian doping. *IEEE Transactions on Electron Devices* 63 (1): 288–295.

12. Ajayan, J., and D. Nirmal. 2015. A review of InP/InAlAs/InGaAs based transistors for high frequency applications. *Superlattices and Microstructures* 86: 1–19.

13. Sharma, A., A. Goud, and K. Roy. 2015. GaSb-InAs n-TFET with doped source underlap exhibiting low subthreshold swing at sub-10-nm gatelengths. *IEEE Electron Device Letters* 35 (12): 1221–1223.

14. Knoch, J., and J. Appenzeller. 2010. Modeling of high-performance p-type III–V heterojunction tunnel FETs. *IEEE Electron Device Letters* 3 (4): 305–307.

15. Verhulst, A.S., W.G. Vandenberghe, K. Maex, S. De Gendt, M. Heyns, and G. Groeseneken. 2008. Complementary silicon-based heterostructure tunnel-FETs with high tunnel rates. *IEEE Electron Device Letters* 29 (12): 1398–1401.

16. Jain, Prateek, Vishwa Prabhat, and Bahniman Ghosh. 2015. Dual metal-double gate tunnel field effect transistor with mono/hetero dielectric gate material. *Journal of computational electronics* 14 (2): 537–542.

17. Kim, Jang Hyun, Sang Wan Kim, Hyun Woo Kim, and Byung-Gook Park. 2015. Vertical type double gate tunnelling FETs with thin tunnel barrier. *Electronics Letters* 51 (9): 718–720.

18. Ghosh, B., and M.W. Akram. 2013. Junctionless tunnel field effect transistor. *IEEE Electron Device Letters* 34 (4): 584–586.

19. Lee, J.S., J.H. Seo, S. Cho, J. Lee, S. Kang, J. Bae, E. Cho, and I.M. Kang. 2013. Simulation study on effect of drain underlap in gate-all-around tunneling field-effect transistors. *Current Applied Physics* 13: 1143–1149.

20. Jagadesh Kumar, M., and Sindhu Janardhanan. 2013. Doping-less tunnel field effect transistor: design and investigation. *IEEE Transactions on Electron Devices* 60: 3285–3290.

21. Nigam, Kaushal, Pravin Kondekar, and Dheeraj Sharma. 2016. Approach for ambipolar behaviour suppression in tunnel FET by workfunction engineering. *Micro & Nano Letters* 11 (8): 460–464.

22. Anghel, Costin, Anju Gupta Hraziia, Amara Amara, and Andrei Vladimirescu. 2011. 30-nm tunnel FET with improved performance and reduced ambipolar current. *IEEE Transactions on Electron Devices* 58 (6): 1649–1654.

23. Kwasnick, R.F., E.B. Kaminsky, P.A. Frank, G.A. Franz, R.J. Saia, K.J. Polasko, and T.B. Gorczyca. 1988. An investigation of a molybdenum gate for submicrometer CMOS. *IEEE Transactions on Electron Devices* 35 (9): 1432–1438.

24. Saurabh, S., and M.J. Kumar. 2011. Novel attributes of a dual material gate nanoscale tunnel field-effect transistor. *IEEE Transaction Electron Devices* 58 (2): 404–410.

25. Lee, J.S., et al. 2003. Low-frequency noise characteristics of ultrathin body p-MOSFETs with molybdenum gate. *IEEE Electron Device Letters* 24 (1): 31–33.

26. TCAD Sentaurus Device Manual. 2010. *Synopsys Inc.* CA, USA: Mountain View.

27. Shen, C., L.T. Yang, E.-H. Toh, C.-H. Heng, G.S. Samudra, and Y.-C. Yeo. 2009. A new robust non-local algorithm for band-to-band tunneling simulation and its application to tunnel-FET. *Solid-State Electronics* 57 (1): 23–30.

# Films of Reduced Graphene Oxide-Based Metal Oxide Nanoparticles

Neena S. John, K. Bramhaiah, Indu Pandey and C. Kavitha

**Abstract** Functional materials based on reduced graphene oxide (rGO) and metal oxide nanoparticles possess superior properties arising from the synergy of the individual properties. Obtaining these materials in the form of large area films are advantageous for most applications involving sensing, photovoltaics, supercapacitors, etc. We have synthesized free standing, thin films of rGO with semiconductor nanostructures such as ZnO, CuO, SnO<sub>2</sub>, and magnetic nanoparticles such as Fe<sub>2</sub>O<sub>3</sub> at a liquid/liquid interface employing a simple interfacial reaction of the precursors. The method can be adopted as a general route to prepare rGO-based metal oxide films. rGO-ZnO films consist of hexagonal cylinders of ZnO, and rGO-Fe<sub>2</sub>O<sub>3</sub> films exhibit particle or rod-like morphologies of iron oxide interspersed with rGO layers. The applications of these hybrid films as renewable surface-enhanced Raman substrates (SERS) and supercapacitors are demonstrated. The higher photodegradation rates provided by the metal oxide-rGO hybrids enable regeneration of the used SERS substrate while the contribution from electric double layer capacitance of rGO and pseudocapacitance due to metal oxide enhances the charge storage in hybrids.

**Keywords** Reduced graphene oxide · Hybrid films · Metal oxides · SERS · Supercapacitor

## 1 Introduction

Nanoscale metal oxides is one of the most exciting and widely investigated research areas by the scientific community due to their remarkable applications in various fields such as pollutant removal, photovoltaics, photocatalysis, solar cells,

---

N. S. John (✉) · K. Bramhaiah · I. Pandey

Centre for Nano and Soft Matter Sciences, Jalahalli, Bangalore 560013, India

e-mail: jsneena@cens.res.in

C. Kavitha

BMS Institute of Technology, Yelahanka, Bangalore 560064, India

surface-enhanced Raman spectroscopy (SERS), and supercapacitors [1]. Combining graphene or its derivatives such as reduced graphene oxide (rGO) with metal oxides can offer materials with superior properties for the applications. rGO possess exceptional properties like high electrical conductivity, surface area, optical, mechanical, and thermal properties [1]. A variety of methods have been explored to synthesize rGO-based metal oxide composites such as solution-based methods, solvothermal, and sonochemical techniques [1]. Liquid/liquid interface method is one of the upcoming methods [2] and has not been explored to a great extent even though it has many advantages. The interface is a non-homogeneous and nanometer scale region, which is formed between two immiscible liquids consisting of polar and nonpolar solvents and provides a confined environment to self-assembly of materials at an interface. The assembly of nanostructures minimizes the interfacial energy, and hence, the formation of materials at the interface is thermodynamically favoured. This may be utilized to obtain large area, ultra-thin, self-assembled films of rGO with various inorganic nanostructures. The films obtained are free standing and enable facile transfer to any desired substrate depending on the envisaged application.

In this study, we exploit *in situ* interfacial reaction at the water/toluene interface for the synthesis of metal oxides and rGO-metal oxide hybrid films including ZnO, rGO-ZnO, Fe<sub>2</sub>O<sub>3</sub>, and rGO-Fe<sub>2</sub>O<sub>3</sub>. Here, GO acts as a surfactant to hold the metal oxide nanoparticles (NPs) at the interface and the NPs are seen well anchored on the surface of self-assembled rGO sheets at the interface. These large area ultra-thin films of rGO-metal oxides NPs are collected on various substrates for demonstration as promising SERS substrates that are renewable and electrode materials for supercapacitors. We have also synthesized rGO-CuO and rGO-SnO<sub>2</sub> NP hybrid films employing this method and demonstrated their potential as reusable SERS substrates for fluorescent analytes [3].

## 2 Experimental Details

### 2.1 Synthesis of rGO-Metal Oxide NP Films

The hybrid films of rGO-ZnO, rGO-CuO, rGO-SnO<sub>2</sub>, rGO-Fe<sub>2</sub>O<sub>3</sub> were prepared by taking the corresponding metal acetylacetone in toluene phase and GO along with hydrolyzing agent in the aqueous phase. Generally, the hydrolyzing agents used were KOH or ammonia, and in the case of Fe<sub>2</sub>O<sub>3</sub>, dimethylamine was used. In a few cases, a reducing agent, tetrakis(hydroxymethyl)phosphonium chloride (THPC) was also added in the aqueous phase to facilitate GO reduction. The whole system was heated at 90 °C in an oil bath for 2 h. After 1 h, an ultra-thin film of rGO-metal oxide NPs is observed at liquid/liquid interface. The films were collected on desired substrates after the toluene evaporation.

### 3 Results and Discussion

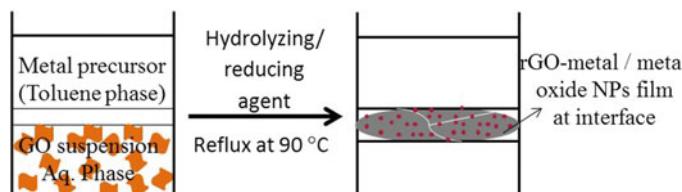

The liquid/liquid interface method for the synthesis of rGO-based metal oxide NP hybrid films involves taking a metal precursor in the organic phase over a GO dispersion along with the required reagent for interfacial reaction. The reduced GO adsorb the hydrolyzed metal ions followed by self-assembly at the interface. The hydrolysis and reduction of metal precursor and GO at the interface are facilitated by the increased thermal motion of reagent molecules during heating [4, 5]. Figure 1 displays the schematic of the method.

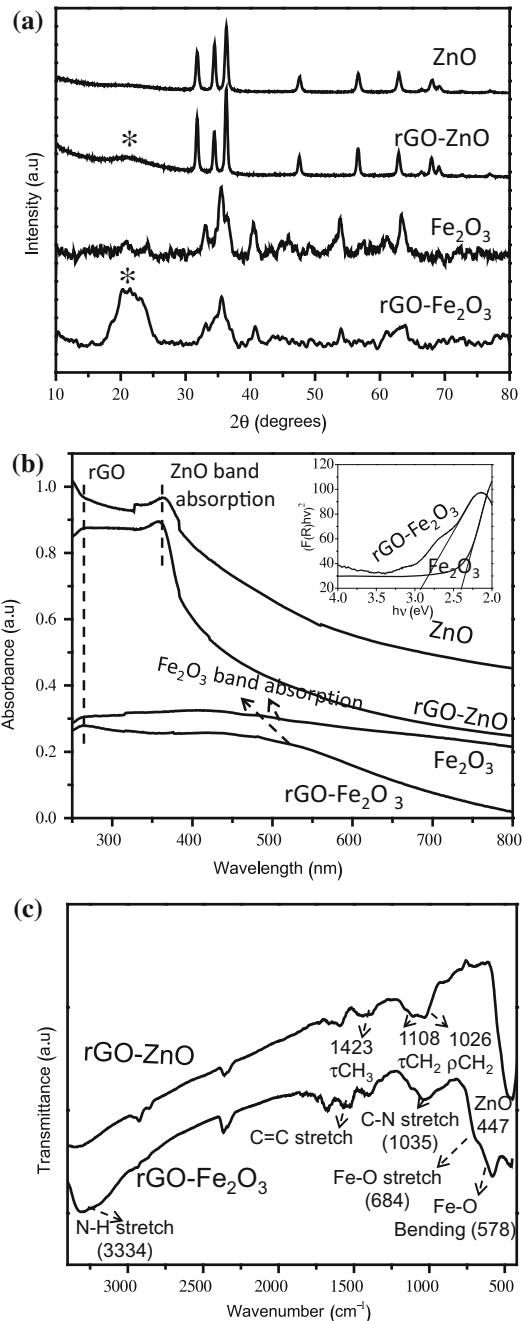

The crystal structure of hybrid films are studied by XRD and depicted in Fig. 2a. XRD patterns of ZnO and rGO-ZnO films confirm that ZnO has crystalline nature and the peaks at  $31.8^\circ$  (100),  $34.4^\circ$  (002),  $36.3^\circ$  (101),  $47.6^\circ$  (102),  $56.7^\circ$  (110),  $62.9^\circ$  (103),  $66.4^\circ$  (200),  $67.9^\circ$  (112),  $69.2^\circ$  (201),  $72.7^\circ$  (004), and  $77^\circ$  (202) correspond to hexagonal wurtzite structure of ZnO.  $\text{Fe}_2\text{O}_3$  films and rGO- $\text{Fe}_2\text{O}_3$  hybrid films show peaks corresponding to a mixture of  $\alpha$  and  $\gamma$  phases,  $33.2$  ( $\alpha$ 104),  $35.6$  ( $\gamma$ 311),  $40.5$  ( $\alpha$ 113),  $53.7$  ( $\gamma$ 422),  $62.5$  ( $\alpha$ 214), and  $62.9$  ( $\gamma$ 440). In the case of rGO-metal oxide hybrid films, a broad amorphous peak is observed at  $23^\circ$  due to exfoliated rGO layers. The optical absorption of as-synthesized hybrid films are given in Fig. 2b, and ZnO, rGO-ZnO,  $\text{Fe}_2\text{O}_3$ , and rGO- $\text{Fe}_2\text{O}_3$  exhibit the absorption bands at 350, 360, 414, and 476 nm, respectively. The band edge absorption for ZnO and rGO-ZnO are close to that seen for bulk ZnO (370 nm). In the case of rGO-metal oxides, the absorption extended into the visible region due to the presence of rGO layers. The  $\pi-\pi^*$  transition of rGO absorption is seen at 265 nm. Inset of Fig. 2b shows the Tauc plot of  $\text{Fe}_2\text{O}_3$  and rGO- $\text{Fe}_2\text{O}_3$  films. The band gap values are in the range of 2.4 and 2.9 eV, respectively. The band gap values are higher than the bulk  $\text{Fe}_2\text{O}_3$  (2.1 eV). FTIR spectra of hybrid films (Fig. 2c) show signatures of acetylacetone and dimethylamine in addition to rGO and metal oxide features. In the case of rGO-ZnO film, the band at  $447\text{ cm}^{-1}$  corresponds to ZnO vibration and the other vibrational bands around  $1026$ ,  $1108$ ,  $1423\text{ cm}^{-1}$  correspond to the  $\rho\text{CH}_2$ ,  $\tau\text{CH}_2$ ,  $\tau\text{CH}_3$ , of acetylacetone, respectively. In the case of rGO- $\text{Fe}_2\text{O}_3$  hybrid film, two major broad peaks at  $460$  and  $580\text{ cm}^{-1}$  correspond to Fe–O bending and stretching vibration modes of  $\text{Fe}_2\text{O}_3$  and the bands at  $3334$  and  $1035\text{ cm}^{-1}$  belong to the N–H and C–N stretching vibrational modes of dimethylamine. This indicates that ligands from the precursors attach to metal oxide

**Fig. 1** Pictorial presentation of the liquid/liquid interface method for the preparation of rGO-metal oxide NP hybrid films

**Fig. 2** **a** XRD patterns; \*amorphous peak of rGO, **b** UV-visible absorption spectra; inset shows the Tauc plots for band gap determination of  $\text{Fe}_2\text{O}_3$  and rGO- $\text{Fe}_2\text{O}_3$ , **c** FTIR spectra of the as-synthesized hybrid films ZnO, rGO-ZnO,  $\text{Fe}_2\text{O}_3$ , and rGO- $\text{Fe}_2\text{O}_3$  prepared by liquid/liquid interface method

nanostructures during their formation. The band at 1580–1600 cm<sup>−1</sup> is observed in both the cases, which is C=C stretching vibration of rGO.

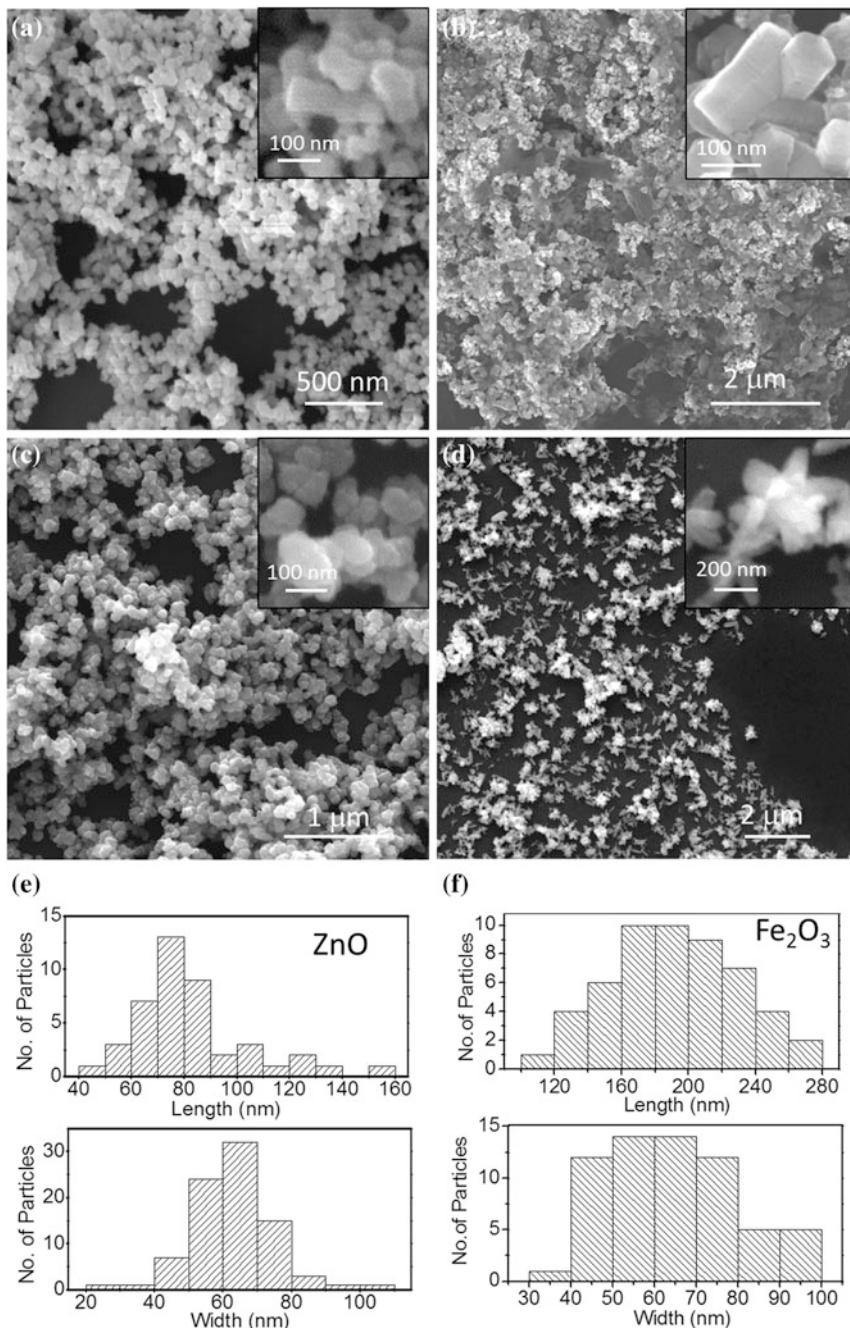

Surface morphology of as-synthesized films of ZnO, rGO-ZnO, Fe<sub>2</sub>O<sub>3</sub>, and rGO-Fe<sub>2</sub>O<sub>3</sub> NPs are given in Fig. 3. Figure 3a shows the bare ZnO NPs, which are hexagonal in shape and majority of them are seen stacked together to form a cylindrical shape. In the case of rGO-ZnO (Fig. 3b), the hexagonal cylindrical ZnO NPs are well anchored on the surface of the rGO sheets. The dimensions of ZnO NPs are highly polydisperse and are in the range of 70–90 nm in width and 50–80 nm in length (Fig. 3e). The inset of Fig. 3b shows a magnified image of one such ZnO cylinder. Bare Fe<sub>2</sub>O<sub>3</sub> films show small Fe<sub>2</sub>O<sub>3</sub> NPs (Fig. 3c) that are aggregated and interconnected to form dendritic network structures. In the case of rGO-Fe<sub>2</sub>O<sub>3</sub> (Fig. 3d), Fe<sub>2</sub>O<sub>3</sub> particles are rod-shaped and aggregates of nanorods (NRs) form flower-like structures on rGO layers. The length and width of Fe<sub>2</sub>O<sub>3</sub> NRs on the rGO are 120–240 nm and 40–80 nm, respectively (Fig. 3f).

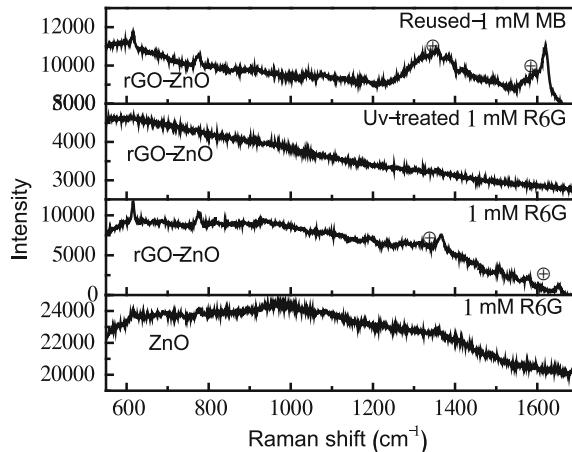

The potential application of rGO-zinc oxide hybrid films as reusable SERS substrates has been explored and is shown in Fig. 4. We have examined Raman spectra of Rhodamine 6G (R6G) as a fluorescent analyte. Figure 4 shows Raman spectra of 1 mM R6G adsorbed on the surface of bare ZnO and rGO-ZnO NPs coated on glass substrates (10 μL of 1 mM R6G was drop cast on the film, washed and dried). Raman band signatures of R6G are seen at 623, 784, and 1184 cm<sup>−1</sup>, corresponding to the in-plane C–C–C ring, out of plane C–H bending and C–C stretching vibrational bands of R6G, respectively. The Raman bands at 1314, 1368, 1523, 1592, and 1647 cm<sup>−1</sup> correspond to the C–C stretching vibrations of R6G [6]. R6G Raman bands on rGO-ZnO hybrid film appear significantly enhanced compared with that of bare ZnO NPs film with a slight suppression in the fluorescence background. The enhancement is attributed to the synergic contribution between rGO and metal oxide NPs, and also charge transfer between the analytes, rGO, and metal oxide NPs. The possible charge transfer pathways are (1) photoexcitation of electrons in ZnO to the defect levels by visible light radiation, which is employed for Raman scattering and further transfer to LUMO of analyte molecules (2) photoexcitation of electrons in HOMO-LUMO levels of dye molecules by visible light and further transfer to the conduction band of ZnO or rGO, which leads to the quenching of the fluorescence of the analytes and enhancing the Raman bands. In the case of rGO-ZnO NP hybrid film, the remnant oxygen functional groups present on the rGO sheets can enhance the local electric field, which also contributes to the enhancement in Raman bands in addition to charge transfer that leads to the suppression in the fluorescence of the analyte. To know the quantitative enhancement in the Raman bands of R6G on the hybrid films, enhancement factor (EF) has been calculated from the following equation [6].

$$EF = I_{SERS}/I_{\text{Bulk}} \times N_{\text{Bulk}}/N_{\text{SERS}},$$

where  $N_{\text{bulk}}$  is the number of the probe molecules under laser illumination in the bulk sample and  $N_{\text{SERS}}$  is the number of the molecules probed on the hybrid nanoparticle substrate, respectively.  $I_{\text{SERS}}$  and  $I_{\text{bulk}}$  are the vibrational intensities of

**Fig. 3** Surface morphology of metal oxide and rGO-metal oxide hybrid films prepared by interfacial reaction **a** ZnO NPs, **b** rGO-ZnO NPs, **c** Fe<sub>2</sub>O<sub>3</sub> NPs and **d** rGO-Fe<sub>2</sub>O<sub>3</sub> NPs; insets show the magnified FESEM images, **e** Hexagonal ZnO particles size distribution histogram, **f** Fe<sub>2</sub>O<sub>3</sub> nanorods size distribution histogram

**Fig. 4** SERS spectra of 1 mM R6G adsorbed on the surface of bare ZnO and rGO-ZnO NP hybrid film coated on glass substrate along with reusability of rGO-ZnO hybrid film as SERS substrate (⊕Raman bands of rGO)

R6G with excitation of 532 nm laser. The calculated EF values are  $\sim 4.15 \times 10^2$  for rGO-ZnO NP hybrid and  $\sim 9.5 \times 10^1$  for bare ZnO NPs film (1 mM R6G). We have studied the reusability of the rGO-ZnO NP hybrid film as a SERS substrate for various analytes, R6G, and methylene blue (MB). It has already been shown that when ZnO nanoparticles are combined with rGO, the recombination rates of photogenerated electrons and holes can be suppressed, which are further available for degradation of dyes. Thus, the photocatalytic efficiency of rGO-ZnO is much higher than bare ZnO [7]. This has been exploited to achieve renewable SERS substrates by degradation of adsorbed dye molecules. The surface of rGO-ZnO hybrid films is irradiated with UV light (365 nm) for 30 min in wet condition to regenerate the fresh surface. SERS spectra of R6G before and after photodegradation along with that of MB dye adsorbed on the regenerated substrate are also shown in Fig. 4. After UV light irradiation, the signatures of R6G disappeared and only a featureless background is observed. The regenerated surface is used for the detection of another dye, MB. The signatures of MB are clearly seen in the Raman spectra. A similar trend is observed in the case of rGO-CuO and rGO-SnO<sub>2</sub> NP hybrid films.

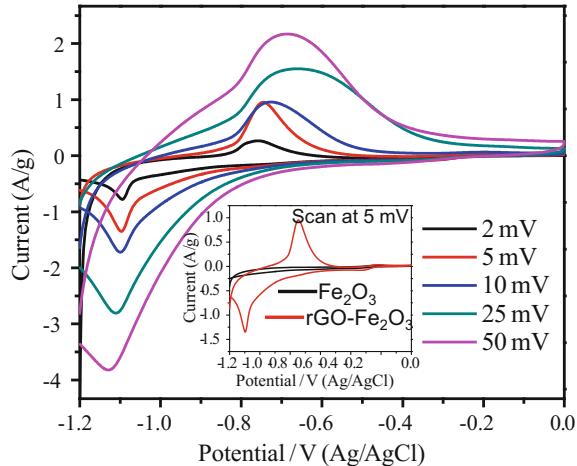

The capacitive behavior of Fe<sub>2</sub>O<sub>3</sub> and rGO-Fe<sub>2</sub>O<sub>3</sub> films is studied by cyclic voltammetry (CV) in 2 M KOH aqueous electrolyte at room temperature using three electrode systems. For this, the films were coated on to pencil graphite and are used as working electrodes. CV measurements were performed at various scan rates in the potential window, -1.2 to 0 V (vs. Ag/AgCl) and are shown in Fig. 5. The cyclic voltammetry graphs exhibit distinct redox peaks in the anodic and cathodic sweep within the voltage range of -1.2 to 0 V. The redox peaks are well defined in the rGO-Fe<sub>2</sub>O<sub>3</sub> hybrid films compared with the bare Fe<sub>2</sub>O<sub>3</sub> film (see inset of Fig. 5). The redox peaks arise because of the reversible conversion of iron oxidation states  $\text{Fe}^{2+} \leftrightarrow \text{Fe}^{3+}$  [8]. The charge storage process is due to the diffusion of K<sup>+</sup> or H<sub>3</sub>O<sup>+</sup> ions and e- within Fe<sub>2</sub>O<sub>3</sub> contributing to pseudocapacitance. The effect of scan rate has also been investigated, we observe that the current density and the area under the redox peaks increase with increasing scan rate, which indicates the fast diffusion

**Fig. 5** CV graphs of rGO-Fe<sub>2</sub>O<sub>3</sub> hybrid films coated on to pencil graphite electrodes with various scan rates; Inset of Fig. 5 shows the CV of bare Fe<sub>2</sub>O<sub>3</sub> and rGO-Fe<sub>2</sub>O<sub>3</sub> NRs at a scan rate of 5 mV/s

of electrolyte ions onto the surface of electrode materials. In the case of rGO-Fe<sub>2</sub>O<sub>3</sub> NR hybrid film, the area under the curve (inset of Fig. 5) is much higher than the bare Fe<sub>2</sub>O<sub>3</sub> NPs. The specific capacitance has been calculated from the CV curves of hybrid films using the  $C = a/2mv\Delta V$ , where  $a$  is the integrated area of the CV cycle,  $m$  is the mass of the electrode material (g),  $v$  is the scan rate (V/s), and  $\Delta V$  is the potential voltage window [9]. At a scan rate of 2 mV/s, the values for bare Fe<sub>2</sub>O<sub>3</sub> and rGO-Fe<sub>2</sub>O<sub>3</sub> NR hybrid are 9.8 and 47.5 F/g, respectively. A higher capacitance is observed in the case of rGO-Fe<sub>2</sub>O<sub>3</sub>, which is  $\sim$  fivefold higher than the bare Fe<sub>2</sub>O<sub>3</sub>. This is due to the synergic property between the rGO and Fe<sub>2</sub>O<sub>3</sub> arising from contributions due to double layer capacitance of rGO and pseudocapacitance of Fe<sub>2</sub>O<sub>3</sub> NRs. rGO also provides large surface area and aids in the transport of electrons from Fe<sub>2</sub>O<sub>3</sub> to the current collector.

#### 4 Conclusion

We have demonstrated a general route to prepare rGO-based metal oxide hybrid films employing liquid/liquid interface method. The free-standing films formed at the interface are thin, uniform, and are transferable to any desired substrates. The morphologies of metal oxide nanostructures are found to vary with the type of metal oxide involved. rGO-ZnO and rGO-Fe<sub>2</sub>O<sub>3</sub> films have been demonstrated as reusable SERS substrates and electrode materials for supercapacitors, respectively. SERS enhancement factor for rGO-ZnO is  $4.15 \times 10^2$  for R6G dye, and the surface has been regenerated by UV exposure for probing a different dye. rGO-Fe<sub>2</sub>O<sub>3</sub> films exhibit fivefold higher capacitance than the bare Fe<sub>2</sub>O<sub>3</sub> film. The synergic effect between the rGO and metal oxide plays important role in the enhanced performances.

## References

1. Khan, M., M.N. Tahir, S.F. Adil, H.U. Khan, M.R.H. Siddiqui, A.A. Al-warthan, and W. Tremel. 2015. Graphene based metal and metal oxide nanocomposites: synthesis, properties and their applications. *Journal of Materials Chemistry A* 3: 18753–18808.

2. Rao, C.N.R., G.U. Kulkarni, V.V. Agrawal, U.K. Gautam, M. Ghosh, and U. Tumkurkar. 2005. Use of the liquid-liquid interface for generating ultrathin nanocrystalline films of metals, chalcogenides, and oxides. *Journal of Colloid and Interface Science* 289: 305–318.

3. Bramhaiah, K., V.N. Singh, C. Kavitha, and N.S. John. 2017. Films of reduced graphene oxide with metal oxide nanoparticles formed at a liquid/liquid interface as reusable surface enhanced Raman scattering substrates for dyes. *Journal of Nanoscience and Nanotechnology* 17: 2711–2719.

4. Bramhaiah, K., and N.S. John. 2013. Hybrid films of reduced graphene oxide with noble metal nanoparticles generated at a liquid/liquid interface for application in catalysis. *RSC Advances* 3: 7765–7773.

5. Bramhaiah, K., and N.S. John. 2014. Reduced graphene oxide based silver sulfide hybrid films formed at a liquid/liquid interface. *AIP Conference Proceedings* 1591: 366–368.

6. Kavitha, C., K. Bramhaiah, N.S. John, and B.E. Ramachandran. 2015. Low-cost, ultrathin films of reduced graphene oxide-Ag nanoparticle hybrid as SERS based excellent dye sensors. *Chemical Physics Letters* 629: 81–86.

7. Bramhaiah, K., V.N. Singh, and N.S. John. 2016. Hybrid materials of ZnO nanostructures with reduced graphene oxide and gold nanoparticles: Enhanced photodegradation rates in relation to their composition and morphology. *Physical Chemistry Chemical Physics: PCCP* 18: 1478–1486.

8. Nithya, V.D., and N.S. Arul. 2016. Review on  $\alpha$ -Fe<sub>2</sub>O<sub>3</sub> based negative electrode for high performance supercapacitors. *Journal of Power Sources* 327: 297–318.

9. Chen, W., Z. Fan, L. Gu, X. Bao, and C. Wang. 2010. Enhanced capacitance of manganese oxide via confinement inside carbon nanotubes. *Chemical Communications* 46: 3905–3907.

# Size Optimization of InAs/GaAs Quantum Dots for Longer Storage Memory Applications

V. Damodaran and Kaustab Ghosh

**Abstract** A theoretical model and simulation is presented to express the electron and hole dynamics in InAs/GaAs quantum dots (QDs). For a fixed aspect ratio of 0.3, quantized energy states were computed using eight-band k.p model by varying the QD size and for different operating temperatures. Computational results show alteration in the dynamical behaviour at different temperatures. We obtained longer electron storage capability for 20 nm dot as compared to holes at room temperature operation. However, due to slower tunnelling rate at cryogenic temperatures within 20–50 K, smaller-sized QDs of 12 nm are suitable for memory devices in information storage for greater time span.

**Keywords** Quantum dots · Memory devices · Carrier dynamics

Theoretical model

## 1 Introduction

Self-assembled quantum dots (QDs) gained prominence over the years due to its special characteristics such as three-dimensional quantum confinement, ‘delta-like’ density of states and size-dependent optical spectra. All these qualities are utilized for fabricating high-performance lasers, photodetectors and solar cells [1–6]. However, a new application and research in data processing and data storage is witnessed for QDs in the last decade, and this function is utilized in the generation of memory devices [7–13]. The QDs in the memory devices can be employed to store information or data in the form of charge carriers. Carriers stored in the QD can escape through thermal and tunnelling emissions, and the rate of these emissions is the key parameters that describe memory performance in terms of its data retention potentiality. Hence, in this paper, theoretical modelling and simulation is

---

V. Damodaran · K. Ghosh (✉)

School of Electronics Engineering (SENSE), VIT University, Chennai, India

e-mail: kaustabghosh@gmail.com; kaustab@vit.ac.in

presented to describe the carrier flow dynamics in InAs/GaAs QD and understand its information storage capability. The aim of this work is to optimize the performance of the device and design superior quality memory devices.

It is well known that the control over the dimensions of nanostructures can be employed to engineer the material properties for specific applications. Hence, change in the size of the dots can be utilized to alter the confinement potential which causes a change in the charge emission characteristics. This in turn leads to the change in the data retention capability for memories. In view of the same, we have carried out a comparative analysis on the emission characteristics for electron and holes in different-sized QDs. Arrhenius plots for the same are computed to elucidate the effects of temperature which are analysed and discussed.

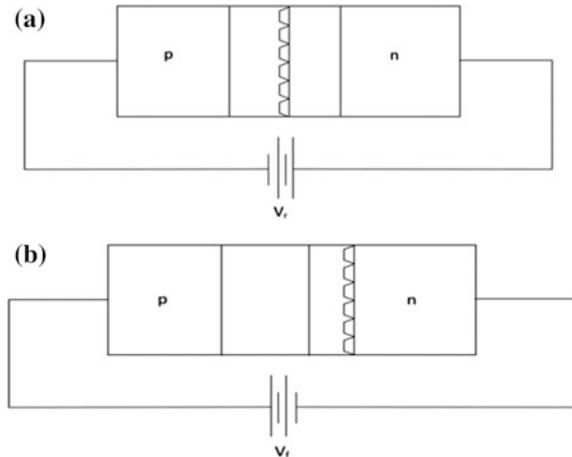

## 2 Theoretical Model

We developed our theoretical model for a truncated pyramidal InAs/GaAs QDs which are embedded in the depletion region of a reverse-biased *p*-*n* junction diode as shown in Fig. 1a. We assumed a forward pulse of 20 ms which reduces the depletion width of the diode. For a *p*<sup>+</sup>-*n* diode structure, forward biasing places the QD layer inside the *n*-type region of the diode as shown in Fig. 1b. This cause the capture of the majority carrier electrons in the dot, and the rate of capture is given by [13]

$$c_n = \gamma_n X \sigma_{\text{th}}^n T^2 \exp\left(-\frac{\Delta E_c}{k_B T}\right) \quad (1)$$

where *X* is the spin degeneracy factor,  $\sigma_{\text{th}}^n$  is the capture cross section for electrons,  $\Delta E_c$  is the change in the conduction band energy at the interface of the dot and the barrier material, and  $\gamma_n$  is a temperature-independent constant given by

$$\gamma_n = \sqrt{2(2\pi)^3 (k_B^2/h^3) M_c m_e^*} \quad (2)$$

where  $M_c$  is the number of conduction band minima and  $m_e^*$  is the electron effective mass.

For a *n*<sup>+</sup>-*p* diode, forward biasing places the dot in the *p*-side of the diode and causes hole capture into the dot, the rate of which is given by

$$c_p = (\gamma_p/X) \sigma_{\text{th}}^p T^2 \exp\left(-\frac{\Delta E_v}{k_B T}\right) \quad (3)$$

where  $\Delta E_v$  is the change in the valence band energy at the dot-barrier interface.

After the forward bias pulse, captured electron in the dot escapes from the QD through thermal and tunnelling emissions.

**Fig. 1** **a** Schmatic sketch of the reverse baised  $p$ - $n$  junction diode with InAs/GaAs QDs embedded in the depletion layer. **b** Forward biased diode  $p^+$ - $n$  diode which places the QDs in the  $n$ -region for carrier capture

The thermal emission of electrons from the QD is given by [7]

$$e_{th} = \gamma_n X \sigma_{th}^n T^2 \exp\left(-\frac{E_A}{k_B T}\right) \quad (4)$$

Here in Eq. (4),  $E_A$  is the activation energy of the electron which is defined as the energy difference between the conduction band of the barrier and the quantized energy state of the electron. We have used eight-band k.p model to compute the quantized state of the electrons and hole. The computation was performed using Tiber CAD simulation software.

In the similar manner, thermal emission for holes can also be computed as Eq. (4) by considering the capture cross section  $\sigma_{th}^p$ , temperature-dependent constant  $\gamma_p$  and the activation energy for holes.

Apart from thermal emission, electrons can also undergo quantum mechanical tunnelling emission from the QD. One such emission is the direct tunnelling through the one-dimensional triangular potential barrier from the QD, the rate of which is given by [13]

$$e_{dt} = \frac{qF}{4\sqrt{2m_e^* E_A}} \exp\left(-\frac{4}{3} \sqrt{\frac{2m_e^* E_A^{3/2}}{\hbar^2 qF}}\right) \quad (5)$$

where 'F' is the applied electric field.

Another is the phonon-assisted tunnelling in which electron from the lower quantized state is excited to the highest bound state thermally and then tunnels through the barrier layer. The phonon-assisted tunnelling rate is given by [11]

$$e_{\text{pht}} = \gamma_n X \sigma_{\text{tun}}^n T^2 \int_0^{E_A} \exp \left[ (-E_A/k_B T) + \left( 4\sqrt{2m_e^* E_B^{3/2}} / 3\hbar q F \right) \right] dE_A \quad (6)$$

Here in Eq. (6),  $E_A$  is the energy difference between the lower quantized state and the highest bound state of the QD, and  $E_B$  the barrier energy which is to be ascertained from the highest bound state to the conduction band edge.

The total emission rate of electrons from the QD can be expressed as

$$e_{\text{tot}} = e_{\text{th}} + e_{\text{dt}} + e_{\text{pht}} \quad (7)$$

### 3 Results and Discussions

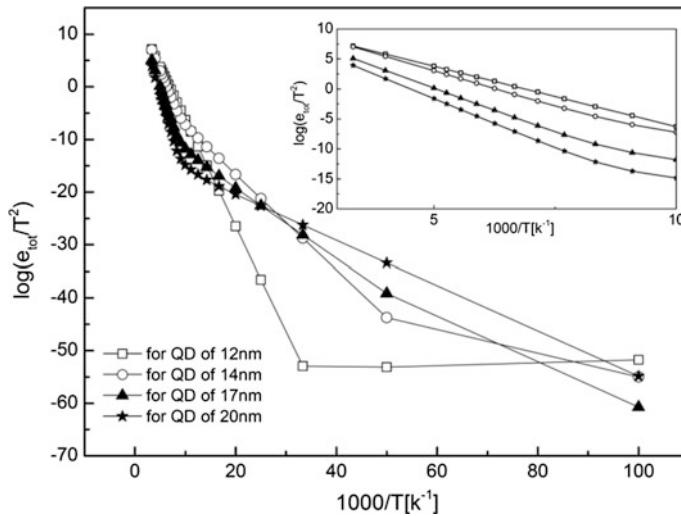

Arrhenius plots of electron emission for QDs of different size are presented in Fig. 2 for temperature ranging from 10 to 300 K. The emission curve for QD size of 14 nm is seen to flatten at lower temperature range of  $30 \leq 1000/T \leq 100$  which can be ascribed to the temperature-independent direct tunnelling from the QDs. For higher temperatures  $1000/T \leq 30$ , the curve is seen to increase with a particular slope. This can be ascribed to the overriding of thermal emission over tunnelling in the aforesaid temperature range. The emission curve slope for QDs of other three sizes is seen to increase with increase in temperature. This can be attributed to the dominance of phonon-assisted tunnelling at lower temperatures followed by thermal emission at higher temperatures. The inset in Fig. 2 shows the Arrhenius plots at the higher temperature side from  $1000/T \leq 10$ . In this temperature range, it can be seen that the large-sized QD of 20 nm base dimension is having the lowest emission rate. This is due to the largest confinement potential of the electron captured in this dot as compared to the other dot sizes. Defining the storage time as the inverse of emission rate, it can thus be inferred that at room temperature, larger QD size can be suitably utilized for fabricating memory devices having longer duration data storage capacity. We have not considered dot size larger than 20 nm as it might lead to coalescence of dots and structural defects. However, with decrease in temperature for  $20 \leq 1000/T \leq 80$ , the emission rate for 20-nm dot increases compared to the other QD, and it can be seen that the smaller QD size of 12 nm is having the least emission rate. This attributes to the suitability of smaller-sized QDs for better memory applications at cryogenic temperatures.

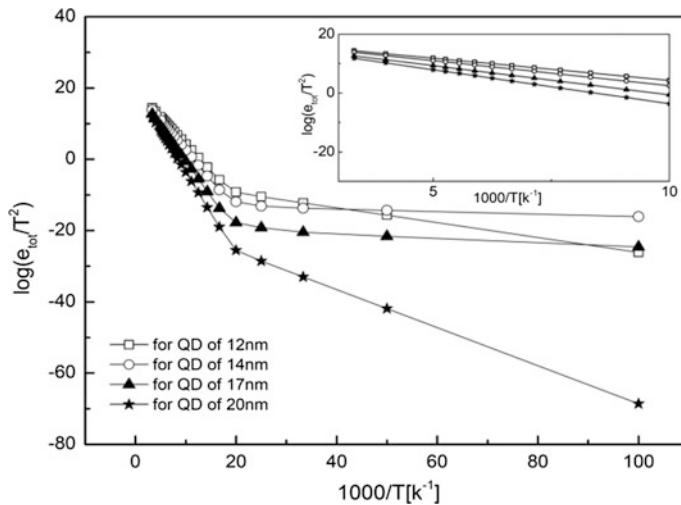

Arrhenius plot for hole emission from the InAs/GaAs QD is depicted in Fig. 3. The inset in the figure shows the same at the higher temperature range, which also portrays lowest emission rate for holes for larger-sized QD of 20 nm dimension. Even at lower temperatures, unlike that of electrons, the emission rate from this QD is the least. Hence, it can be inferred that QDs having larger dimension are

**Fig. 2** Arrhenius plot for electron emission rate for QDs of different base dimensions

**Fig. 3** Arrhenius plot for hole emission rate for QDs of different base dimensions

preferable for longer duration information storage in the form of holes at all temperatures.

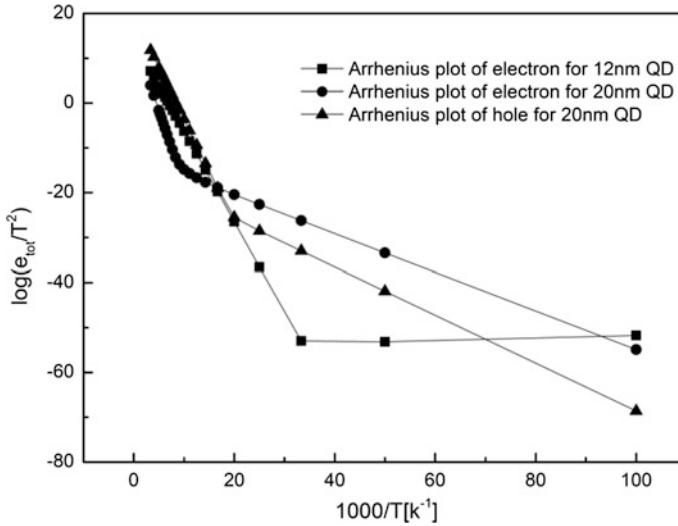

Comparison of Arrhenius plot of the electron emission rates for QD size of 20 nm, 12 nm and hole emission for 20-nm QD is presented in Fig. 4. It can be seen that the electron emission is lesser than holes at room temperature for 20-nm dot. With decrease in temperature for  $20 \leq 1000/T$ , electron emission increases as

**Fig. 4** Comparison on the Arrhenius plot for electrons and holes for different-sized QDs

compared to holes. However, electron emission for 12-nm dot is lesser than holes in the temperature range  $20 \leq 1000/T \leq 50$ . Thus, from this study, it can be surmised that for InAs/GaAs QD, electrons are preferable than holes for longer storage duration memory devices for a broad range of temperature from 20 to 300 K. Larger-sized QDs is more suited for room temperature memory device, whereas smaller size is suitable for cryogenic devices [14] operating within 20–50 K.

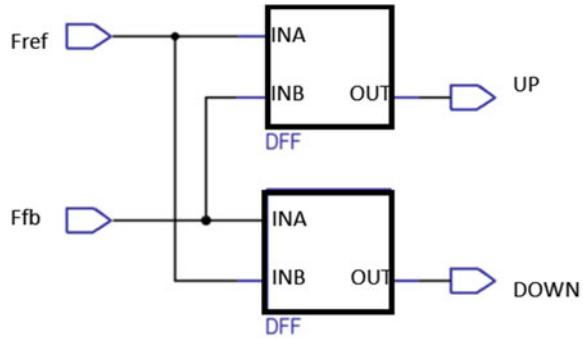

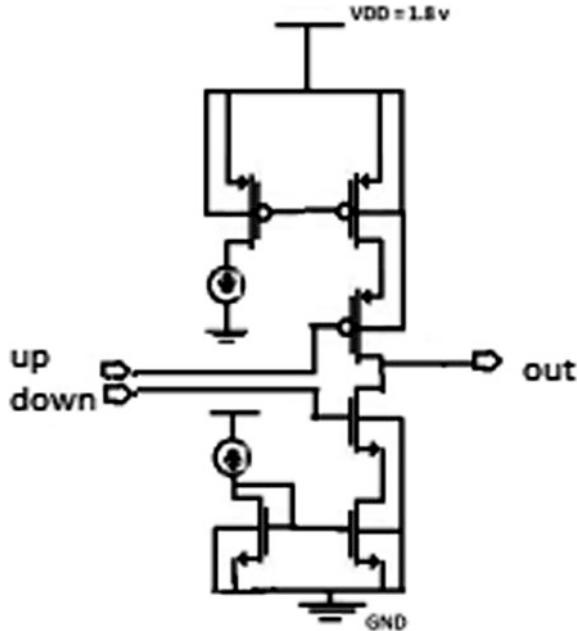

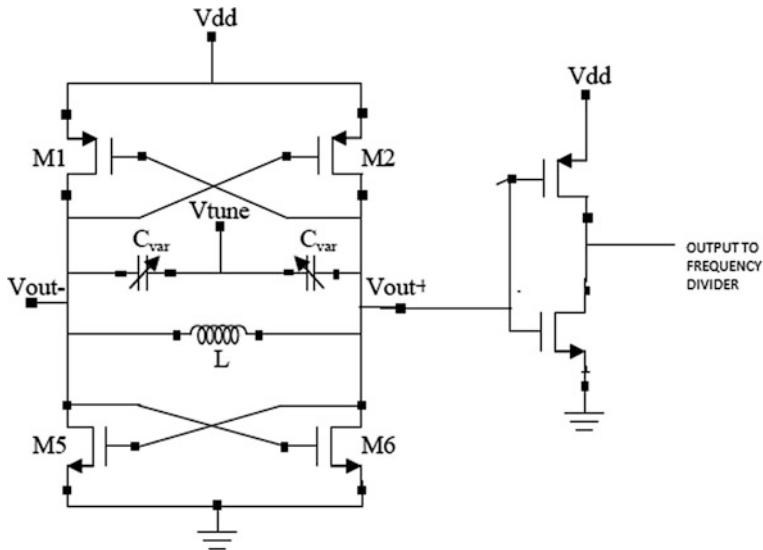

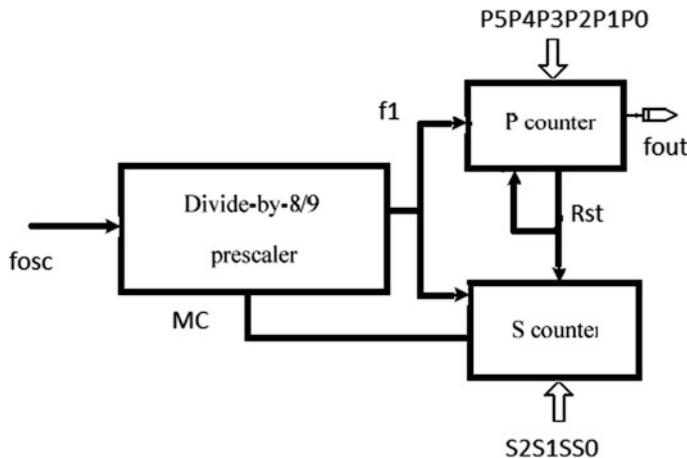

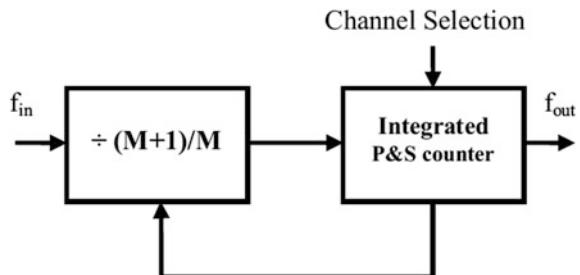

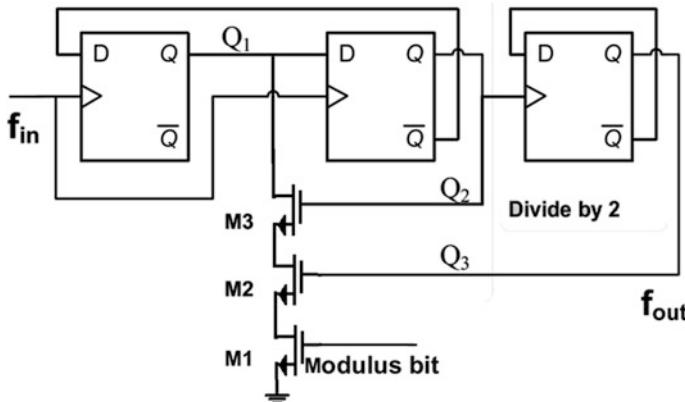

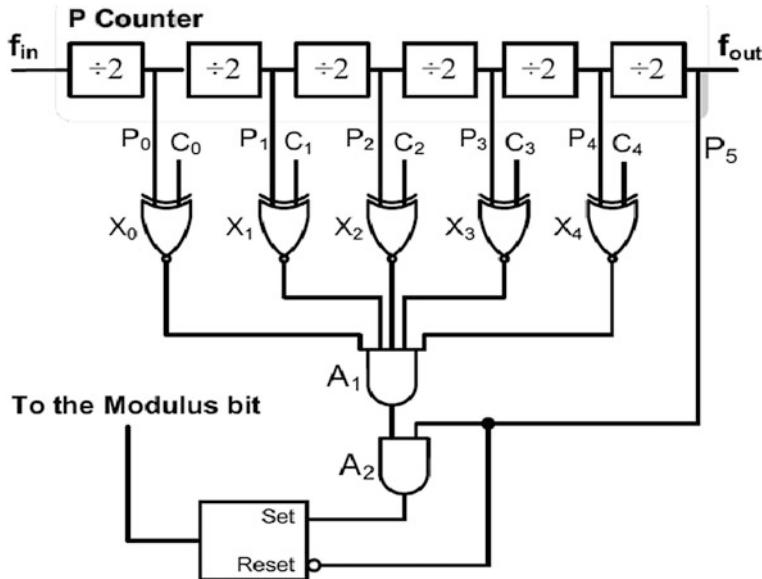

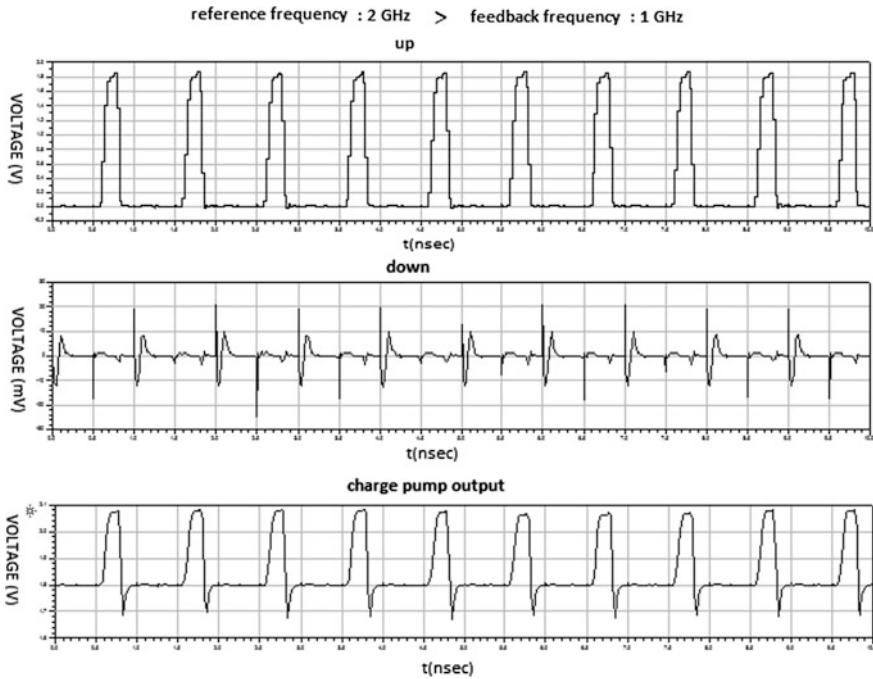

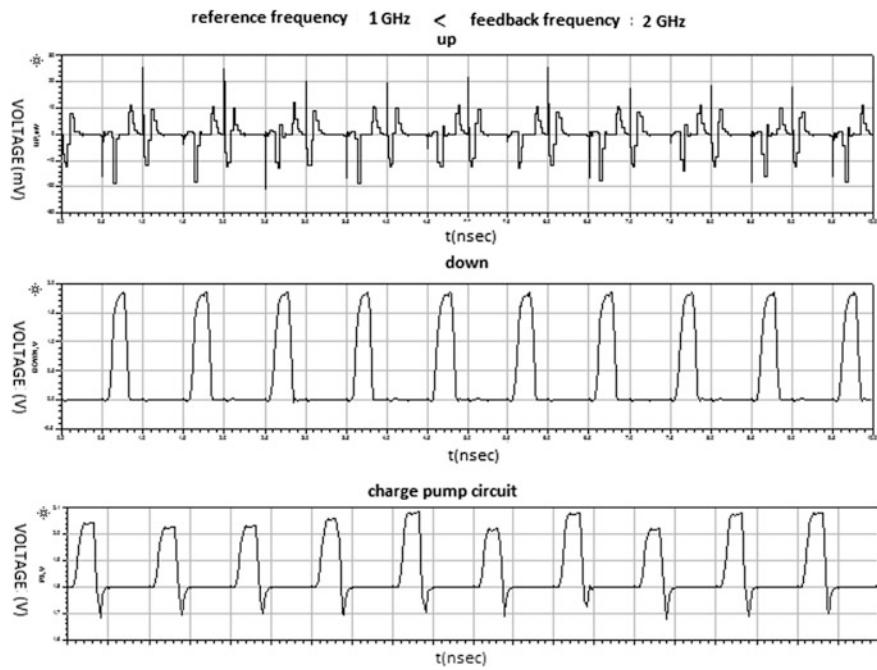

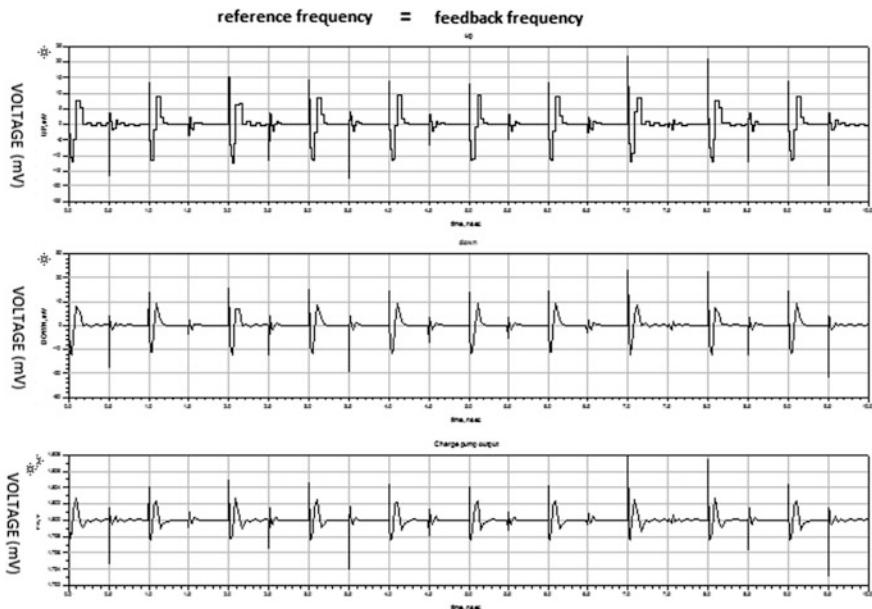

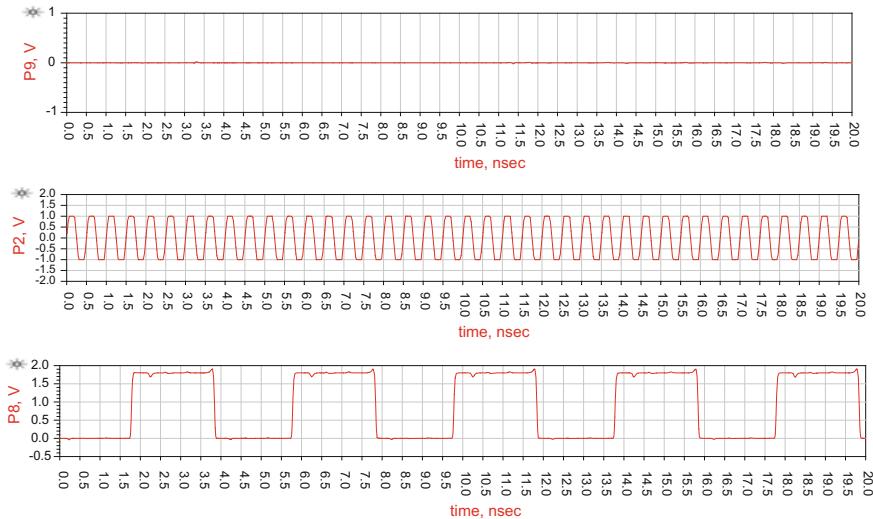

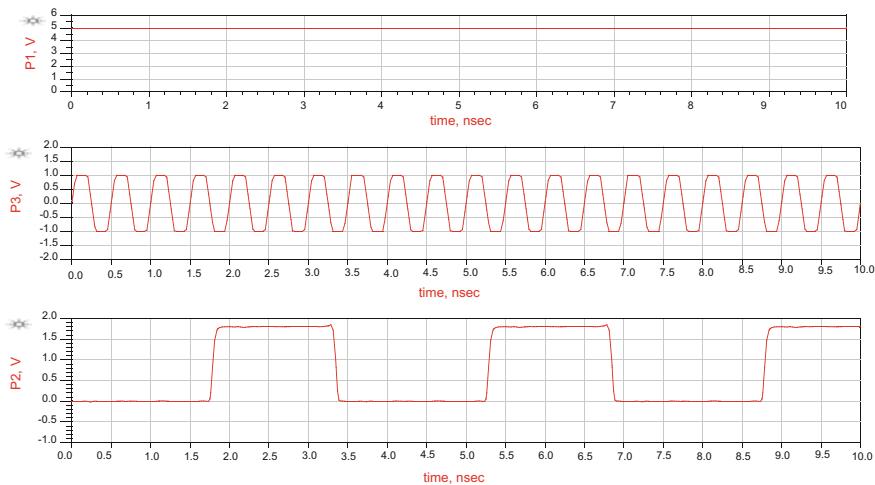

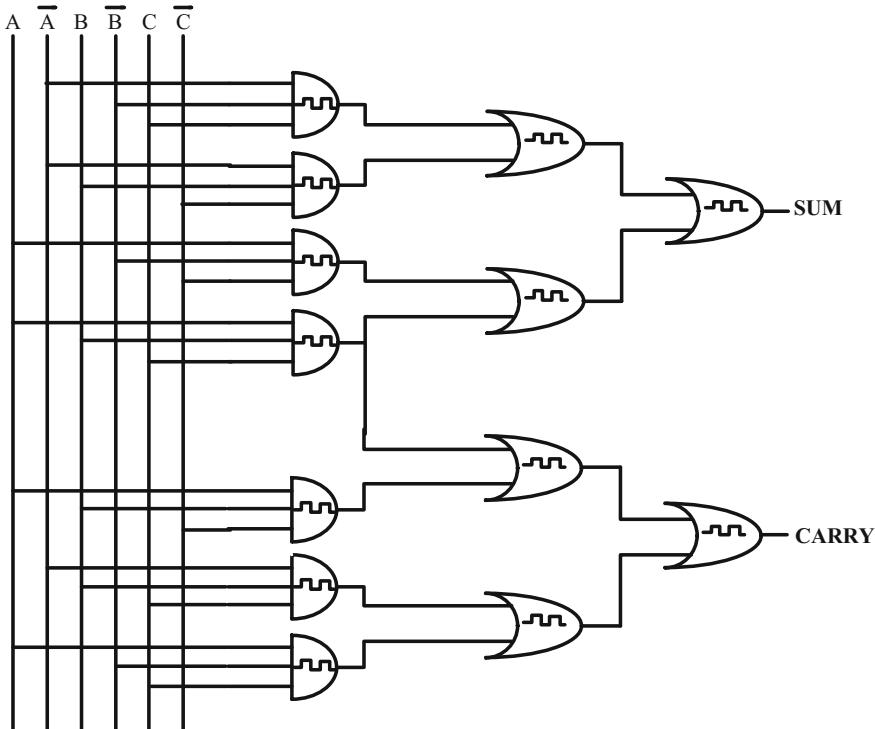

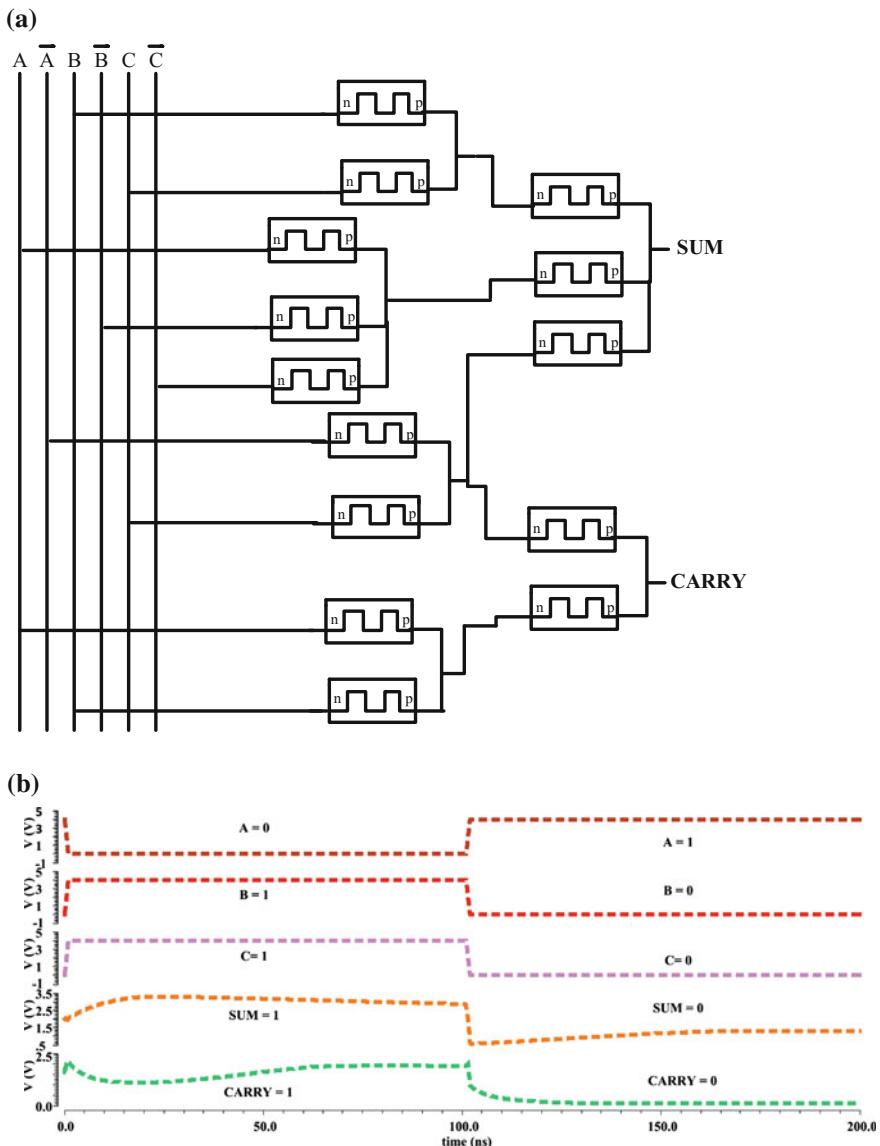

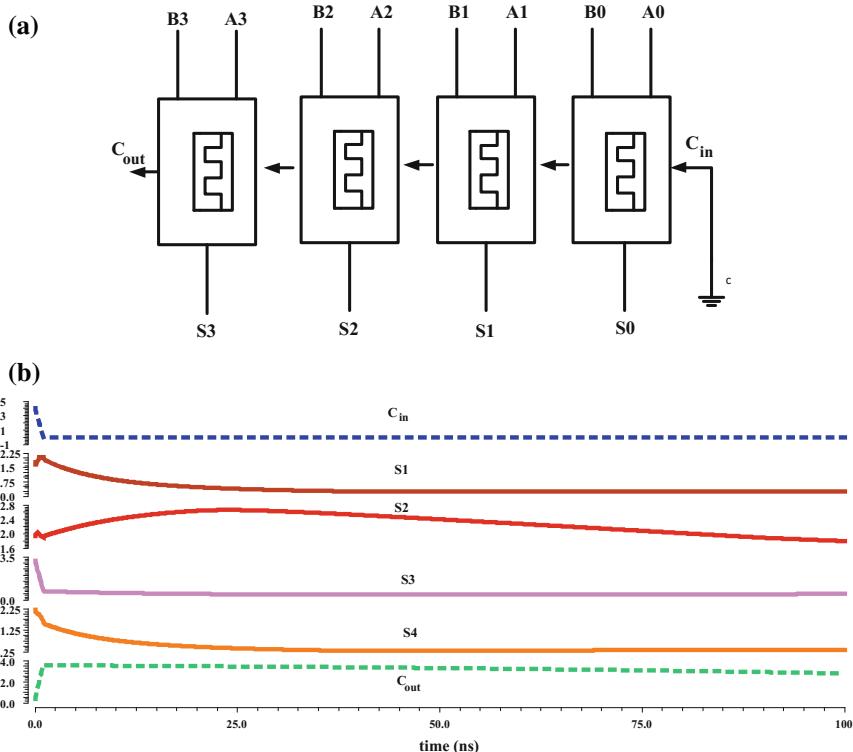

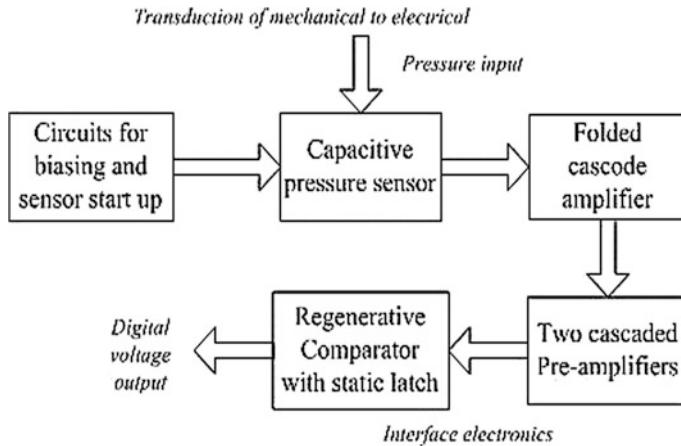

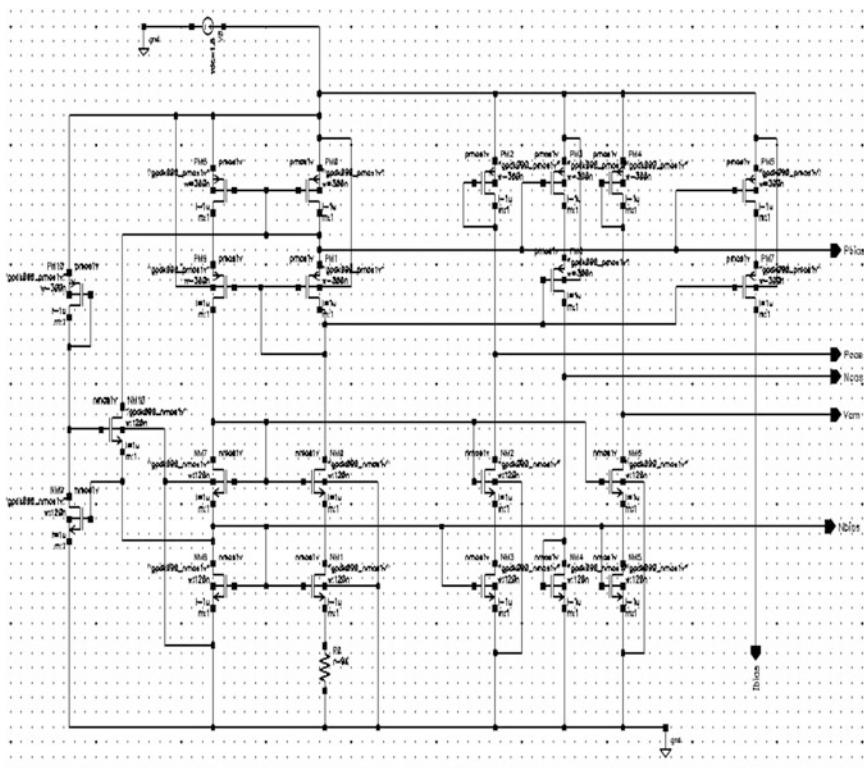

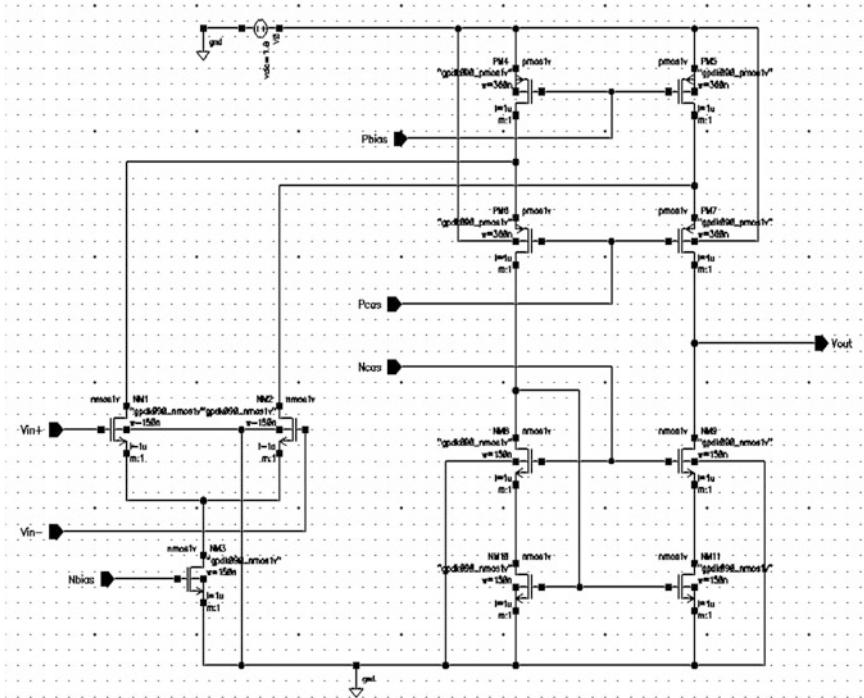

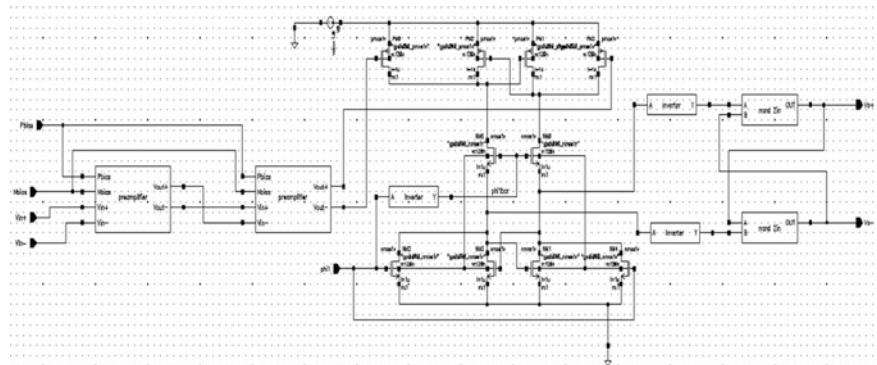

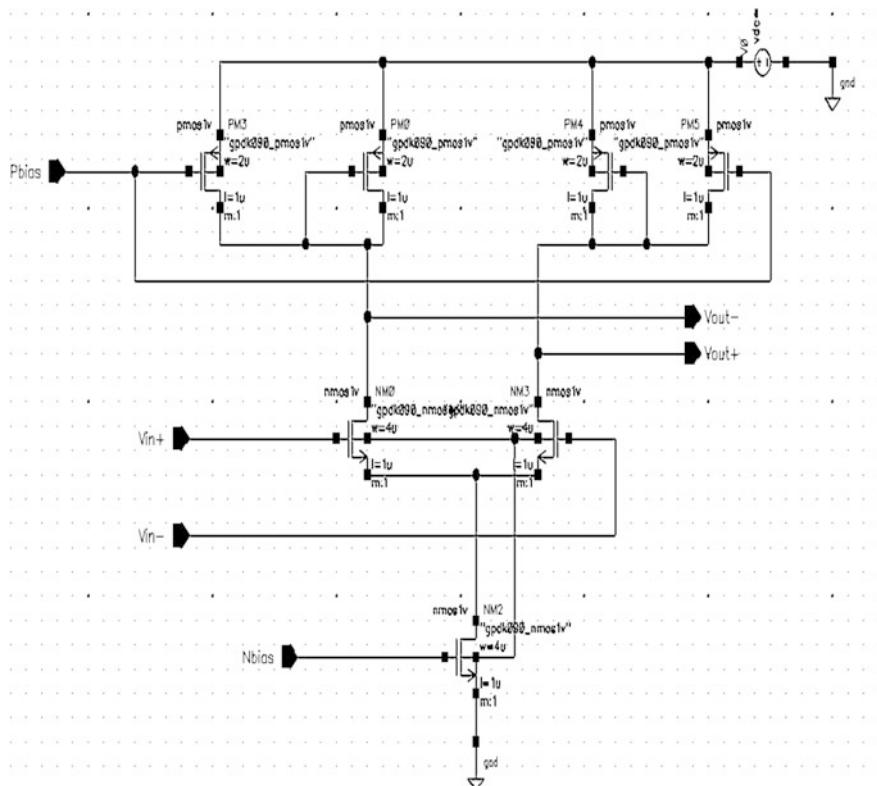

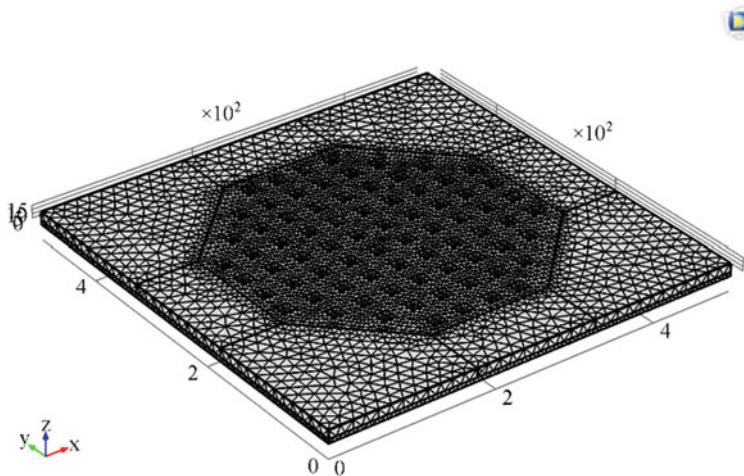

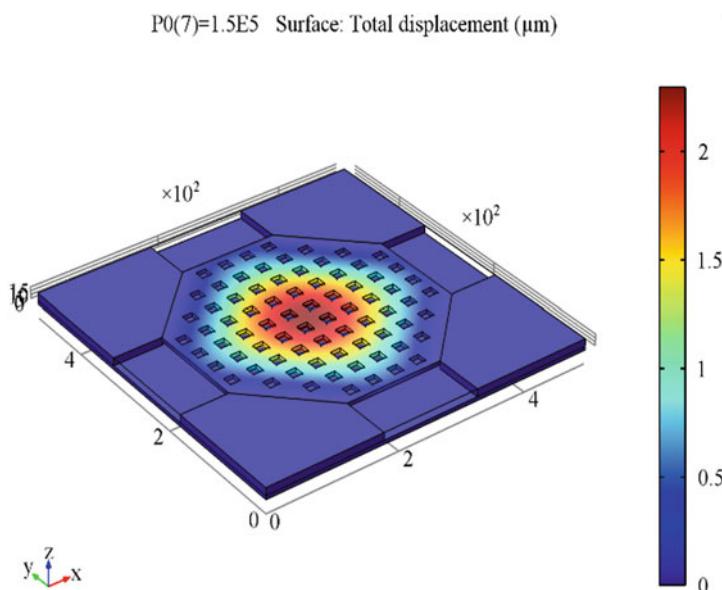

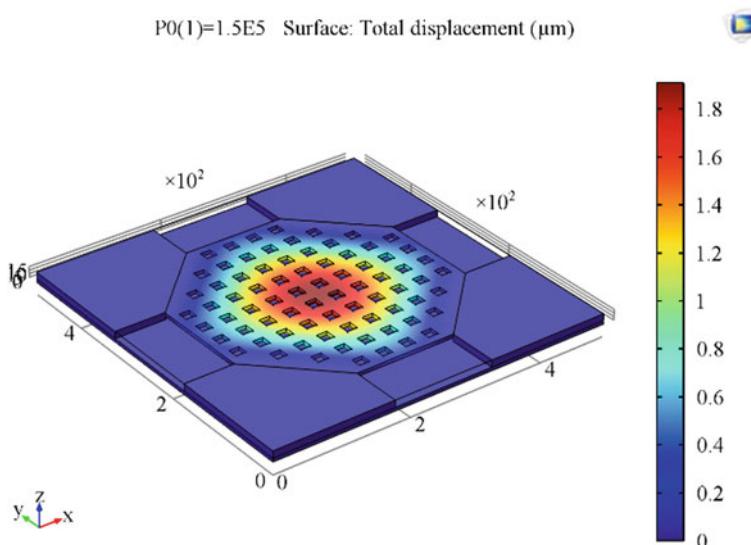

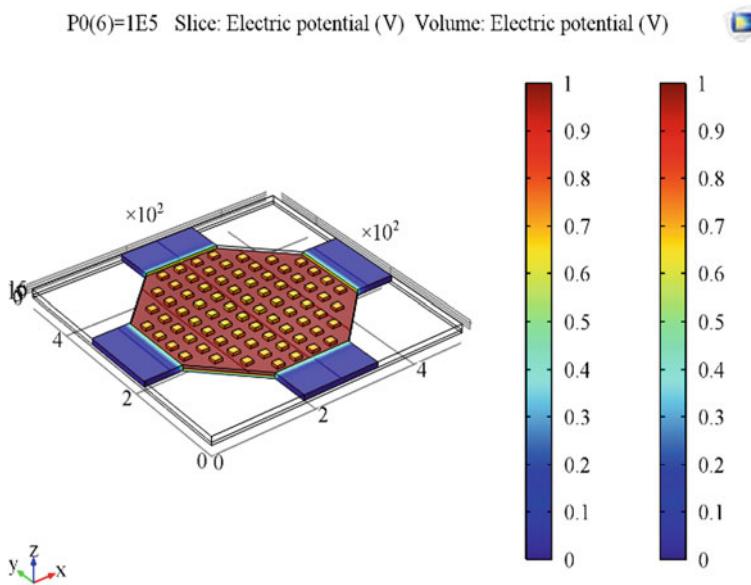

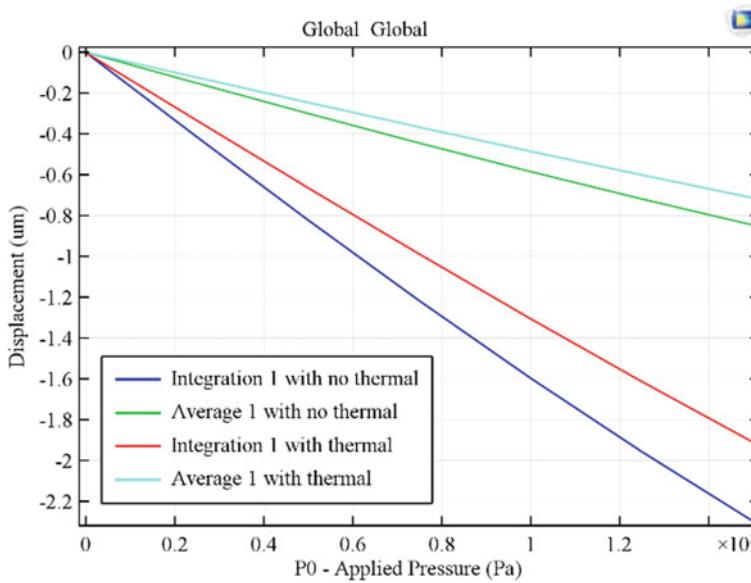

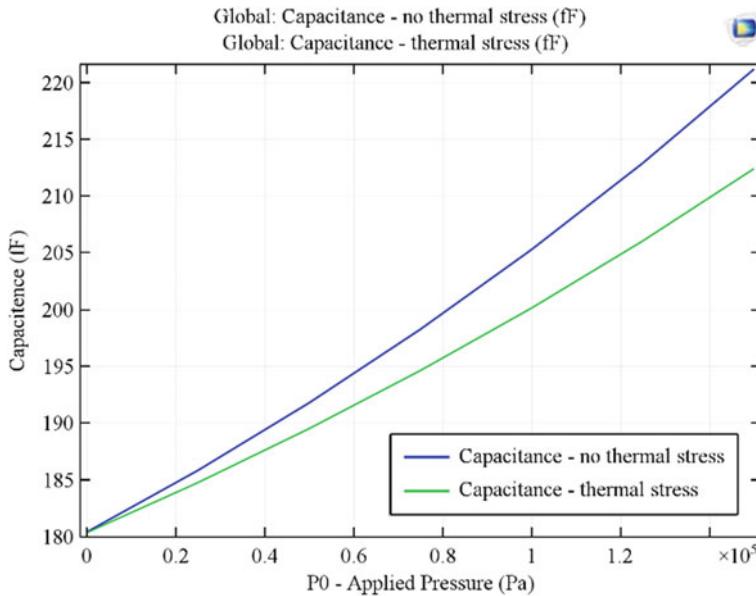

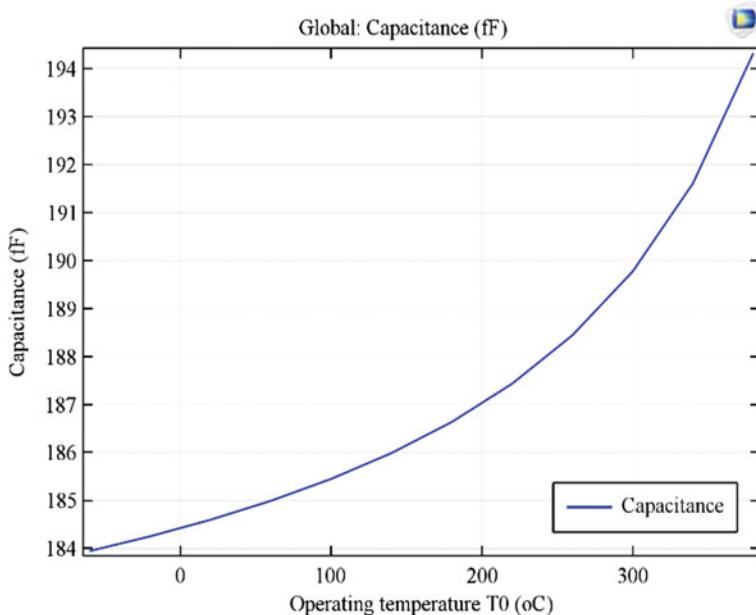

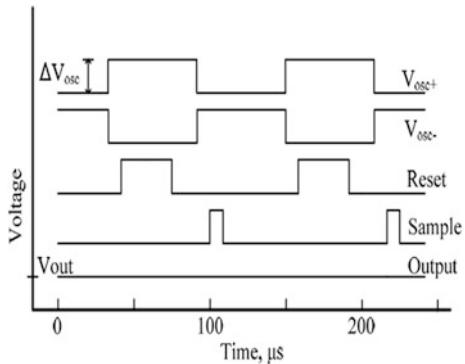

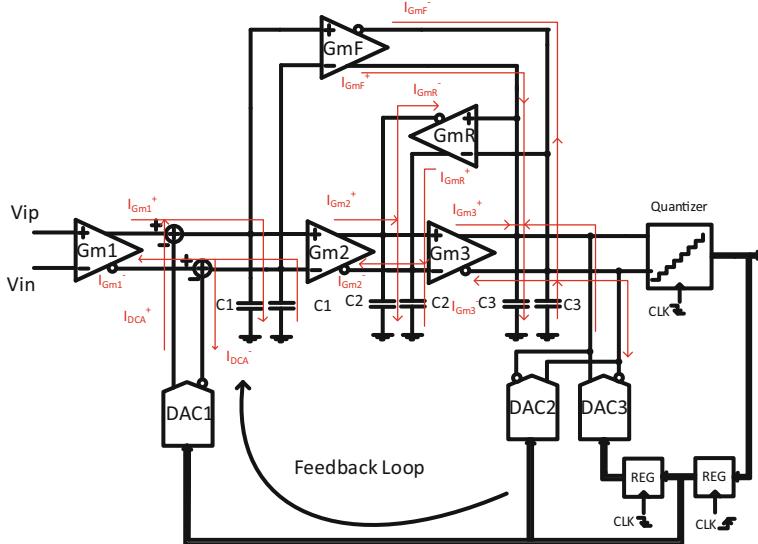

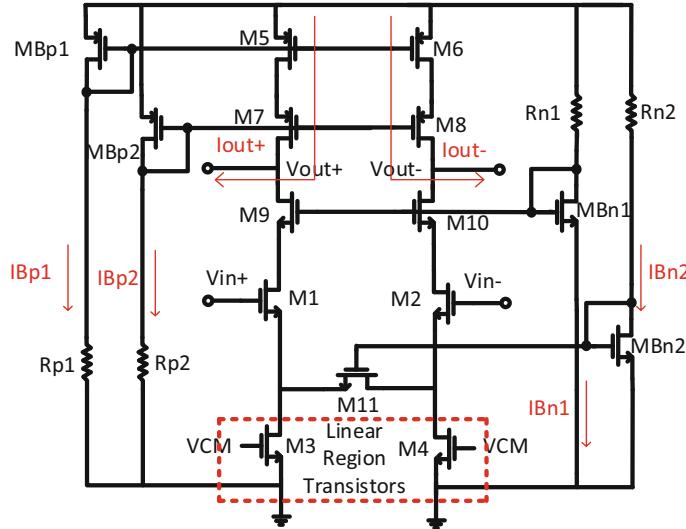

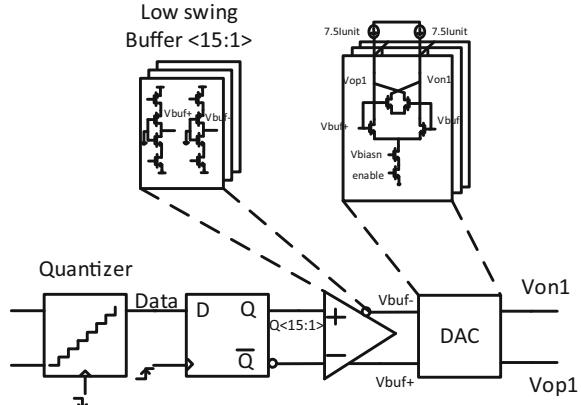

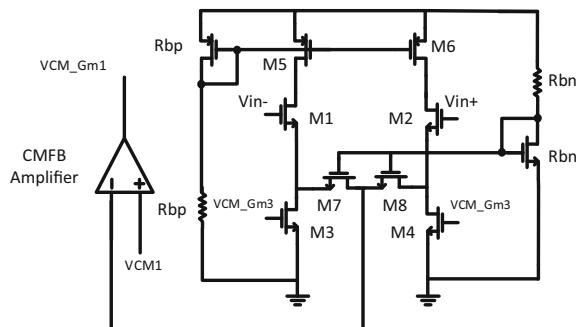

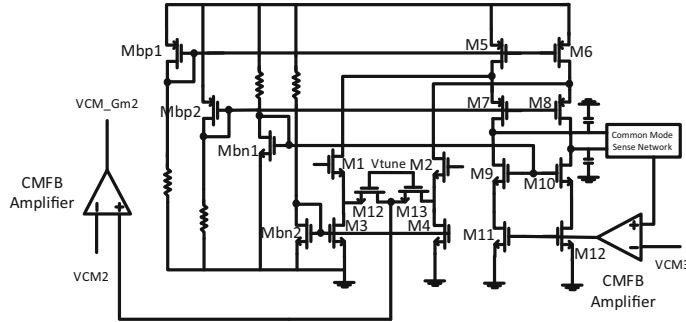

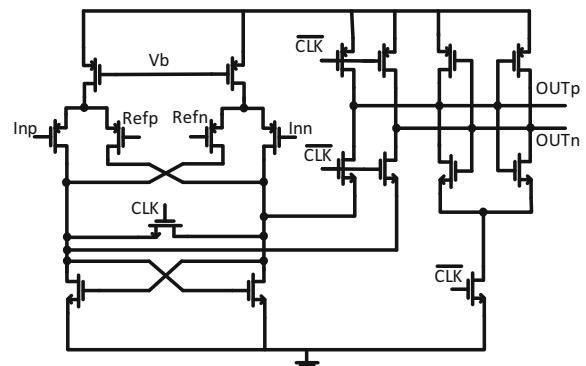

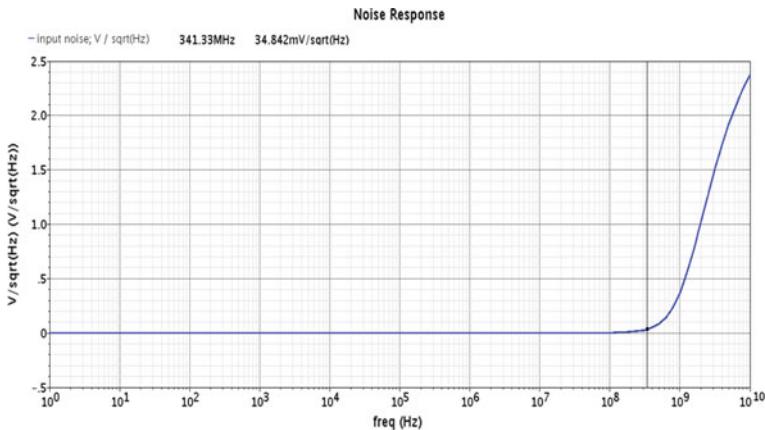

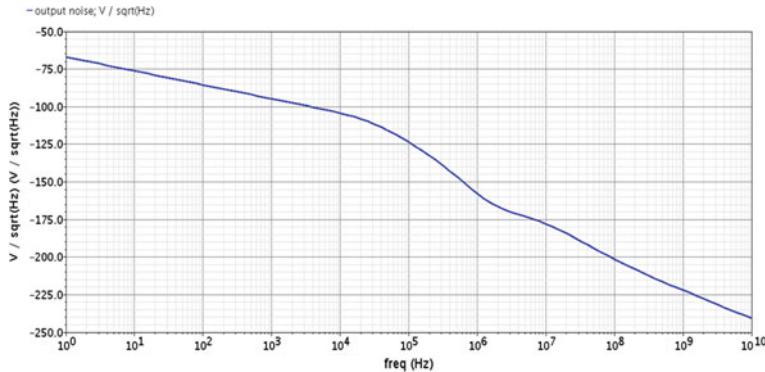

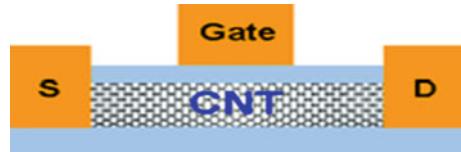

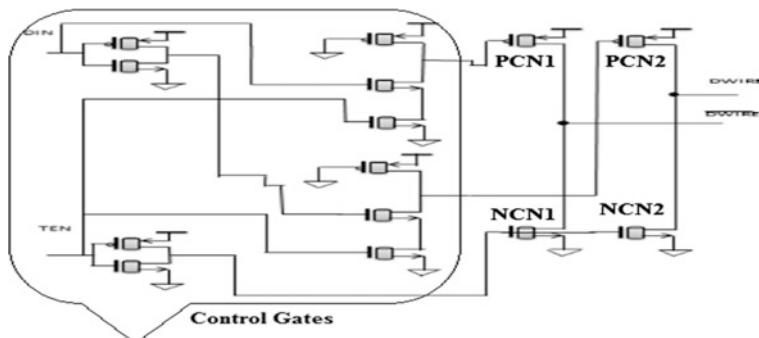

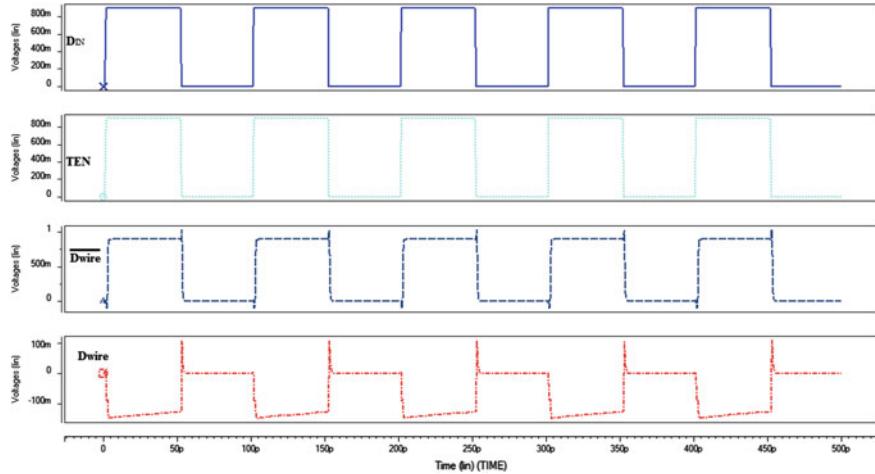

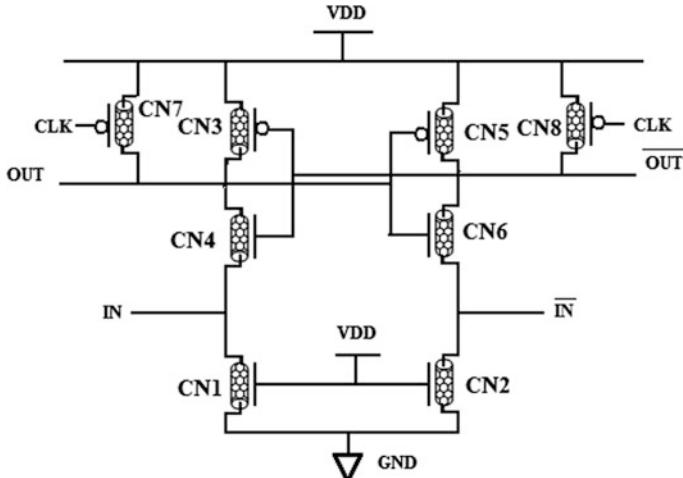

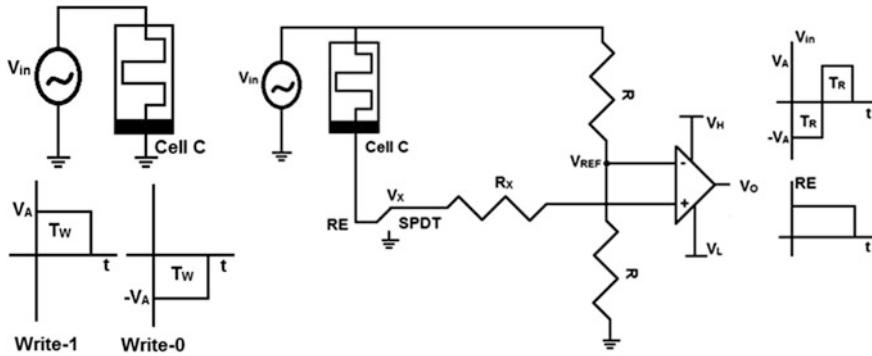

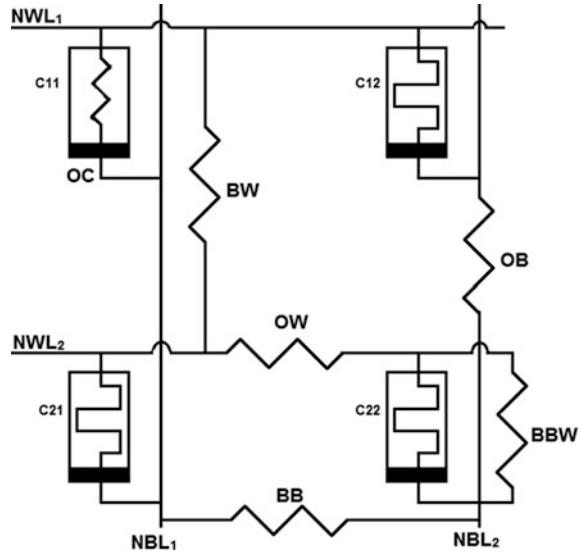

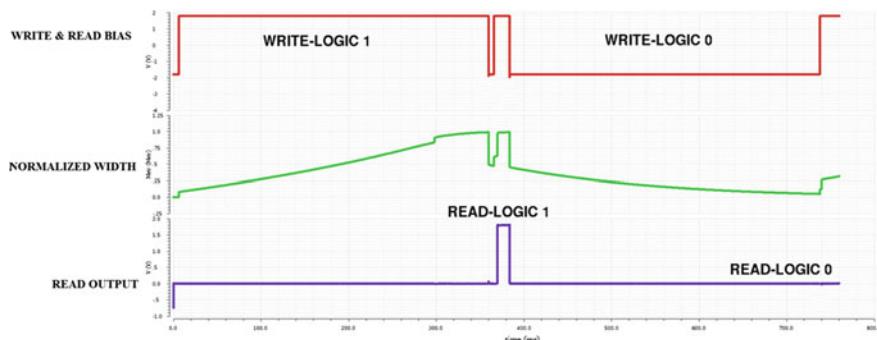

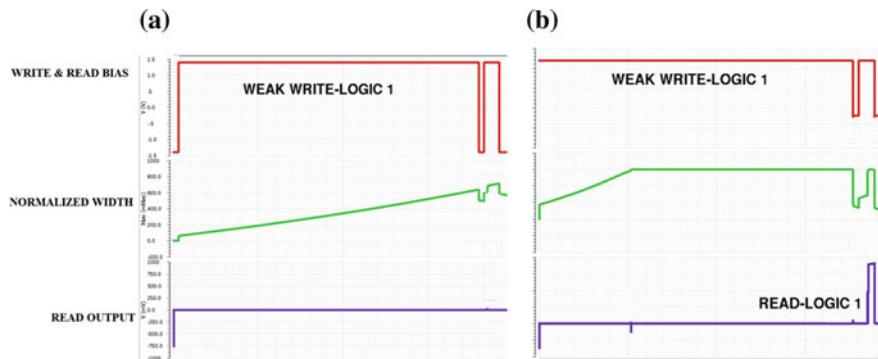

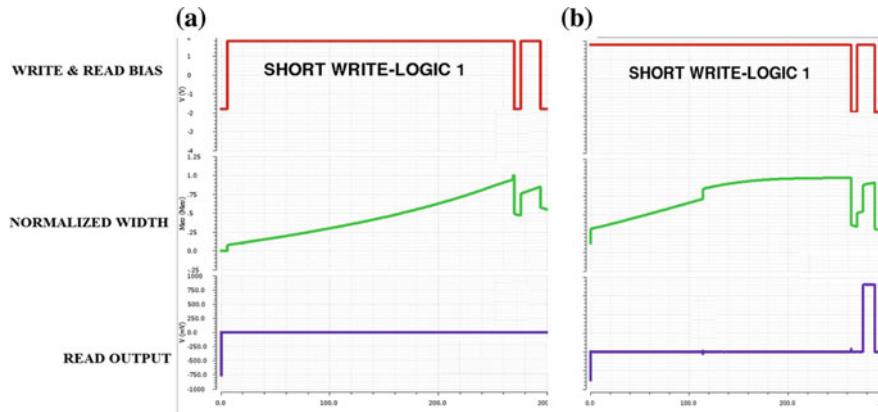

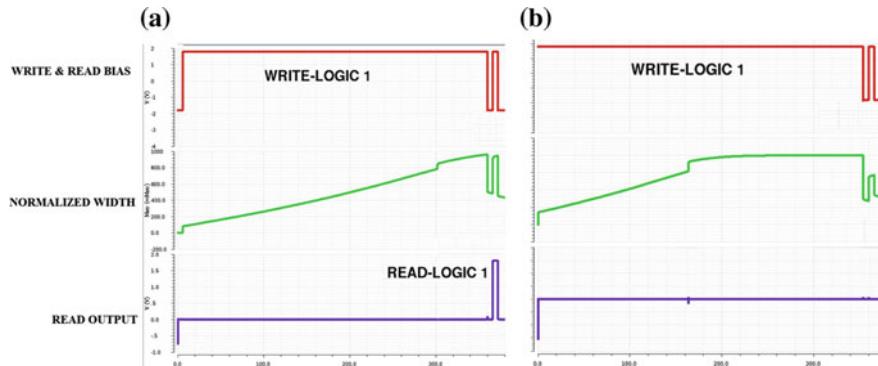

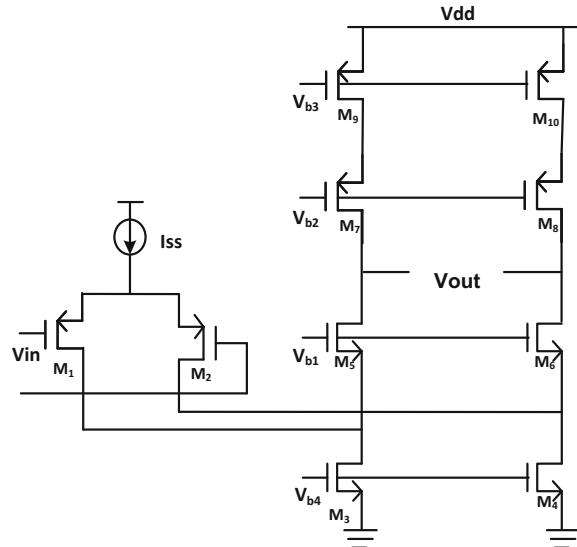

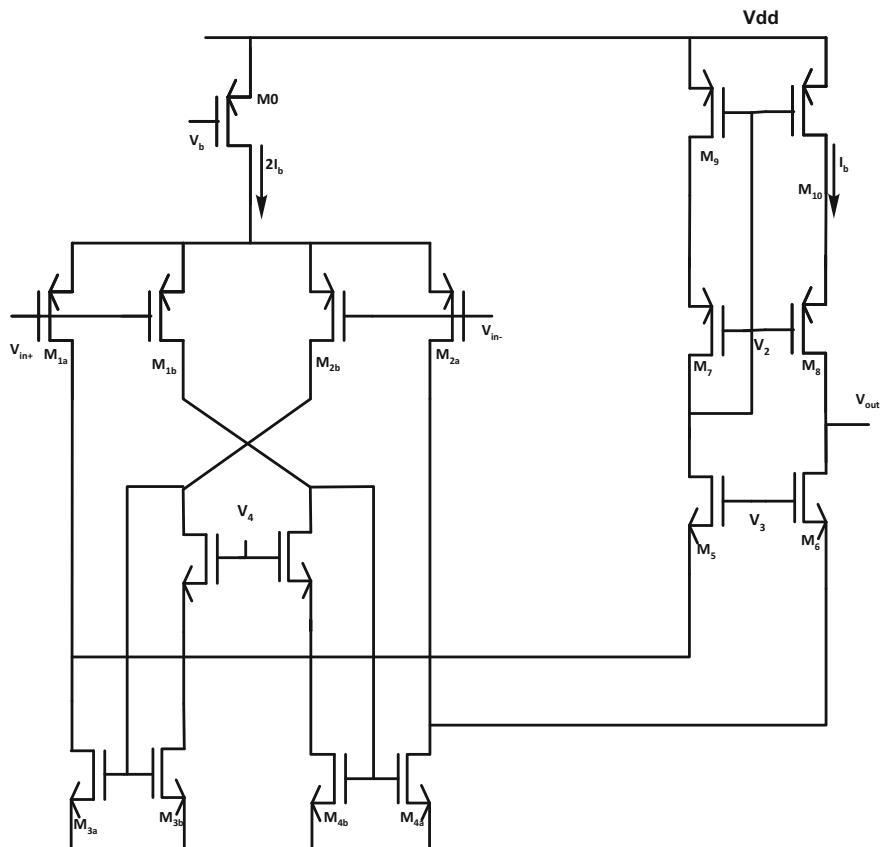

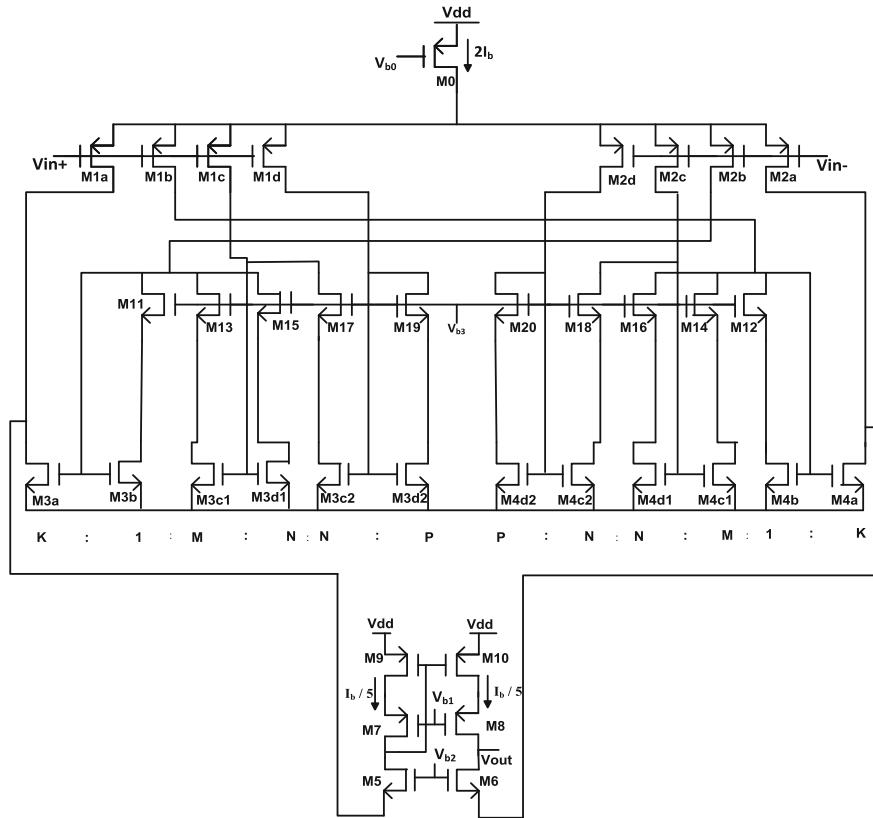

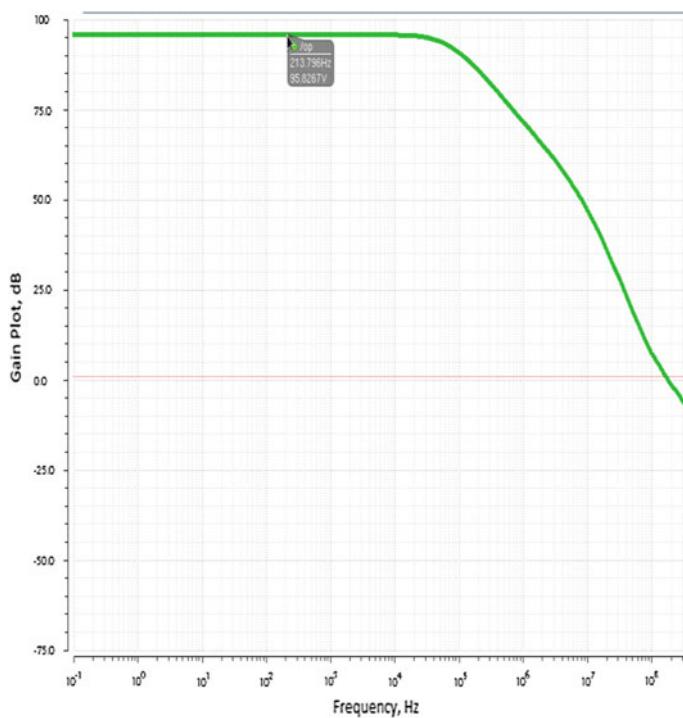

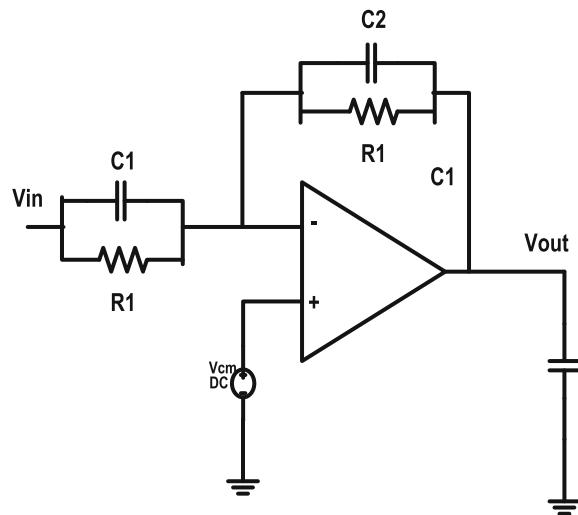

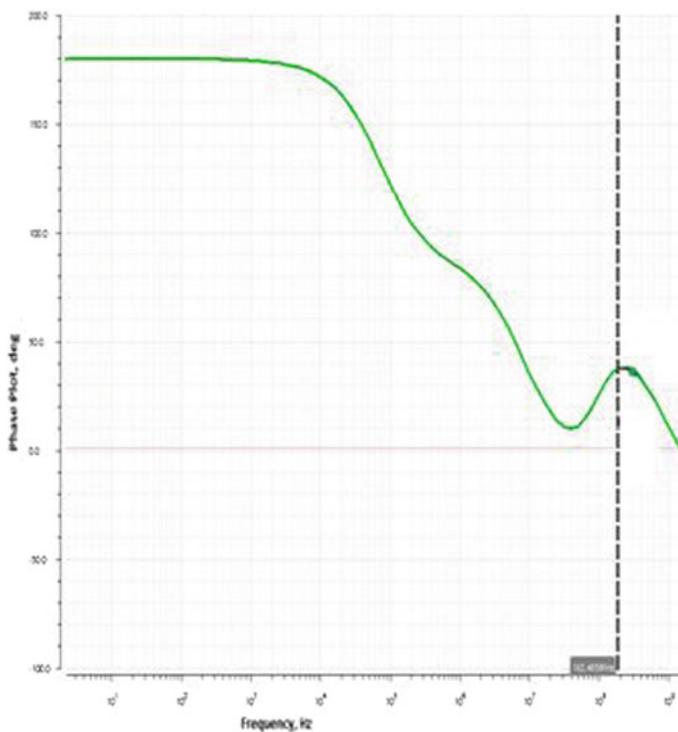

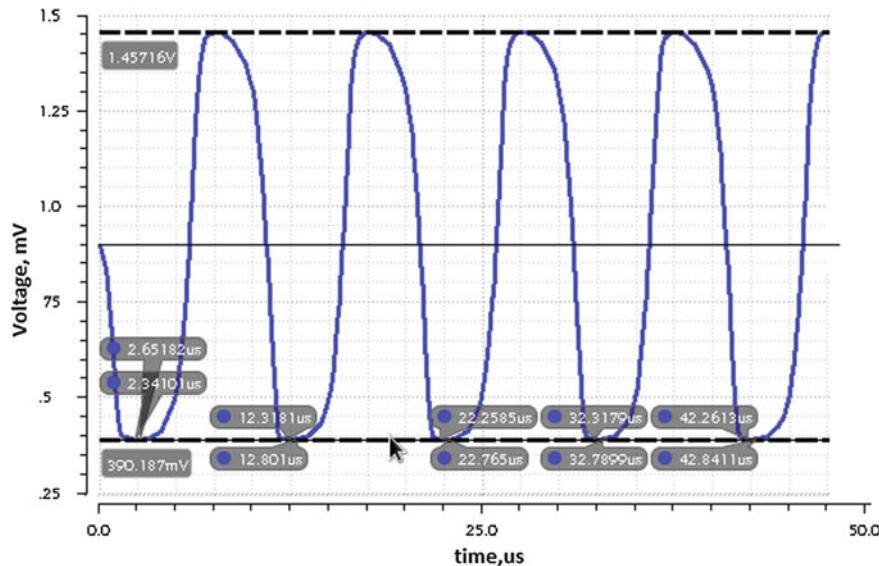

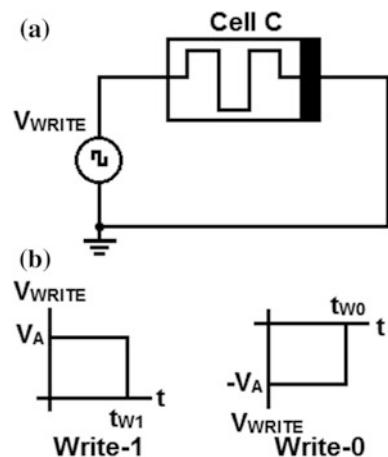

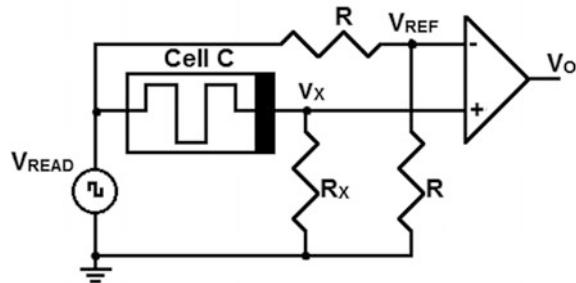

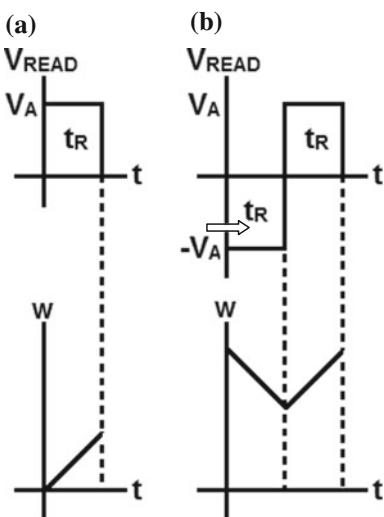

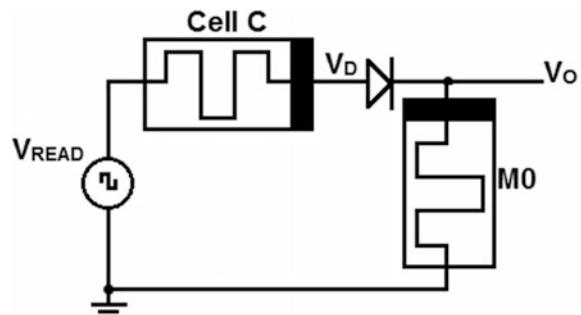

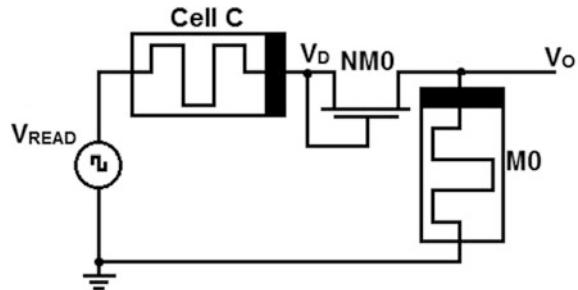

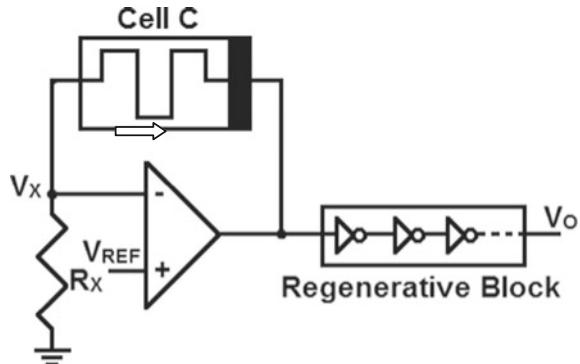

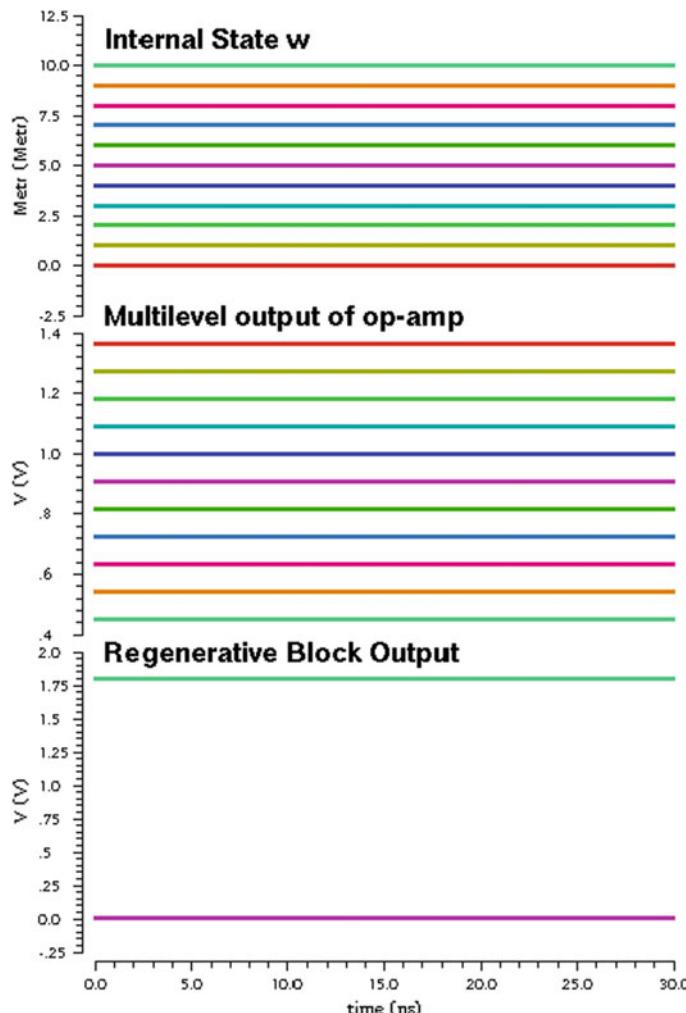

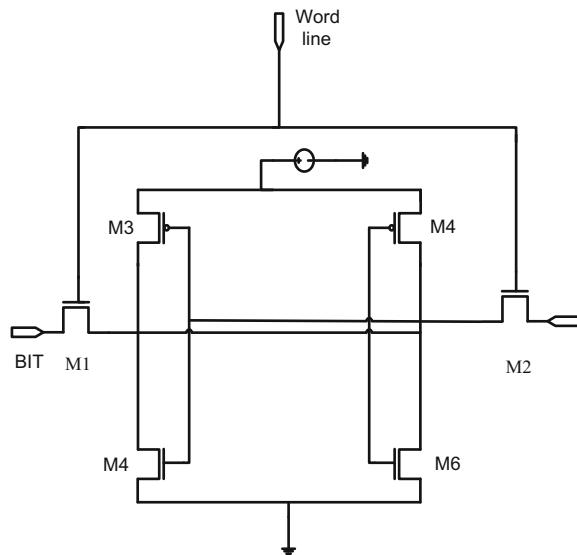

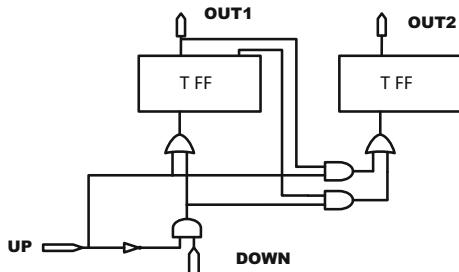

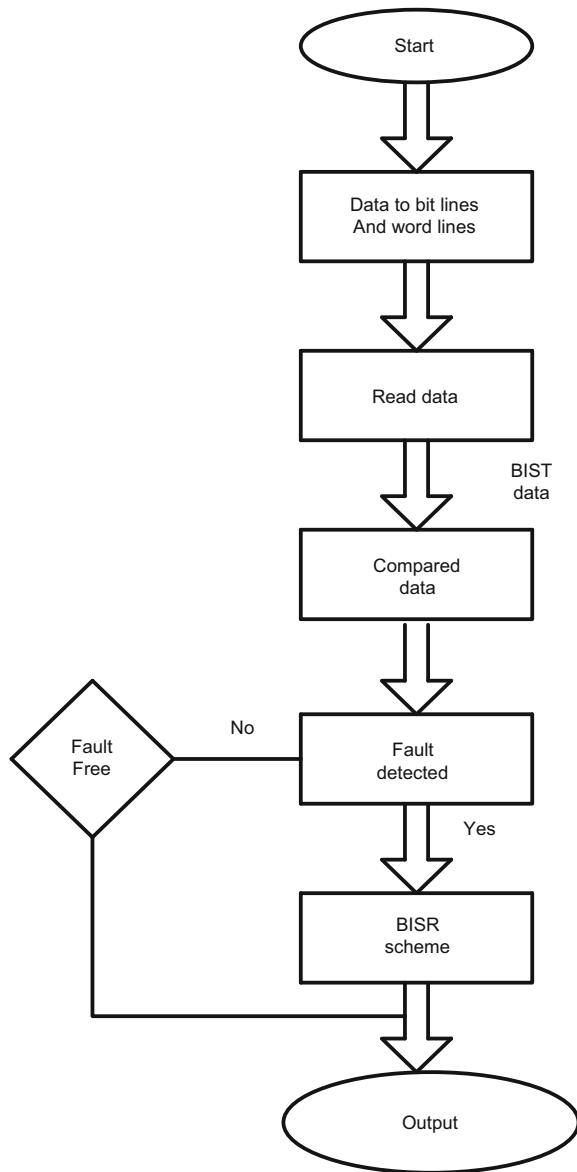

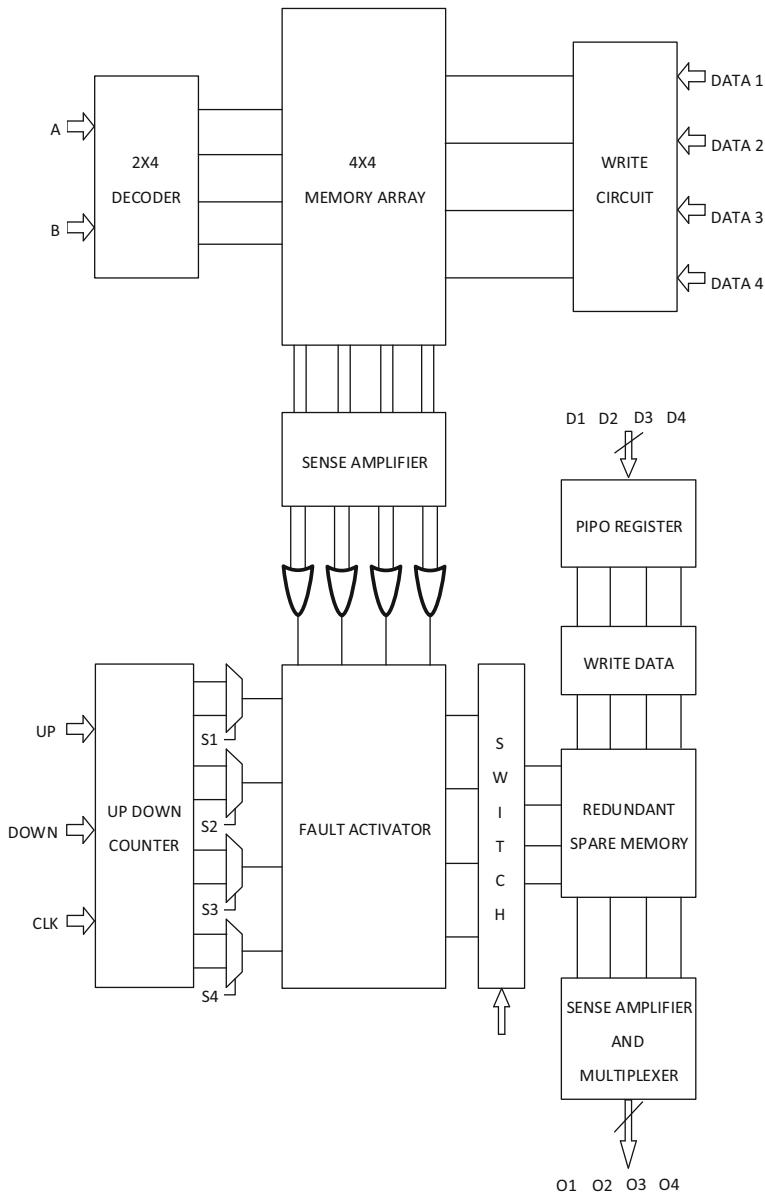

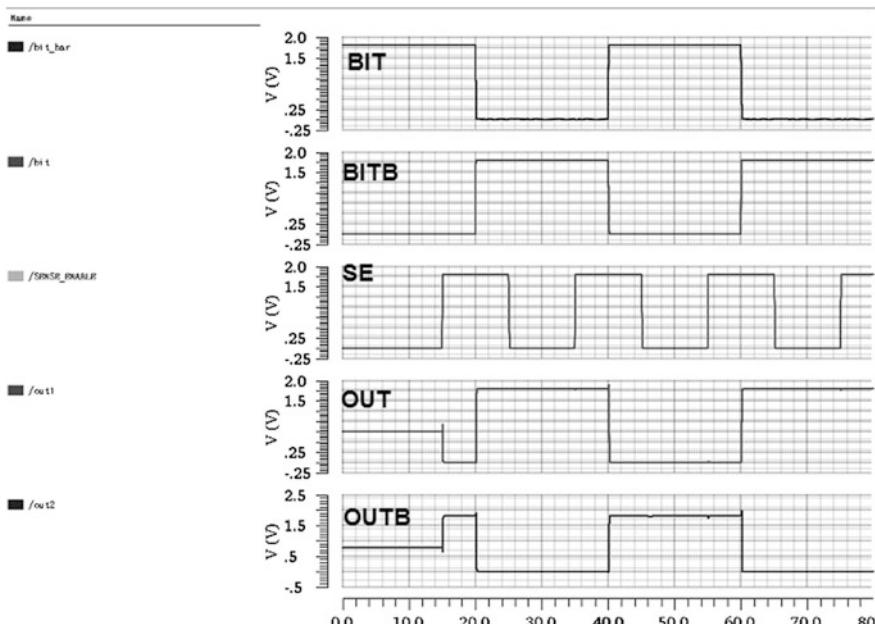

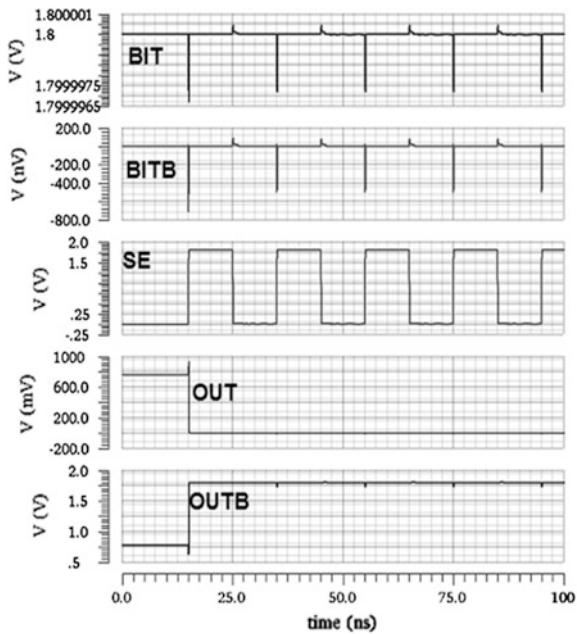

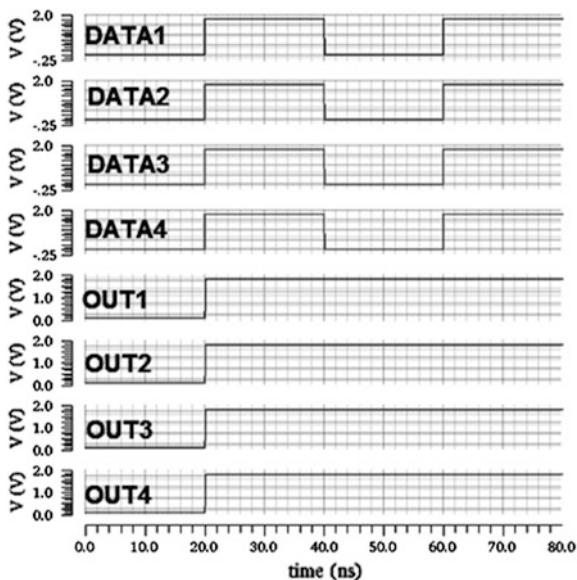

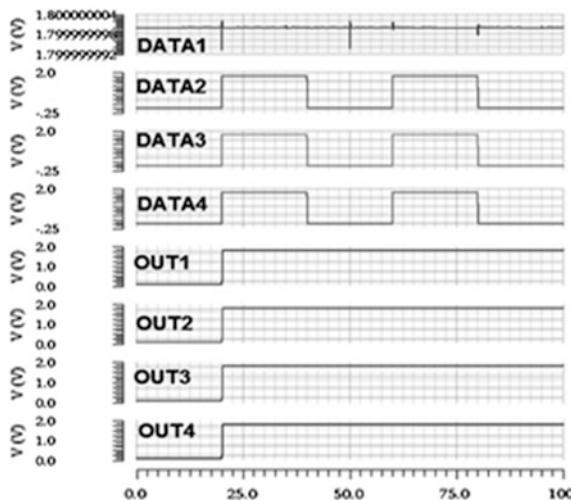

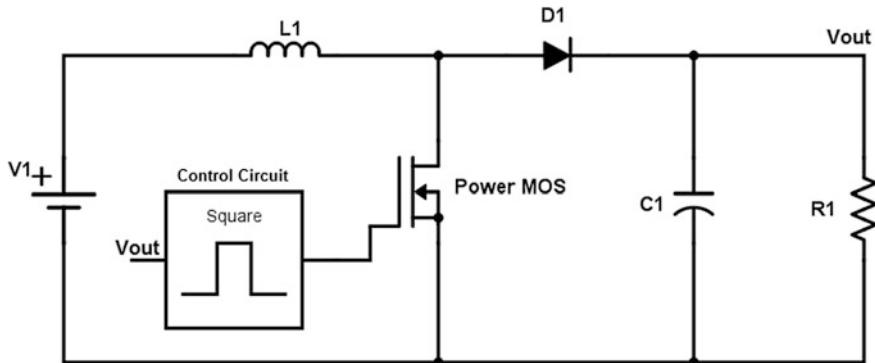

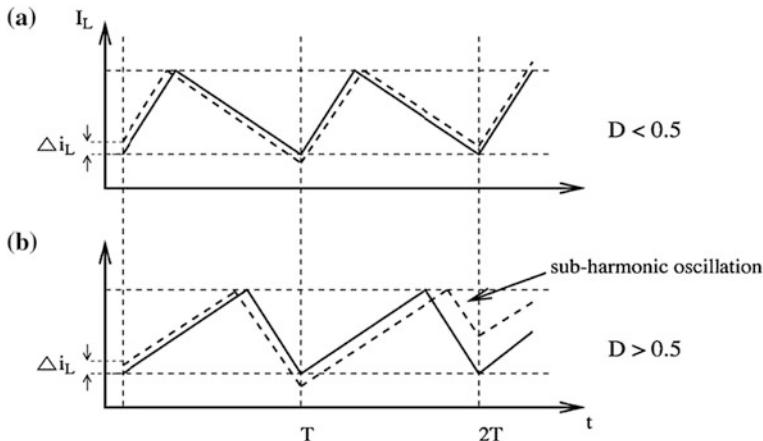

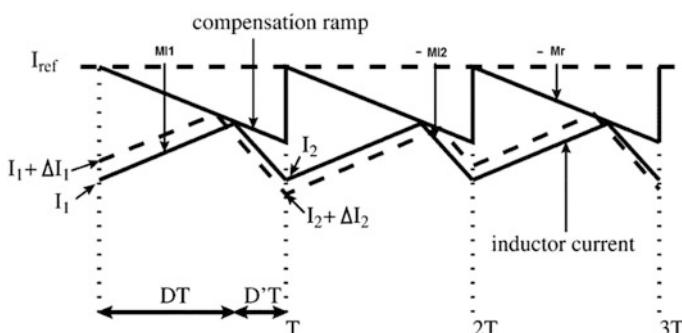

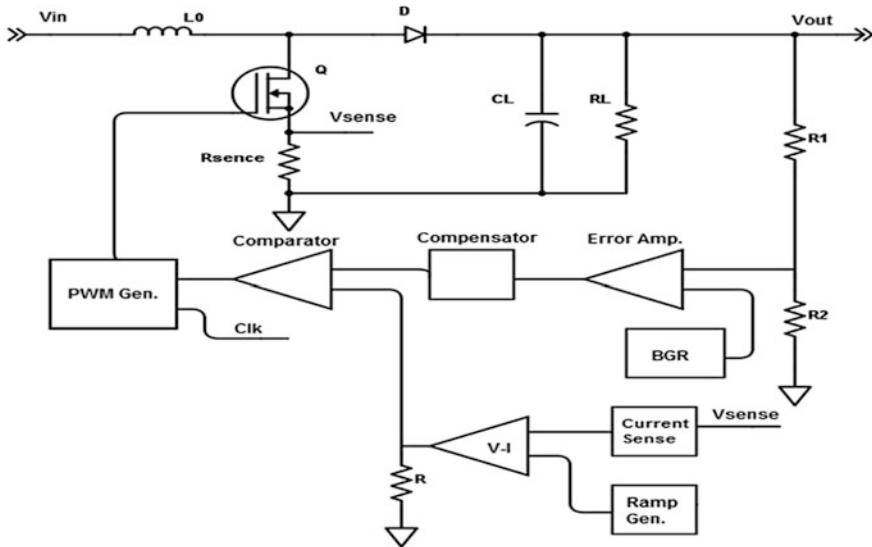

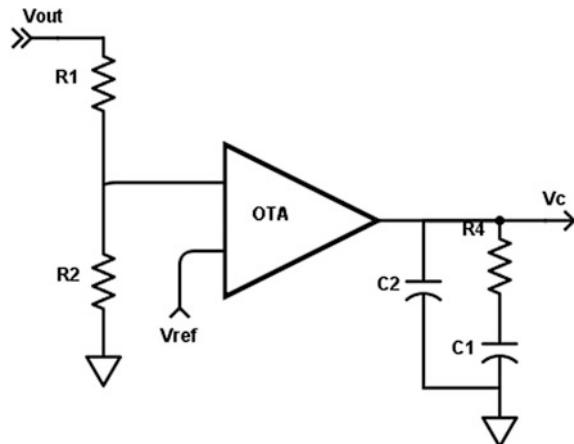

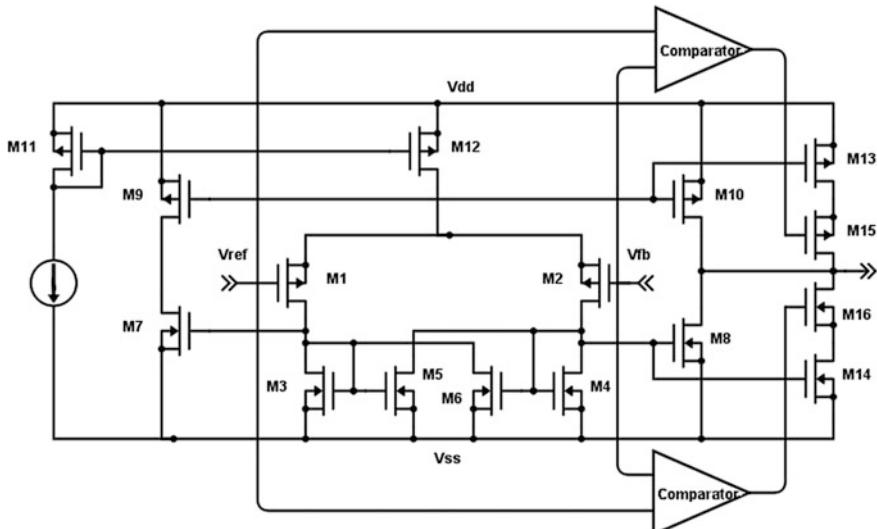

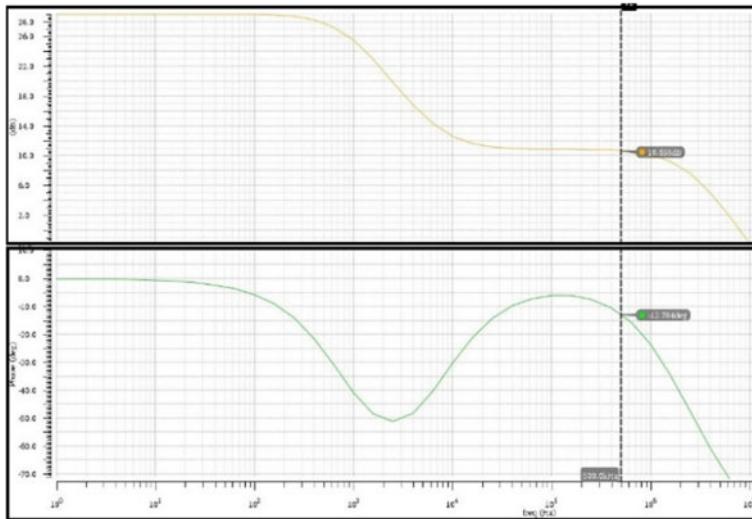

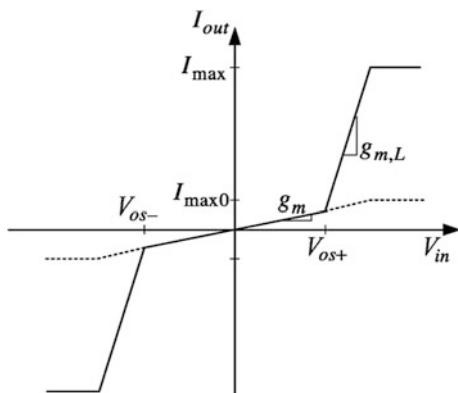

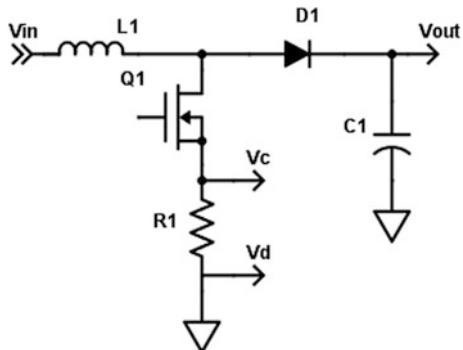

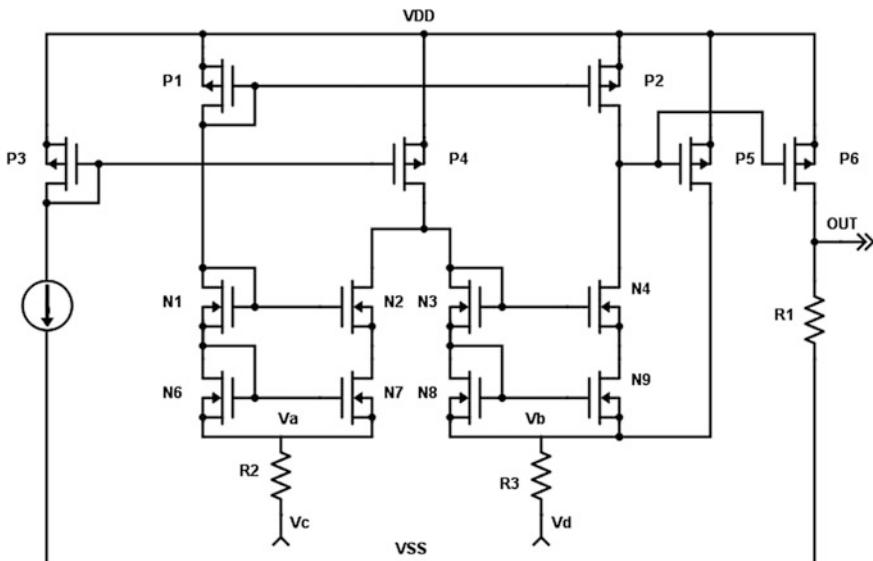

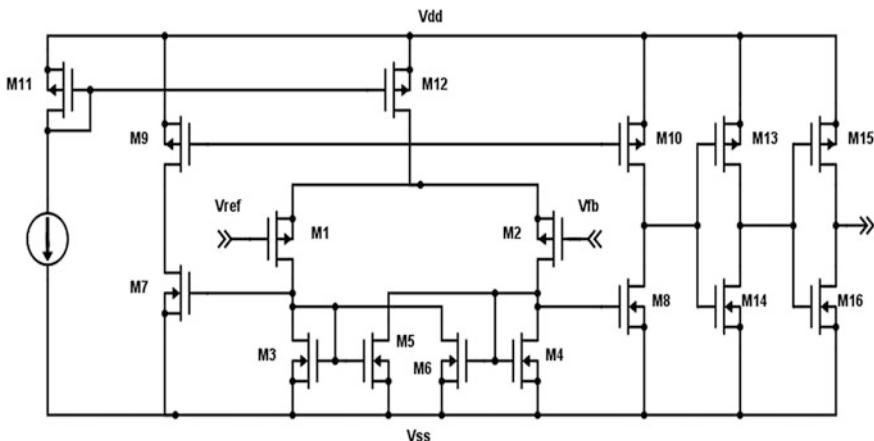

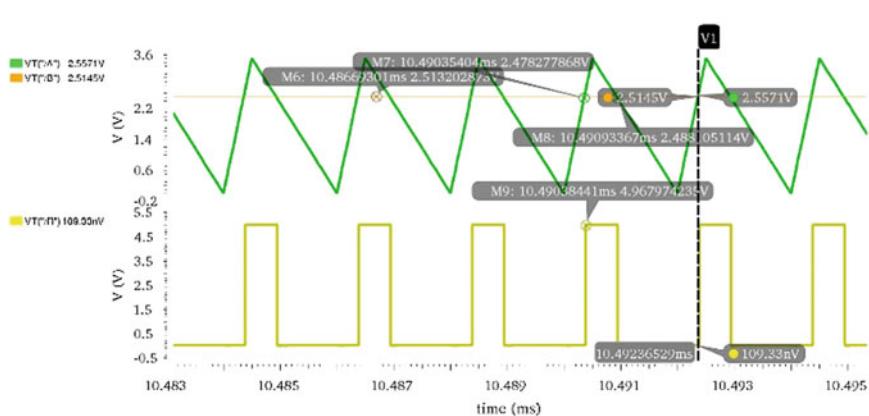

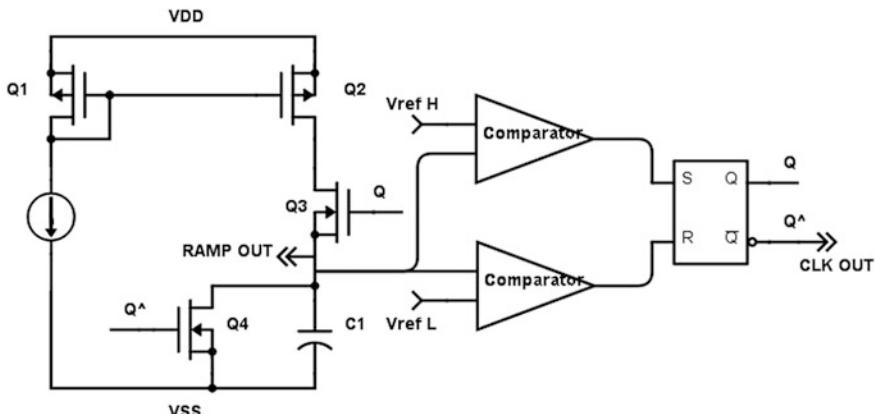

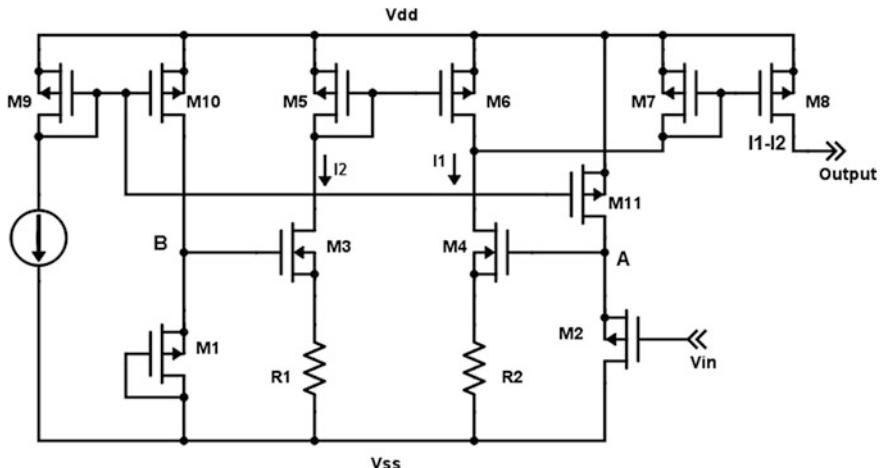

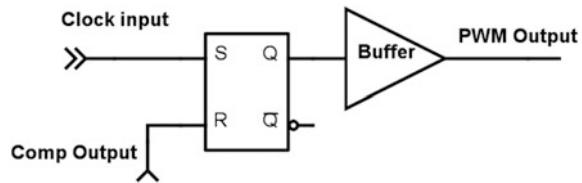

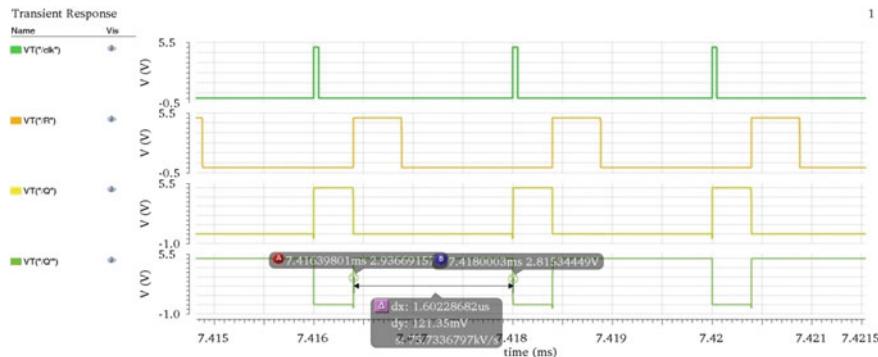

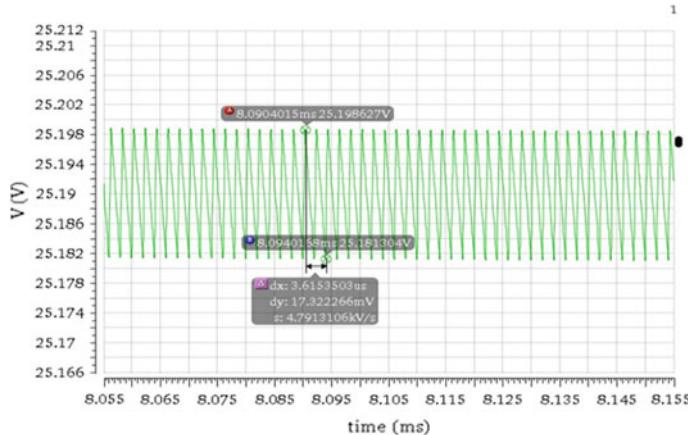

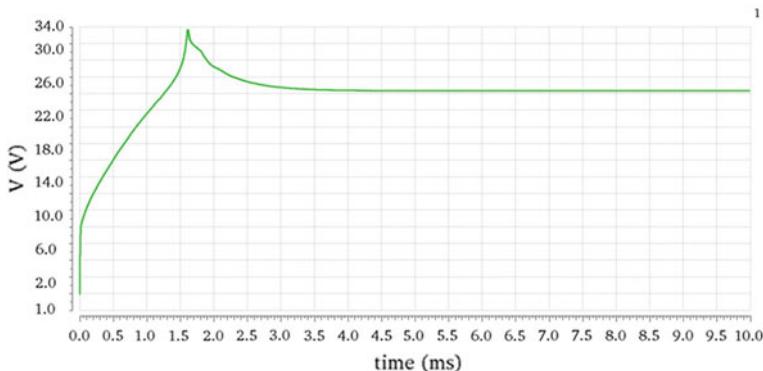

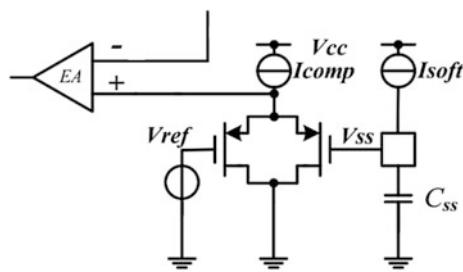

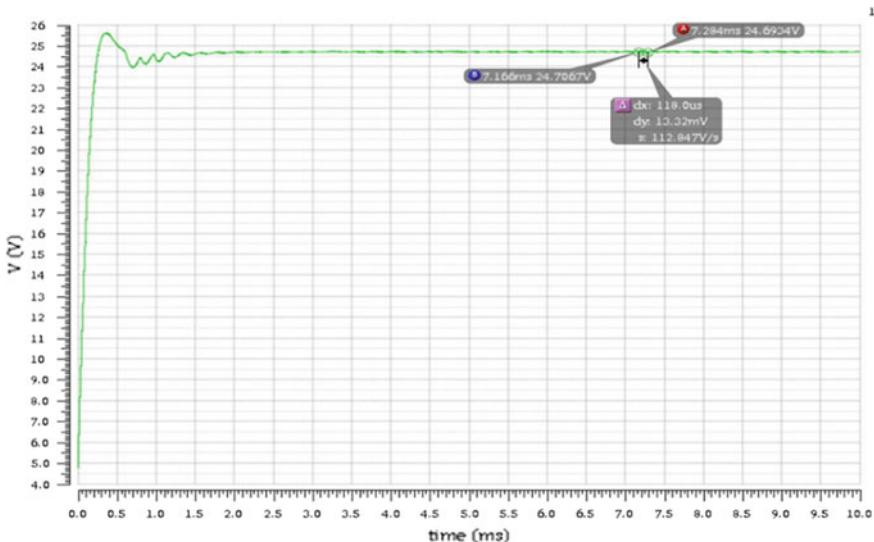

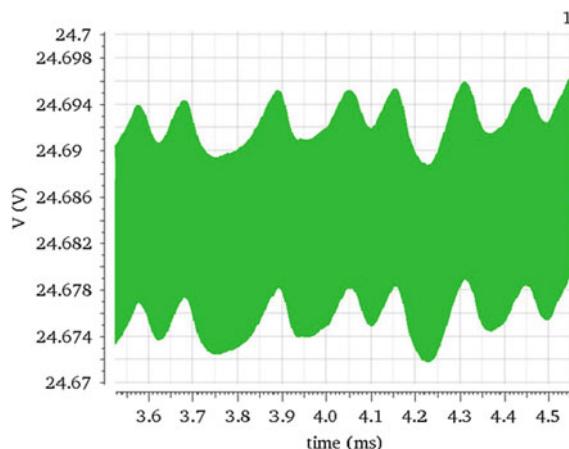

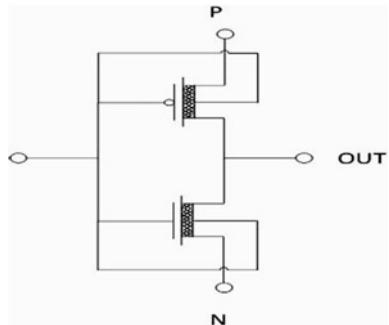

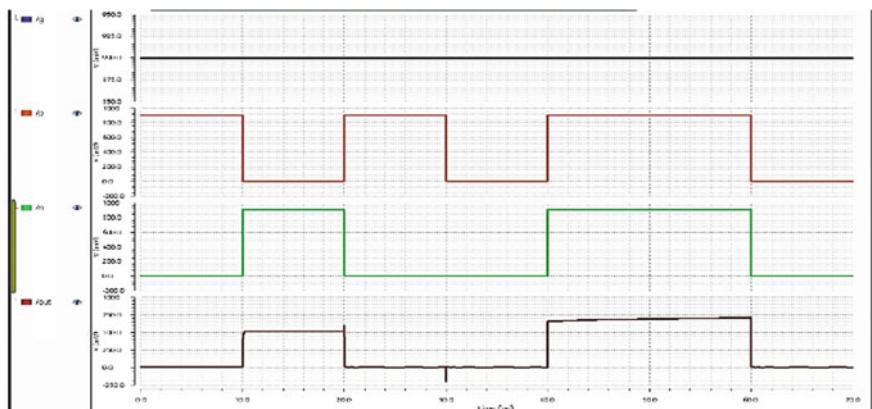

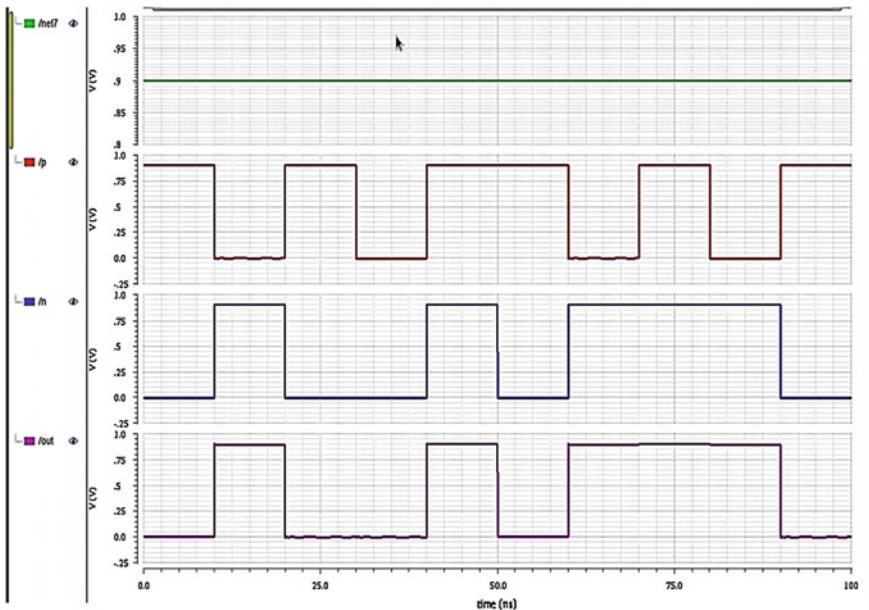

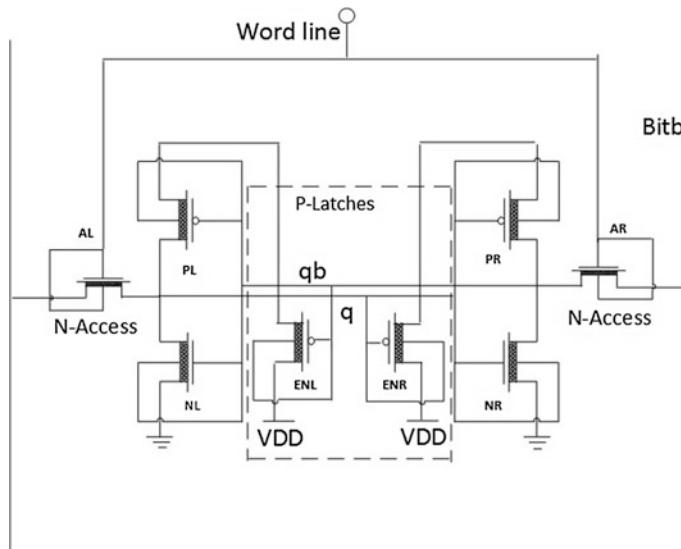

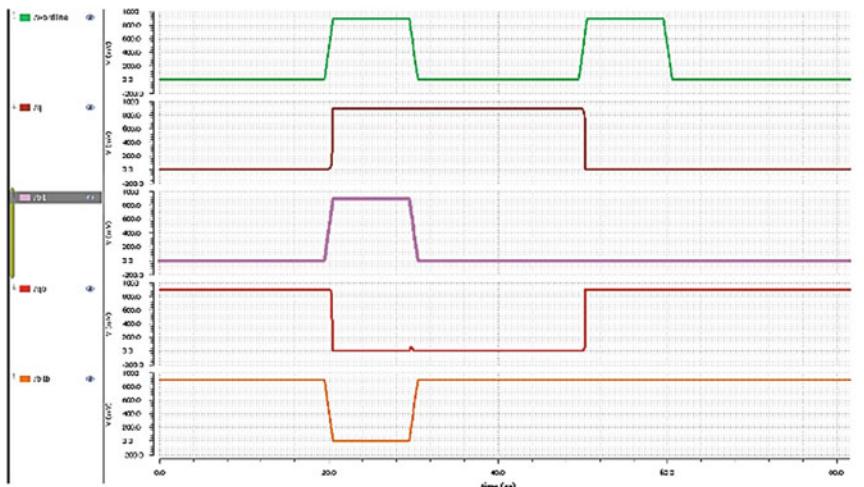

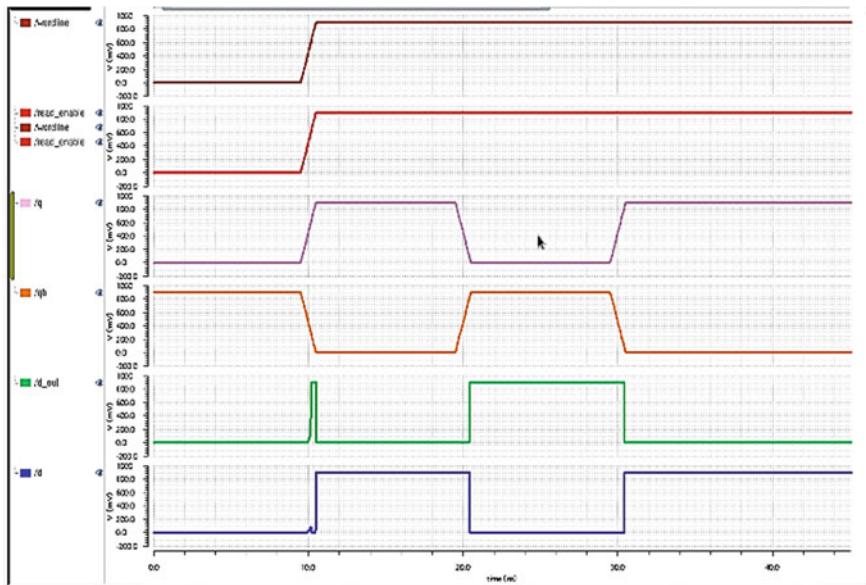

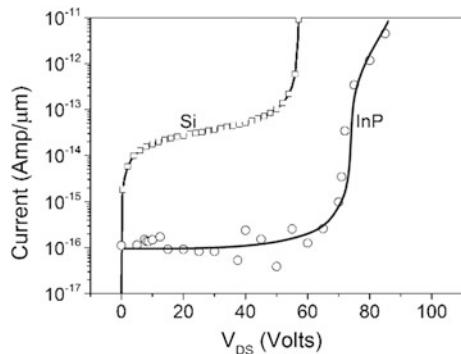

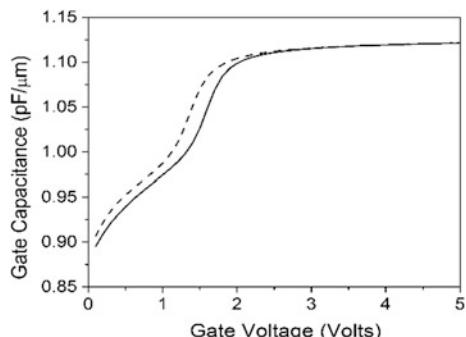

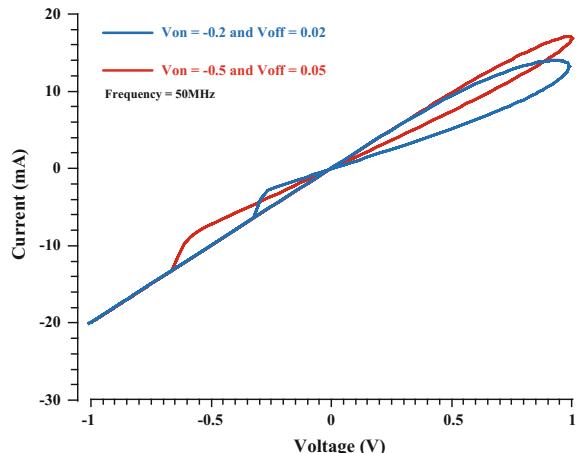

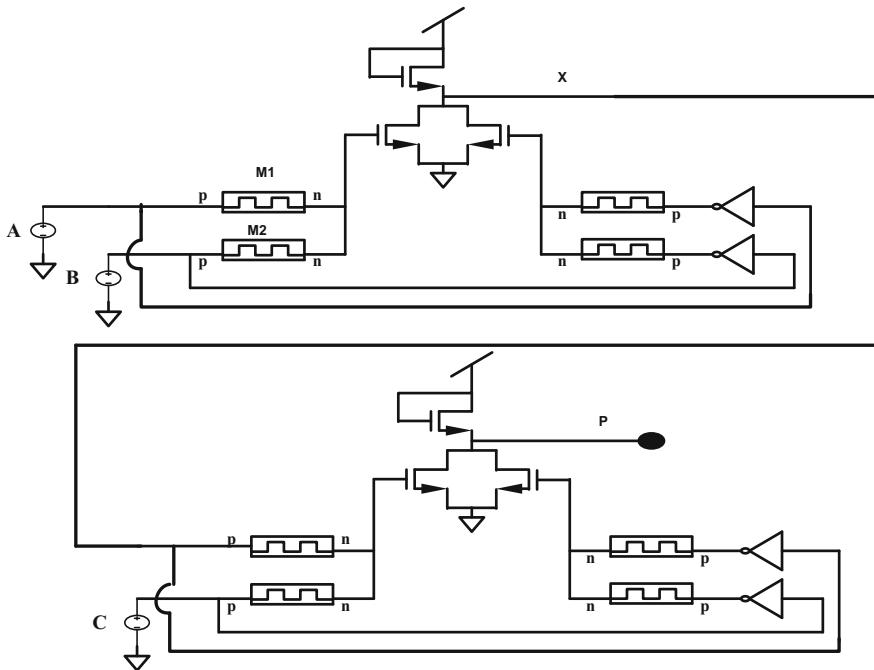

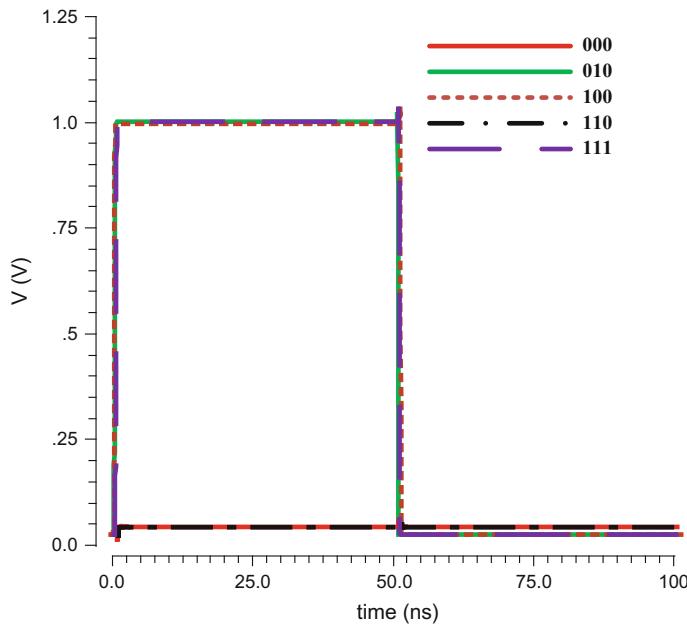

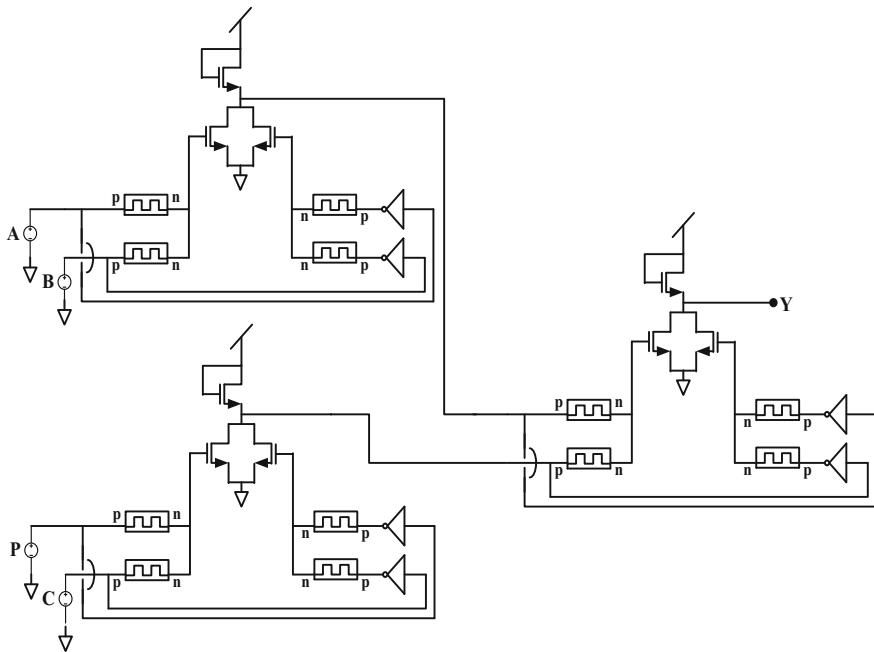

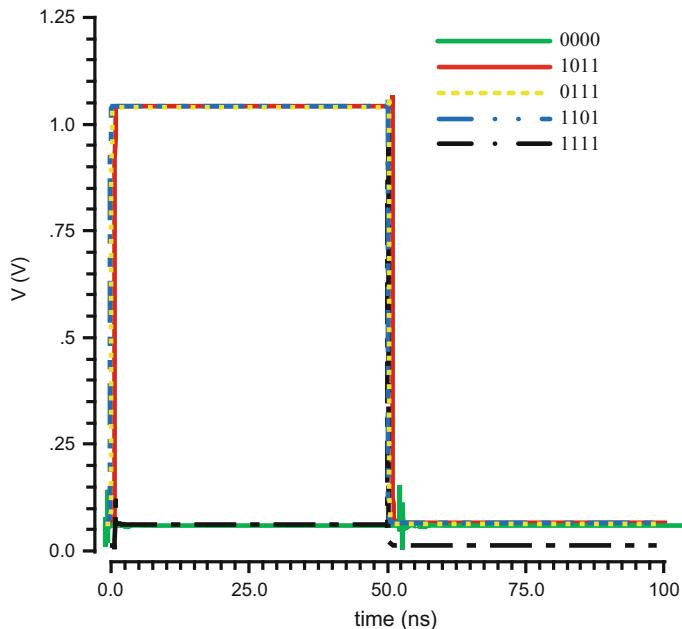

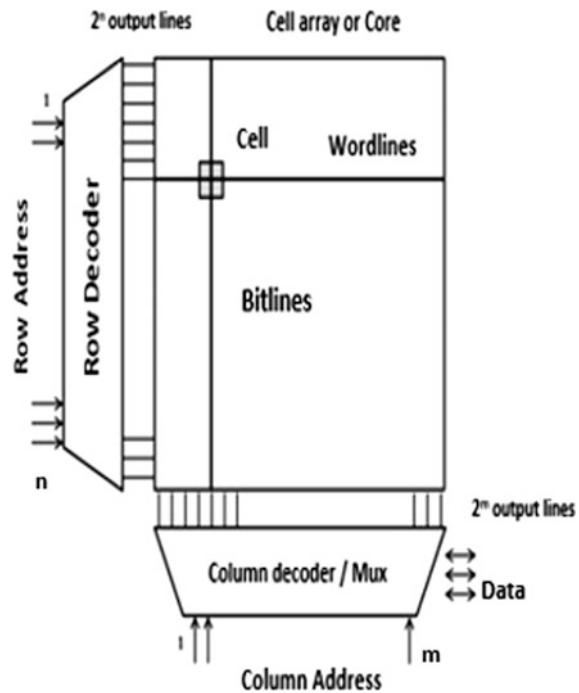

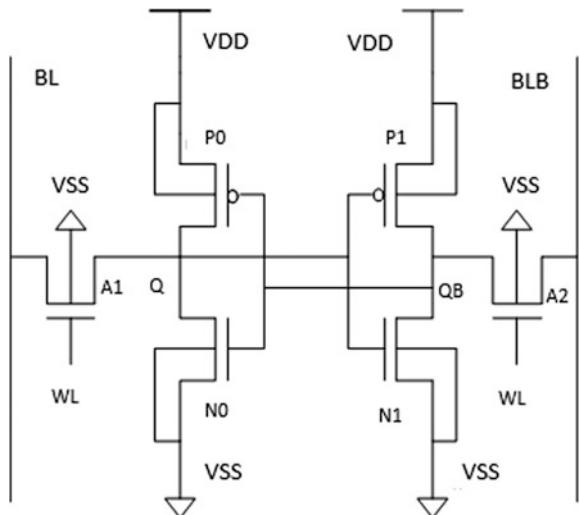

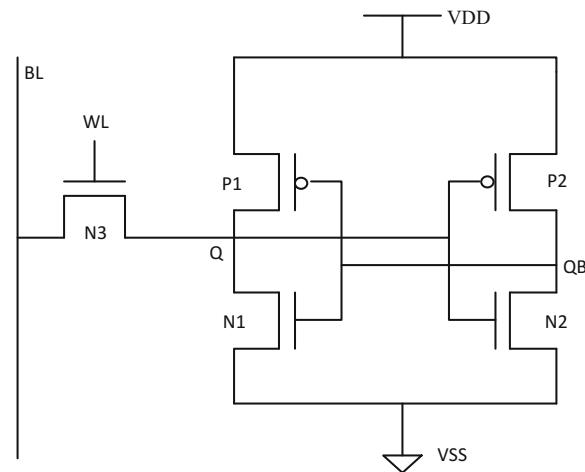

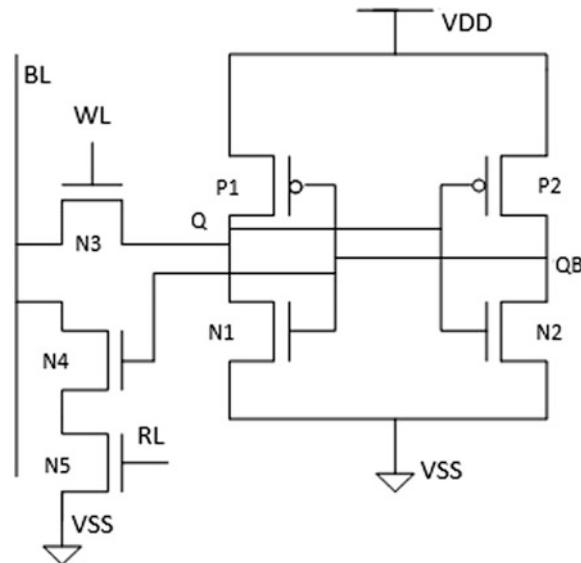

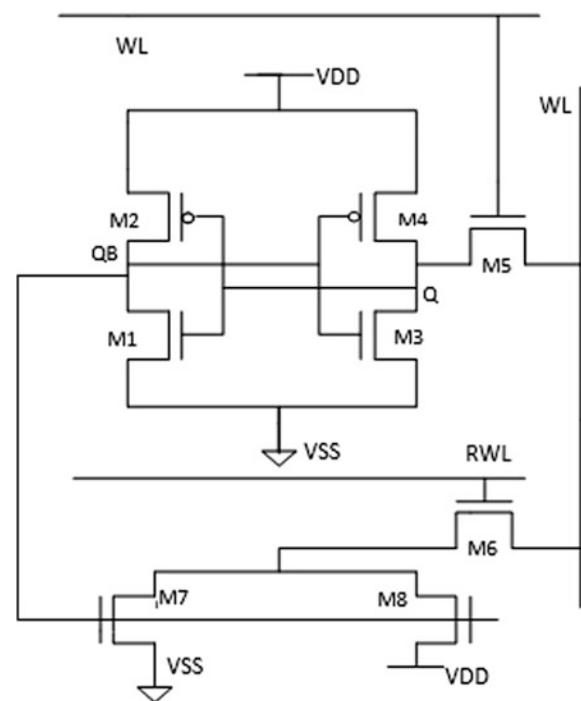

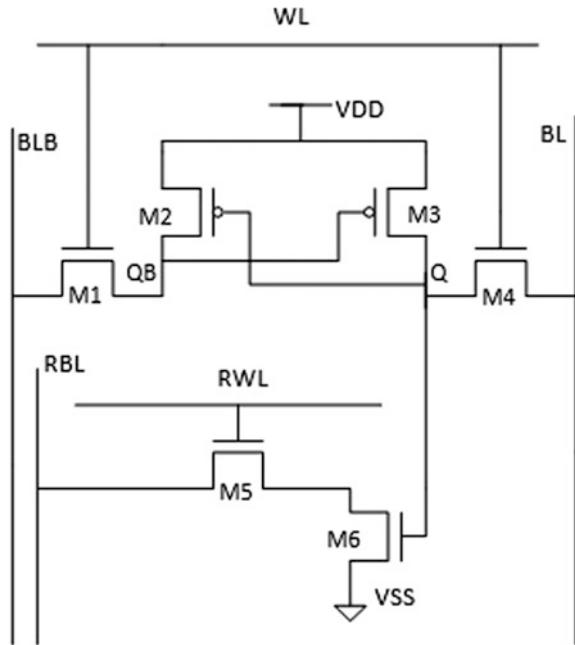

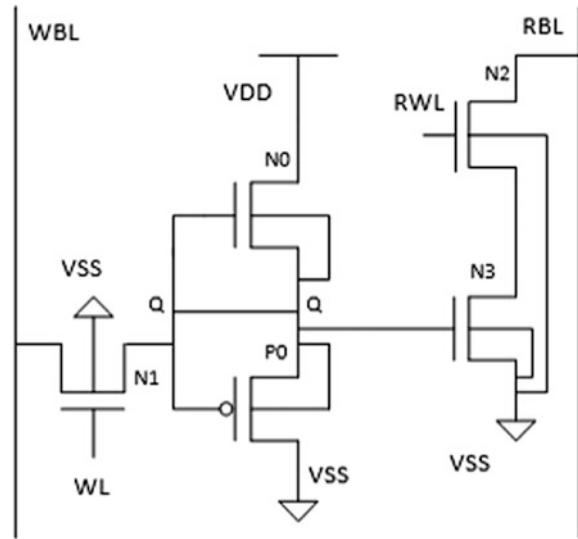

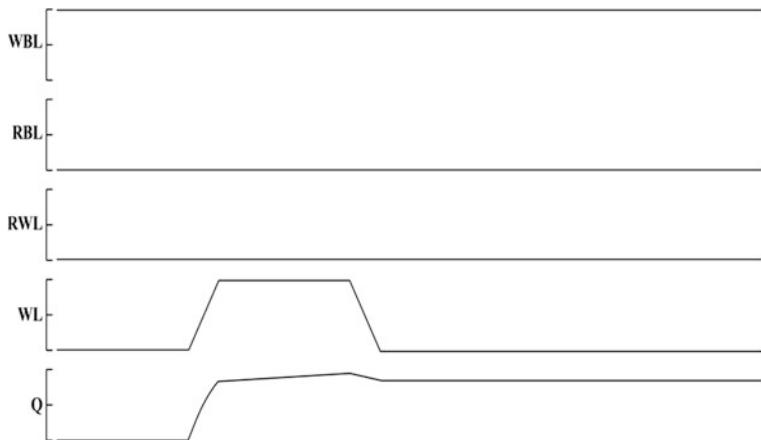

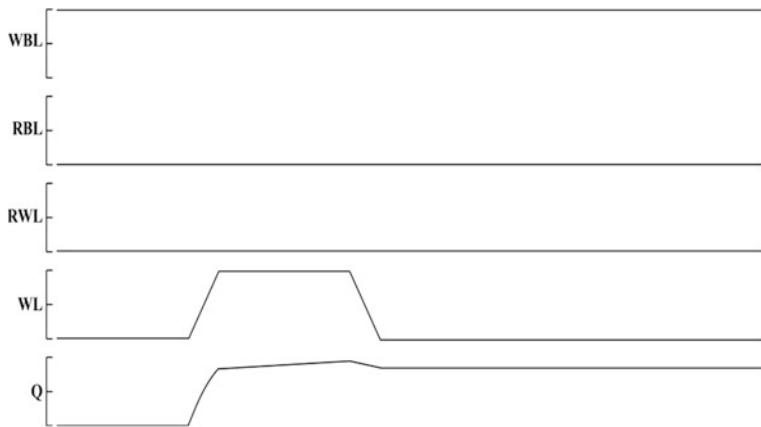

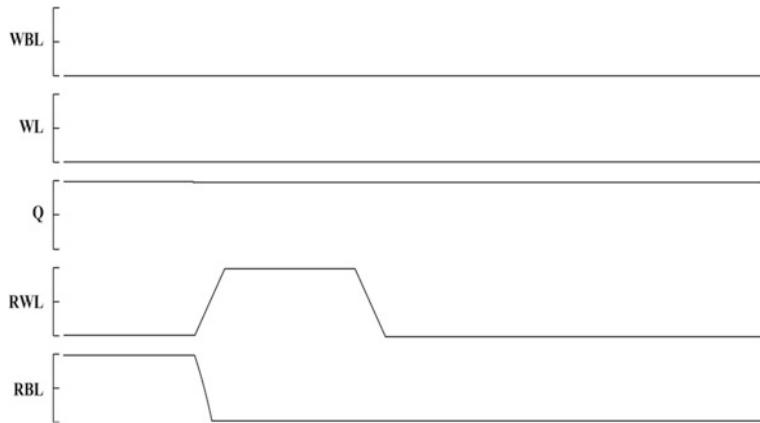

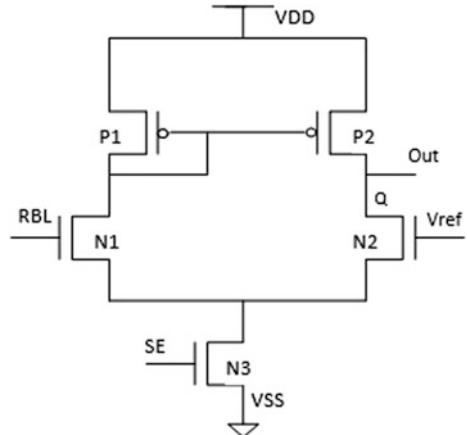

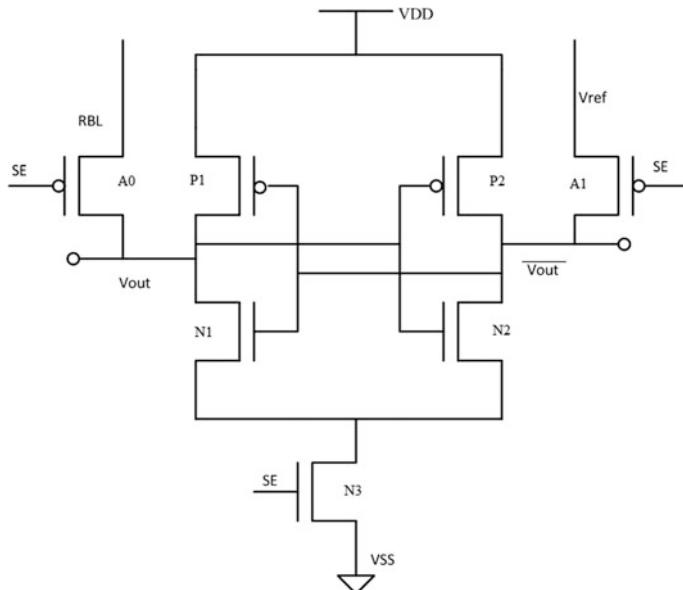

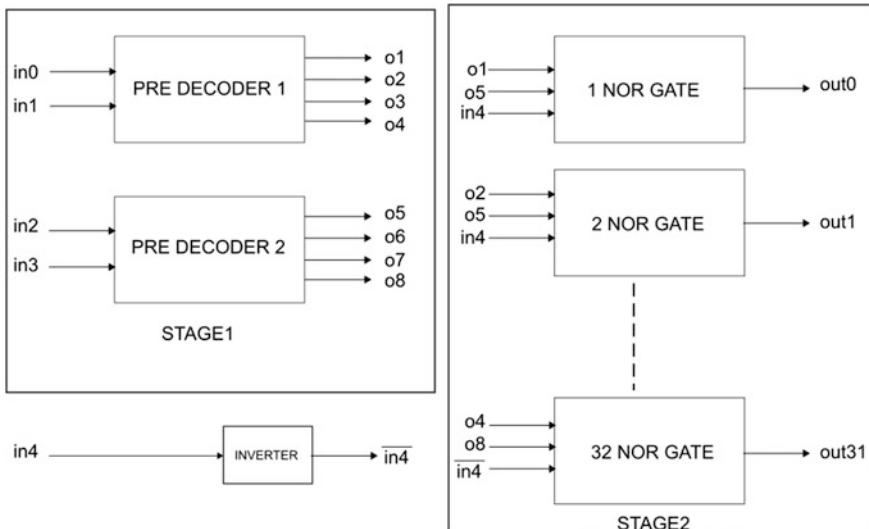

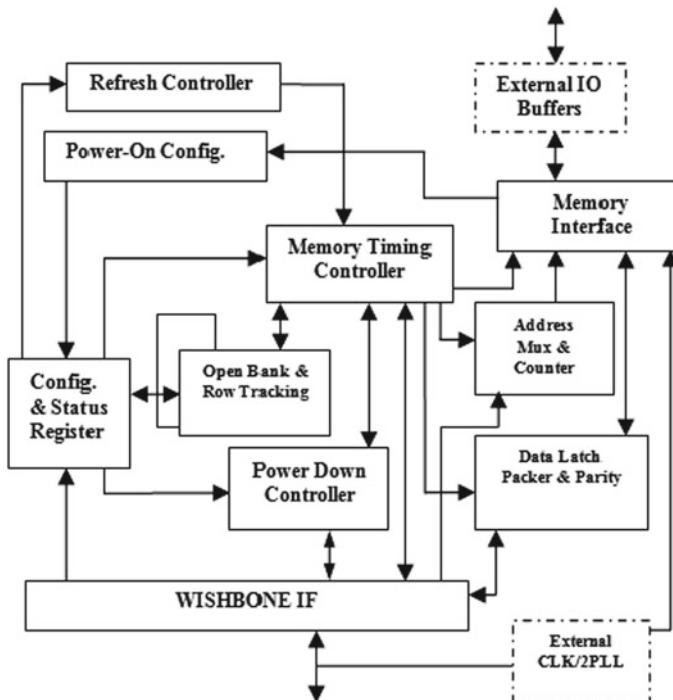

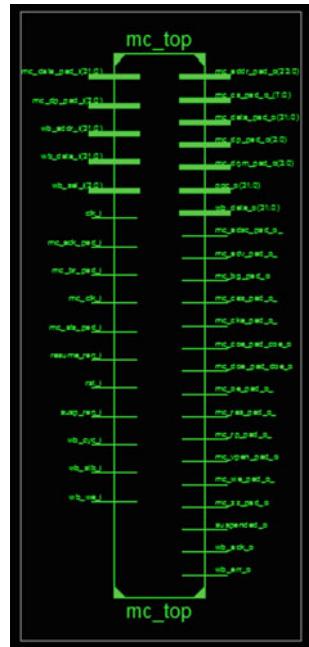

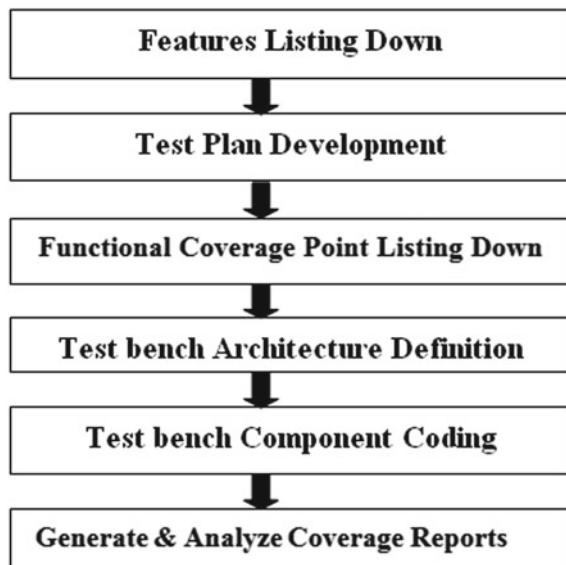

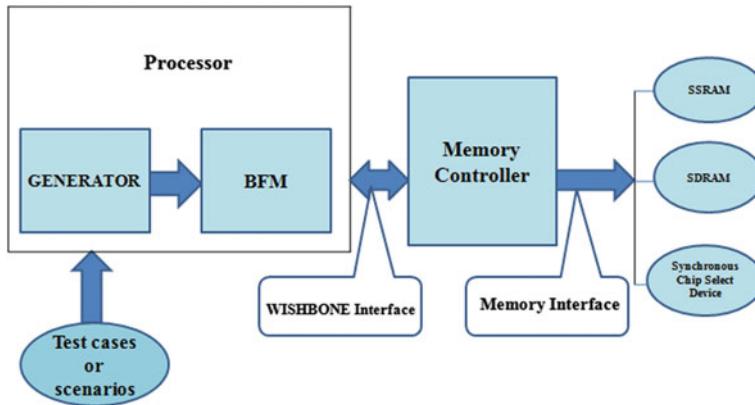

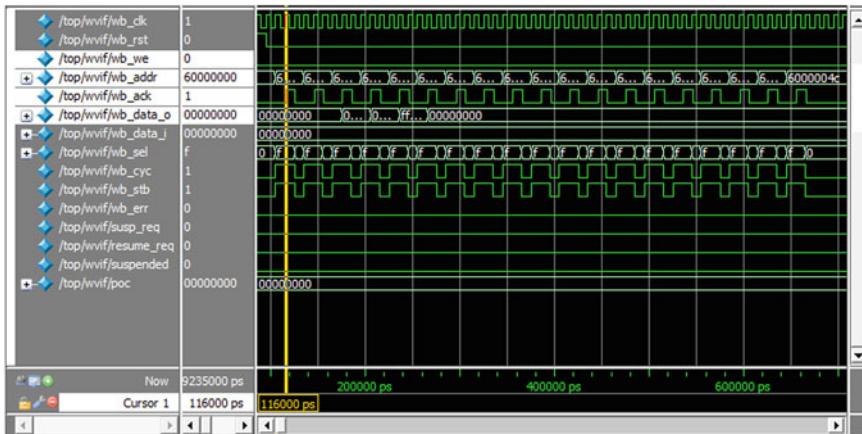

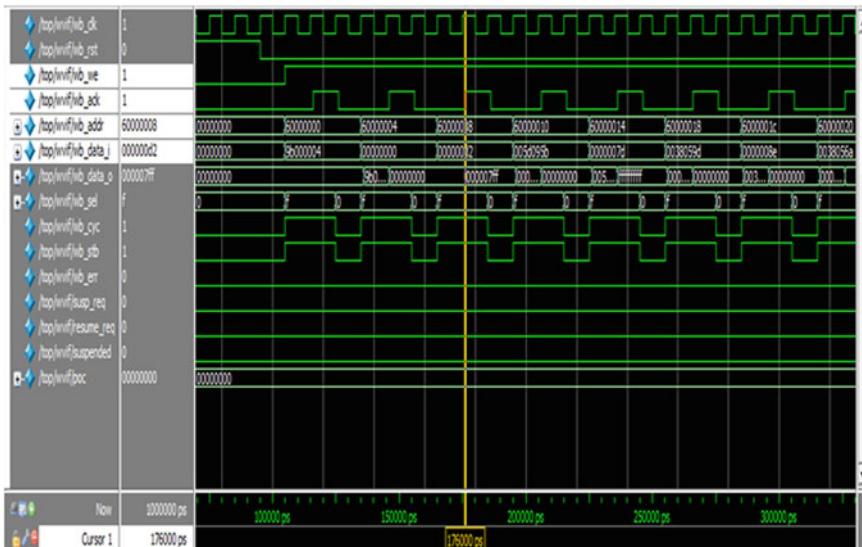

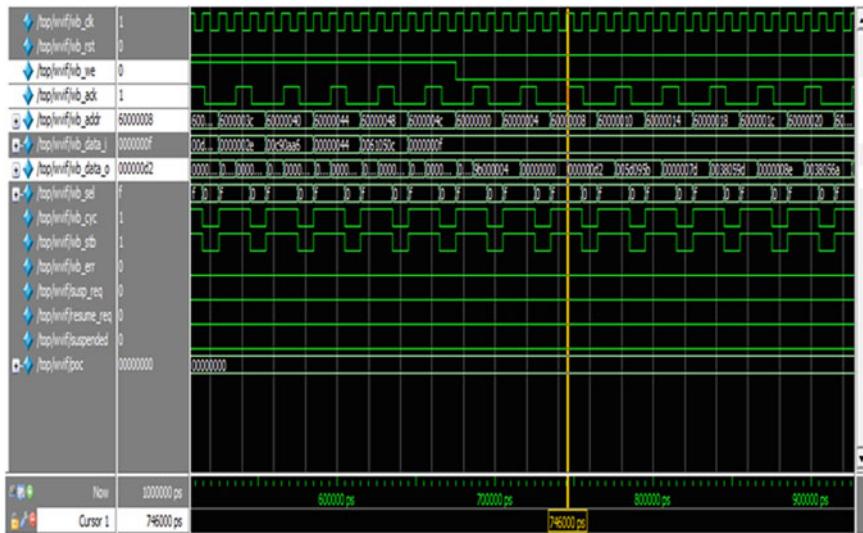

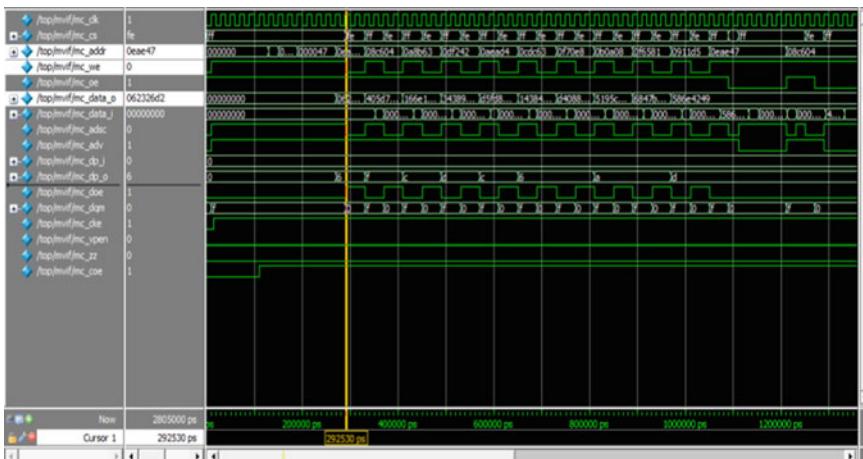

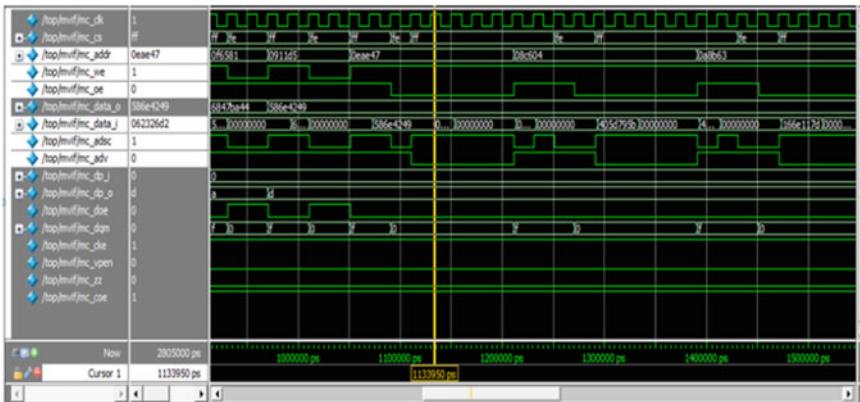

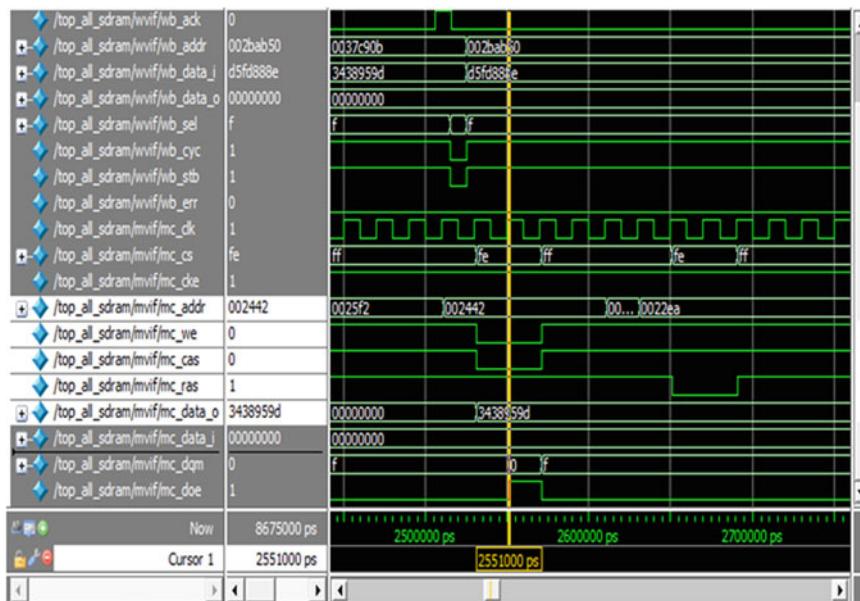

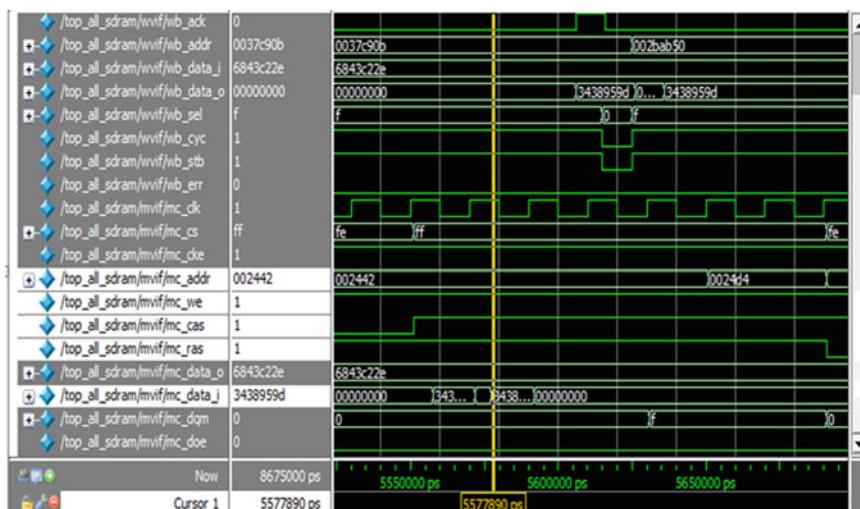

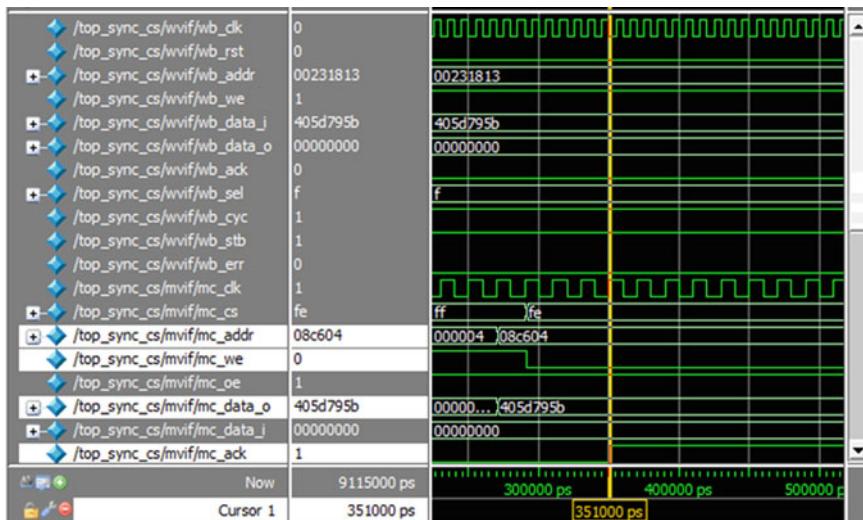

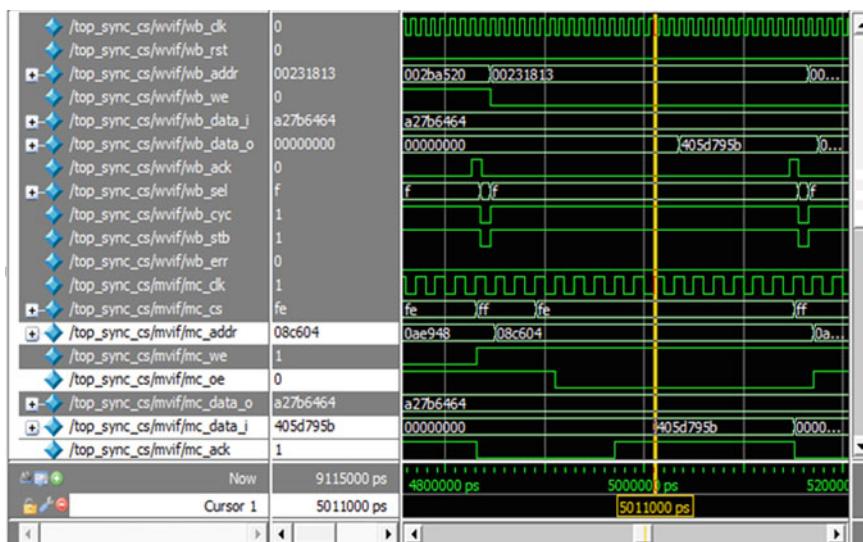

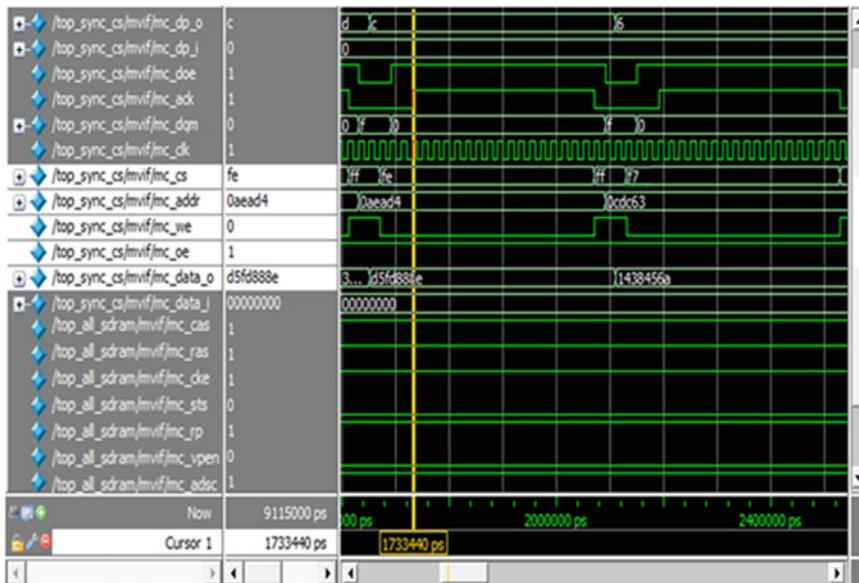

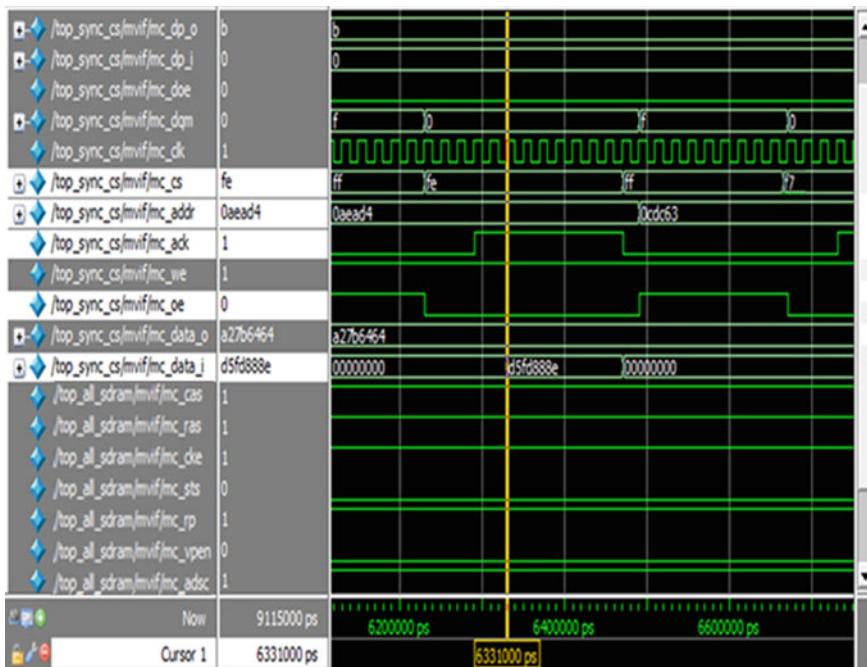

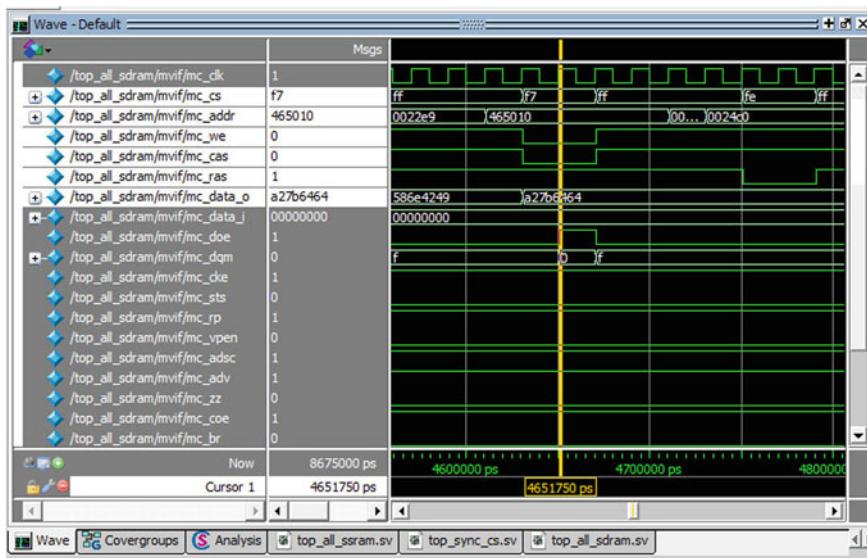

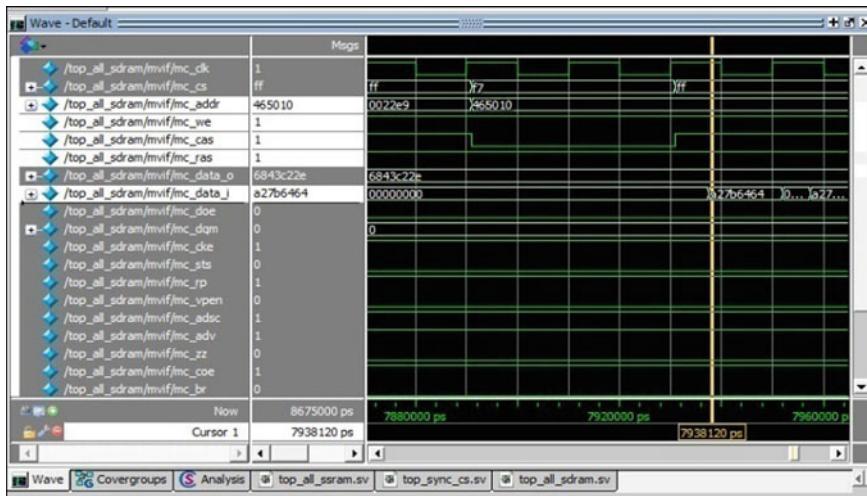

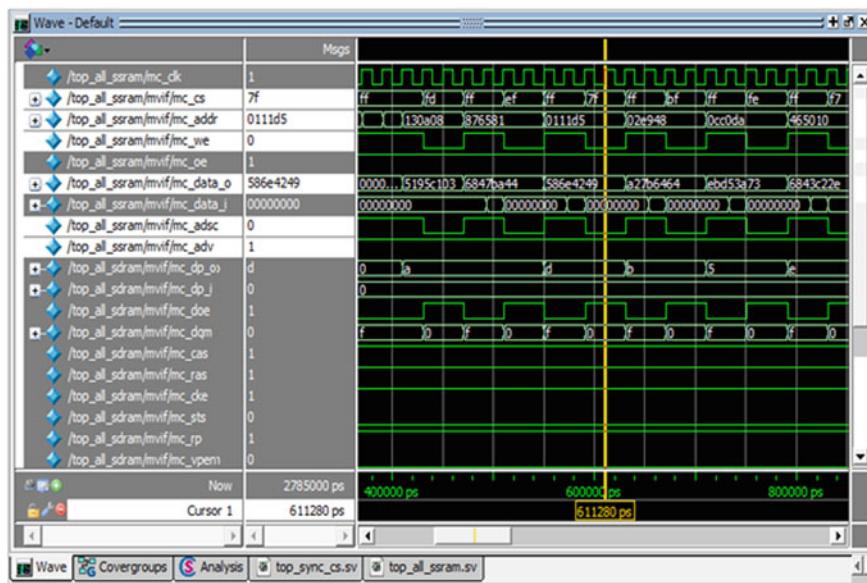

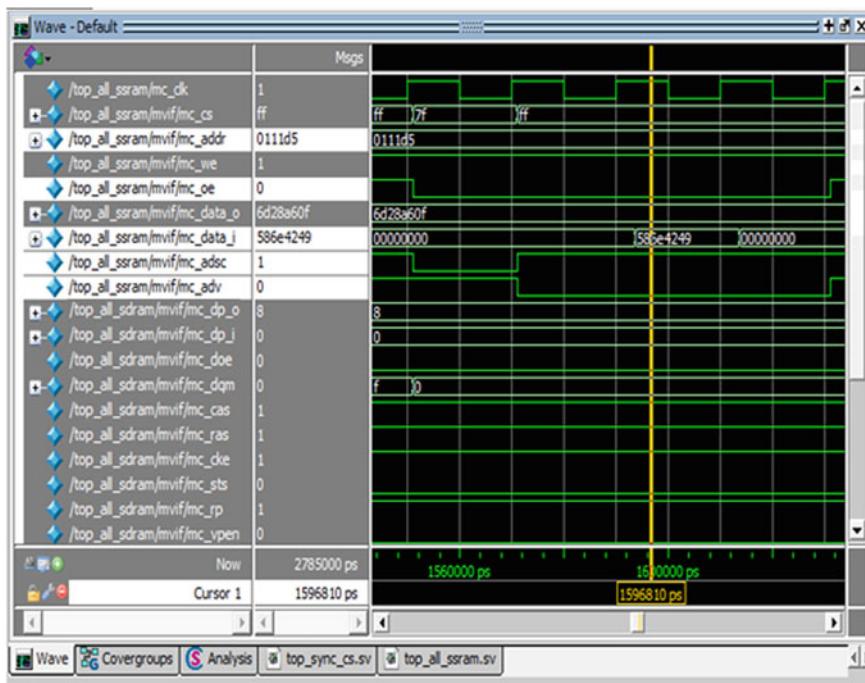

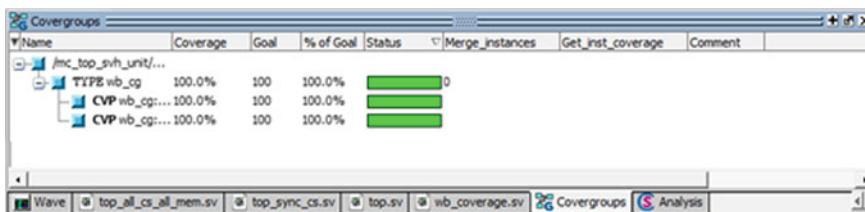

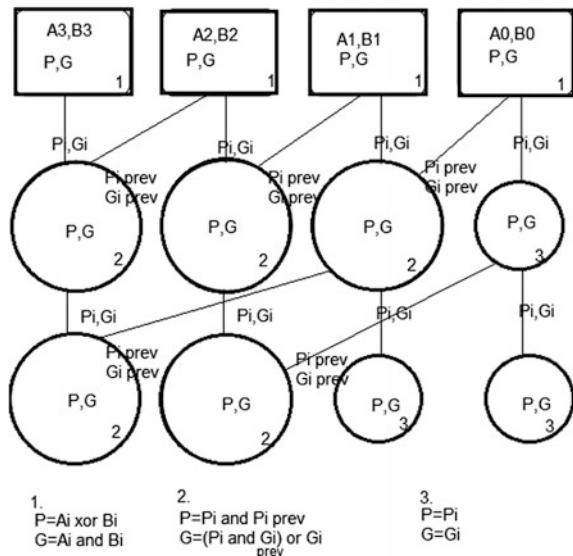

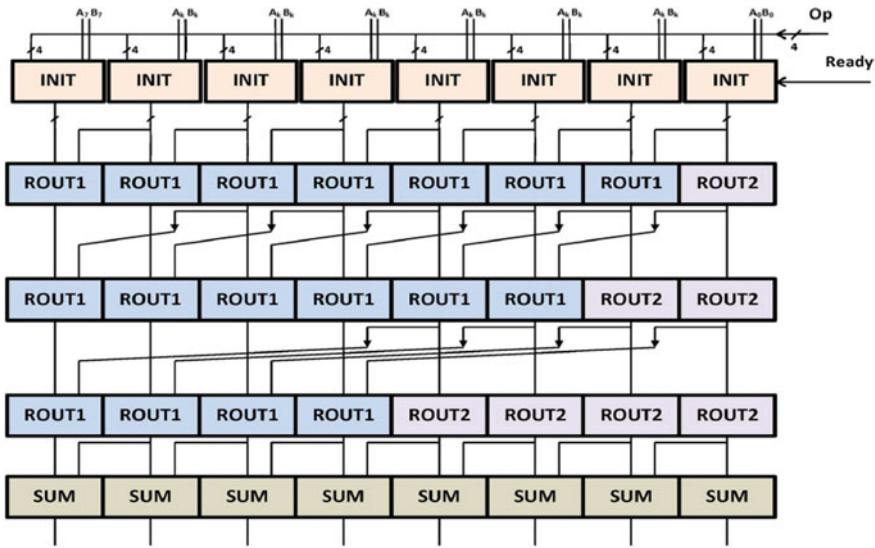

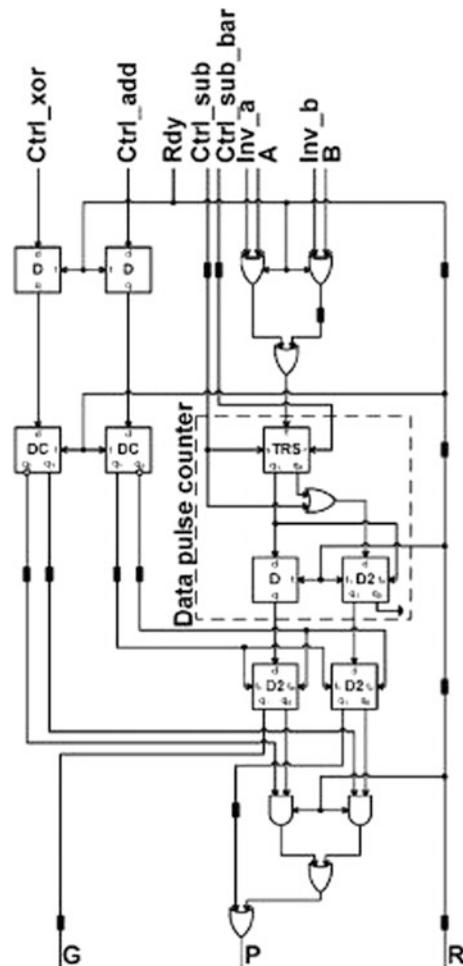

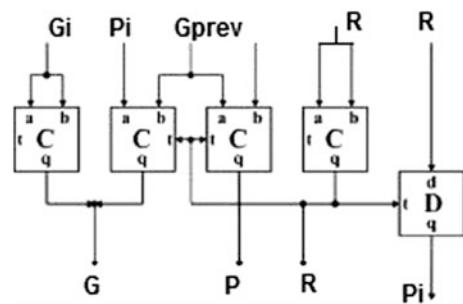

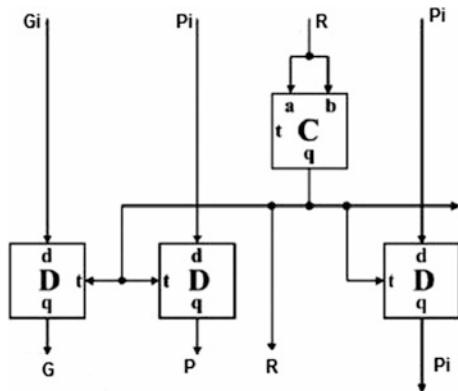

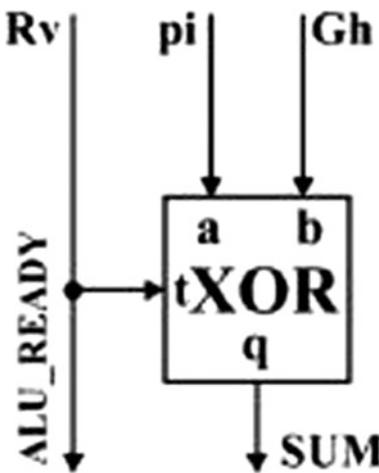

## 4 Conclusion