*Kevin James*

# *PC Interfacing and Data Acquisition*

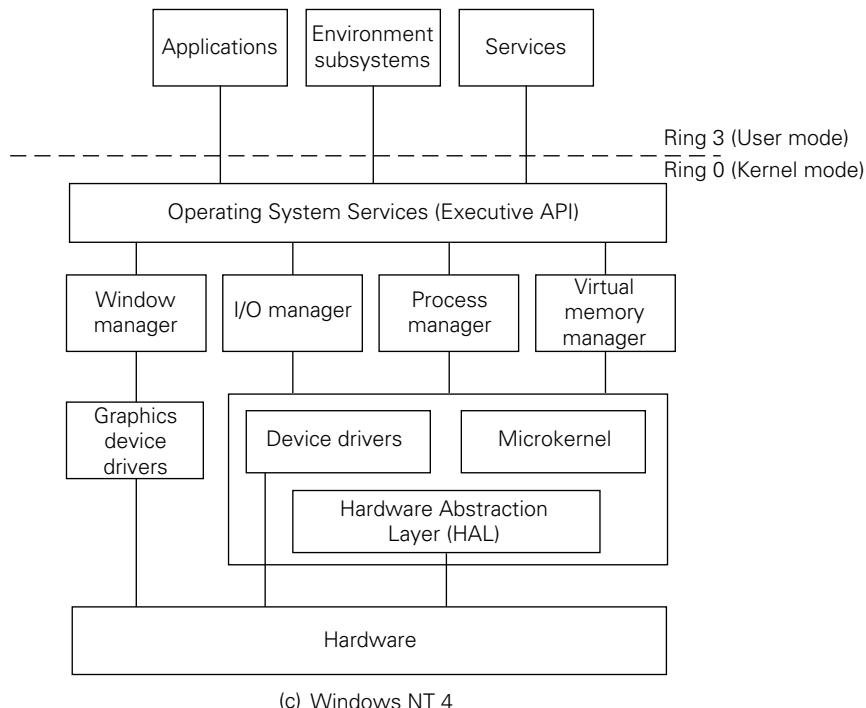

# PC Interfacing and Data Acquisition

**This Page Intentionally Left Blank**

# PC Interfacing and Data Acquisition: Techniques for Measurement, Instrumentation and Control

Kevin James

**Newnes**

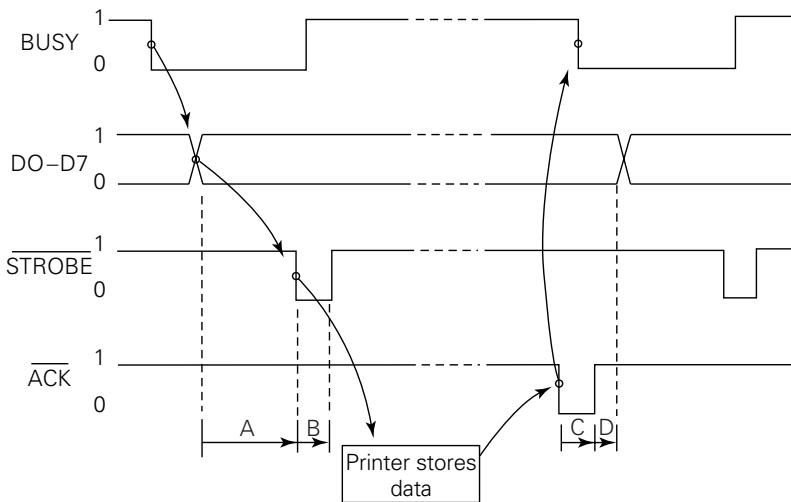

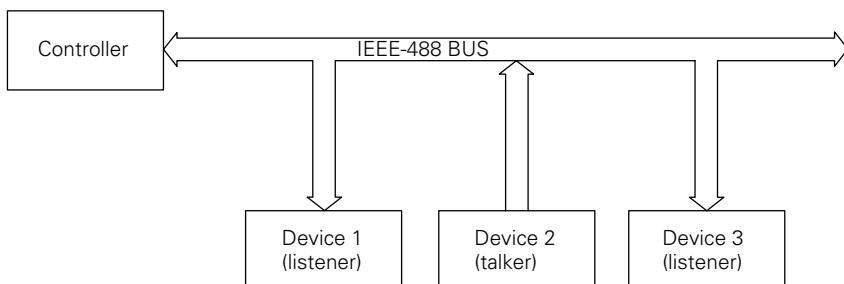

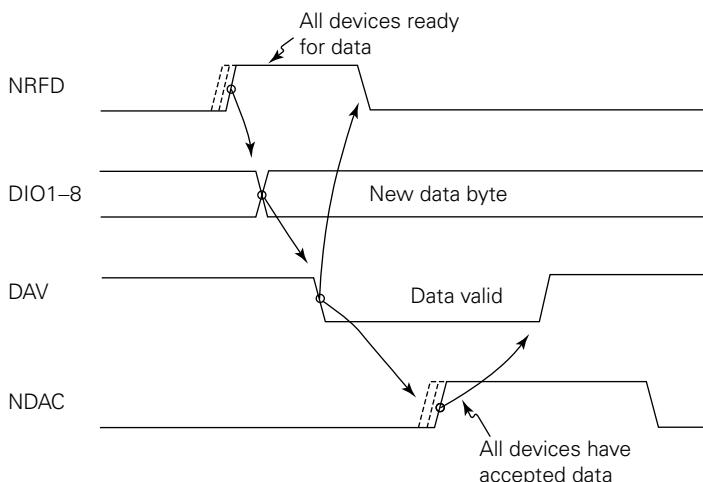

OXFORD AUCKLAND BOSTON JOHANNESBURG MELBOURNE NEW DELHI

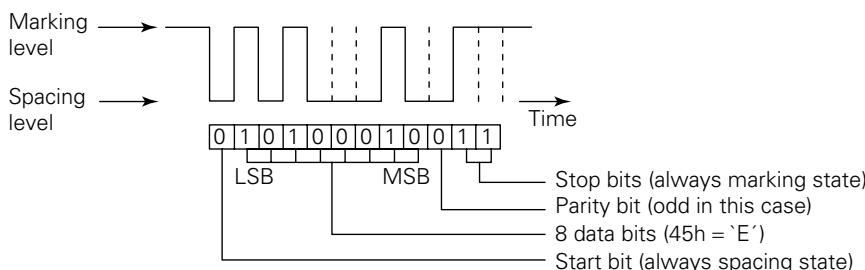

Newnes

An imprint of Butterworth-Heinemann

Linacre House, Jordan Hill, Oxford OX2 8DP

225 Wildwood Avenue, Woburn, MA 01801-2041

A division of Reed Educational and Professional Publishing Ltd

A member of the Reed Elsevier plc group

First published 2000

© Kevin James 2000

All rights reserved. No part of this publication may be reproduced in any material form (including photocopying or storing in any medium by electronic means and whether or not transiently or incidentally to some other use of this publication) without the written permission of the copyright holder except in accordance with the provisions of the Copyright, Designs and Patents Act 1988 or under the terms of a licence issued by the Copyright Licensing Agency Ltd, 90 Tottenham Court Road, London, England W1P 9HE. Applications for the copyright holder's written permission to reproduce any part of this publication should be addressed to the publishers

**British Library Cataloguing in Publication Data**

A catalogue record for this book is available from the British Library

ISBN 0 7506 4624 1

Typeset by Laser Words, Madras, India

Printed and bound in Great Britain

# Contents

|                                                           |     |

|-----------------------------------------------------------|-----|

| <b>Preface</b>                                            | ix  |

| A note on software examples                               | x   |

| <br>                                                      |     |

| <b>Part 1: Introduction to Data Acquisition on the PC</b> |     |

| 1 The PC as a platform for data acquisition               | 3   |

| 1.1 Types of PC                                           | 4   |

| 1.2 The processor                                         | 5   |

| 1.3 Memory                                                | 11  |

| 1.4 Input/output ports                                    | 15  |

| 1.5 Buses and adaptor card slots                          | 17  |

| 2 Software considerations                                 | 26  |

| 2.1 An overview of DA&C software                          | 26  |

| 2.2 Data acquisition and control in real time             | 30  |

| 2.3 Implementing real-time systems on the PC              | 45  |

| 2.4 Robustness, reliability and safety                    | 61  |

| <br>                                                      |     |

| <b>Part 2: Sampling Fundamentals</b>                      |     |

| 3 Sensors and interfacing                                 | 71  |

| 3.1 Introduction                                          | 71  |

| 3.2 Digital I/O                                           | 76  |

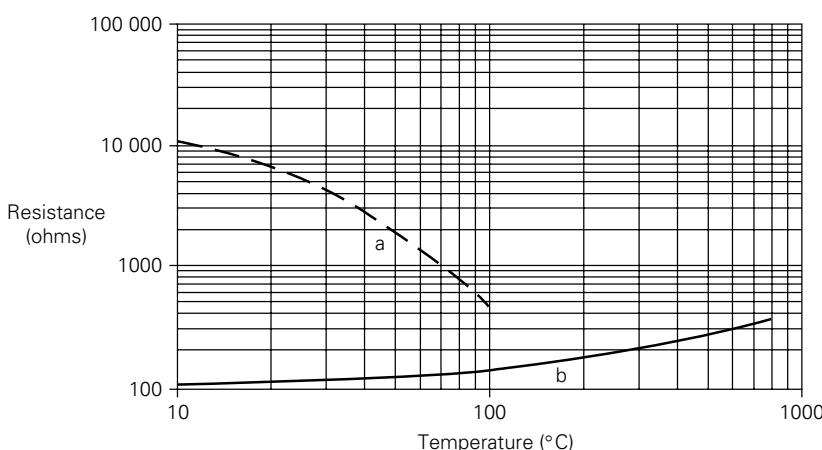

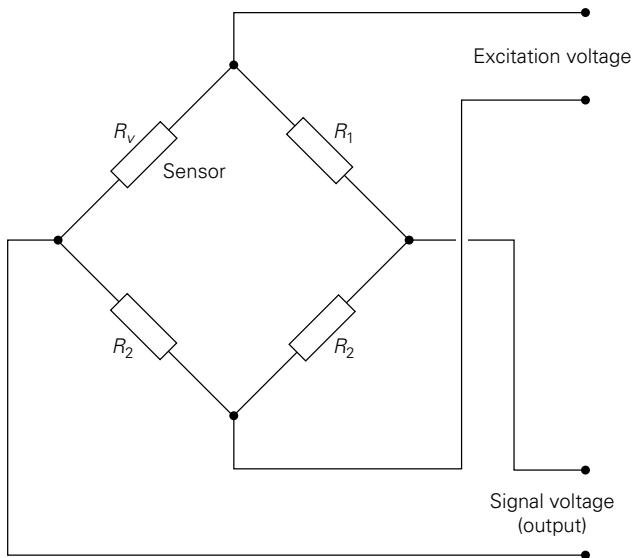

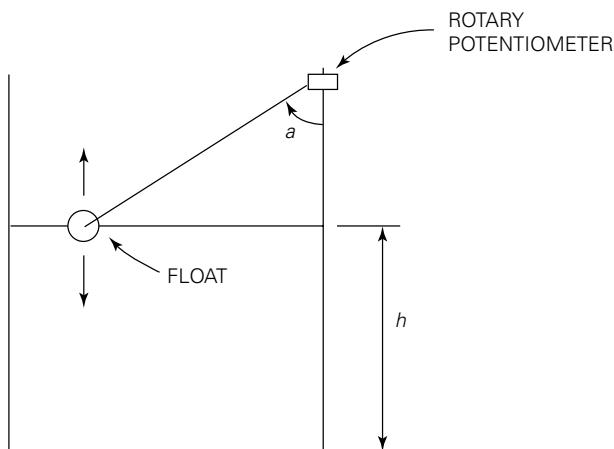

| 3.3 Sensors for analogue signals                          | 81  |

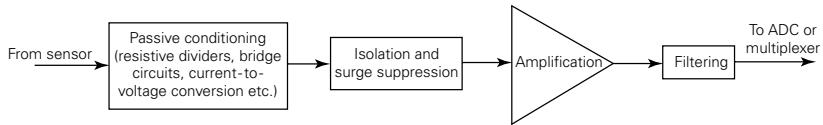

| 3.4 Handling analogue signals                             | 95  |

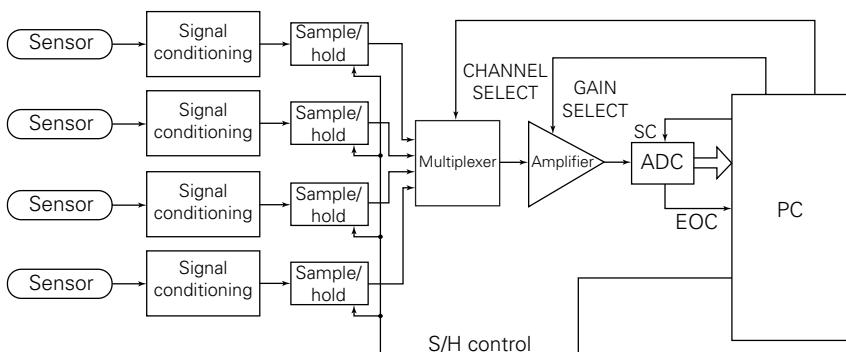

| 3.5 Digitization and signal conversion                    | 103 |

| 3.6 Analogue measurements                                 | 124 |

| 3.7 Timers and pacing                                     | 128 |

| 4 Sampling, noise and filtering                           | 131 |

| 4.1 Sampling and aliasing                                 | 131 |

| 4.2 Noise and filtering                                   | 142 |

|                                                     |     |

|-----------------------------------------------------|-----|

| <b>Part 3: I/O Techniques and Buses</b>             |     |

| 5 The interrupt system                              | 163 |

| 5.1 Interrupt vectors                               | 164 |

| 5.2 Hardware interrupts                             | 169 |

| 5.3 Software interrupts and processor exceptions    | 185 |

| 5.4 Interrupt priorities                            | 189 |

| 5.5 Writing interrupt handlers                      | 190 |

| 5.6 Re-entrancy and accessing shared resources      | 199 |

| 5.7 Interrupt response times                        | 200 |

| 6 Data transfer                                     | 205 |

| 6.1 Data-acquisition interface devices              | 205 |

| 6.2 Data transfer techniques and protocols          | 211 |

| 6.3 Buffers and buffered I/O                        | 244 |

| 7 Parallel buses                                    | 251 |

| 7.1 Introduction                                    | 252 |

| 7.2 Data acquisition using a parallel bus           | 253 |

| 7.3 The PC's parallel port                          | 254 |

| 7.4 The IEEE-488 (GPIB) bus                         | 270 |

| 8 Serial communications                             | 284 |

| 8.1 Some common terms                               | 284 |

| 8.2 Introduction to asynchronous communication      | 286 |

| 8.3 Data acquisition via a serial link              | 291 |

| 8.4 Serial interface standards                      | 296 |

| 8.5 Asynchronous serial I/O on the PC               | 308 |

| <b>Part 4: Interpreting and Using Acquired Data</b> |     |

| 9 Scaling and linearization                         | 345 |

| 9.1 Scaling of linear response curves               | 346 |

| 9.2 Linearization                                   | 356 |

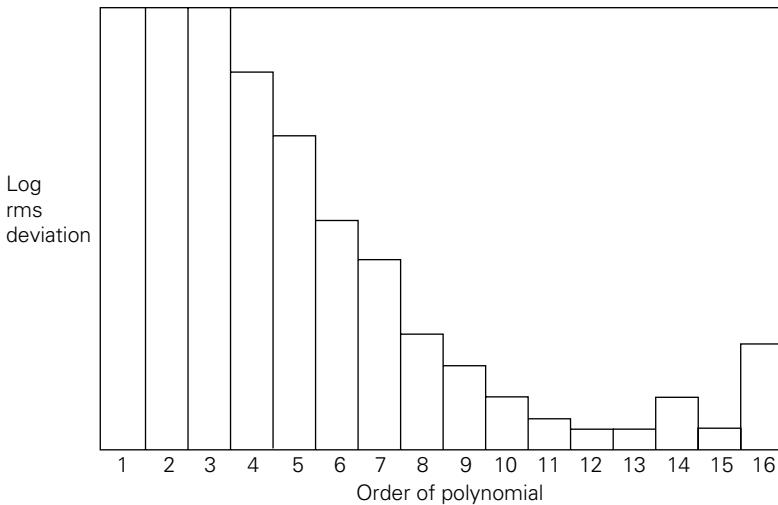

| 9.3 Polynomial linearization                        | 357 |

| 9.4 Interpolation between points in a look-up table | 373 |

| 9.5 Interpolation vs. power-series polynomials      | 381 |

| 9.6 Interactive calibration programs                | 381 |

| 9.7 Practical issues                                | 383 |

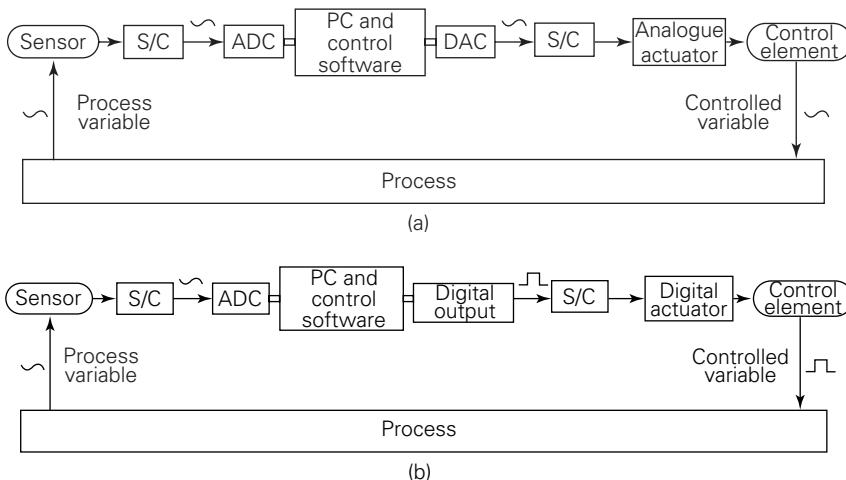

| 10 Basic control techniques                         | 387 |

| 10.1 Terminology                                    | 387 |

| 10.2 An overview of control systems                 | 388 |

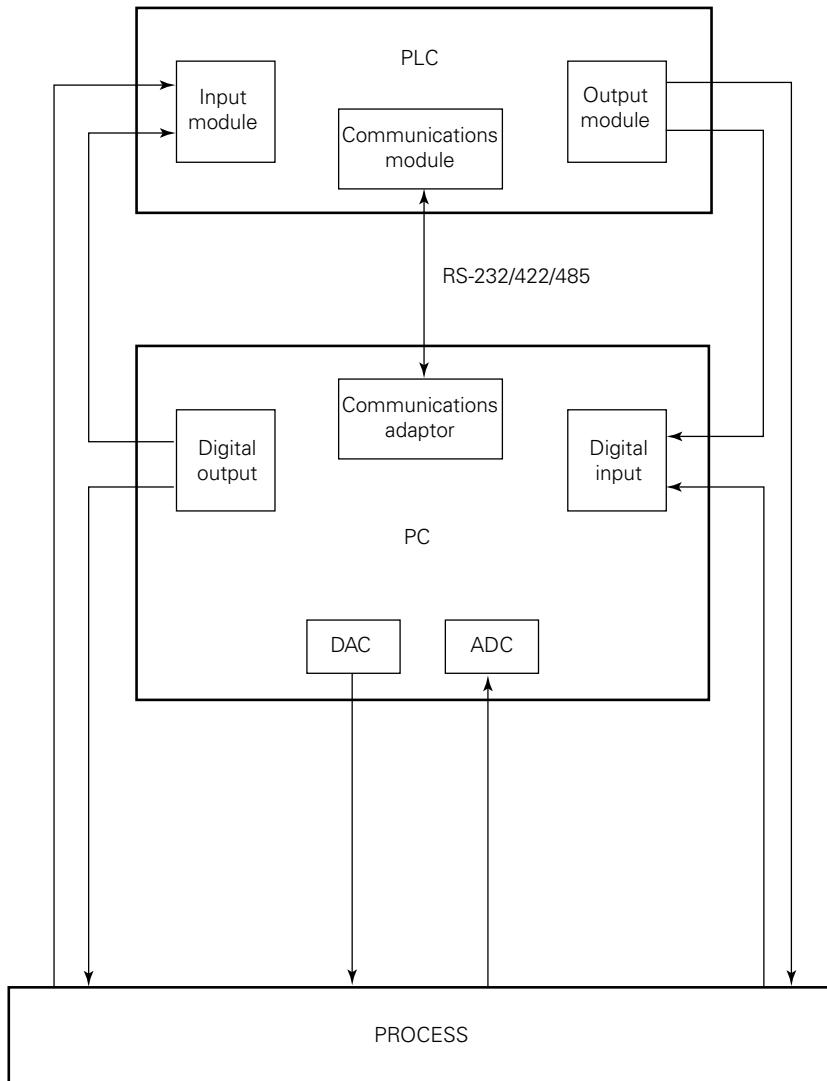

| 10.3 Programmable logic controllers                 | 390 |

| 10.4 Safety and reliability of control systems      | 391 |

| 10.5 Discontinuous control systems                  | 392 |

| 10.6 Continuous control systems                     | 396 |

**Part 5: Examples**

|                                                                        |     |

|------------------------------------------------------------------------|-----|

| 11 Example projects                                                    | 411 |

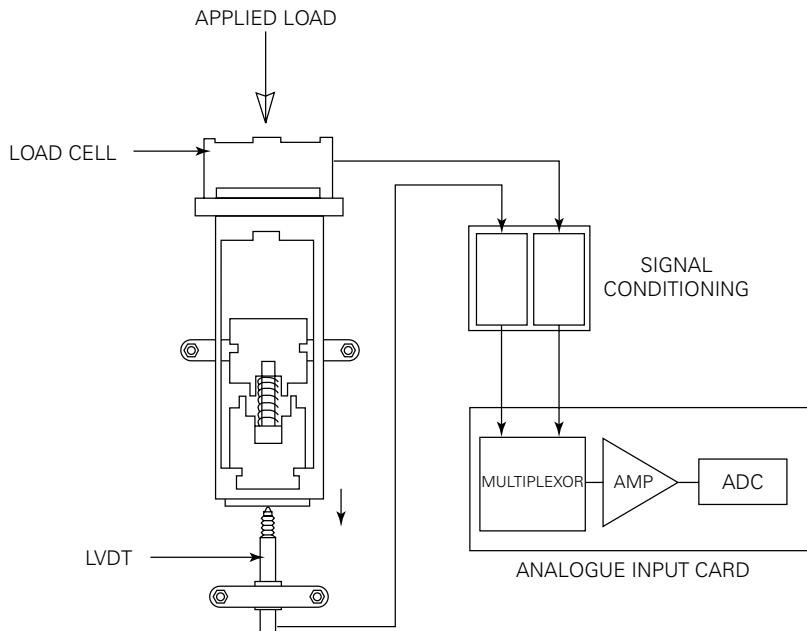

| 11.1 Dimensional gauging of railway carriage wheels                    | 411 |

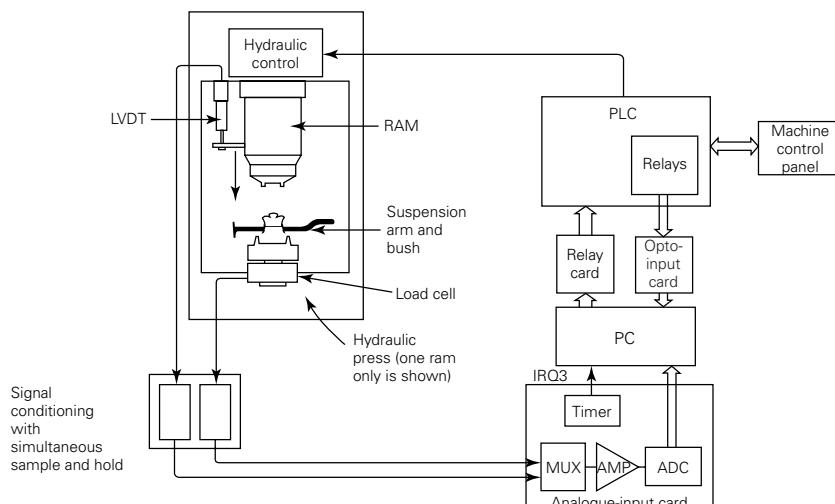

| 11.2 <i>In-situ</i> sensor calibration on a tube-straightening machine | 413 |

| 11.3 Dimensional gauging of turbine blades                             | 416 |

| 11.4 Torsional rigidity testing of car bodies                          | 420 |

| 11.5 Winch testing system                                              | 423 |

| 11.6 Brake actuator test system                                        | 426 |

| 11.7 Monitoring of bush-insertion load                                 | 429 |

| 11.8 Laboratory furnace temperature control                            | 432 |

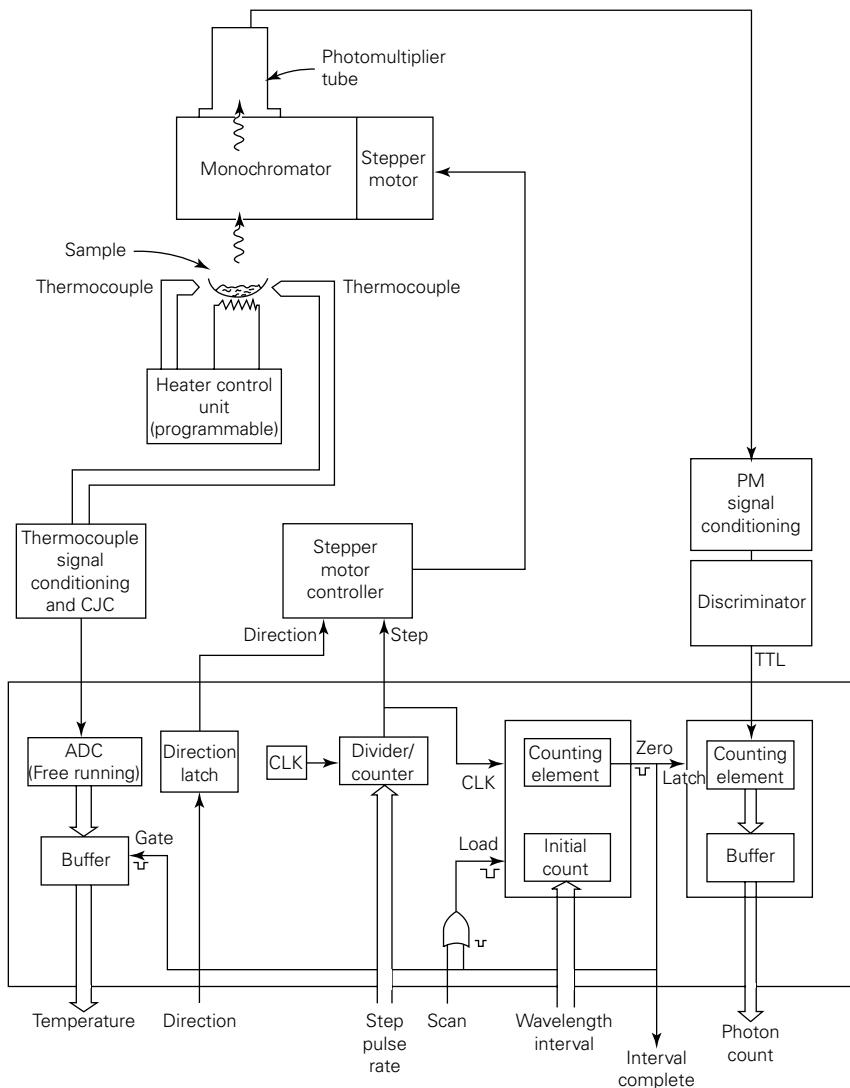

| 11.9 Thermoluminescence spectrometry                                   | 434 |

**Part 6: Appendices**

|                                           |     |

|-------------------------------------------|-----|

| Appendix A Adaptor installation reference | 441 |

| Appendix B Character codes                | 447 |

| <br>References                            | 453 |

| <br>Index                                 | 457 |

**This Page Intentionally Left Blank**

# Preface

Until fairly recently most scientific data-gathering systems and industrial control procedures were based on electromechanical devices such as chart recorders and analogue gauges. The capability to process and analyse data was rather limited (and in some cases error prone) unless one had access to a minicomputer or mainframe. Today, that situation has changed considerably. I am sure that most potential readers of this book will be aware of the profound effect the PC has had on the way in which engineers and scientists are able to approach data-gathering tasks.

Despite the now widespread use of various types of PC for automated data capture, there has been only a small number of publications on PC-based DA&C. Most if not all of these texts have concentrated on the hardware aspects of interfacing and measurement. A book emphasizing the design of DA&C *software* is long overdue.

One of the reasons for this has become increasingly apparent to me during the course of writing the present text. The subject spans numerous conventional disciplines and no single book can really do full justice to every aspect of this interdisciplinary subject. DA&C programming tends to require skills in (or at least a basic knowledge of) a range of subjects and, for this reason, the book draws together elements of programming, PC architecture, operating systems, interfacing, communications, sampling theory and process control.

My task has been complicated because of the wide range of backgrounds from which DA&C programmers tend to originate. Amongst the readership there will, no doubt, be fairly experienced programmers as well as engineers and scientists whose main area of expertise lies in fields other than computer programming. Some readers will already have a sound knowledge of data acquisition, while for others the principles of interfacing, measurement and control will be relatively new. With such a broad spectrum of potential

readers, it is inevitable that some users of the book will find that certain chapters provide unnecessary detail or that some topics are presented too concisely.

I have not assumed that the reader possesses any particular range of skills, although a broadly numerate or technical background and a basic knowledge of computer programming will undoubtedly be of benefit.

I have attempted to ensure that all information provided is correct and unambiguous. However, it is possible that a few minor errors will have found their way into the text. Unfortunately, it is in the nature of DA&C software that minor errors can have catastrophic results and, for this reason, I strongly advise you to cross-check all critical information that you use in your software against independent sources, and to thoroughly test all programs before 'going live'. I would greatly appreciate hearing of any errors in the text, whether technical or typographic. I can be contacted at: [kjames\\_sd@hotmail.com](mailto:kjames_sd@hotmail.com).

## **A note on software examples**

The code examples are presented with the primary intention of conveying the ideas presented in the text. In some cases this involves a trade-off between clarity and execution speed. In most instances I have favoured the former. You may wish to recode some of the examples to improve their efficiency and speed.

Note that the software listings are intended only as examples of how one might go about solving isolated coding problems. They are not intended as complete working programs or solutions to specific problems. For reasons of clarity, the examples are designed to operate in a real-mode (DOS) environment. In many cases the code may be adapted for use in protected mode or under 32-bit multitasking operating systems such as Microsoft Windows NT.

Although I have tested every example and they work correctly under my test conditions, factors such as execution speed and timing, hardware variability, and incompatibilities with other software (e.g. operating systems) may affect them. If you use them in your own programs you should thoroughly test them to ensure that they work correctly and reliably within the context of your application.

The examples are presented in a mixture of C and assembly language. While assembly language is *essential* for some low level programming tasks, the programmer has more scope when choosing a high level language (HLL). I have chosen C (specifically Borland C version 3) for the examples in this book mainly because it is the most widely used language in DA&C and interfacing applications.

I recognize that C code does not have a favourable reputation for clarity. For this reason, and to enable readers to translate easily to other languages, I have avoided C's shorthand notation and have used only constructs which have analogues in other HLLs. You should bear in mind that there tends to be subtle variations between different dialects of C. One such variation occurs in the various I/O instructions as described in Chapter 6. Another that is particularly relevant here concerns integer data types. Throughout the text, I have used the `int` data type as a 16-bit quantity, but in some 32-bit compilers (e.g. Microsoft Visual C ++ version 4.0) it is treated as a 32-bit integer. Be sure that you know how your system interprets `int` declarations. Those readers who have any doubts over the meaning of C data declarations and statements should consult one of the numerous introductory C texts as well as their C compiler's programming manual.

**This Page Intentionally Left Blank**

# Part 1 Introduction to Data Acquisition on the PC

**This Page Intentionally Left Blank**

# 1 The PC as a platform for data acquisition

The field of data acquisition and control (DA&C) encompasses a very wide range of activities. At its simplest level, it involves reading electrical signals into a computer from some form of sensor. These signals may represent the state of a physical process, such as the position and orientation of machine tools, the temperature of a furnace or the size and shape of a manufactured component. The acquired data may have to be stored, printed or displayed. Often the data have to be analysed or processed in some way in order to generate further signals for controlling external equipment or for interfacing to other computers. This may involve manipulating only static readings, but it is also frequently necessary to deal with time-varying signals as well.

Some systems may require data to be gathered slowly, over time spans of many days or weeks. Other will necessitate short bursts of very high speed data acquisition – perhaps at rates of up to several thousand readings per second. The dynamic nature of many DA&C applications is a fundamental consideration which we will repeatedly return to in this book.

The IBM PC is, unfortunately, not an ideal platform for DA&C. There are a number of problems associated with using it in situations which demand guaranteed response times. However, it is used widely for laboratory automation, industrial monitoring and control, as well as in a variety of other time-critical applications. So why is it so popular?

The most obvious reason is, of course, that the proliferation of office desktop systems, running word processing, accounting, DTP, graphics, CAD and many other types of software, has led IBM and numerous independent PC-clone manufacturers to develop ever more powerful and inexpensive computer systems. The technology is now well developed and stable in most respects. For the same reason, an enormous software base now exists for this platform. This includes all manner of scientific, statistical analysis, mathematical and

engineering packages that may be used to analyse acquired data. A wide range of software development tools, libraries, data-acquisition hardware and technical documentation is also available. Perhaps the most important reason for using the PC for data acquisition and control is that there is now a large and expanding pool of programmers, engineers and scientists who are familiar with the PC. Indeed it is quite likely that many of these personnel will have learnt how to program on an IBM PC or PC clone.

This book sets out to present some of the basic concepts of DA&C programming from a practical perspective and to illustrate how elements of the PC architecture can be employed in DA&C systems. Although it contains quite detailed descriptions of certain elements of the PC's hardware and interface adaptors, the text concentrates on the software techniques that are required to make effective use of the PC for DA&C. The first two chapters begin by discussing the structure of DA&C systems and attempt to assess how well the PC and its operating systems meet the stringent requirements of data acquisition and real-time operation.

## **1.1 Types of PC**

Since the first models of the IBM Personal Computer (PC) were introduced in the early 1980s there have been many variants issued by IBM and by numerous 'clone' manufacturers. Each new variant has tended to introduce improved components or subsystems which enhance speed or provide some other system capability. We will not describe the various models of PC in detail here as most readers will already be familiar with the basic differences between the XT, AT, PS/2 and EISA machines. It is sufficient to note that the basic architecture of most types of PC is very similar. The differences in performance between systems arise from the different types of processor, memory subsystem and expansion bus used. These are perhaps the most important considerations although other components, such as the disk and video subsystems, can substantially affect throughput.

The IBM PC was originally developed as a stand-alone machine for office desktop use. While many DA&C applications can, and do, run successfully on such systems, desktop models do not always provide the required degree of robustness for use in harsh environments. This has led a number of manufacturers to produce more rugged versions of the PC. Many systems are built into rack-mounted chassis. They may incorporate conventional motherboard designs or they may utilize a backplane system into which a processor card, video adaptors and disk drive controllers are inserted. Ruggedized industrial PCs offer benefits such as sealed keyboards, positively

pressurized cooling systems, and anti-vibration shock mountings. Both hard disks and floppy disk drives tend to be easily damaged by dust, vibration and magnetic fields. These problems are circumvented in some systems by substituting a solid state (i.e. EPROM or SRAM based) disk emulation card which is generally less susceptible to damage.

Some industrial PCs may possess interfaces for disks, serial ports, parallel ports, and other peripheral devices on the same circuit board. Single-board computers are often integrated into dedicated equipment which is used, for example, in industrial or medical monitoring applications. These embedded systems are normally designed so as to minimize size, power consumption and cooling requirements. In these systems, hard disks are frequently replaced by ROM-based devices which provide storage for all software, including the operating system. Embedded PC controllers are also used in mobile equipment. However, there are a number of other options when it comes to mobile computing. There are now many notebook PCs and ruggedized portable computers on the market. These can easily interface to external data logging or control equipment in order to facilitate configuration or downloading of acquired data.

Ruggedized PCs, embedded PC systems, portable machines and desktop PCs all share the same basic architecture and are generally capable of running the same software. The structural differences between them are largely irrelevant to the software engineer. Indeed software can usually be developed on a desktop system and then transferred to a ruggedized or portable PC without modification, although minor changes may sometimes be needed when porting to embedded systems in order to accommodate ROM-based operating systems or to interface to specialized external buses.

## 1.2 The processor

Most readers of this book will already be aware of the different types of processor and coprocessor used in the PC range. This section summarizes the most important characteristics of each of the main classes of processor. The text by Hummel (1992) provides more detailed descriptions of the various processors and coprocessors available.

### ***The 80x86 family of processors***

Pentium processors are perhaps the most recognized components of today's PCs. They originate from a long line of Intel processors dating back to the 1970s (see Table 1.1). The capabilities of the

## 6 PC interfacing and data acquisition

**Table 1.1** Comparison of 80x86/Pentium processors

| Processor   | Address range | Data width (bits) | Clock (internal) (MHz) | Approx. relative speed <sup>(3)</sup> | New features and notes                                                                                                                                 |

|-------------|---------------|-------------------|------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8088        | 1 MB          | 8                 | 4.77                   | 1                                     | Real mode only.                                                                                                                                        |

| 8086        | 1 MB          | 16                | 4.77, 8                | 1.5                                   | Real mode only. Required 8087 floating-point unit.                                                                                                     |

| 80286       | 16 MB         | 16                | 6–16                   | 5                                     | Limited protection features in protected mode. Required 80287 floating-point unit.                                                                     |

| 80386SX     | 16 MB         | 32 <sup>(1)</sup> | 16–25                  | 10                                    | Enhanced protected V86 mode. Required 80387 floating-point unit.                                                                                       |

| 80386DX     | 4 GB          | 32                | 16–40                  | 15                                    | 32-bit data and address buses. Required 80387 floating-point unit.                                                                                     |

| 80486SX     | 4 GB          | 32                | 25–40                  | 40                                    | Parallel instruction execution. 8 Kbyte on-chip cache. Internal clock doubling, tripling and quadrupling circuits. Required 80487 floating-point unit. |

| 80486DX     | 4 GB          | 32                | 25–100                 | 60                                    | On-chip numeric processor.                                                                                                                             |

| Pentium     | 4 GB          | 32 <sup>(2)</sup> | 60–166                 | 200                                   | Dual execution pipeline. Enhanced branch prediction. Enhanced V86 paging. Multiprocessor support.                                                      |

| Pentium Pro | 64 GB         | 32 <sup>(2)</sup> | 200, 266               | 500                                   | Triple pipelining. 256 Kbyte L2 cache. 36-bit address bus.                                                                                             |

| Pentium II  | 64 GB         | 32 <sup>(2)</sup> | 200–450                | 800                                   | Enhanced L1 and L2 caches. Power saving features. MMX extensions.                                                                                      |

| Pentium III | 64 GB         | 32 <sup>(2)</sup> | 500+                   | 1000+                                 | Very efficient floating-point unit. Katmai New Instructions and new KNI mode.                                                                          |

<sup>(1)</sup>16-bit external bus.

<sup>(2)</sup>64-bit external bus.

<sup>(3)</sup>Integer processing. Figures are a rough guide only. Actual speed depends on clock rate, instruction mix and performance of PC subsystems.

earlier processors will be of little relevance to most readers who, nowadays, are not likely to encounter anything more primitive than an 80486. For this reason we will not discuss them in any further detail. We should remember, though, that some specialized systems (particularly embedded PC applications) still make use of the earlier 8086, 80286 and 80386 processors. Indeed, special versions have been developed for this market. The 80186, for example, is similar to the 8086, but also possesses on-chip DMA (Direct Memory Access) and interrupt controllers and other support circuitry. The 80186 and similar special-purpose processors are not used in a normal PC.

From the viewpoint of application-software development, it is convenient to divide the various PC processors into three classes: real-mode processors (8088, 8086 and compatibles such as the NEC V20 and V30); the intermediate 80286 processor (which we will not discuss); and full 32-bit processors (80386, 80486, Pentiums and Celeron processors).

In essence the early real-mode processors (used on the first models of PC) ran only one program at a time, provided limited memory addressing (up to 1 MB), and operated relatively slowly (being clocked at 4.77 to 10 MHz, typically).

At the other extreme, the 80486DX and Pentium class processors can address large amounts of memory (4 GB), and possess features for task switching, high speed processing and memory/hardware protection. These capabilities are used by sophisticated 32-bit operating systems such as Windows NT to implement efficient multi-tasking and to control access to system resources.

Intel released a cheaper alternative to the Pentium in 1998: the Celeron processor. This is similar to the Pentium II, but without the latter's built-in level 2 cache. Despite the fact that, by most standards, the Celeron is significantly slower, it is becoming popular in some industrial applications, particularly in embedded systems.

Pentium II processors operate at up to 450 MHz internally. This and enhancements such as 64-bit external data bus, separate caches for instructions and data, a much improved instruction handling capability and very efficient numeric processing are responsible for the superior performance of Pentium-based PCs. The Pentium III offers further improvements in performance. Initial versions are clocked at up to 500 MHz and faster versions will no doubt be available by the time this book is published. Floating-point performance has been enhanced in the Pentium III with the addition of a special instruction set (Katmai New Instructions, or KNI) and new registers. This provides up to about  $2 \times 10^9$  floating-point operations per second (2 Gflops): sufficient for the processor to take on tasks that

might otherwise have required a specialized Digital Signal Processor (DSP): real-time audio processing, for example.

Because each new processor in the sequence incorporates a superset of the instructions and features of earlier processors, they are termed 'backward compatible'. Software written for an 80286 processor, for example, will generally be able to run on 80386 and all later processors. Even the latest Pentium processors can operate in real mode, emulating the early 8086. Note, however, that the converse is not true: an 8086 will not run most of the software written for the Pentium. In spite of this backward compatibility, the timing of many instructions varies between processors. The speed of most instructions tends to be greater in the newer processors although some instructions may execute more slowly. This point should be borne in mind when writing very time-critical code, particularly if the software is intended to run on a range of different processors.

### ***Processor modes***

The 8086 processor is capable of directly addressing up to 1 MB of memory. It is designed to support the execution of only one program (or process) at any time. This process has complete control over the PC and has direct access to all addressable memory and I/O locations, even those belonging to the system BIOS or to the operating system itself. Because there are no protection mechanisms to prevent interference between processes it is difficult to implement safe multitasking (see Chapter 2) on the 8086. The 8086's mode of operation is known as real address mode (often abbreviated to just 'real mode'). All later processors support real mode as well as other modes that allow access to more than 1 MB of memory.

The protected mode available on 80286 and later processors helps to circumvent the 1 MB limitation. As well as providing access to more memory, it incorporates a number of mechanisms which help to prevent processes from conflicting with each other or with the operating system. All subsequent processors (i.e. 80386 and later) also possess a virtual 8086 (V86) mode. In this mode, the processor operates as multiple virtual 8086 machines, dividing its time between each. Programs are allocated their own virtual machine and in this way it appears to the program that it is running on its own 8086 processor. Each virtual machine may have its own DOS environment and is isolated from the rest of the system. The program running on each virtual machine believes that it has full control of the system, as on a real 8086. Interprocess memory conflicts and I/O conflicts are avoided by means of sophisticated protection mechanisms provided by the processor (as described later in this chapter). In order to

perform multitasking using the processor's protected or V86 modes the whole machine has to be managed by suitable operating system software. We will discuss this topic in Chapter 2.

Although the modes available on the more advanced processors are very efficient, their protection mechanisms can involve a substantial software overhead, especially if complex multitasking operating systems are used to mediate between processes. DA&C programs are normally relatively small and uncomplicated, and a simple real-mode environment (e.g. a DOS-based system) is often the most suitable. A protected-mode system can, however, provide the potential for a greater degree of reliability. The inherent protection mechanisms can help to prevent resource conflicts and may highlight certain types of coding error during development.

## **Registers**

Throughout this book I will make frequent references to an important feature of the processor: its registers. The basic concepts are introduced below. However, this is only a very brief overview to aid your understanding of the examples presented in subsequent chapters. You should consult a specialist text on processor architecture or assembly language programming – e.g. Hummel (1992), Swan (1989) or Holzner and Norton (1991) – for a more detailed discussion of this subject.

Each processor in the 80x86 family possesses several 16-bit registers which are used to hold data and memory addresses. In many operations, you have a choice of which register to use. However, most registers are designed specifically for certain operations. Some registers, such as CS, DS and SS, address particular memory segments (blocks of up to 64 KB addressable in real mode). Others (e.g. IP, SP, BX) can be used to address individual bytes or words as offsets from the beginning of an associated segment. Yet other registers are used to hold numeric data. Some of the 16-bit registers (i.e. AX, BX, CX and DX) allow their high and low order bytes to be addressed separately. For example, the high order byte of AX is referenced within an assembly language program as AH, and the low order byte as AL. The AX register is used exclusively in certain operations such as reading from or writing to an I/O port. The Flags register contains various bits which indicate the results of arithmetic operations or which control how particular features of the processor operate.

The 80386 and subsequent processors are equipped with 32-bit registers. Each of the 16-bit registers mentioned above is actually implemented as the low order 16 bits of the corresponding 32-bit register. Just as it is possible to separately reference the high and low

order bytes of certain 16-bit registers, one can reference either the full 32-bit register (by preceding the normal register designation with an 'E', e.g. EAX) or only the low order 16 bits (e.g. AX). For the sake of simplicity and compatibility with the 80286 and earlier processors, only the 16-bit register set is used in the examples presented in the remainder of this book. Those readers who are unfamiliar with assembly language should consult a book such as Swan (1989) for an introduction to this subject.

The most important point to remember about the registers is that their contents completely define the state of the processor at any given time. The registers may hold a variety of information relating to the current process. This includes the address of the next instruction to be executed, intermediate results, the interrupt state and many other essential parameters. If the register contents are incorrectly modified or become corrupted it is very likely that this will result in the failure of the software. You should bear this in mind when dealing with any form of context switch such as an interrupt or task switch, and take appropriate steps to preserve the state of the registers. Refer to Chapter 2 for more on task switches and concurrent processing, or to Chapter 5 for a detailed discussion of interrupts.

## ***Numeric processing***

Predecessors of the 80486DX have a limited mathematical processing capability. While they are able to perform a variety of integer arithmetic, data transfer, and logical operations, they were not designed to undertake floating-point calculations. Many compilers and development tools incorporate floating-point software libraries. These contain long and complex routines to facilitate floating-point computation. Unfortunately, floating-point software can be slow. When many calculations have to be performed, the burden placed on the processor may unacceptably degrade the system's throughput. This problem can be particularly acute in high speed DA&C applications.

The alternative technique is to use special hardware for numeric processing. A numeric processing unit is dedicated to performing floating-point calculations and operates more or less in parallel with the main processor. It supports a number of floating-point data types and provides facilities for performing trigonometric and transcendental functions. The 80486DX and Pentium class processors have built-in numeric processing units, but earlier processors required a matching numeric coprocessor IC. This hardware solution makes very substantial increases in throughput possible, although the degree of benefit gained does, of course, depend upon the

nature of the software. Numeric processors are not essential in all DA&C applications. Many programs execute only integer instructions during the period of data acquisition. However, a numeric processor can be invaluable in applications which have to execute mathematical control algorithms (e.g. PID control) or which must undertake any form of real-time signal processing.

The presence or otherwise of a numeric processor is normally transparent to programmers working with C, Pascal or other high level languages. The programmer will normally only have to select a compiler ‘switch’ in order to generate code for a numeric processor or to emulate one in software. He or she need not be concerned with *how* floating-point calculations are actually performed. This is not true, however, for assembly language programmers. These readers are advised to consult more specialized texts on the subject such as Hummel (1992) or Holzner and Norton (1991).

### 1.3 Memory

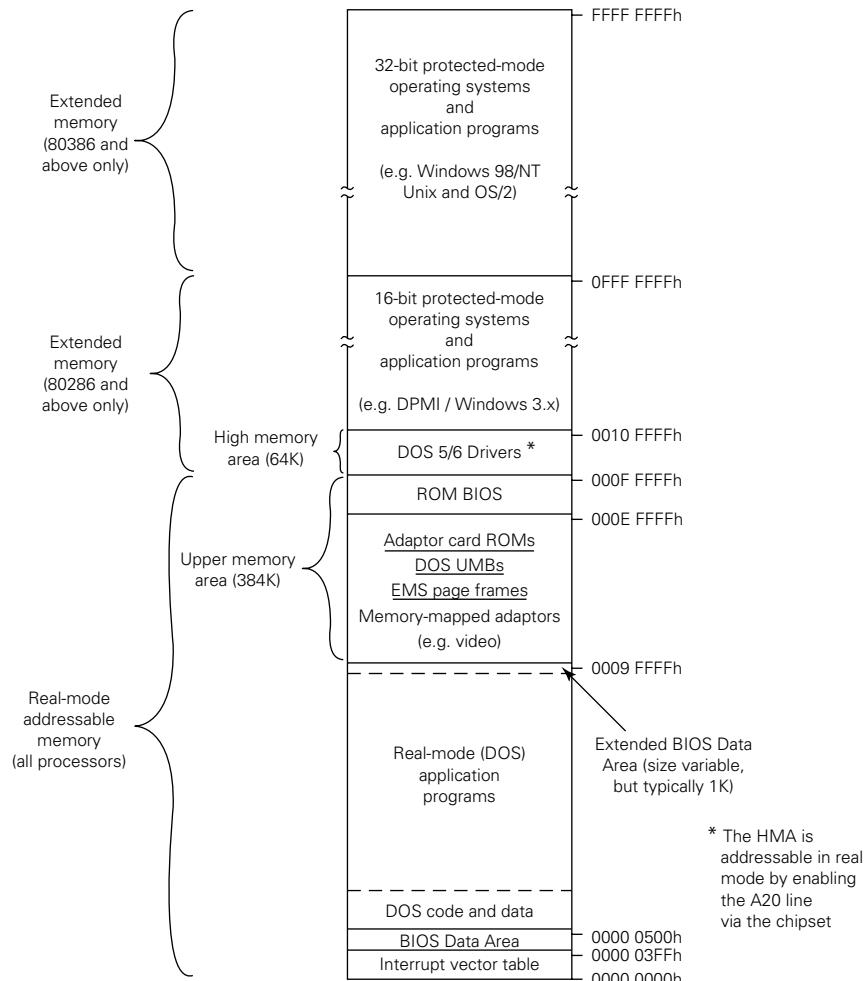

As we have already seen, modern PCs can address up to 4 GB of memory, although most contain very much less. Figure 1.1 illustrates the PC’s memory space and shows some important regions within the address map. The addressable range is processor (and mode) dependent.

When operating in real mode, the 80x86 and Pentium processors employ a segmented memory addressing scheme. Each memory address is specified in the software by the contents of a segment register and an offset register. In real mode both of these registers are 16 bits wide and thus a memory segment is defined as a memory block up to 65 536 bytes in length. A segment begins on any paragraph (16-byte) boundary. The contents of the segment and offset registers are combined to form a physical address by multiplying the contents of the segment register by 16 and then adding the result to the value held in the offset register. This generates a 20-bit address which can be used to access any location in the 1 MB memory area. The segmented memory scheme can complicate programming somewhat, although it does have a number of practical advantages. It provides a means of dividing memory up into convenient segments, the beginning of each segment being addressed by the contents of the segment register. Successive bytes within a segment can then be easily referenced by incrementing or decrementing a single 16-bit offset register.

The addressing method used in the 80286’s protected mode is similar. However, the value held in the segment register no

**Figure 1.1** The PC's memory map

longer corresponds to a physical segment base address. Instead, it is used as a selector. This is a pointer to an entry in a table maintained by the operating system. Each entry in this table is known as a descriptor and specifies the physical address of the segment of memory which is to be accessed. The selector and descriptor also contain other data relating to the memory segment. This includes the information necessary for operating systems to implement interprocess protection and memory management. For example, the descriptor specifies whether the segment referenced is a code or data segment and thus provides a mechanism for the

operating system to trap actions such as inadvertent writes to a code segment. It also specifies the size of the segment so that accesses to memory beyond the segment limit can be detected. The 80286 can access up to 16 MB of memory.

A similar system is used on the 80386 and later processors when they are running in protected mode. However, these processors can use a 32-bit flat addressing scheme in which the selector is kept fixed by the operating system and the programmer addresses memory by means of only a 32-bit offset. This provides access to up to 4 GB of memory. The 80386 and later processors also provide an additional memory management facility, known as *paging*. When paging is disabled, the address determined from the descriptor represents the physical memory address (as in the 80286 processor). When paging is enabled, the linear (or virtual) address read from the descriptor table has to undergo another translation step in order to arrive at the physical address. The page translation mechanism makes possible the V86 mode and is also essential for a number of other advanced operations on the 80386 and later processors. Unlike the segmentation scheme, page translation is generally transparent to the applications programmer. It is normally managed invisibly by the operating system. However, the paging mechanism does have certain implications for real-time DA&C systems. It allows an operating system, such as Windows NT, Windows 95/98 (or Windows 3.1 operating in enhanced mode), to temporarily swap blocks of memory out to a hard disk. Although this can be a great advantage in non-time-critical systems it may be unacceptable in real-time DA&C applications as it has the potential to introduce variations in the time taken for the DA&C program to respond to external events.

The protected-mode segmentation scheme, the page translation mechanism and V86 modes are quite involved topics and full descriptions of them are beyond the scope of this book. You should consult a text on the subject of operating system architecture or on the processor itself (e.g. Hummel, 1992) for further information.

### ***Accessing memory above 1 MB from real mode***

Many DA&C applications are relatively straightforward and may not need the complex multitasking and protection capabilities offered by the processor's protected and V86 modes. Often, however, they do require large quantities of memory in which to store acquired data, and this is not directly available in real mode. If you prefer the simplicity, speed and degree of control offered by a real-mode DOS-based system (perhaps one of the specialized real-time versions

of DOS), there are several ways in which to gain access to memory above the 1 MB limit.

First, you could make use of two BIOS services provided on the IBM AT and compatible machines. These services allow data to be moved between real-mode-addressable memory (i.e. memory below the 1 MB boundary) and extended memory. This technique is rather slow and requires a degree of buffering in real-mode-addressable memory. It also relies upon the cooperation of all other processes running on the machine in order that they do not overwrite another's data.

The second method of accessing extended memory is to employ an extended memory driver conforming to the Extended Memory Specification (XMS). Such a driver, HIMEM.SYS, is used by Microsoft Windows 3.1 for managing extended memory. It provides a comprehensive set of services which can be used to access memory above the 1 MB boundary as well as the so-called Upper Memory Blocks (UMBs) in the 640 KB to 1 MB area.

The third method is simply to make use of a RAM disk (also known as a Virtual disk) device driver. This sets aside an area of memory (usually extended memory) to emulate a disk drive. The RAM disk operates in the same fashion as a normal hard or floppy disk. Although it is many times faster than a typical hard disk drive, data still has to be transferred via the DOS file and device driver system and so this method is generally slower than direct memory storage.

The final approach is to employ an expanded memory system. This technique is largely obsolete on the PC, but it is instructive to consider it briefly because some specialized data-acquisition hardware makes use of a similar system for transferring data to and from the PC's memory. Expanded memory has been used in embedded systems for some time, and a number of 8086-compatible processors that have been developed especially for embedded applications include on-chip expanded memory support.

Expanded memory is essentially bank switched memory which can be selectively paged in and out of a memory window (known as a page frame) residing below the 1 MB real-mode-address limit. Data may be read from, or written to, expanded memory through this window as though one were accessing the PC's memory. The DA&C program can select new pages at any time by calling a group of system services that are provided by an expanded memory device driver. The services generally conform to a standard known as the Expanded Memory Specification (EMS). Versions 3.2 and 4.0 of this standard are the most widely used. One of the more effective EMS implementations utilizes the paging facilities provided by the 80386

and later processors, allowing some or all of the PC's extended memory (i.e. that above 1 MB) to be treated as expanded memory.

Although the bank switching and paging mechanisms used on the PC are fast and ideally suited to DA&C, they have to be managed by some form of device driver. As with all drivers and programs written by third parties, you should be sure that they do not compromise the deterministic qualities necessary in real-time systems (see Chapter 2).

EMS, XMS and the extended memory BIOS services are covered in many books on the IBM PC such as Duncan (1989), Duncan *et al.* (1990) or Dettmann and Johnson (1992).

## 1.4 Input/output ports

In addition to its memory, the PC has another entirely separate address space. This is dedicated to transferring data to or from peripheral devices and is known as Input/Output space (or simply I/O space). Just as the PC's memory space is divided into separate byte locations, the I/O space consists of many byte-sized I/O ports. Each port is addressable in much the same way as memory, although an additional control line is used within the PC to distinguish between memory and I/O port accesses. I/O space consists of a contiguous series of I/O addresses. Unlike memory space, the I/O address space is not segmented and cannot be paged. In fact, the processor references I/O ports by means of a 16-bit address and this means that no more than 65 536 I/O ports can be supported by the PC. In practice, this is further limited by the I/O address decoding scheme used on the PC and its adaptor cards.

The I/O ports provide a means of sending data to, and receiving data from, devices such as the video adaptor, the disk subsystem, or analogue-to-digital converters (ADCs) on plug-in data-acquisition cards. Software can use the assembly language `IN` or `OUT` instructions, or their high level language counterparts, to communicate with hardware devices via the I/O ports. These are discussed in more detail in Chapter 6, but for the moment we will consider a simple example. Suppose that a plug-in 8-bit ADC card possesses control and data registers that are each mapped to one of the PC's I/O ports. The software starts the analogue-to-digital conversion process by writing a bit pattern to the I/O port that maps to the ADC card's control register. When the ADC has finished the conversion it might set a bit (known as the End of Conversion, or EOC, bit) in another register to indicate that digitized data is now available. In this way, the software is able to detect the EOC bit by reading the corresponding I/O port. Knowing that the conversion had been

completed, the software would then read the digitized data from a data register mapped to a third I/O port.

### ***I/O port allocation***

Hardware devices map their registers to specific I/O ports simply by decoding the PC's address bus and control lines. In this way, a specific combination of address and control lines is needed to cause data to be transferred from the register to the PC's data bus or vice versa. Some I/O ports can only be read or written, while others are capable of bidirectional data transfer. Whether ports are read-only (R/O), write-only (W/O) or read-write (R/W) is determined by how the hardware decodes the address and control lines. The processor itself makes no distinction between ports in this regard. You can still perform an `IN` instruction for a write-only port although the results of such an action will generally be indeterminate.

The PC and adaptor-card hardware do not fully decode the address lines. In fact, in the IBM PC, XT, AT and compatible machines, including the PS/2 line, only the lower 10 lines are used. This means that it is possible to address only 1024 separate I/O ports. Even certain addresses within *this* range are not fully decoded. Thus some devices which should require only two or three registers may actually occupy a much larger block of I/O addresses: the same registers being mirrored at a series of other addresses within the block. A much more satisfactory approach is taken on EISA systems. These decode the address lines more fully, providing additional I/O ranges that are dedicated specifically to the system motherboard or to adaptors residing in each of the EISA expansion bus slots. On each class of PC, certain I/O addresses are reserved for particular devices. Table A.3 in Appendix A provides an overview of I/O port usage and may be used as an aid to selecting ports for use by data-acquisition adaptor cards.

### ***I/O protection mechanisms***

The PC's I/O ports are always accessible in real mode. In protected and V86 modes, however, the processor can be programmed to restrict access to I/O addresses. This facility is used in multitasking operating systems such as OS/2 and Windows NT to control which processes (i.e. running programs) will be allowed to read and write the I/O ports. In this way it is possible for the operating system to mediate between two or more processes that need to access the same I/O device. The operating system runs at a high privilege level, which means that it is allowed to execute certain privileged instructions.

These include instructions that access the I/O ports and those which change the state of the processor's Interrupt Flag (see Chapter 5).

In protected and V86 modes, when a program operating at a low privilege level attempts to execute one of the privileged I/O instructions, the processor generates a General Protection exception. This causes control to be immediately passed to the operating system, which can then oversee the I/O port access. The details of this process are quite involved and cannot be covered here. You should consult a text such as Hummel (1992) for more on this topic.

One of the consequences of the I/O protection mechanism is that an application program running in protected or V86 mode (e.g. under OS/2 or Windows) will generally be prevented from *directly* accessing the I/O ports. I/O port accesses require at least some operating system intervention and this reduces the maximum possible throughput of the system. It also contributes to a degree of uncertainty in the speed at which the system will respond. This can be a particularly important consideration when designing a real-time DA&C program.

## 1.5 Buses and adaptor card slots

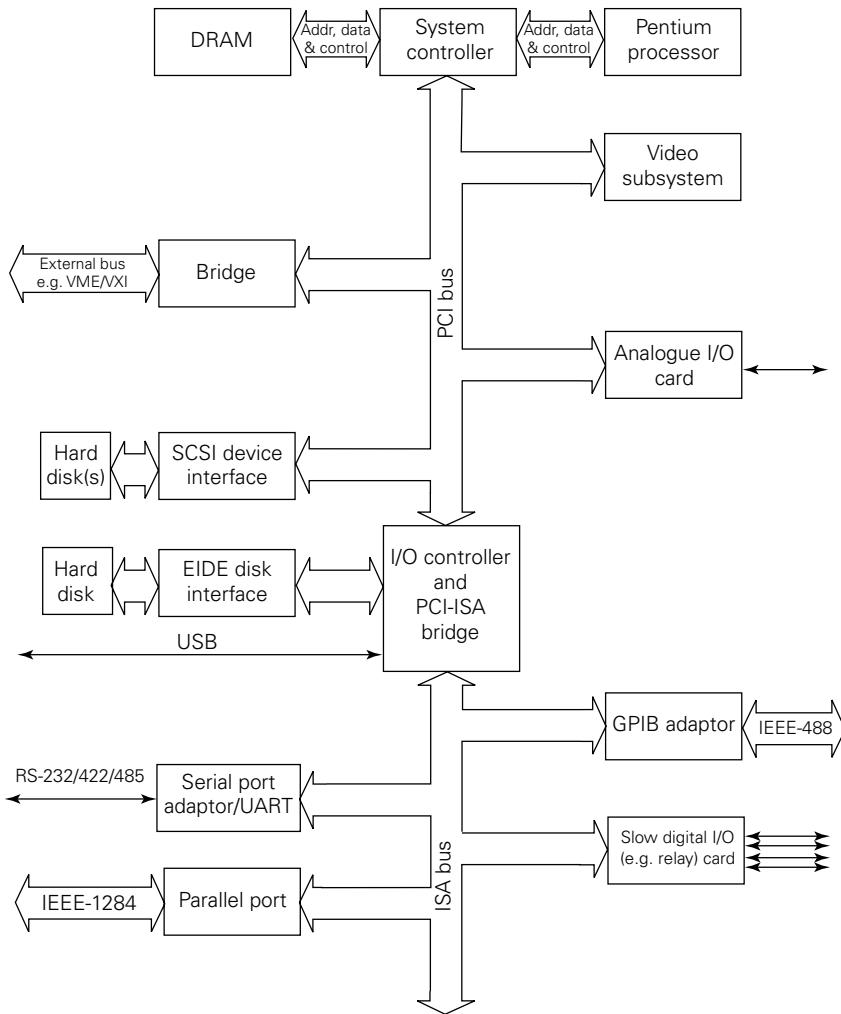

Passing data to and from a DA&C card via an I/O port actually involves transferring the data over one or more system buses. Figure 1.2 illustrates a variety of buses that can be interfaced to the PC. A typical PC may not contain all of the buses shown, although the PCI and ISA buses are present in most systems. Other types of bus (many of them proprietary systems) can be interfaced by means of special adaptors or bridges to the PC. The IEEE-488 bus and the VXI bus, for example, are used in specialized instrumentation applications. Of primary concern here though are the PC's native buses – i.e. the ones that are an integral part of the PC's own architecture.

The type of bus used within the PC not only has a bearing on the type of interface card that can be connected, it may also have a profound effect on the throughput of the system as a whole. Although normal bus operation cannot be modified under software control and is largely transparent to the programmer, it is of great importance in interfacing and so a brief overview is provided below.

### ***The ISA bus***

Until the mid-to-late 1990s, the Industry Standard Architecture (ISA) bus dominated the PC market and was the interface used for most

**Figure 1.2** Example bus connections and interfaces on a PC used for data acquisition. Note that not all devices and buses shown will be present on every system, and some systems will incorporate additional devices

plug-in DA&C cards. It is derived from the earlier, and slower, 8-bit bus used in the IBM PC and XT (known as the PC bus or XT bus). Note that the 16-bit ISA bus (also known as the AT bus because it was introduced in the IBM AT computer) is in some literature also misleadingly referred to as the PC bus.

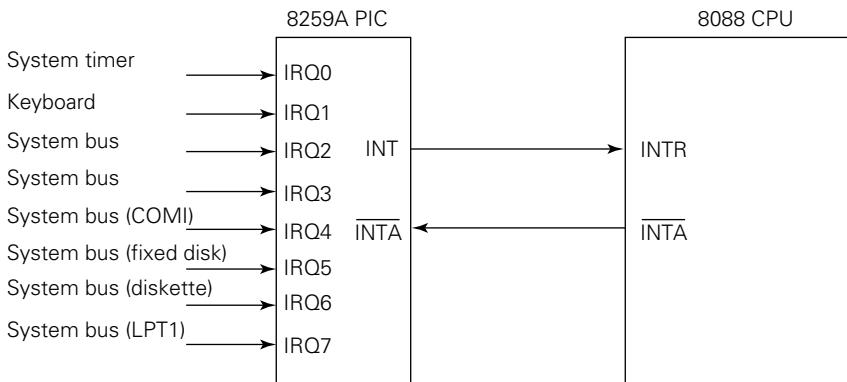

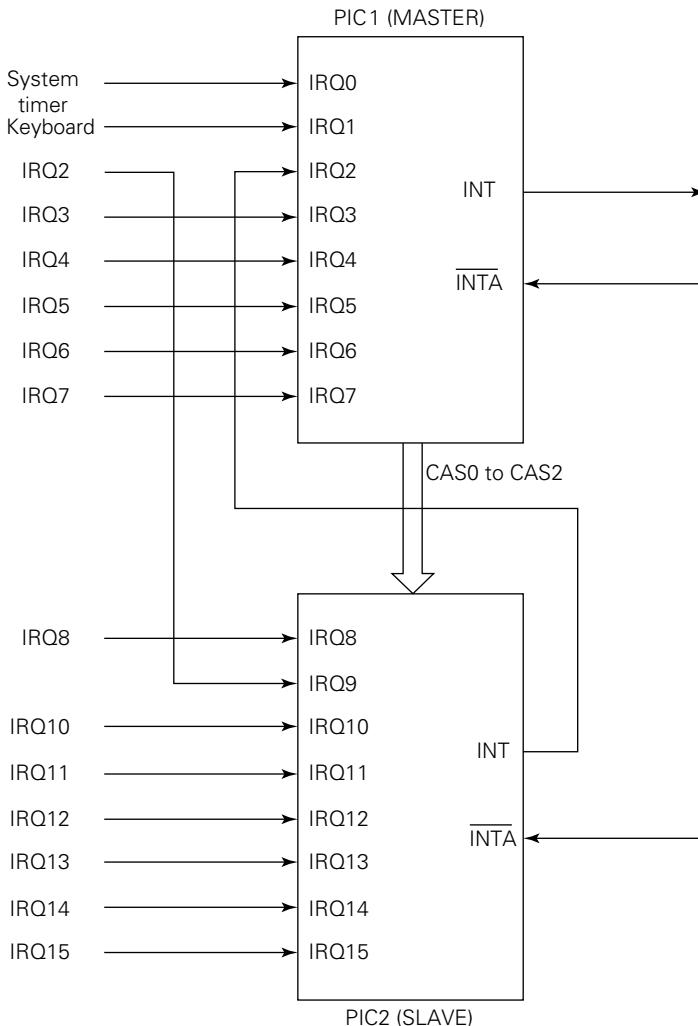

The ISA bus incorporates a number of enhancements over the XT bus, such as a 16-bit data path, a 16 MB addressing capability,

an increased number of interrupt request lines (see Chapter 5) and additional DMA channels (see Chapter 6). The extra data, address and control lines necessary to interface to ISA type adaptor cards were added in a second connector placed in line with the original XT type connector. Although a few of the connector pins on the XT connector were redesignated, the ISA bus connector provides full backward compatibility with the older XT cards. Most ISA machines are equipped with several 16-bit ISA slots and one or two 8-bit XT type slots. With a few exceptions (noted below), 8-bit cards can also be inserted in the XT portion of 16-bit ISA slots.

The ISA bus clock speed is not tied to the processor clock as it was in the XT bus. Widely differing bus and processor clock speeds are used on ISA machines and synchronization between the two is maintained by means of special support circuits. The IBM AT's bus was clocked at 8 MHz. Many newer systems allow the bus clock speed (and indeed the processor and DMA clock speeds) to be reprogrammed using a BIOS configuration utility. The chosen speed is recorded in the system's CMOS RAM. A high frequency (e.g. 10 or 11 MHz) may be selected provided that all adaptor cards will operate reliably at this speed. Most modern ISA adaptor cards are capable of running at 10 or 11 MHz, but some older DA&C cards are not.

Bear in mind that even the standard 8 MHz ISA clock speed may be incompatible with some older ADC or counter/timer cards that were intended specifically for IBM PC or XT systems. These cards are designed to provide their on-board components with clock signals derived from the PC's 4.77 MHz bus clock and are, therefore, unsuitable for use with the higher clock frequencies present on the ISA bus. Indeed they are also incompatible with the 8 or 10 MHz XT buses employed in some XT clones. Generally speaking, this is no longer a problem with modern DA&C cards as these tend to be driven from their own dedicated oscillator, rather than from the system bus clock. You should, however, be wary of this potential difficulty when using some pre-1990 DA&C cards.

Today, new desktop PCs now rarely possess more than one or two ISA card connectors, the remaining expansion capability being provided by the PCI bus, which we will discuss shortly. However, the ISA bus is far from obsolete in the industrial data-acquisition market. Many rack-mounted industrial PCs still employ this standard and there are numerous ISA bus DA&C cards still on the market. Before discussing the PCI bus, it is appropriate to briefly mention two other buses: the MCA bus and the EISA bus. Although these are both technically superior to the ISA bus in many respects, they have not enjoyed such widespread use.

## ***The MCA bus***

The MCA (Micro-Channel Architecture) bus was developed by IBM for its range of PS/2 computers. MCA was more rigidly specified than the ISA bus in terms of its physical, electrical and timing characteristics, and incorporated a software-based card configuration facility. The latter feature, called Programmable Option Select (POS), circumvented the need to use DIP switches or jumpers for selecting options such as base address or interrupt levels. As all configuration is performed via manufacturer-supplied software, the details of POS operation are rarely of interest to the DA&C programmer. Readers are referred to the text by Eggebrecht (1990) for more information on POS.

## ***The EISA bus***

The main disadvantage of the MCA bus was its incompatibility with the earlier XT and ISA buses. A consortium of PC manufacturers attempted to circumvent this problem by developing an enhanced version of the ISA bus, known as the Extended Industry Standard Architecture, or EISA, bus. This provided a number of benefits similar to those of MCA while maintaining full backward compatibility with ISA cards. EISA buses, which are used in some 80386 and later systems, incorporate a 32-bit data bus and have an enhanced slot-specific I/O addressing capability. Like MCA, EISA cards are configured by means of software utilities and data files supplied by the manufacturer.

## ***The PCI local bus***

Local buses began to emerge as potential competitors to conventional expansion buses such as ISA in the mid-1990s. Whereas conventional buses have to employ special circuitry to manage bus traffic and to synchronize high speed processors with slower bus operations, local buses are more tightly coupled to the processor.

Currently, the dominant local bus standard is Intel's PCI (Peripheral Component Interconnect) bus. Although the latest PCI standard (version 2.2) allows for 64-bit transfers at 66 MHz, standard PC-based PCI implementations currently provide a 32-bit data path. Because PCI operates at the processor's clock frequency (i.e. the frequency of the clock signal supplied to the processor, rather than the processor's internal clock frequency), it is capable of very high rates of throughput. The PCI bus also supports bus mastering in which PCI devices can take control of the bus in order to transfer

data. This is much like the DMA technique used on the ISA bus (see Chapter 6). The principal difference is that each device supplies its own bus-mastering hardware rather than relying on the PC's DMA controller. Additional performance enhancements can often be realized by this means because bus transfers can be carried out in parallel with certain processor operations. PCI devices can, for example, exchange data along the bus at the same time that the processor is accessing system memory.

### Transfer rates

Table 1.2 summarizes the main characteristics of the buses discussed so far. A 32-bit PCI bus clocked at 33 MHz can, in theory, provide a data transfer rate of 132 MB/s. This represents a huge increase over conventional buses. An 8 MHz ISA bus was, for example, capable of transferring data at up to 16 MB/s. The MCA and EISA buses fare

**Table 1.2** PC expansion buses

| Bus      | Address width (bits) | Data width (bits) | Standard clock rate (MHz)  | Max. throughout at standard clock (MB/s) |  | Notes                                                                                                                        |

|----------|----------------------|-------------------|----------------------------|------------------------------------------|--|------------------------------------------------------------------------------------------------------------------------------|

|          |                      |                   |                            |                                          |  |                                                                                                                              |

| PC (XT)  | 20                   | 8                 | 8                          | 8                                        |  | Six IRQ lines. Three DMA channels.                                                                                           |

| ISA (AT) | 24                   | 16                | 8                          | 16                                       |  | Twelve IRQ lines. Seven DMA channels.                                                                                        |

| MCA      | 24                   | 32                | Variable (typically 10–20) | 20–160                                   |  | Maximum transfer rates achieved in data streaming mode. DMA implemented via bus mastering with up to 16 arbitrating devices. |

| EISA     | 32                   | 32                | 8                          | 33                                       |  | Quoted throughput achieved in data streaming mode.                                                                           |

| PCI      | 32                   | 32 or 64          | 33 or 66                   | 132 <sup>(1)</sup>                       |  | Intelligent bus mastering with support for DMA. Quoted transfer rate is achievable in burst mode only. <sup>(1)</sup>        |

<sup>(1)</sup>For a 32-bit implementation running at 32 MHz. Maximum throughput increases proportionately for faster or wider versions of PCI.

somewhat better. MCA supports 32-bit data transfers at rates up to 20 MB/s. Higher rates (typically 40 to 80 MB/s) are achievable with a special data streaming mode. EISA systems provide bus transfer rates of up to 32 MB/s. Bear in mind that these maximum transfer rates cannot always be realized in practice. Throughput is often limited by factors other than bus bandwidth.

The AT's DMA controller can provide a throughput of up to approximately 1 MB/s (or 2 MB/s, depending upon whether an 8-bit or 16-bit DMA channel is used). A greater throughput can sometimes be achieved using programmed I/O: typically up to 3 MB/s on a fast machine. In practice, however, delays inherent in other components (e.g. the ADC conversion time, multiplexer settling times, signal conditioning bandwidth – see Chapter 3) tend to be the principal throughput-limiting factors. For this reason, the maximum bus transfer rate cannot usually be realized and in many applications bus speed has only a minimal effect on the overall system throughput. DMA, programmed I/O and throughput rates are discussed in more detail in Chapter 6.

### **PCMCIA interface**

Like local buses, PCMCIA cards (sometimes known as just PC cards) are a fairly recent innovation in PC interfacing. The PCMCIA (Personal Computer Memory Card International Association) standard defines a hardware and software interface for attaching miniature adaptor cards to the PC. It was originally intended as a standard bus for interfacing removable memory cards to portable computers, although it has now been adopted for other peripheral devices such as serial ports, modems, network interfaces and hard disks. DA&C component manufacturers now also produce data acquisition cards in PCMCIA format. At the time of writing, these devices are largely limited to simple mainstream DA&C functions (8 channel multiplexed ADCs, dual DAC cards, counter/timers, simple digital I/O facilities etc.) and provide reasonably high, although not exceptional, throughput. Few PCMCIA cards offer more advanced features such as very high speed ADCs, FIFO buffers or an on-board processing capability. A number of industrial communications PCMCIA cards (RS-232/422/485 or IEEE-488) are also available.

As mentioned above, PCMCIA cards are small: about 2 inches (50 mm) across. They are produced in various thicknesses: Type I cards are 3.3 mm thick; Type II cards are 5.0 mm thick; and Type III are 10.5 mm thick. The extra thickness of Type III cards is required principally to accommodate miniature hard disks and radio frequency communications products. DA&C cards are normally of

Type II. Most notebook PCs are able to accommodate at least two of these Type II cards, permitting moderately complex DA&C systems to be designed around a portable computer.

PCMCIA cards offer several benefits. They are software configurable, so installation (I/O address selection, interrupt selection etc.) can generally be automated. Apart from the fact that they follow a fairly rigid specification in terms of power usage, signal timing, and physical size, they also offer specific advantages for users of DA&C systems. Their 16-bit data bus provides reasonably high rates of throughput at moderate cost. Because of their size, PCMCIA cards are extremely portable and, when used in conjunction with notebook PCs, open up the possibility of data acquisition in awkward environments (e.g. in moving vehicles). They can be unplugged from the PC or from other DA&C system components, facilitating relocation from one DA&C site to another. PCMCIA cards also have a *hot insertion* capability. This permits cards to be removed from the computer and swapped for other cards without having to switch off the PC.

Due to the small size of the cards, subminiature connectors are employed. This means that PCMCIA DA&C cards normally have to be used in conjunction with extension cables and screw terminal panels which will accept the field connections from transducers or signal-conditioning units. In certain applications, these devices may also include sensor excitation references or isothermal connections for thermocouple cold-junction compensation (see Chapter 3). As the PCMCIA circuit board is fully enclosed it is difficult to gain access to trimpots or to test points for calibration or fault diagnosis. However, PCMCIA DA&C cards are normally factory calibrated where necessary and any subsequent recalibration can usually be performed by adjusting scaling factors and offsets in software (see Chapter 9). Most PCMCIA card manufacturers supply software drivers and, in many cases, configuration, calibration and diagnostics programs as well.

### ***Industrial and instrumentation buses***

As mentioned previously, the standard desktop PC format is not robust enough for use in harsh industrial environments. Industrial DA&C systems often employ ruggedized versions of the PC in specially designed rack-mounted enclosures. However, the physical properties of the enclosure are not the only consideration. The standard PC architecture may not have the interfacing support needed to directly manage some complex industrial sensing or control systems. It does, nevertheless, have many other advantages (noted in the

introduction to this chapter) which makes it highly desirable in this type of application.

A number of manufacturers have attempted to bridge the gap between the desktop PC and more robust industrial systems by producing versions of the XT, ISA or PCI buses in a passive backplane format that is suitable for use in industrial 19 inch rack-mounted enclosures. These backplanes usually have a large number of expansion slots allowing various types of processor cards, I/O interface boards, and other adaptor cards to be attached.

Special adaptors known as *bridges* are available, which permit devices on the PC bus to interface to a range of more specialized industrial buses. These buses tend to be modular and rigidly specified, allowing them to be easily interfaced to industry-standard I/O devices. There are three main types of bus: STE/STD, Multibus and VME. The STE bus is an 8-bit bus capable of addressing 1 MB of memory and 4 KB of I/O space. STE was developed from the earlier 8-bit STD bus standard. Multibus also permits access to a 1 MB memory space, but allows 16-bit data transfers. Its successor, Multibus II, provides an enhanced addressing capability and is suitable for use with 32-bit processors. The VME bus has been widely used in embedded systems for some years. It is capable of 8-, 16-, 32- or 64-bit data transfers. 32-bit VME systems can achieve data transfer rates of up to 40 MB/s; 64-bit implementations can achieve twice this. Depending upon its configuration, VME can address up to 4 GB of memory, but it has no I/O space. Instead all I/O operations are memory mapped. An important variant of the VME bus is VXI. This incorporates the 32-bit VME data bus as well as a number of extensions for synchronizing and managing instruments on the bus.

Finally there are specialized implementations of PCI. Several versions of this standard bus have been developed for use in industrial embedded systems. One of the most promising of these is CompactPCI. From a functional point of view, this is very similar to a standard PCI system, although it incorporates a number of mechanical and electrical design enhancements (including a different connector, a new circuit board format and support for hot swapping of circuit boards) which make it more suited to industrial use.

It is necessary to employ a suitable interface (or bridge) in order to connect an external bus, such as Multibus or VXI, to the PC's ISA bus. The bridge performs many functions. For example, registers or buffers belonging to devices present on the external bus must be mapped into the PC's I/O space or into its memory space. Various techniques can be used. Multibus employs DMA techniques (see Chapter 6) to transfer data between the PC and the external bus. Memory mapping may be accomplished using a type of page

mapping similar to that used by the EMS. This permits regions of the external bus's memory space to be selectively mapped into a 64 KB page frame within the PC's addressable range. Alternatively, the external memory is sometimes mapped to the top of the PC's 4 GB memory space. The latter option is only possible with 80386 or later processors and with operating system software that permits 32-bit addressing. Interrupt requests on the external bus must also be mapped onto the PC's own interrupt levels (see Chapter 5 for an explanation of interrupts). Again, a number of different schemes are used. The external bus may provide more interrupt signals than are available on the PC and, in these instances, several external bus interrupts may be mapped to the same PC interrupt level. Alternatively, the external bus may support shared interrupt lines and the different interrupt allocations must be resolved by the bridge interface (possibly in conjunction with suitable software).

In general, the interface is implemented in such a way that the PC software can regard the external bus simply as an extension of its own PCI or ISA bus. Manufacturers of VME and STE bus devices may supply driver programs for use in conjunction with DOS or Windows applications running on the PC. The presence of the external bus is thus largely transparent to the DA&C programmer, although the devices connected to it (e.g. other PC boards, instruments and I/O devices) can have a profound effect on what the software is able to do. In addition, the bus implementation and bridge circuits can sometimes introduce interrupt (and other) latencies which may have to be addressed in real-time systems.

### ***Other buses***

Many other buses and communications standards, which are commonly used in PC-based DA&C systems, have not yet been mentioned: for example, IEEE-488, the Centronics parallel port, and a variety of serial buses such as RS-232, RS-422, RS-485 and USB. We will describe most of these in subsequent chapters. In addition, there are several systems and protocols, such as HART (Highway Addressable Remote Transfer) and BitBus, used in industrial sensing and control applications, as well as a number of proprietary DA&C buses (e.g. DT-Connect and Metrabus), which are outside the scope of this book.

# 2 Software considerations

The architecture of the PC is reasonably well suited to data acquisition. Most of the problems that occur in designing DA&C systems result from limitations imposed by software. In fact, the most serious obstacles to writing effective data-acquisition software are usually generated by the PC's operating systems. In this chapter we will discuss the main requirements of data-acquisition software and will describe some of the problems posed by using operating systems intended for desktop applications in the more demanding environment of a real-time DA&C system.

## 2.1 An overview of DA&C software

In addition to code that acquires data or issues control signals, it is usual for DA&C software to incorporate a number of support modules which allow the system to be configured and maintained. Other routines may be required for sorting, analysing and displaying the acquired data. A typical DA&C program may contain the following modules and facilities:

- program configuration routines

- diagnostics modules

- system maintenance and calibration modules

- run-time modules

- device drivers

- data analysis modules.

With the exception of device drivers, these modules are executed more or less independently of each other (although it is, of course, possible for multitasking systems to execute two or more concurrently). A brief overview of the main software components of a typical DA&C system is given below. Particular systems may, of

course, differ somewhat in the detail of their implementation but most applications will require at least some of these modules.

### ***Program configuration routines***

These software routines may be used for initial configuration of elements of the system that the end user would normally never (or very infrequently) have to change. This might include facilities for selecting and setting up hardware and driver options; for specifying how data is to be routed through software ‘devices’ (such as comparators, triggers, data-scaling operators, software latches, logical operators, or graphical displays etc.); for defining start, stop and error conditions, or for selecting delays, run times and data buffer sizes.

### ***Diagnostic modules***

Once a DA&C program has been tested and debugged, any diagnostic routines which the designer may have included for testing are often removed or disabled. However, their value should not be underestimated in ‘finished’ (i.e. operational) systems. Routines such as these can be invaluable tools during installation and for subsequent system maintenance. Often, the dynamic and transient nature of input/output (I/O) signals and the complex interrelation between them can make it very difficult to reproduce a fault during static testing with a voltmeter, continuity tester or a logic probe. Well-designed diagnostic routines can be a great benefit to maintenance engineers should a fault occur somewhere in the DA&C system.

With a little care and thought it is usually quite straightforward to implement a range of simple but useful diagnostic routines. These can be made to monitor aspects of the DA&C system either during normal operation or when the system is placed in a special test mode. On the simplest level, the diagnostic routines might check for incorrect hardware or software configuration. They might also be designed to perform continuous tests during normal operation of the system. This might include checking for interruptions in communication between system components, ensuring correct timing of I/O control signals, and monitoring or validating data from individual sensors.

Diagnostic software routines have their limitations, however, and other means of fault finding must be used where appropriate. Various items of test equipment such as voltmeters, logic probes, and logic pulsers may also be needed. More sophisticated equipment is sometimes required, especially when dealing with rapid pulse trains.

Digital storage, or sampling, oscilloscopes allow high frequency waveforms to be captured and displayed. These are especially suited to monitoring digital signals on high speed parallel buses or serial communications links. Where it is necessary to see the relationship between two or more time-varying signals, logic analysers may be used. These devices possess multiple (typically 32) probes, each of which detects the logic state of some element of the digital I/O circuit under test. Logic analysers are controlled by a dedicated microcomputer and can be programmed to provide a snapshot of the logic states present at the probes on a display screen. The conditions for triggering the snapshot – i.e. a selected pattern of logic states – can be programmed by the user. The device may also be used for timing analysis, in which case it operates in a similar way to a multiple-beam oscilloscope.

In addition to these items of equipment, purpose-built test harnesses may be used in conjunction with diagnostic software. Test harnesses may consist of relatively simple devices such as a bank of switches or LEDs which are used to check the continuity of digital I/O lines. At the other extreme a dedicated computer system, running specially designed test software, may be required for diagnosing problems on complex DA&C systems. See the *Software production and testing* section later in this chapter for more on this topic.

### ***System maintenance and calibration modules***

Tasks such as calibrating sensors, adjusting comparators, and tuning control loops might need to be carried out periodically by the user. Because any errors made during calibration or control loop tuning have the potential to severely disrupt the operation of the DA&C system, it is essential for the associated software routines to be as robust and simple to use as possible.

One of the most important of these system maintenance tasks is calibration of analogue input (i.e. sensor) channels. Many sensors and signal-conditioning systems need to be recalibrated periodically in order to maintain the system within its specified operating tolerance. The simplest approach (from the program designer's perspective) is to require the user to manually calculate scaling factors and other calibration parameters and then to type these directly into a data file etc. It goes without saying that this approach is both time consuming and error prone. A more satisfactory alternative is to provide an interactive calibration facility which minimizes the scope for operator errors by sampling the sensor's input at predefined reference points, and then automatically calculating the

required calibration factors. We will resume our discussion of this subject in Chapter 9 which covers scaling and interactive calibration techniques in some detail.

### ***Run-time modules***

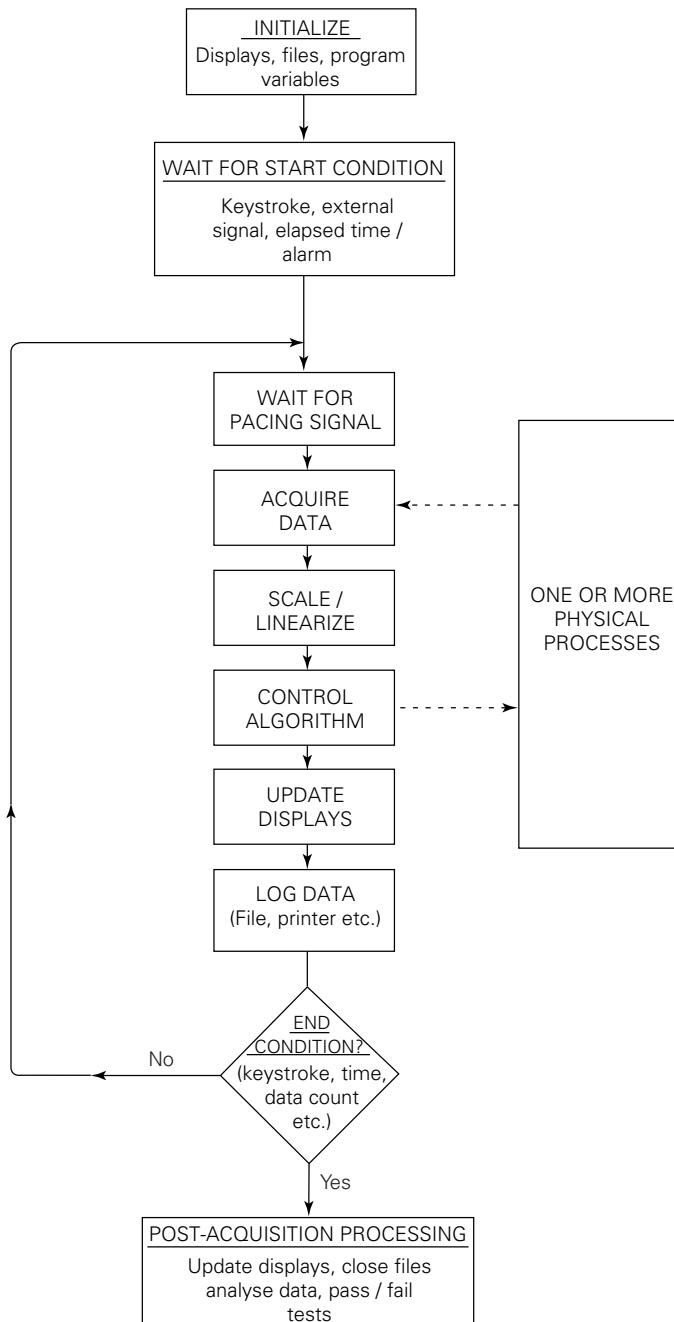

These, together with the device drivers, form the core of any DA&C system. They are responsible for performing all of the tasks required of the system when it is 'live' – e.g. reading sensor and status inputs, executing control algorithms, outputting control signals, updating real-time displays or logging data to disk.

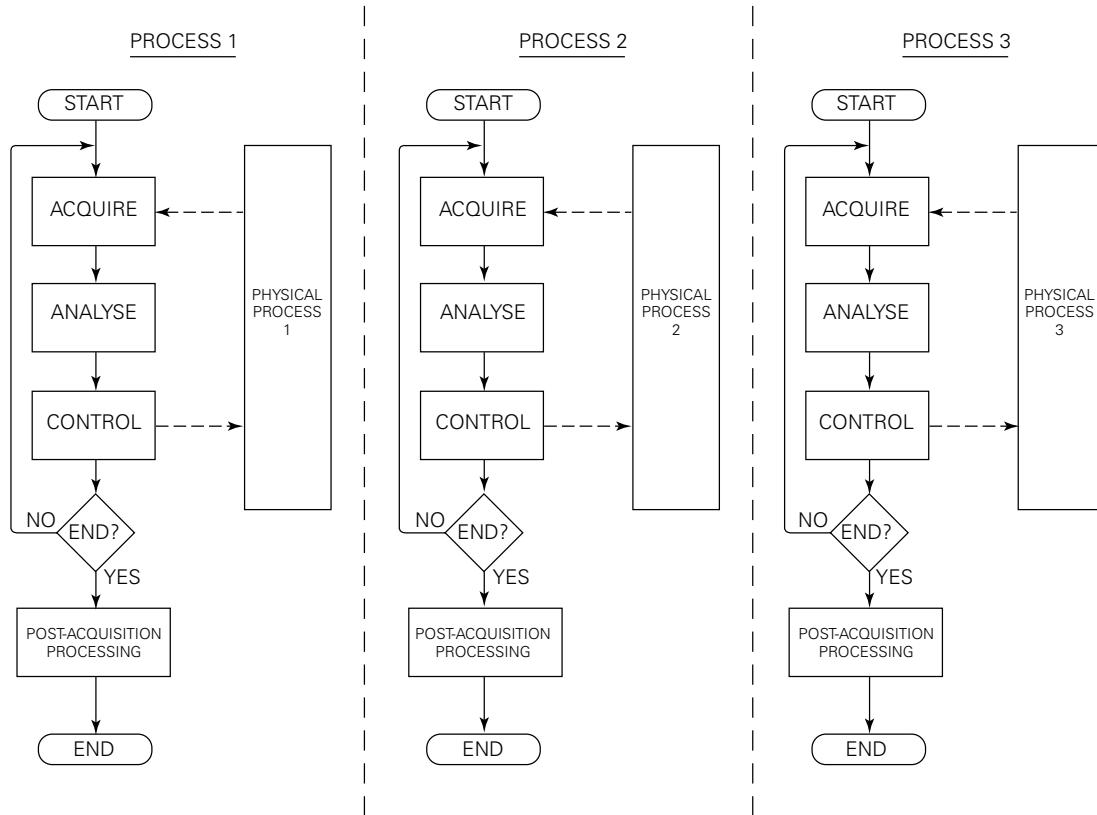

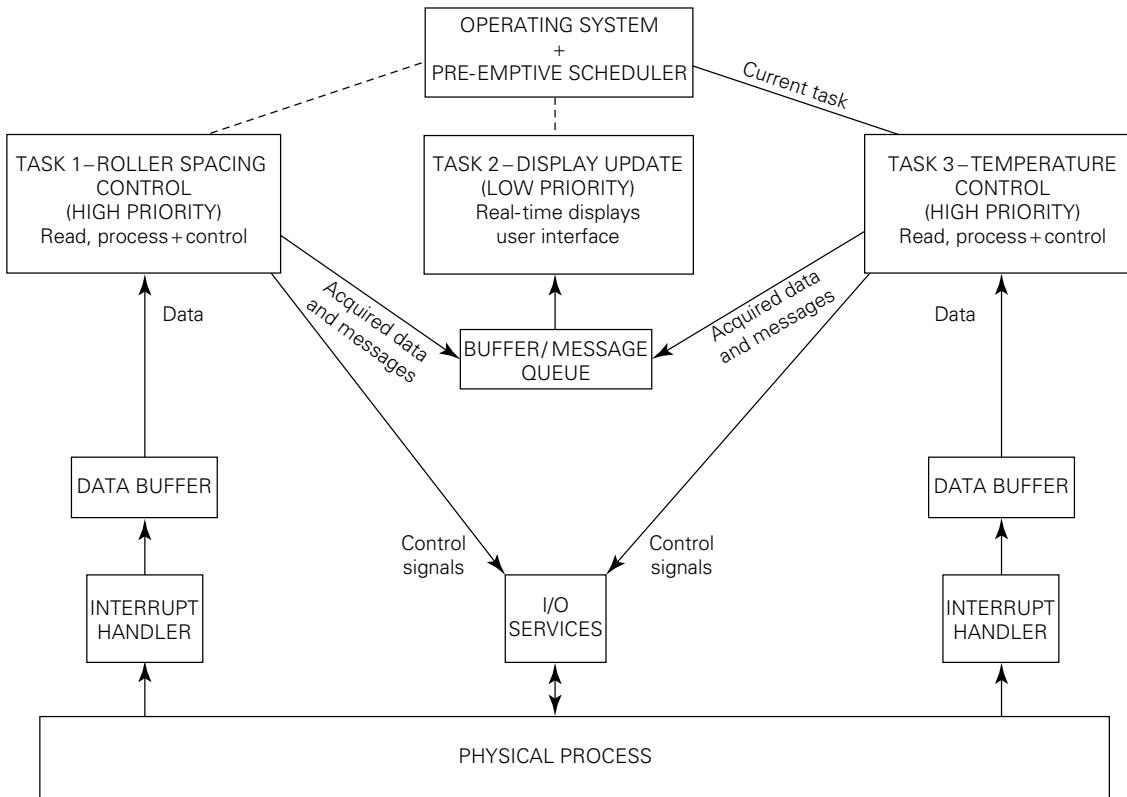

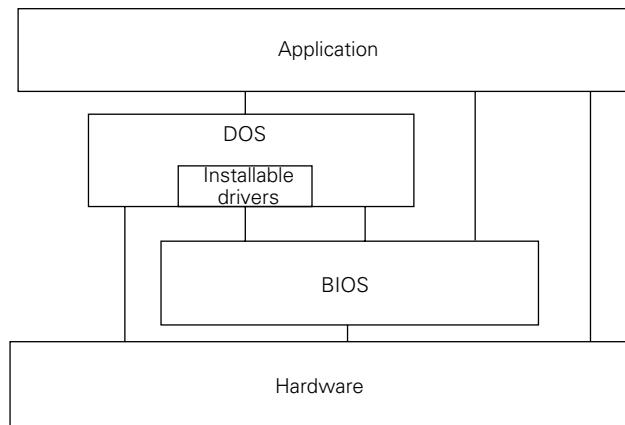

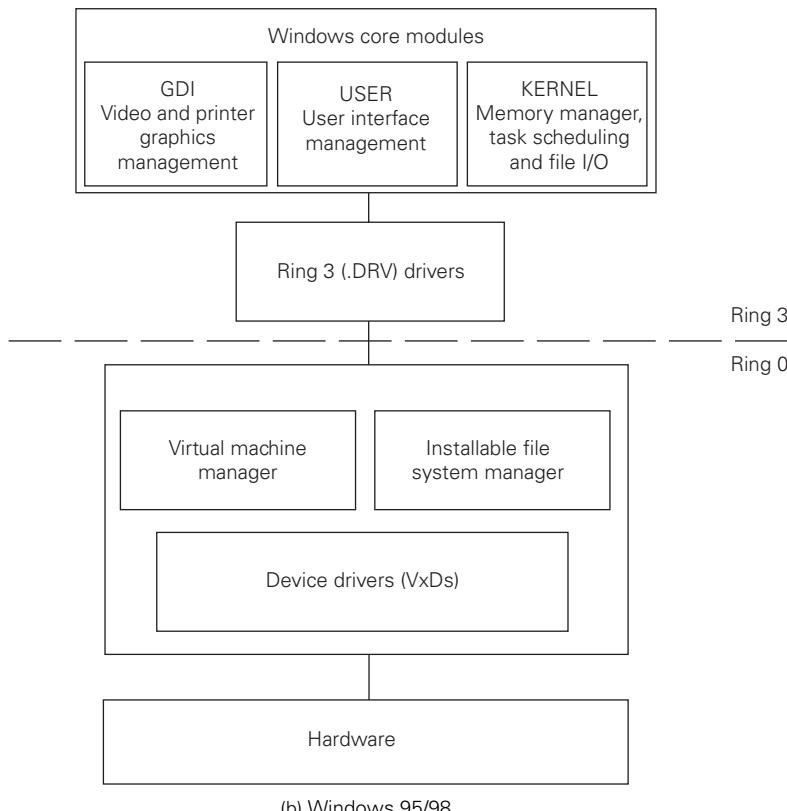

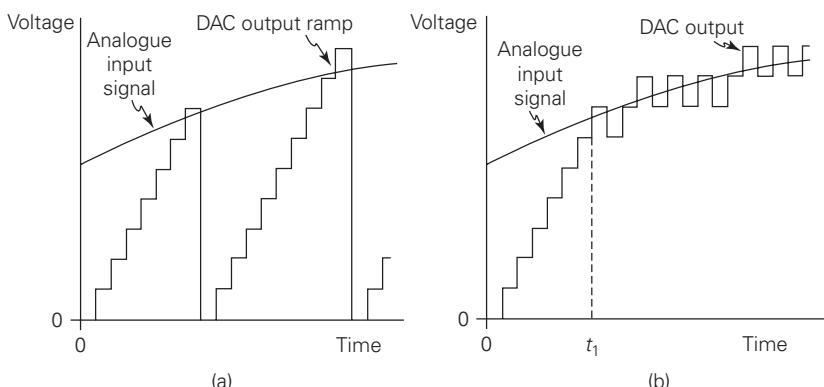

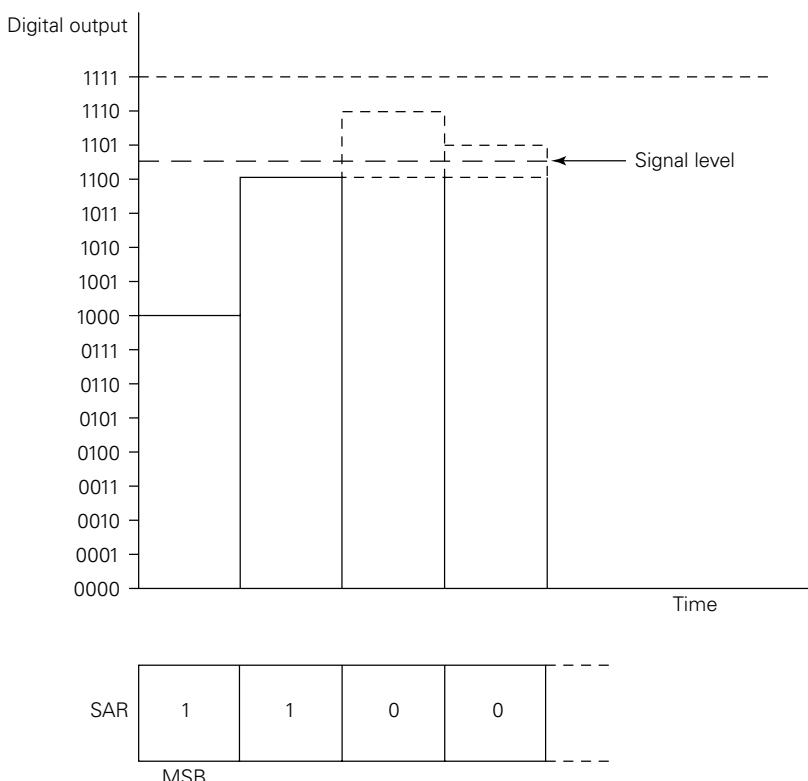

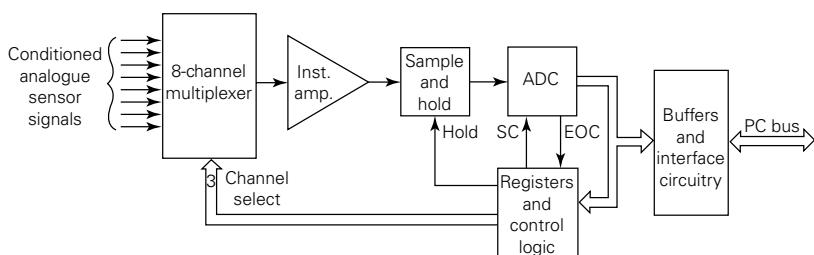

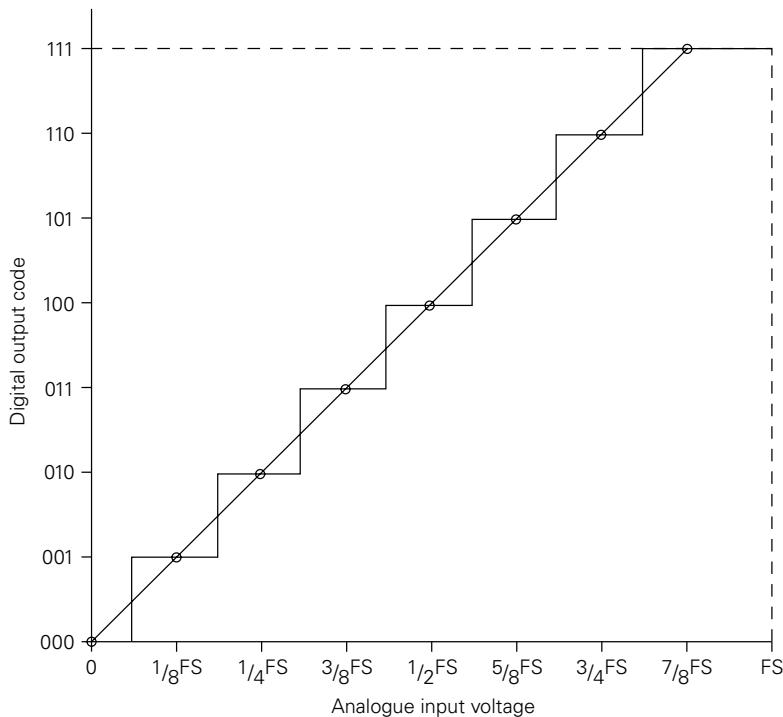

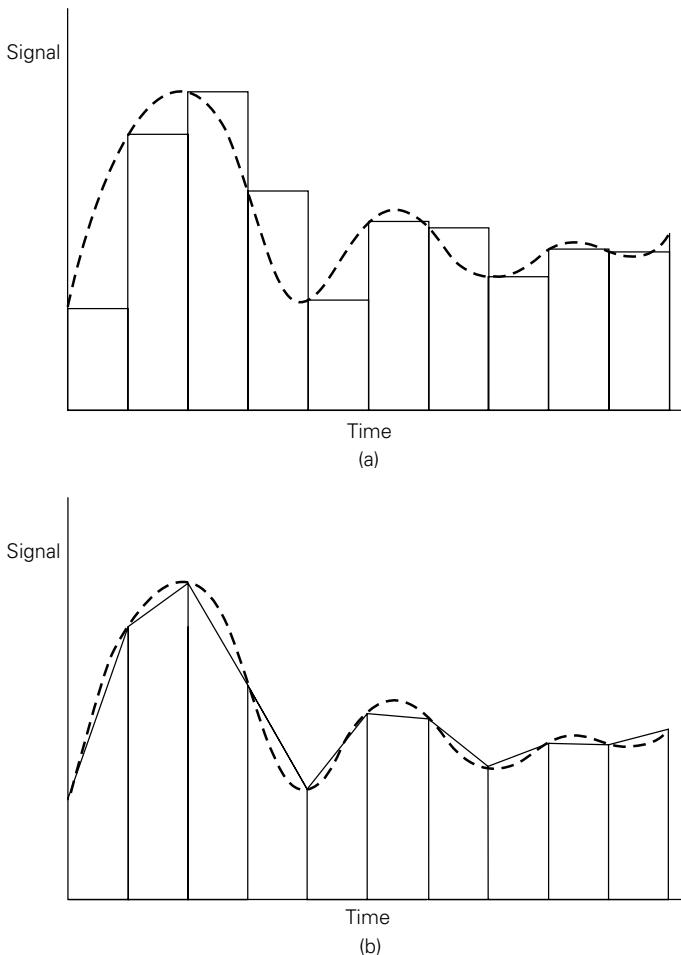

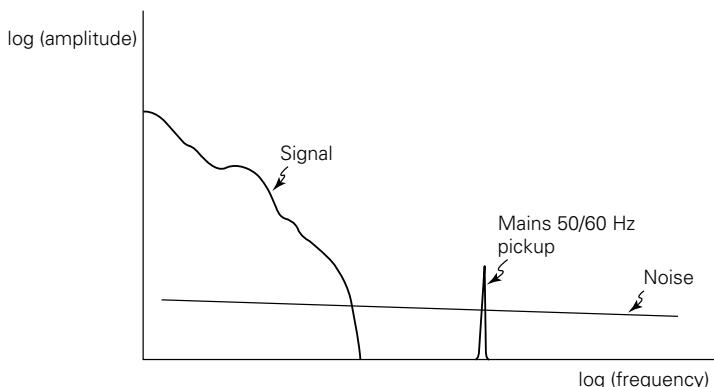

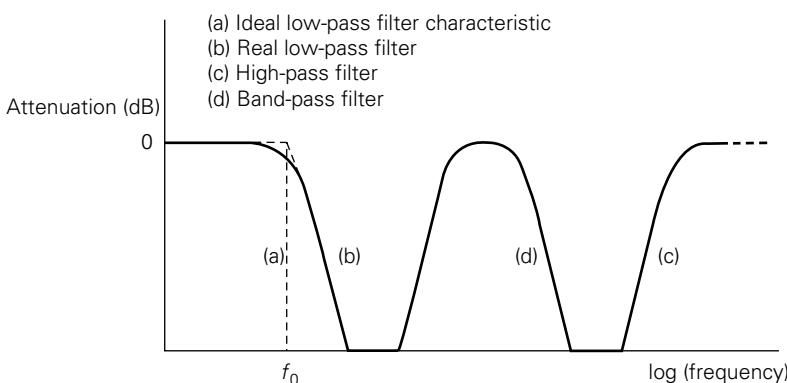

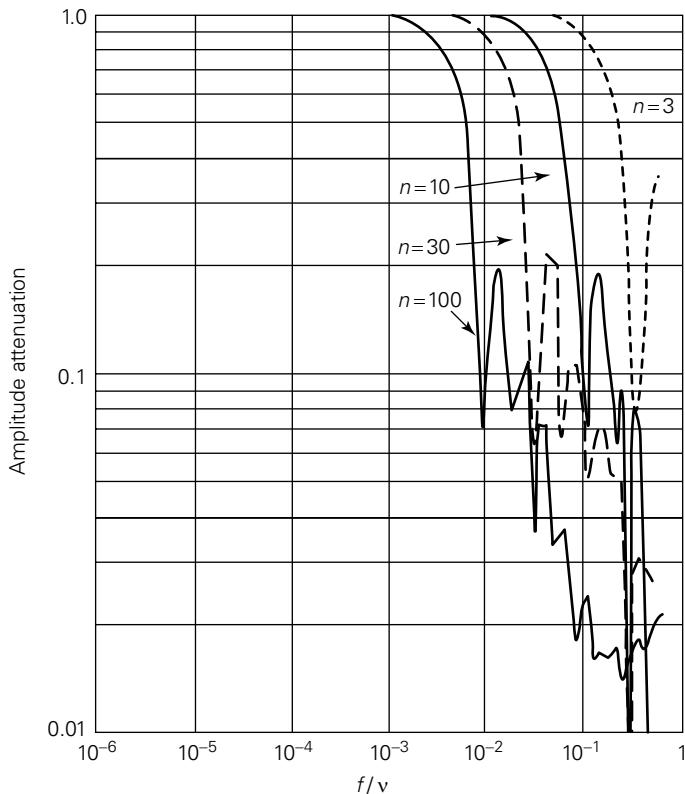

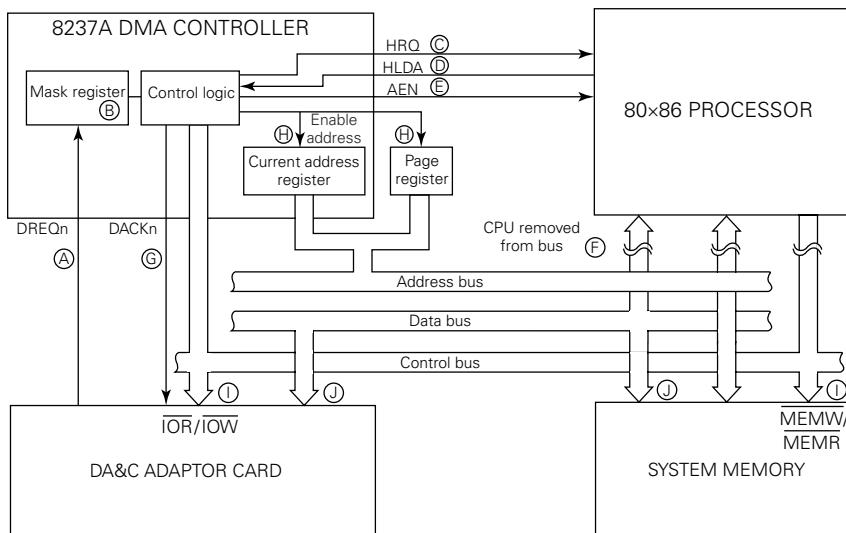

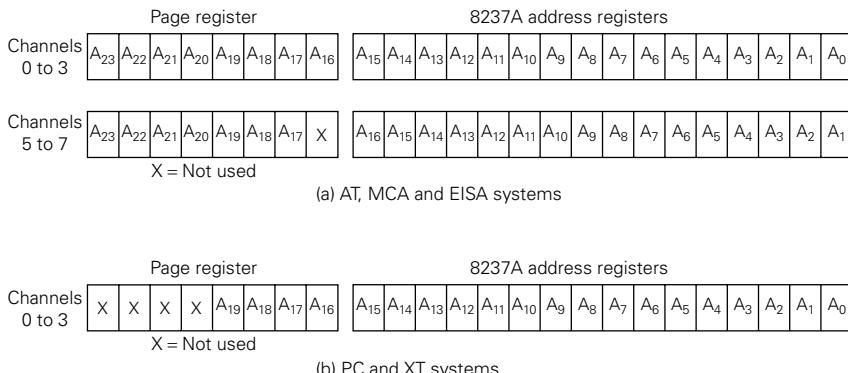

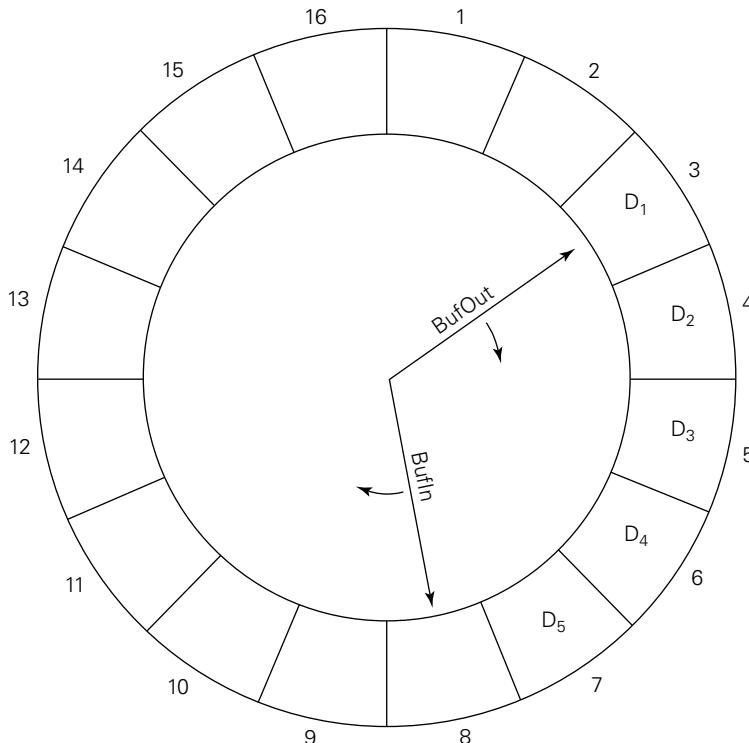

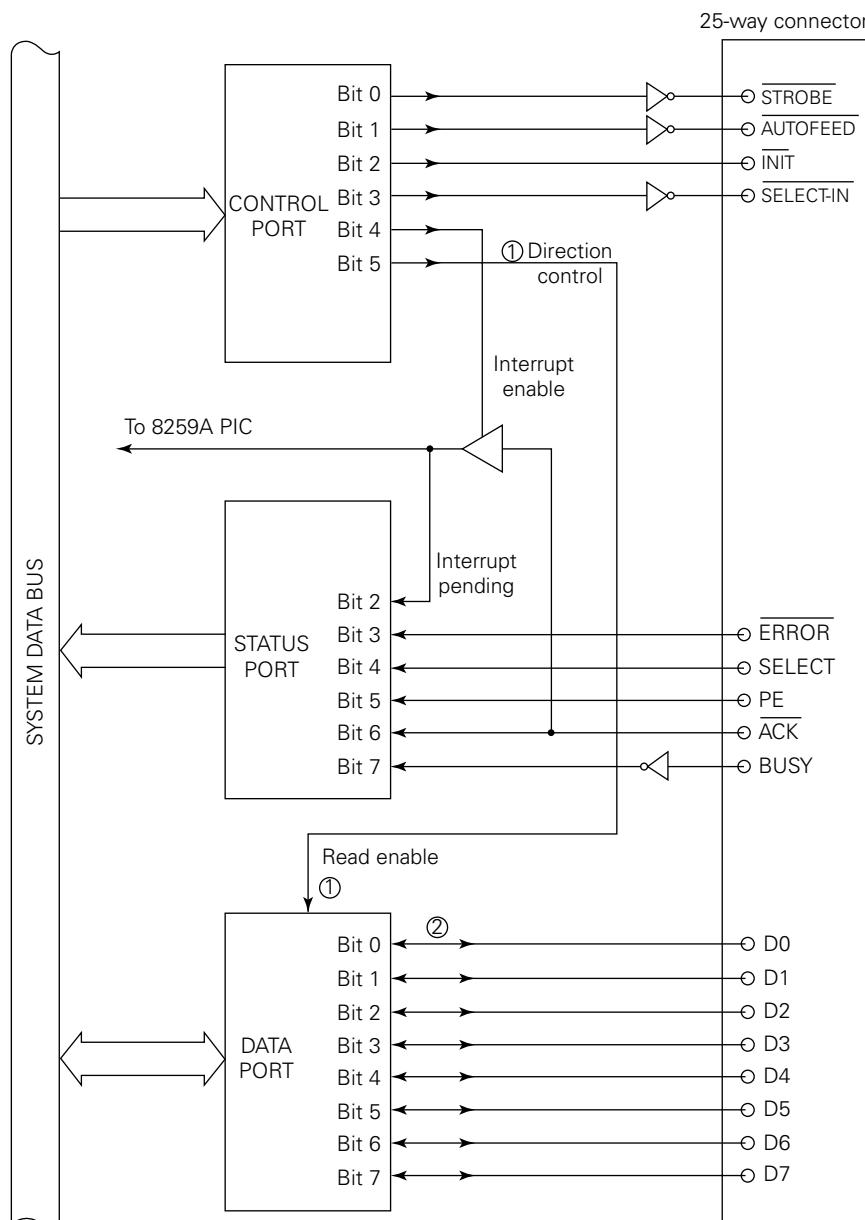

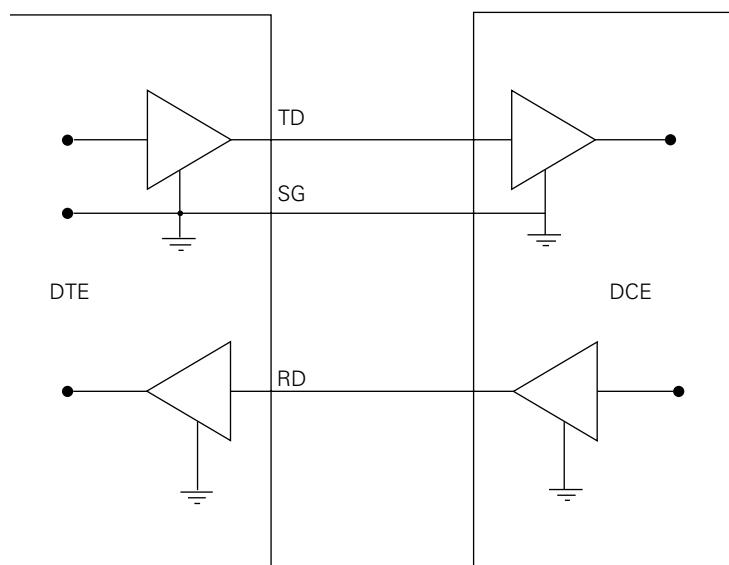

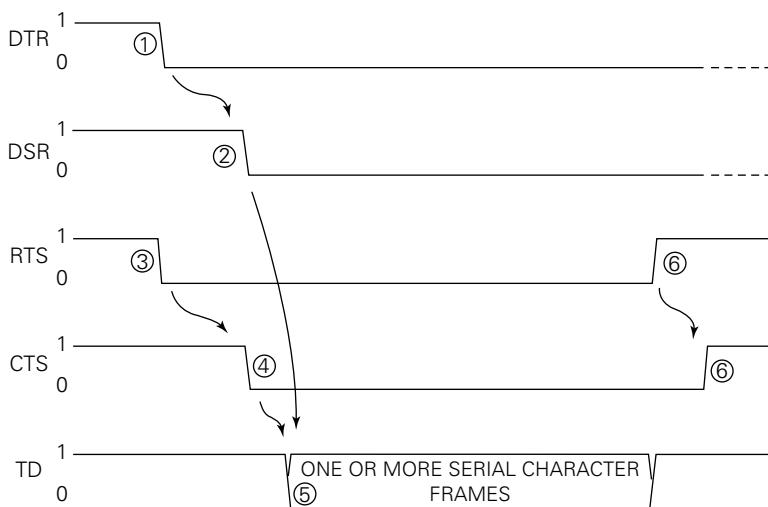

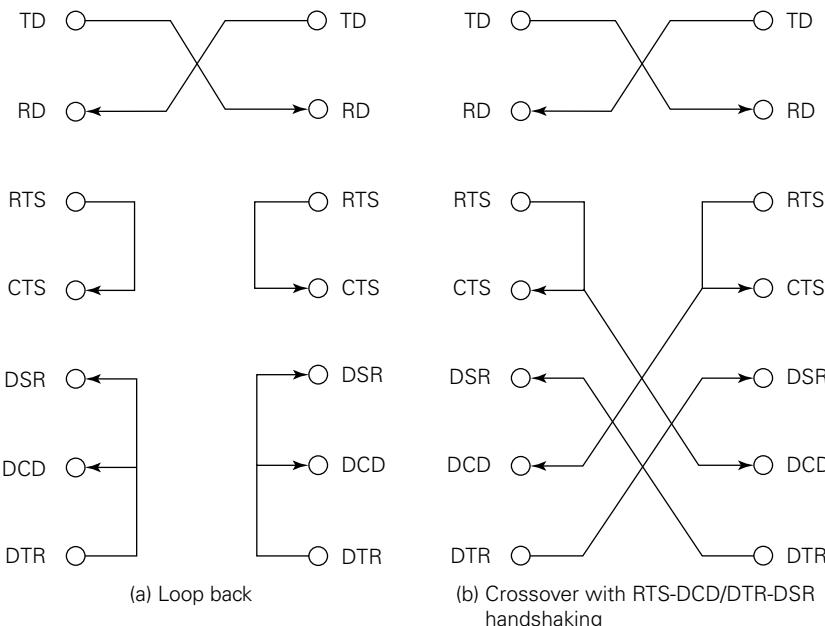

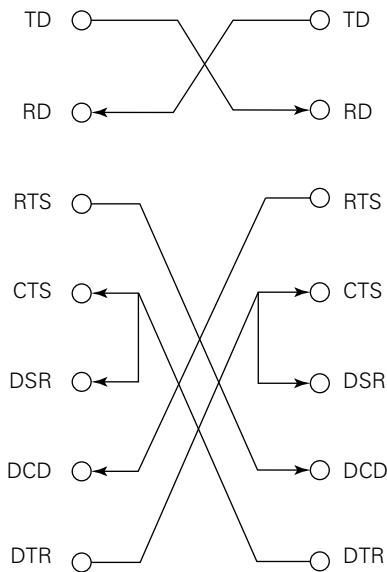

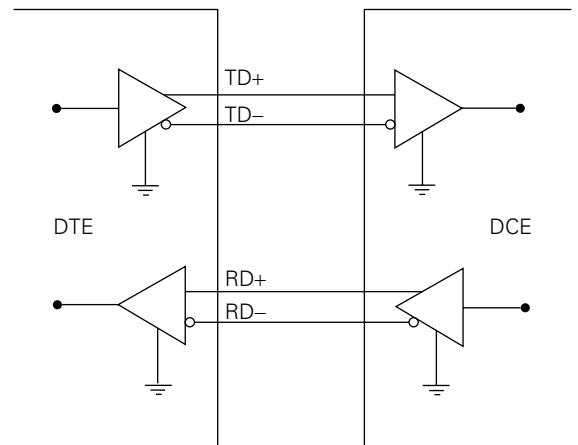

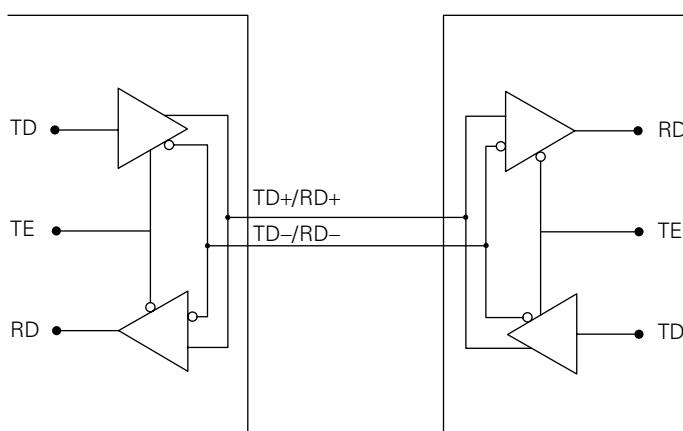

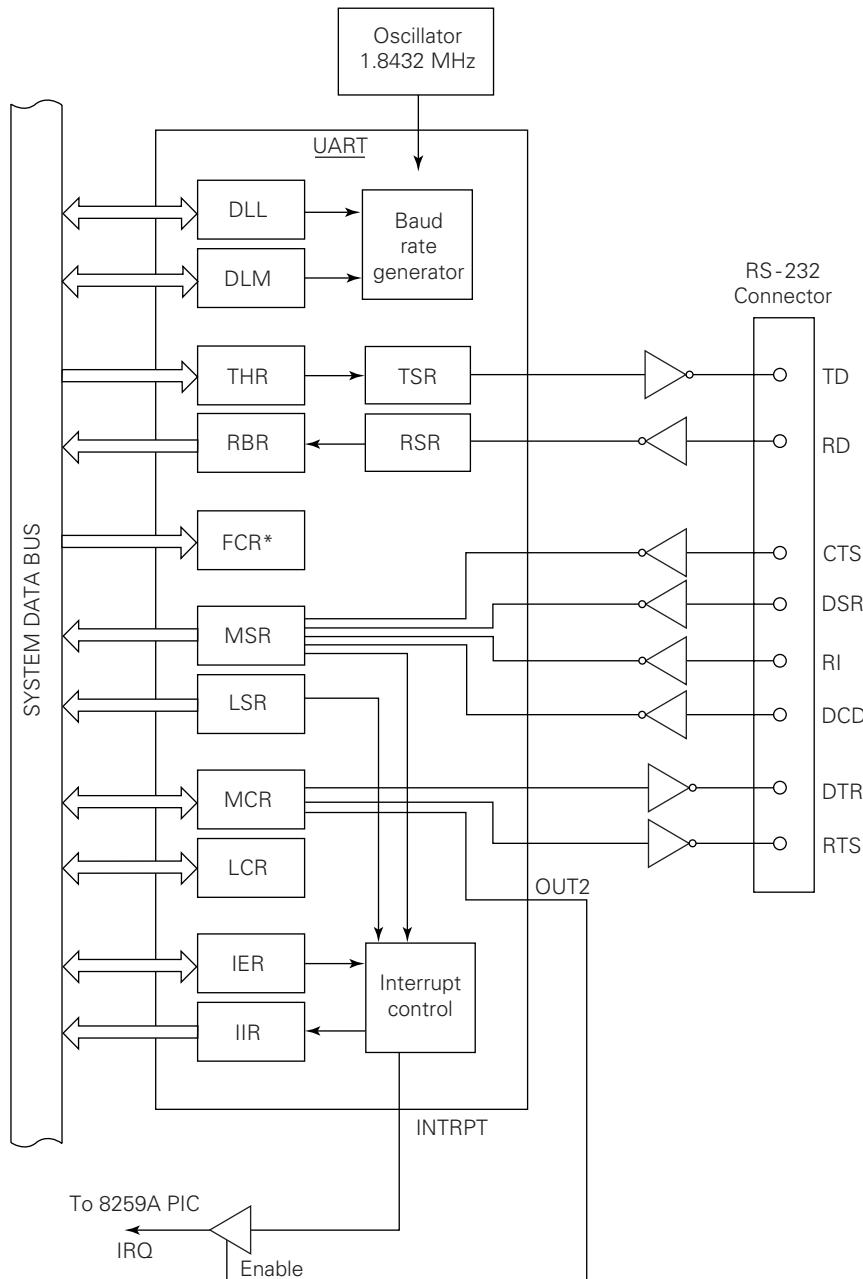

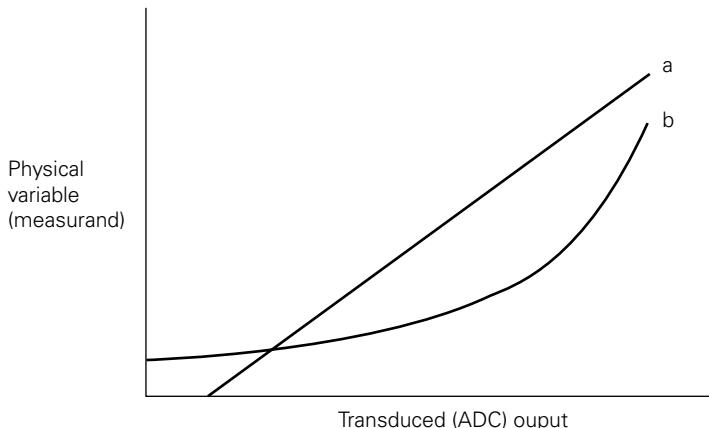

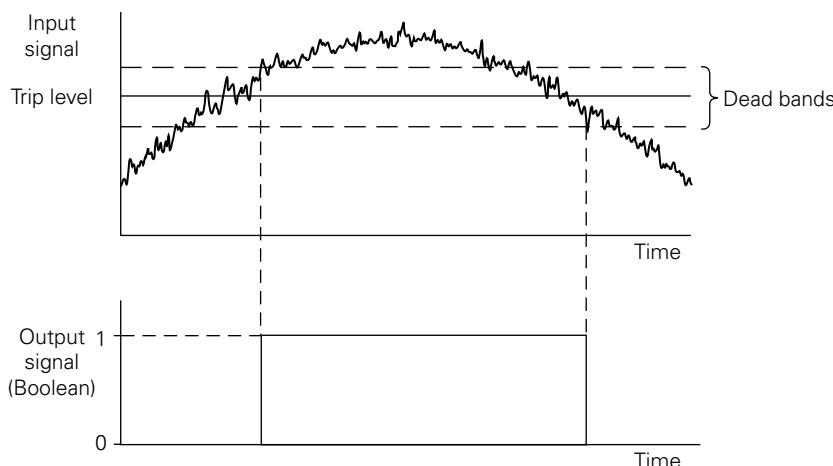

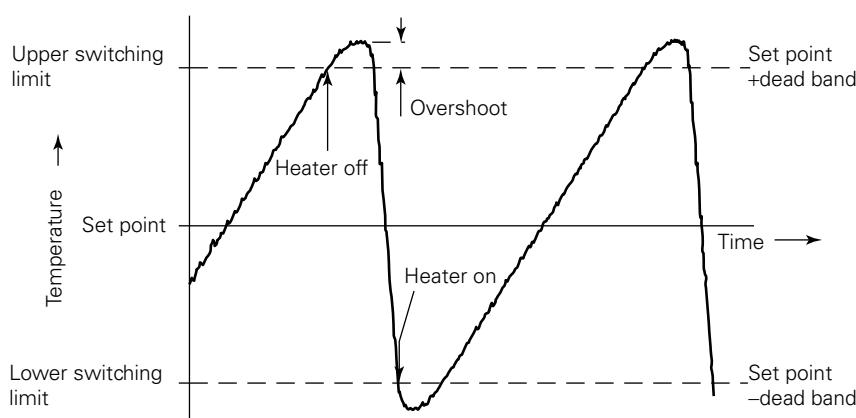

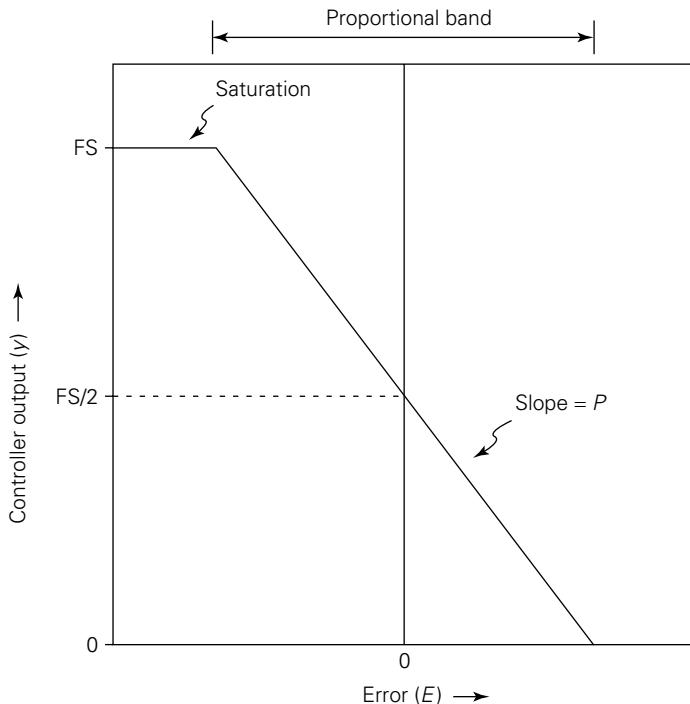

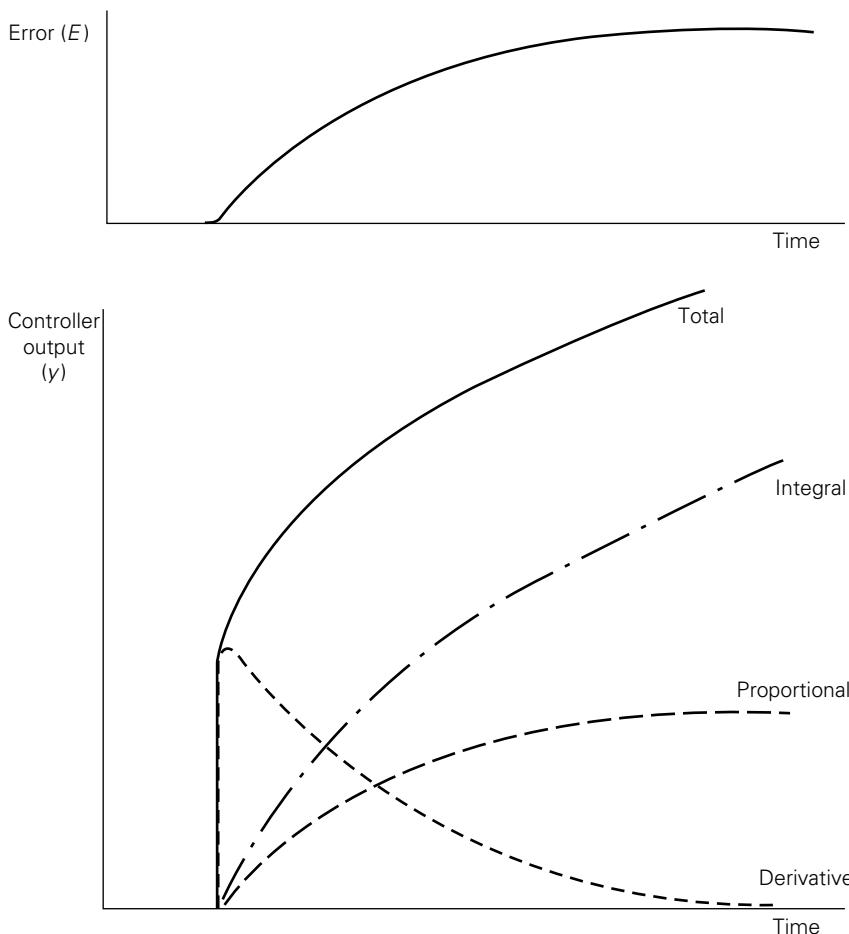

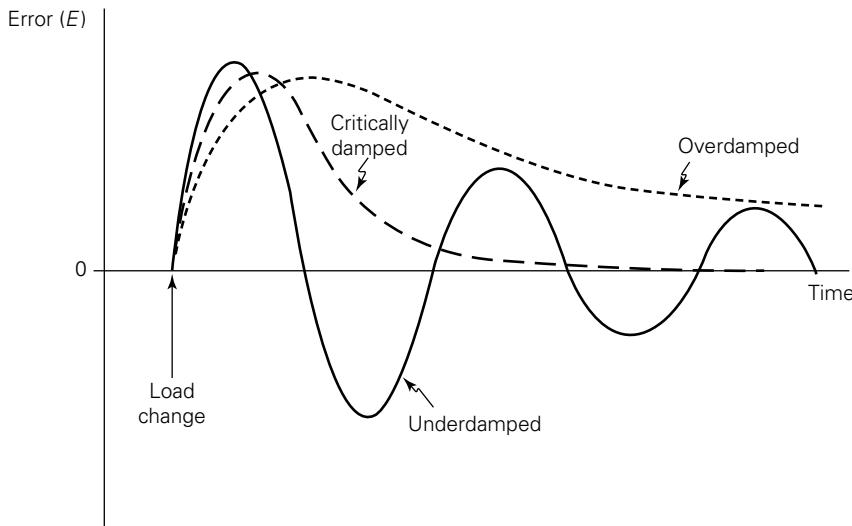

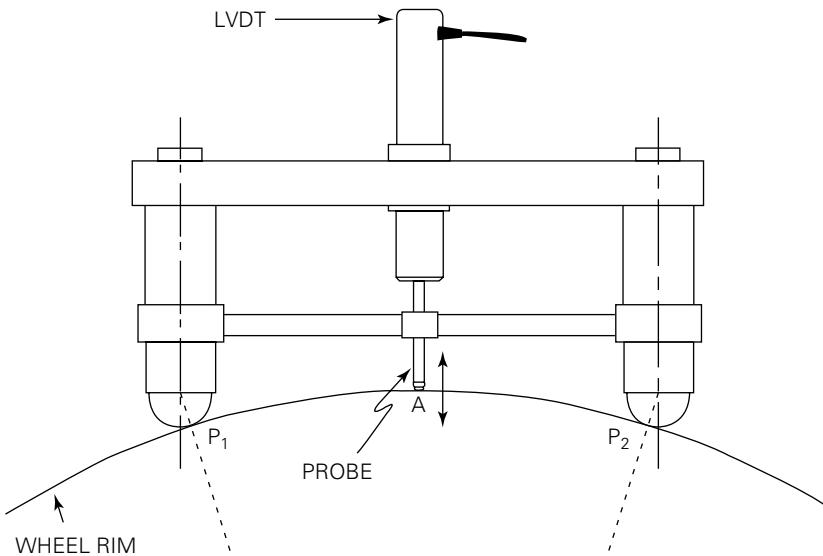

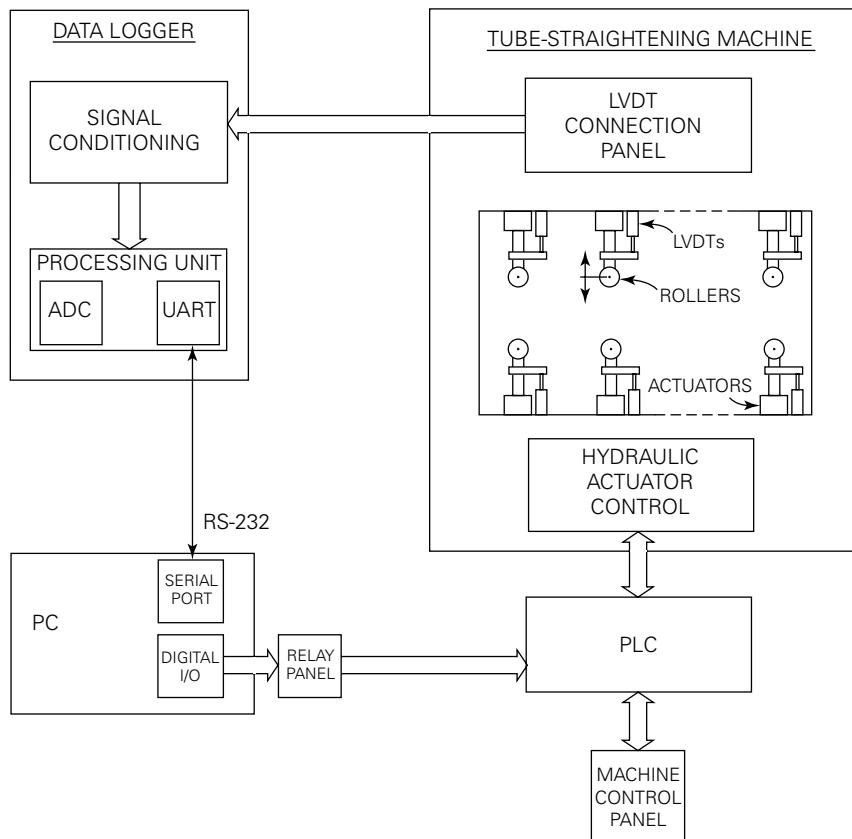

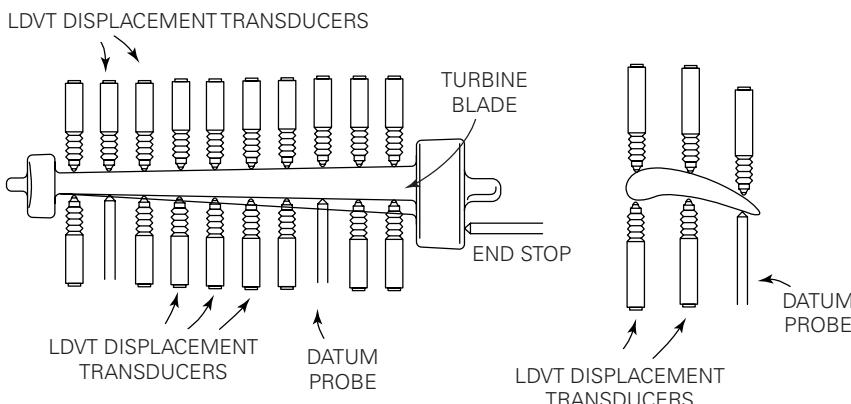

The nature of the run-time portion varies immensely. In some monitoring applications, the run-time routine may be very simple indeed. It might, for example, consist of an iterative polling loop that repeatedly reads data from one or more sensors and then perhaps stores the data in a disk file or displays it on the PC's screen. In many applications other tasks may also have to be carried out. These might include scaling and filtering the acquired data, or executing dynamic control algorithms.