INCLUDES

FREE

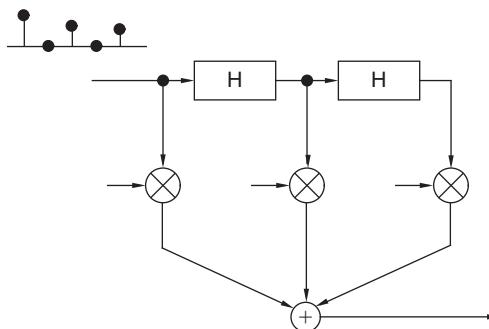

NEWNES ONLINE

MEMBERSHIP

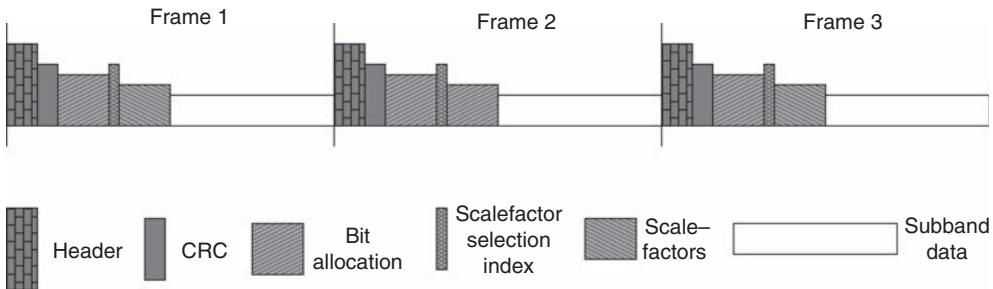

# DIGITAL SIGNAL PROCESSING

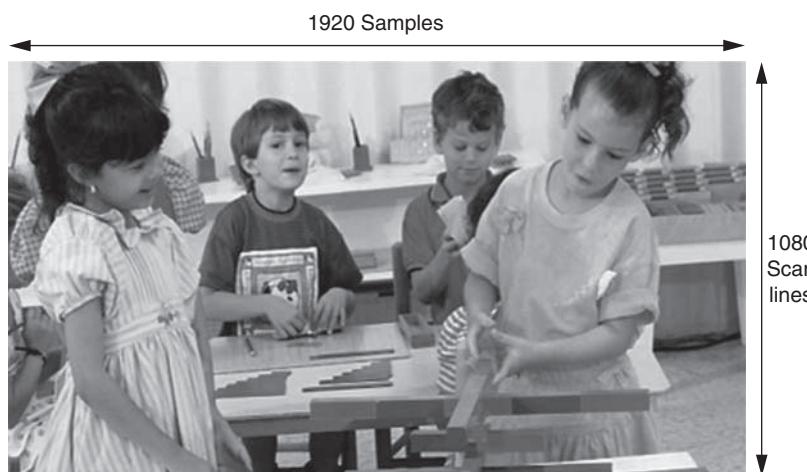

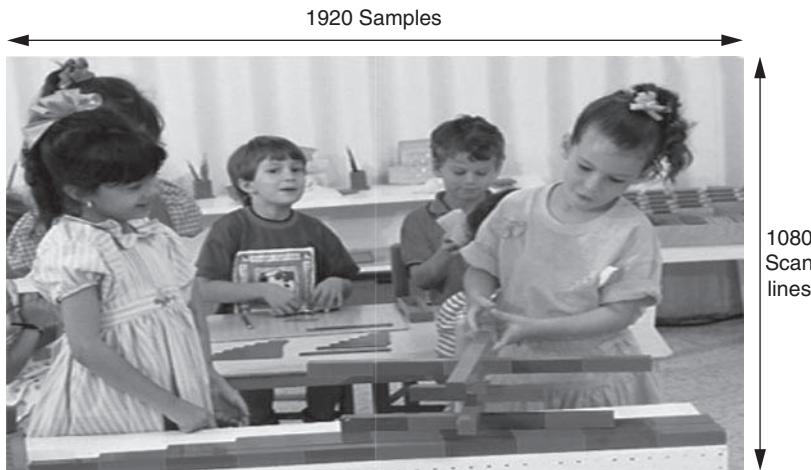

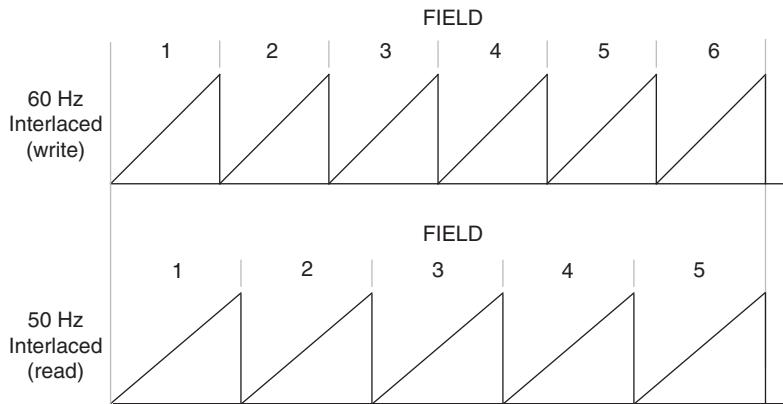

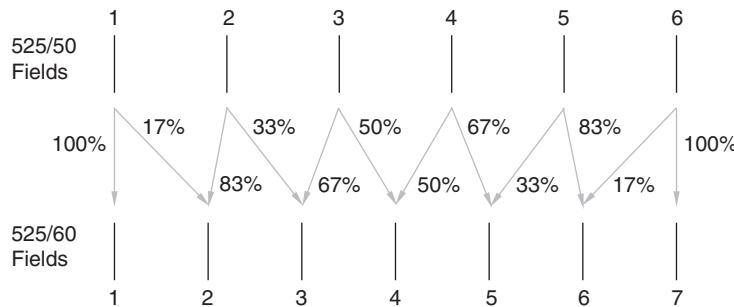

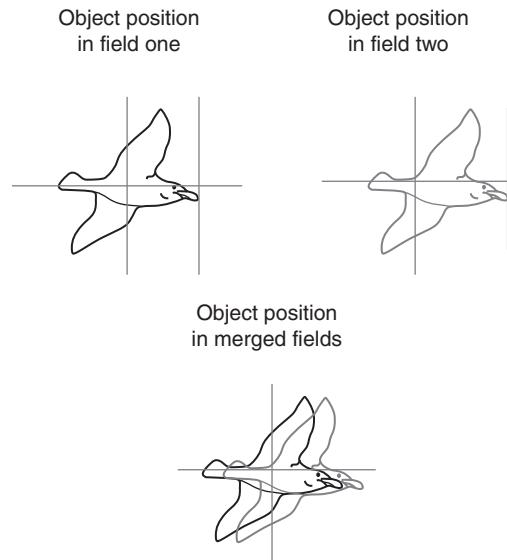

## WORLD CLASS DESIGNS

- Hand-picked content selected by Kenton Williston, Editor of **DSP DesignLine**

- Proven best design practices for image, audio, and video processing

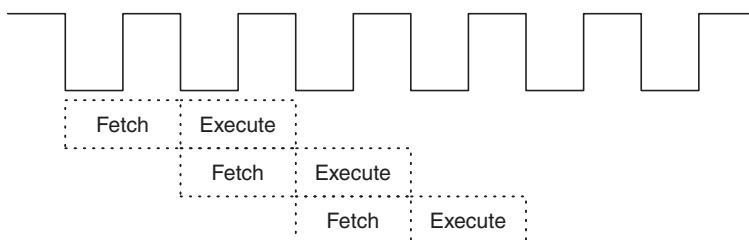

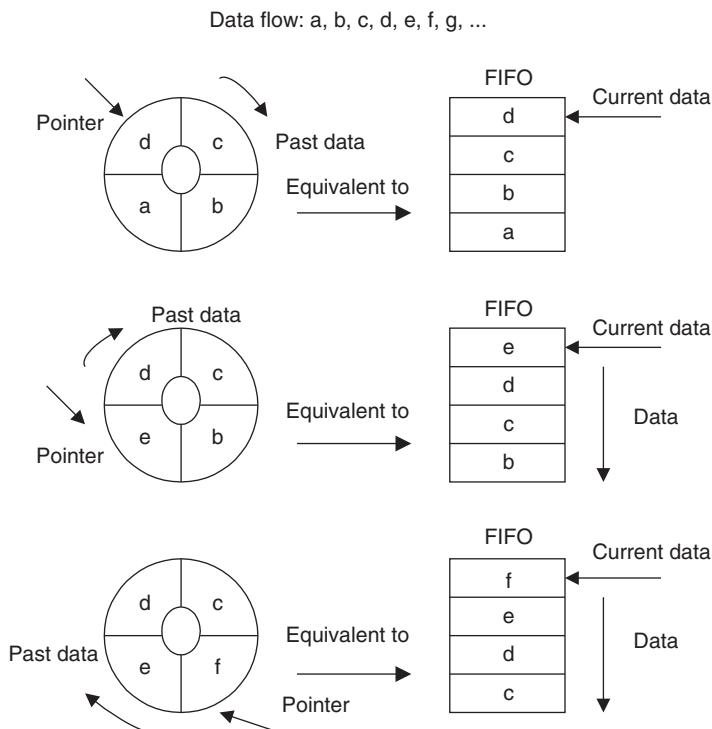

- Case histories and design examples get you off and running on your current project

Kenton Williston EDITOR

*Digital Signal Processing*

*World Class Designs*

***Newnes World Class Designs Series***

***Analog Circuits: World Class Designs***

Robert A. Pease

ISBN: 978-0-7506-8627-3

***Embedded Systems: World Class Designs***

Jack Ganssle

ISBN: 978-0-7506-8625-9

***Power Sources and Supplies: World Class Designs***

Marty Brown

ISBN: 978-0-7506-8626-6

***FPGAs: World Class Designs***

Clive “Max” Maxfield

ISBN: 978-1-85617-621-7

***Digital Signal Processing: World Class Designs***

Kenton Williston

ISBN: 978-1-85617-623-1

***Portable Electronics: World Class Designs***

John Donovan

ISBN: 978-1-85617-624-8

***RF Front-End: World Class Designs***

Janine Sullivan Love

ISBN: 978-1-85617-622-4

For more information on these and other Newnes titles visit: [www.newnespress.com](http://www.newnespress.com)

# *Digital Signal Processing*

## *World Class Designs*

Kenton Williston

*with*

Rick Gentile

Keith Jack

David Katz

Nasser Kehtarnavaz

Walt Kester

Dake Liu

Robert Meddins

Robert Oshana

Ian Poole

Khalid Sayood

Li Tan

AMSTERDAM • BOSTON • HEIDELBERG • LONDON

NEW YORK • OXFORD • PARIS • SAN DIEGO

SAN FRANCISCO • SINGAPORE • SYDNEY • TOKYO

Newnes is an imprint of Elsevier

Newnes is an imprint of Elsevier

30 Corporate Drive, Suite 400, Burlington, MA 01803, USA

Linacre House, Jordan Hill, Oxford OX2 8DP, UK

Copyright © 2009, Elsevier Inc. All rights reserved.

No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher.

Permissions may be sought directly from Elsevier's Science & Technology Rights Department in Oxford, UK: phone: (+44) 1865 843830, fax: (+44) 1865 853333, E-mail: [permissions@elsevier.com](mailto:permissions@elsevier.com). You may also complete your request online via the Elsevier homepage (<http://elsevier.com>), by selecting "Support & Contact" then "Copyright and Permission" and then "Obtaining Permissions."

**Library of Congress Cataloging-in-Publication Data**

Application submitted.

**British Library Cataloguing-in-Publication Data**

A catalogue record for this book is available from the British Library.

ISBN: 978-1-85617-623-1

For information on all Newnes publications

visit our Web site at [www.elsevierdirect.com](http://www.elsevierdirect.com)

09 10 11 10 9 8 7 6 5 4 3 2 1

Printed in the United States of America

Working together to grow

libraries in developing countries

[www.elsevier.com](http://www.elsevier.com) | [www.bookaid.org](http://www.bookaid.org) | [www.sabre.org](http://www.sabre.org)

ELSEVIER BOOK AID International Sabre Foundation

# Contents

|                                                                             |            |

|-----------------------------------------------------------------------------|------------|

| <i>Preface</i> .....                                                        | ix         |

| <i>About the Editor</i> .....                                               | xv         |

| <i>About the Contributors</i> .....                                         | xvii       |

| <b>Chapter 1: ADCs, DACs, and Sampling Theory .....</b>                     | <b>01</b>  |

| 1.1 Coding and Quantizing .....                                             | 02         |

| 1.2 Sampling Theory .....                                                   | 24         |

| 1.3 Data Converter AC Errors .....                                          | 36         |

| 1.4 General Data Converter Specifications .....                             | 93         |

| 1.5 Defining the Specifications .....                                       | 96         |

| References .....                                                            | 117        |

| Bibliography .....                                                          | 119        |

| <b>Chapter 2: Digital Filters .....</b>                                     | <b>123</b> |

| 2.1 Chapter Preview .....                                                   | 123        |

| 2.2 Analog Signal Processing .....                                          | 124        |

| 2.3 An Alternative Approach .....                                           | 125        |

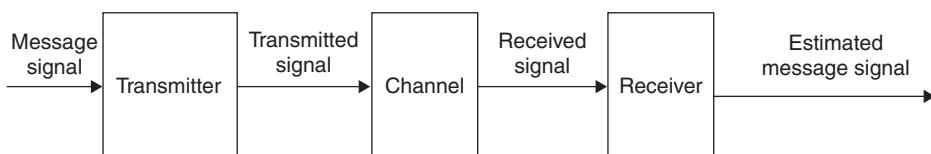

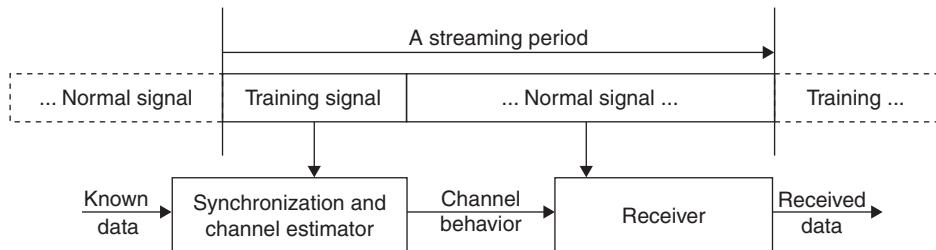

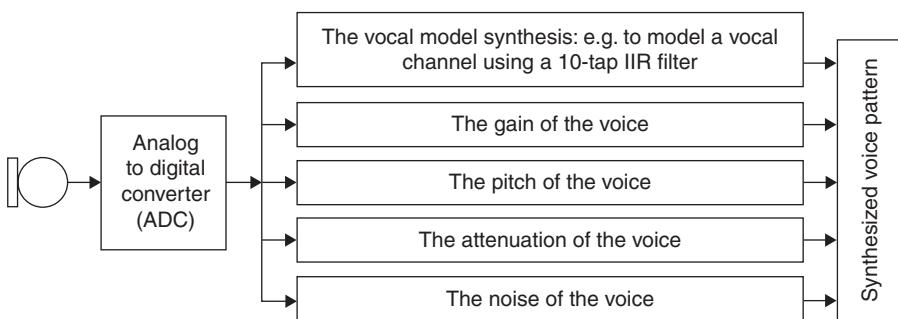

| 2.4 The Complete DSP System .....                                           | 126        |

| 2.5 Recap .....                                                             | 130        |

| 2.6 Digital Data Processing .....                                           | 131        |

| 2.7 The Running Average Filter .....                                        | 131        |

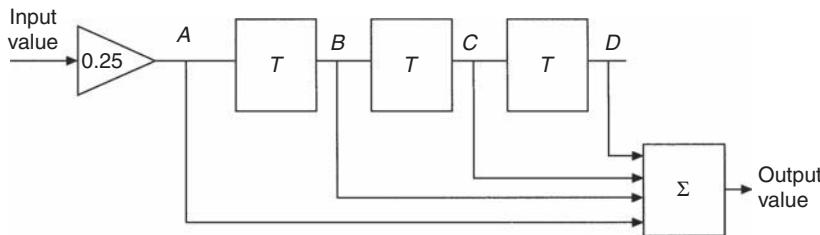

| 2.8 Representation of Processing Systems .....                              | 134        |

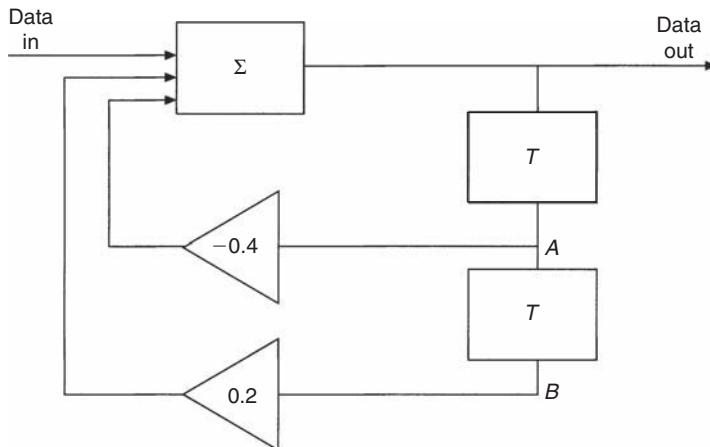

| 2.9 Feedback (or Recursive) Filters .....                                   | 134        |

| 2.10 Chapter Summary .....                                                  | 137        |

| Bibliography .....                                                          | 138        |

| <b>Chapter 3: Frequency Domain Processing .....</b>                         | <b>139</b> |

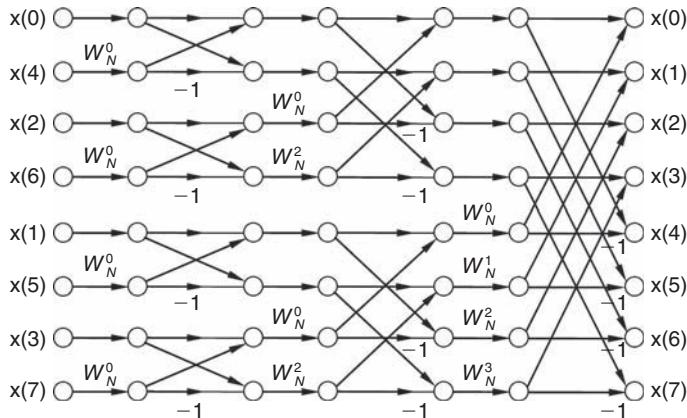

| 3.1 Discrete Fourier Transform (DFT) and Fast Fourier Transform (FFT) ..... | 140        |

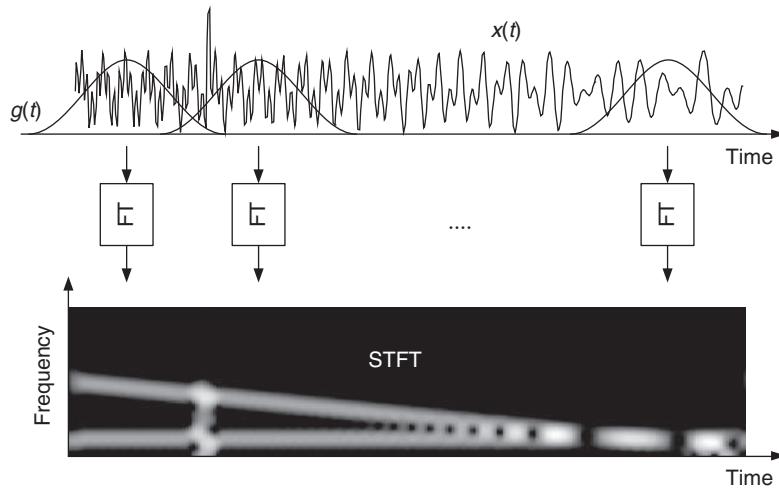

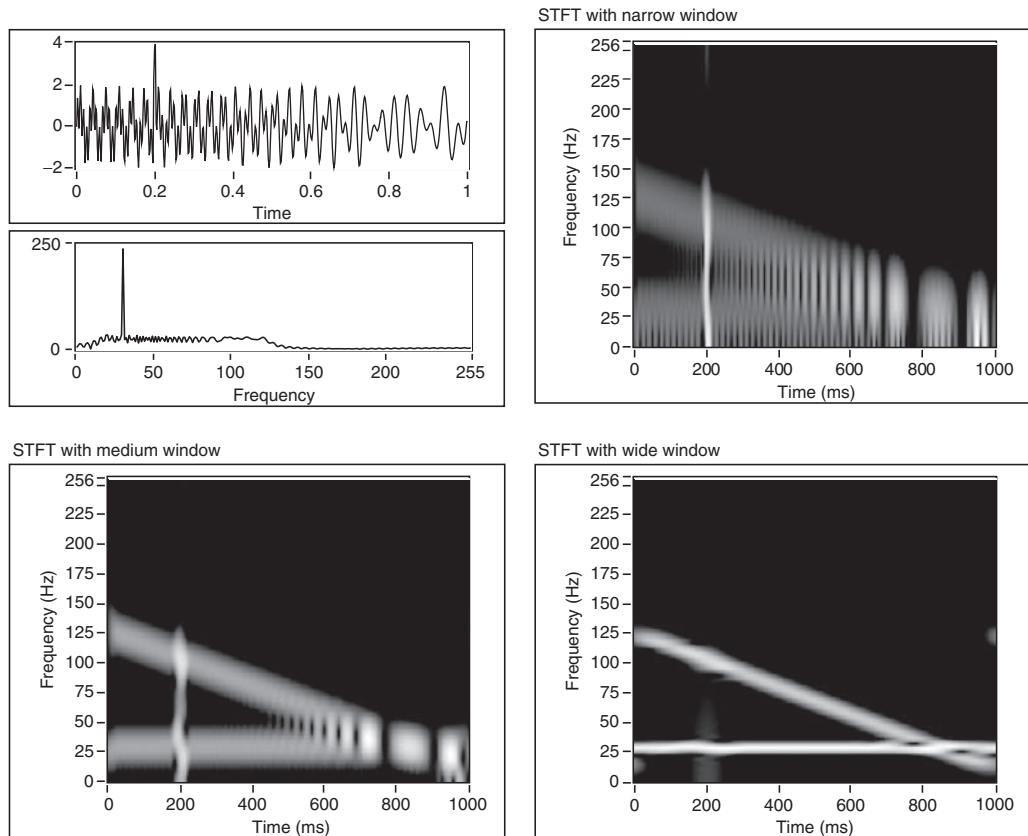

| 3.2 Short-Time Fourier Transform (STFT) .....                               | 141        |

|      |                                                 |            |

|------|-------------------------------------------------|------------|

| 3.3  | Discrete Wavelet Transform (DWT) .....          | 142        |

| 3.4  | Signal Processing Toolset .....                 | 145        |

|      | References.....                                 | 156        |

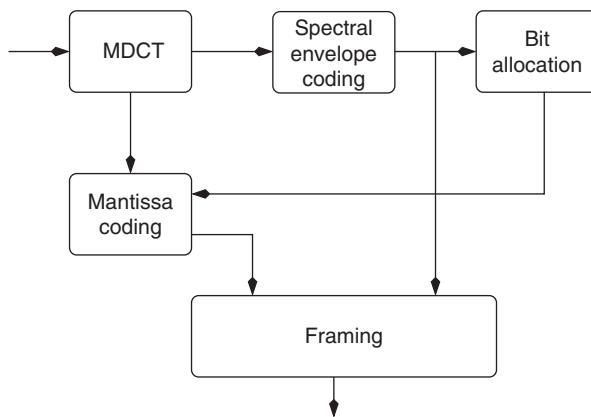

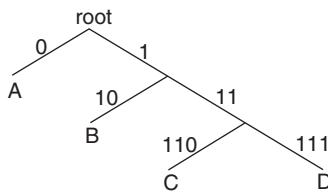

|      | <b><i>Chapter 4: Audio Coding</i></b> .....     | <b>159</b> |

| 4.1  | Overview .....                                  | 160        |

| 4.2  | Introduction.....                               | 160        |

| 4.3  | MPEG Audio Coding.....                          | 164        |

| 4.4  | MPEG Advanced Audio Coding.....                 | 173        |

| 4.5  | Dolby AC3 (Dolby Digital) .....                 | 180        |

| 4.6  | Other Standards.....                            | 183        |

| 4.7  | Summary .....                                   | 183        |

|      | Bibliography .....                              | 183        |

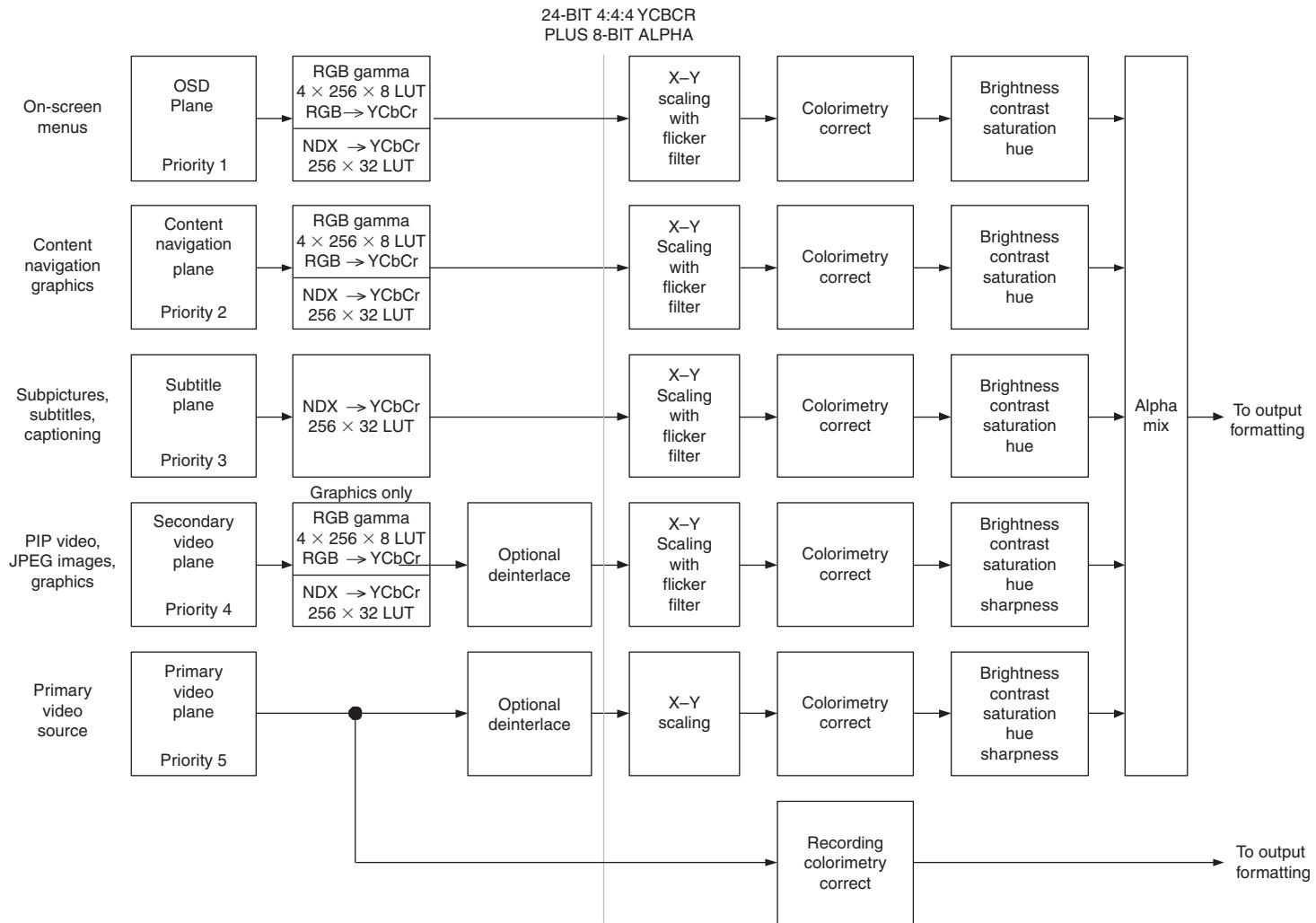

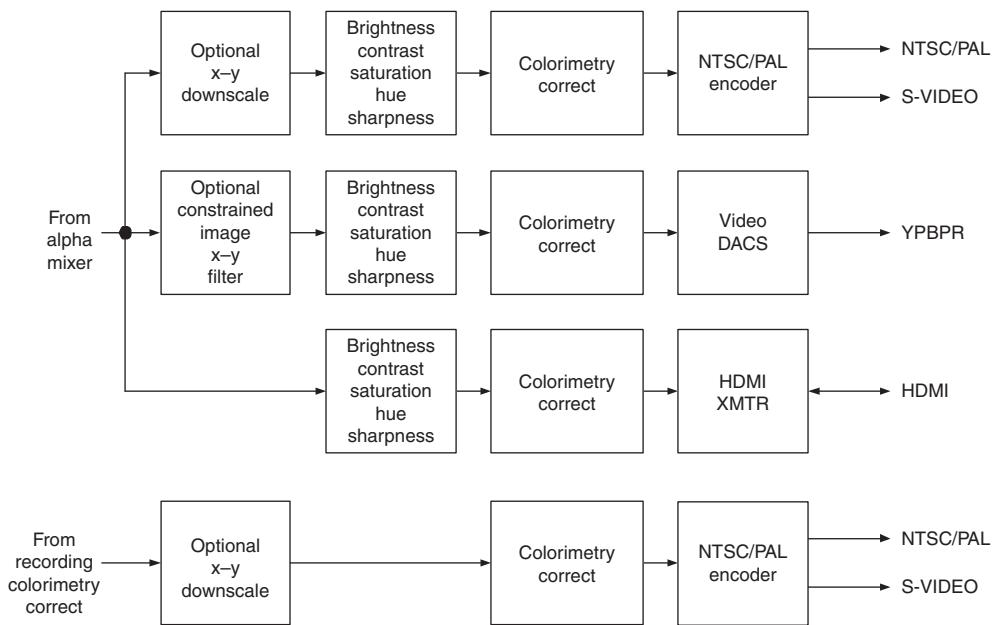

|      | <b><i>Chapter 5: Video Processing</i></b> ..... | <b>185</b> |

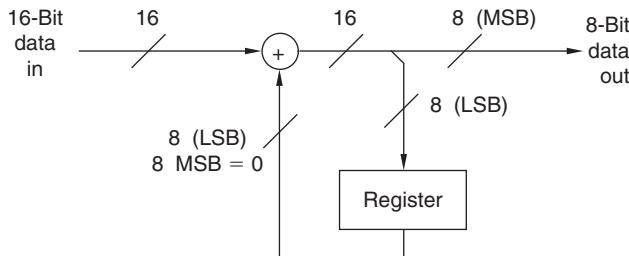

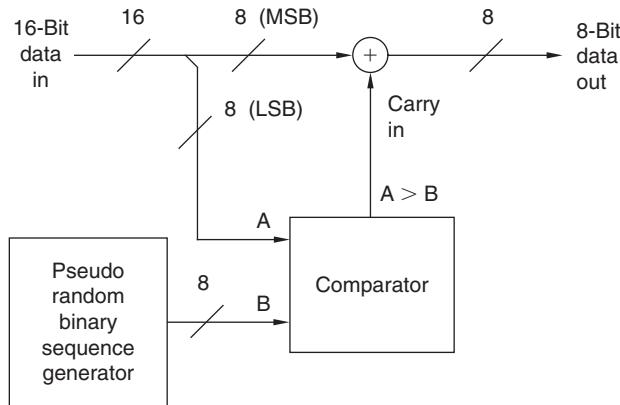

| 5.1  | Rounding Considerations .....                   | 186        |

| 5.2  | SDTV-HDTV YCbCr Transforms .....                | 187        |

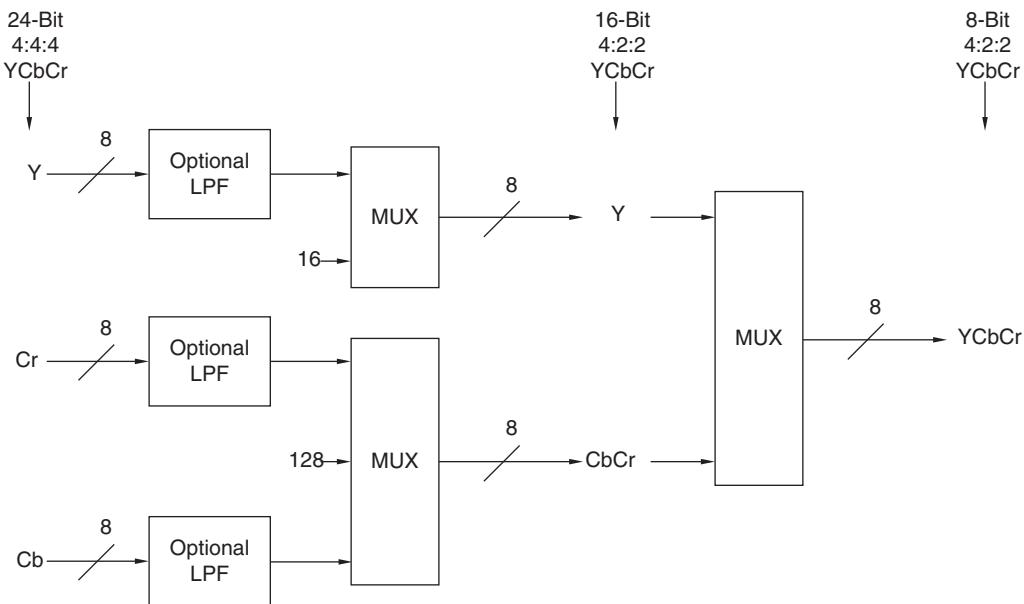

| 5.3  | 4:4:4 to 4:2:2 YCbCr Conversion .....           | 189        |

| 5.4  | Display Enhancement .....                       | 192        |

| 5.5  | Video Mixing and Graphics Overlay .....         | 198        |

| 5.6  | Luma and Chroma Keying .....                    | 204        |

| 5.7  | Video Scaling .....                             | 219        |

| 5.8  | Scan Rate Conversion .....                      | 226        |

| 5.9  | Noninterlaced-to-Interlaced Conversion .....    | 237        |

| 5.10 | Interlaced-to-Noninterlaced Conversion .....    | 238        |

| 5.11 | DCT-Based Compression .....                     | 246        |

| 5.12 | Fixed Pixel Display Considerations .....        | 250        |

| 5.13 | Application Example.....                        | 251        |

|      | Bibliography .....                              | 253        |

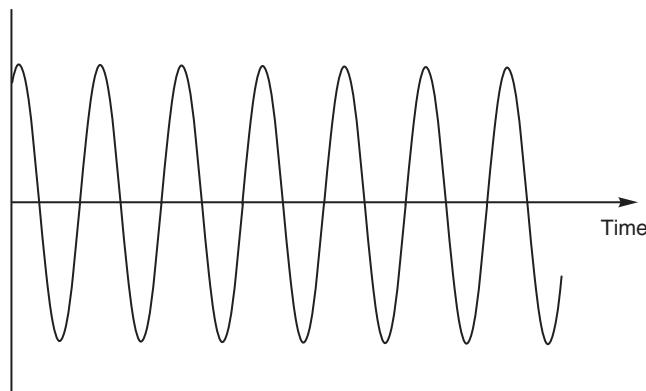

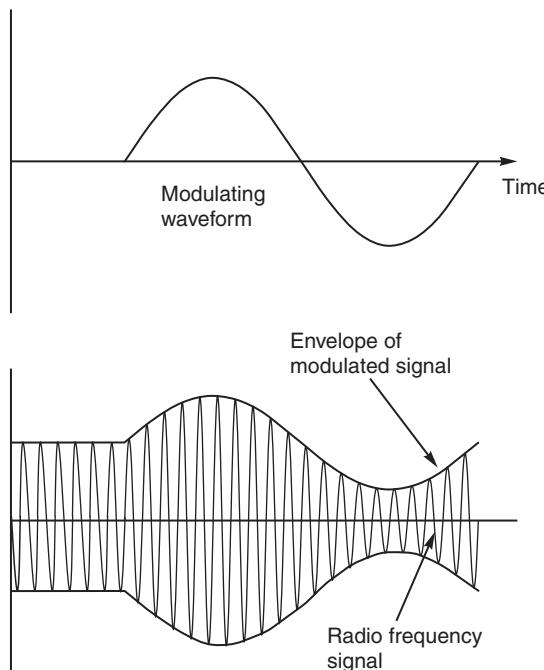

|      | <b><i>Chapter 6: Modulation</i></b> .....       | <b>255</b> |

| 6.1  | Radio Carrier.....                              | 256        |

| 6.2  | Amplitude Modulation.....                       | 256        |

| 6.3  | Modulation Index .....                          | 261        |

| 6.4  | Frequency Modulation .....                      | 261        |

| 6.5  | Modulation Index and Deviation Ratio.....       | 263        |

| 6.6  | Sidebands .....                                 | 263        |

| 6.7  | Bandwidth .....                                 | 265        |

---

|                                                                    |                                                                                                              |            |

|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------------|

| 6.8                                                                | Improvement in Signal-to-Noise Ratio .....                                                                   | 266        |

| 6.9                                                                | Frequency-Shift Keying .....                                                                                 | 266        |

| 6.10                                                               | Phase Modulation.....                                                                                        | 267        |

| 6.11                                                               | Phase-Shift Keying.....                                                                                      | 268        |

| 6.12                                                               | Minimum-Shift Keying.....                                                                                    | 270        |

| 6.13                                                               | Quadrature Amplitude Modulation.....                                                                         | 272        |

| 6.14                                                               | Spread Spectrum Techniques .....                                                                             | 274        |

| 6.15                                                               | Frequency Hopping.....                                                                                       | 274        |

| 6.16                                                               | Direct-Sequence Spread Spectrum.....                                                                         | 275        |

| 6.17                                                               | Orthogonal Frequency Division Multiplexing .....                                                             | 279        |

| 6.18                                                               | Bandwidth and Data Capacity.....                                                                             | 281        |

| 6.19                                                               | Summary .....                                                                                                | 282        |

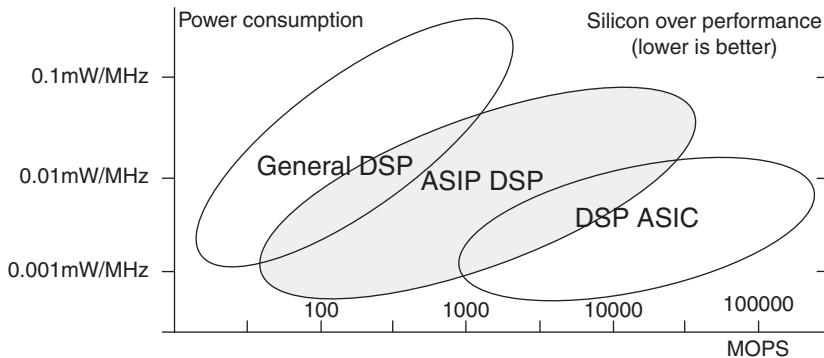

| <b>Chapter 7: DSP Hardware Options .....</b>                       |                                                                                                              | <b>283</b> |

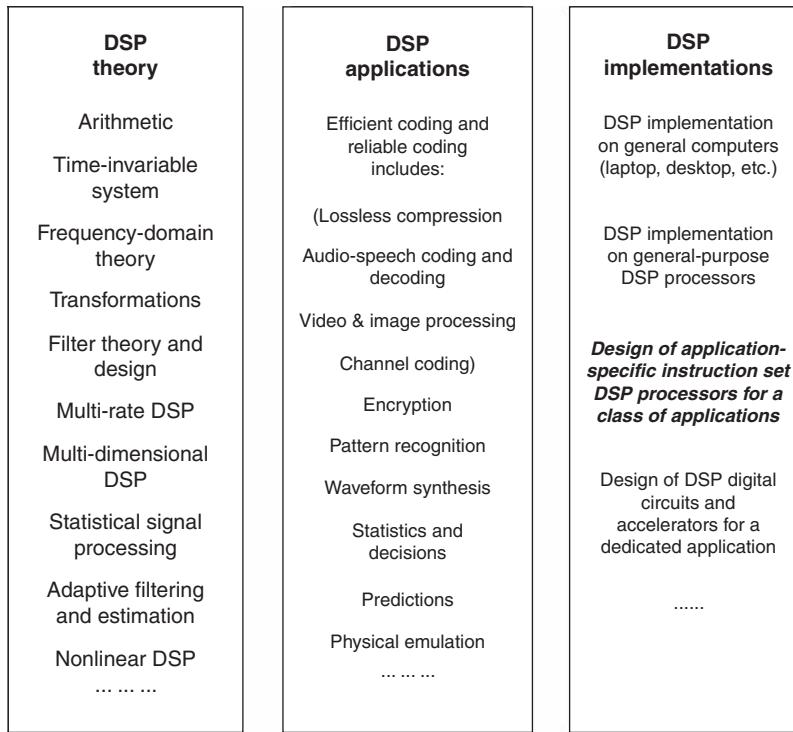

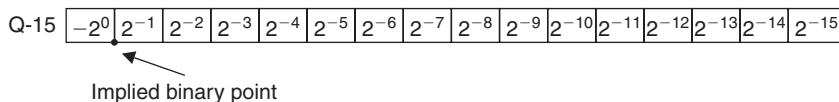

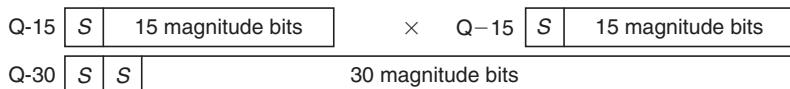

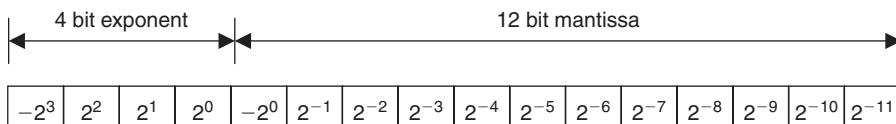

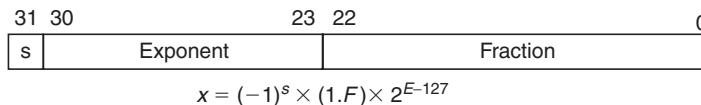

| 7.1                                                                | DSP Theory for Hardware Designers .....                                                                      | 284        |

| 7.2                                                                | Theory, Applications, and Implementations .....                                                              | 294        |

| 7.3                                                                | DSP Applications.....                                                                                        | 296        |

| 7.4                                                                | DSP Implementations .....                                                                                    | 304        |

| 7.5                                                                | Review of Processors and Systems .....                                                                       | 309        |

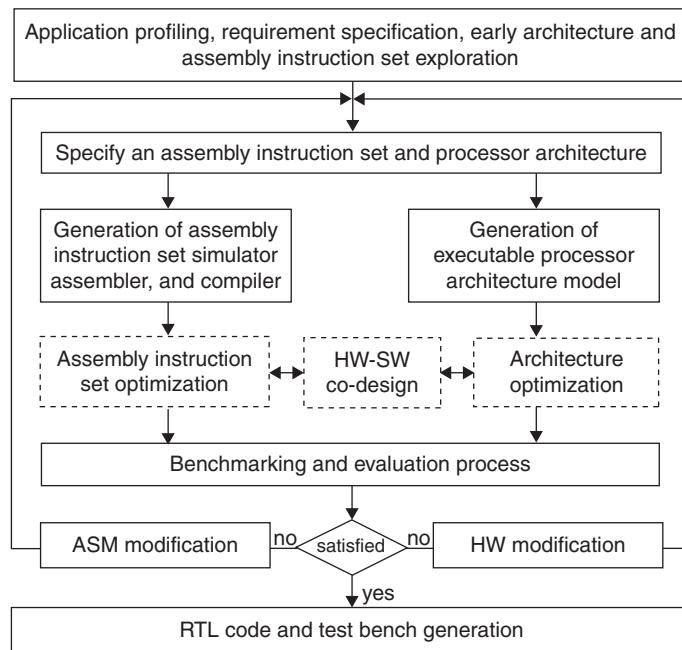

| 7.6                                                                | Design Flow .....                                                                                            | 317        |

| 7.7                                                                | Conclusions .....                                                                                            | 324        |

|                                                                    | References.....                                                                                              | 325        |

| <b>Chapter 8: DSP Processors and Fixed-Point Arithmetic.....</b>   |                                                                                                              | <b>329</b> |

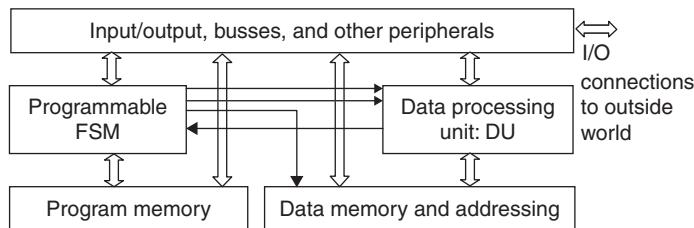

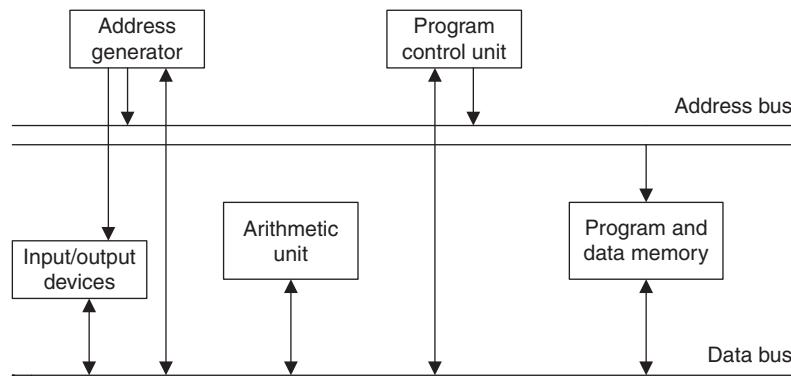

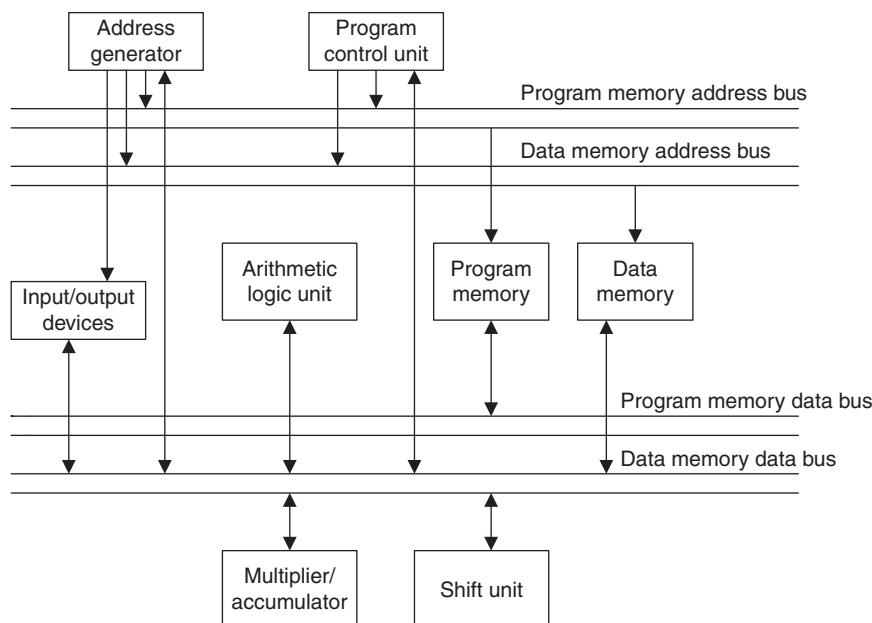

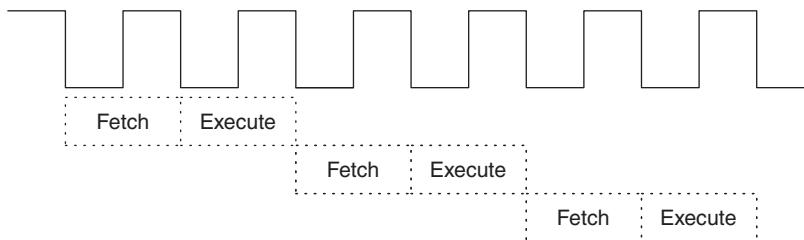

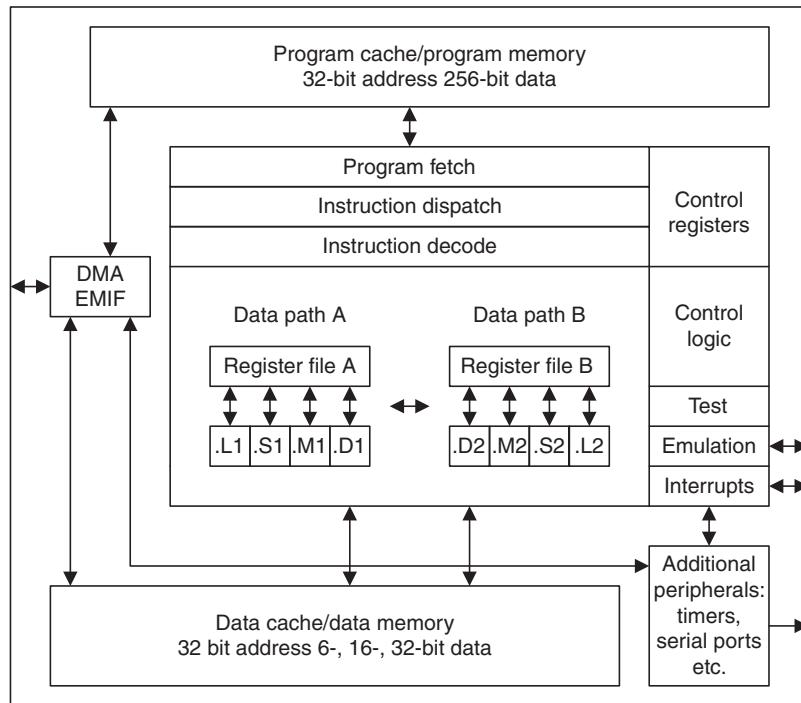

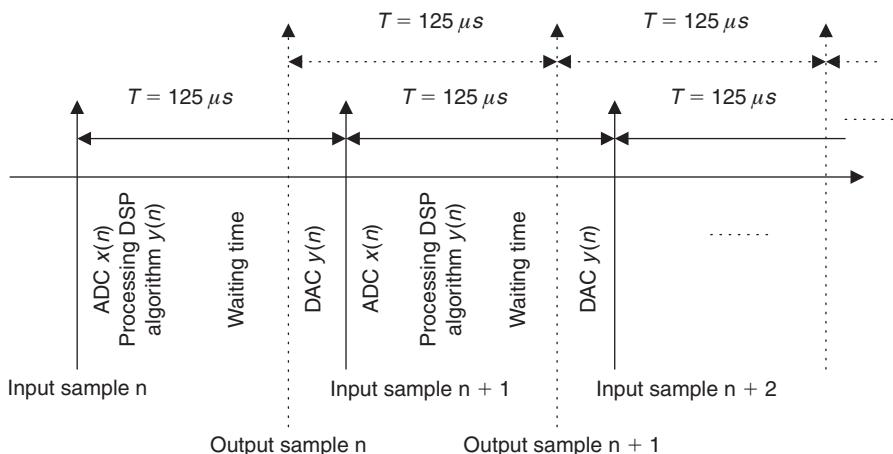

| 8.1                                                                | Digital Signal Processor Architecture.....                                                                   | 329        |

| 8.2                                                                | Digital Signal Processor Hardware Units .....                                                                | 333        |

| 8.3                                                                | Digital Signal Processors and Manufacturers .....                                                            | 335        |

| 8.4                                                                | Fixed-Point and Floating-Point Formats .....                                                                 | 336        |

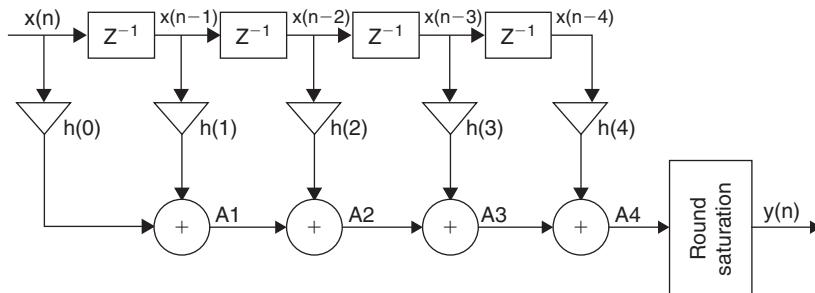

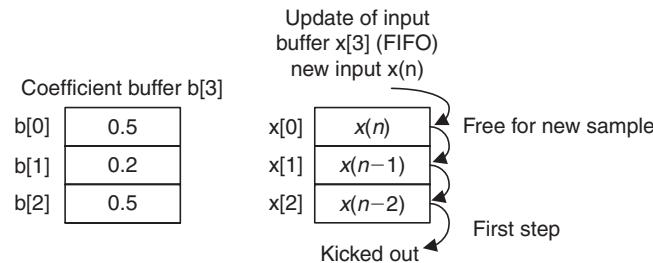

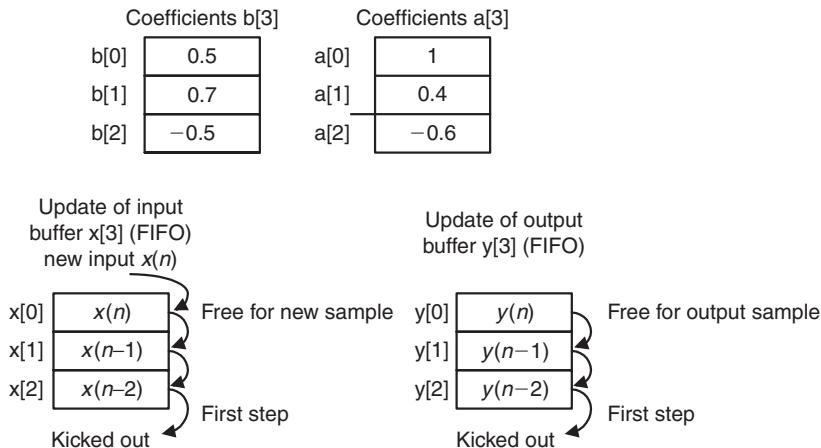

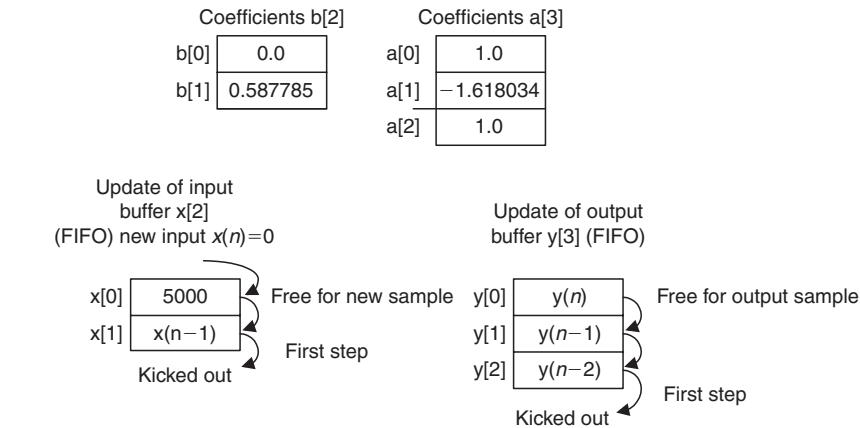

| 8.5                                                                | Finite Impulse Response and Infinite Impulse Response Filter<br>Implementations in Fixed-Point Systems ..... | 358        |

| 8.6                                                                | Digital Signal Processing Programming Examples .....                                                         | 364        |

| 8.7                                                                | Summary .....                                                                                                | 375        |

|                                                                    | Bibliography .....                                                                                           | 378        |

| <b>Chapter 9: Code Optimization and Resource Partitioning.....</b> |                                                                                                              | <b>379</b> |

| 9.1                                                                | Introduction.....                                                                                            | 380        |

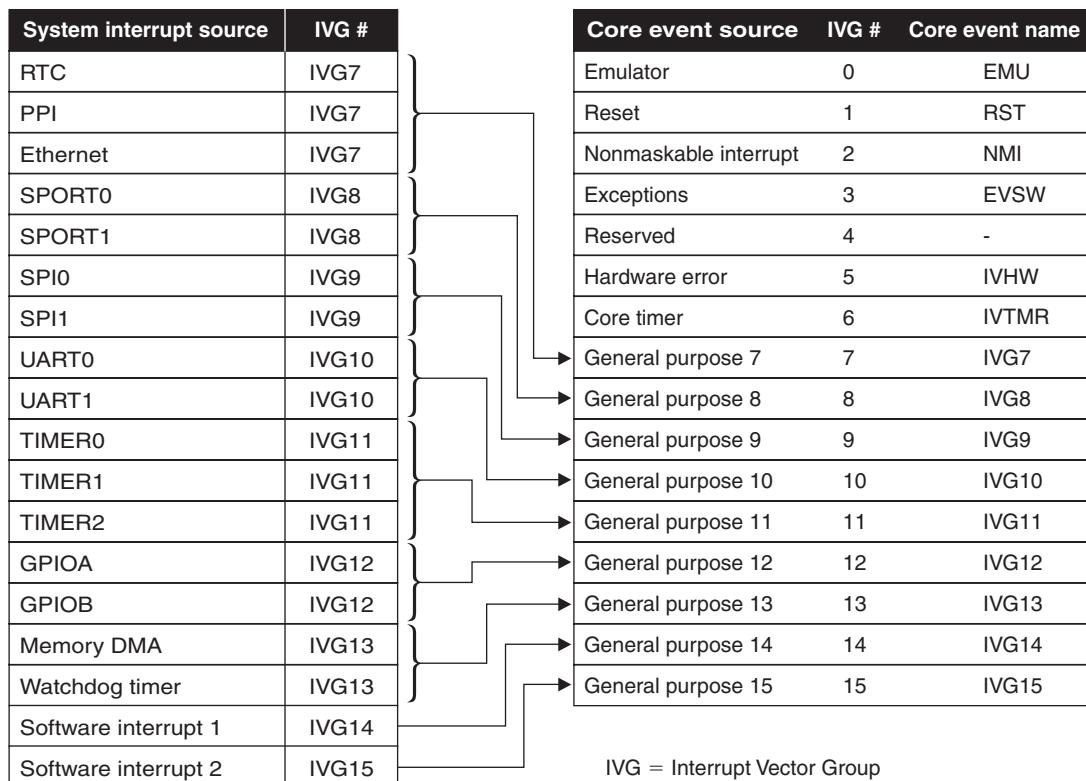

| 9.2                                                                | Event Generation and Handling .....                                                                          | 380        |

|      |                                                                   |            |

|------|-------------------------------------------------------------------|------------|

| 9.3  | Programming Methodology .....                                     | 384        |

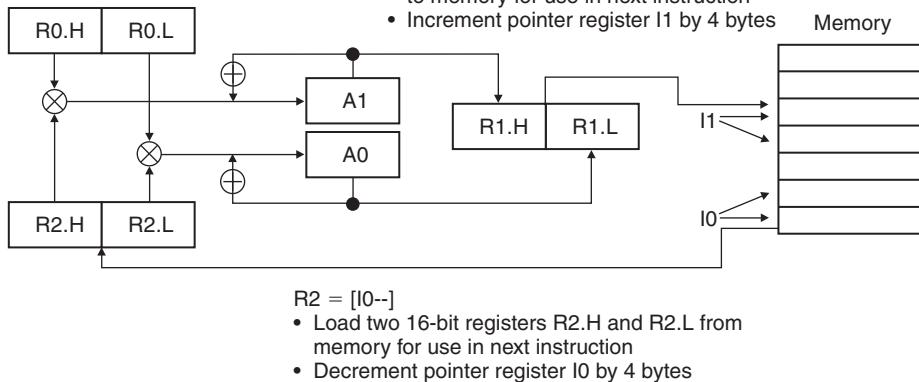

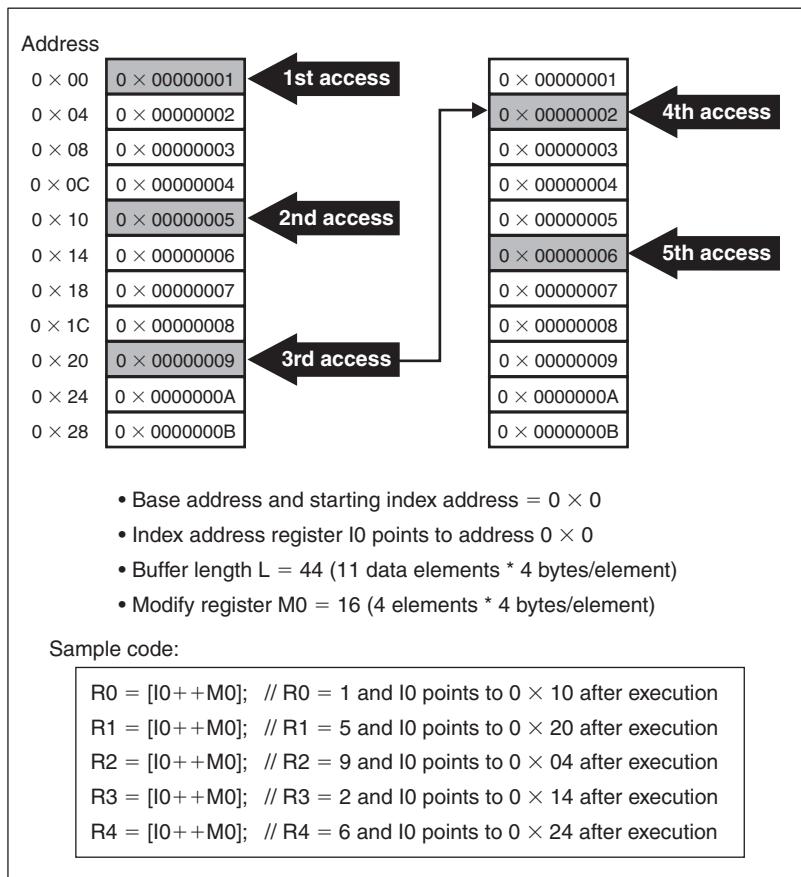

| 9.4  | Architectural Features for Efficient Programming.....             | 385        |

| 9.5  | Compiler Considerations for Efficient Programming .....           | 393        |

| 9.6  | System and Core Synchronization .....                             | 399        |

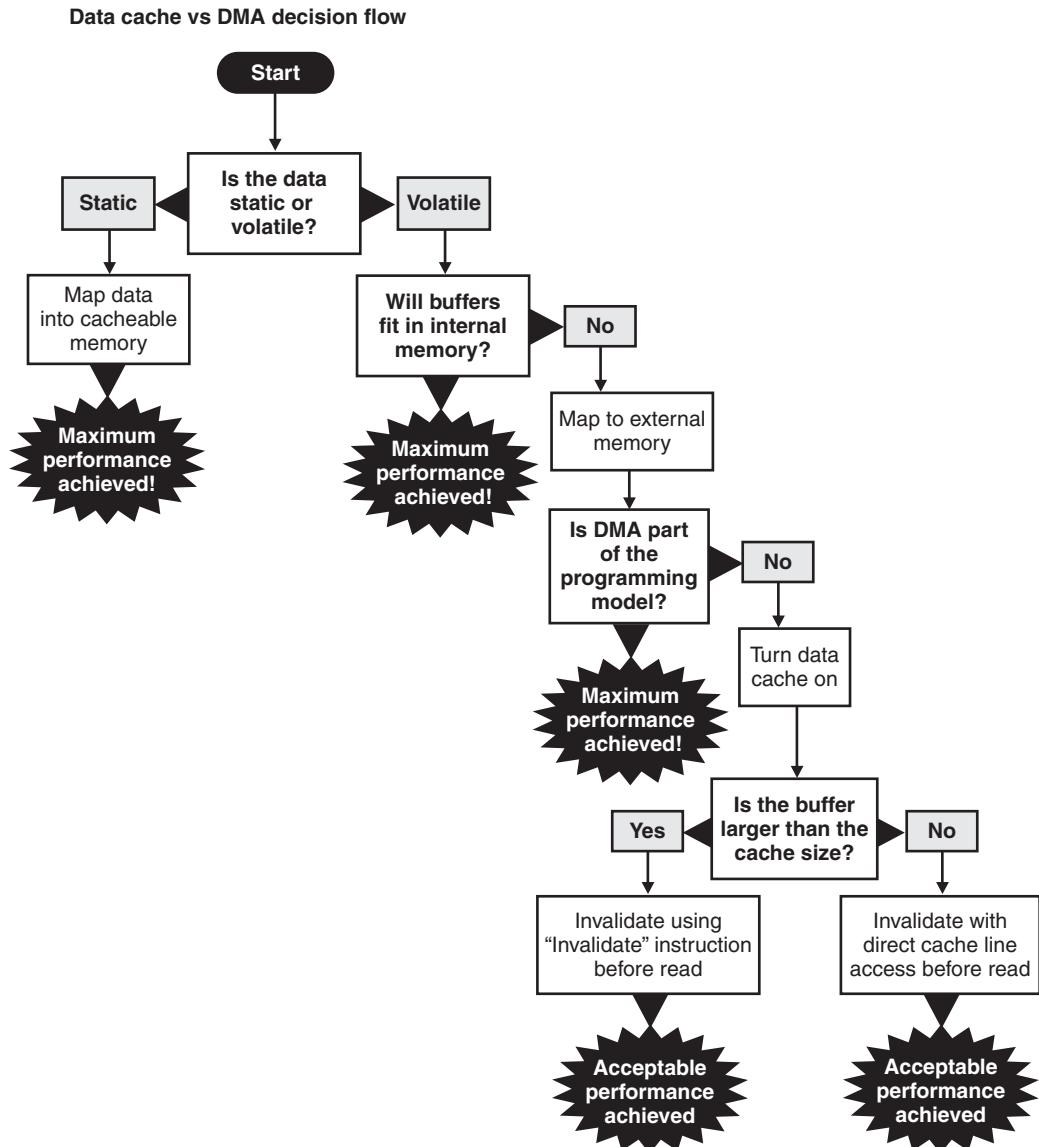

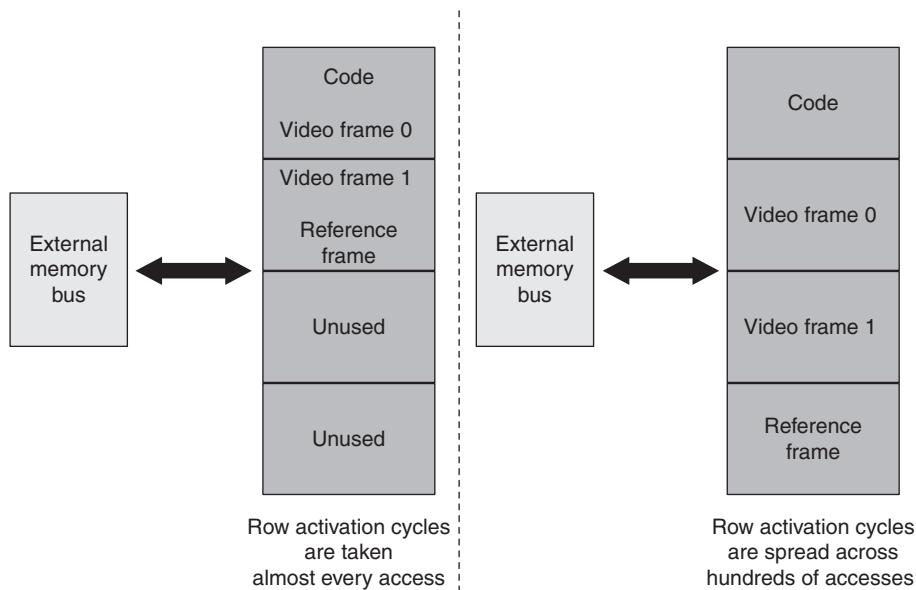

| 9.7  | Memory Architecture—the Need for Management.....                  | 403        |

| 9.8  | Physics of Data Movement .....                                    | 414        |

|      | Bibliography .....                                                | 421        |

|      | <b><i>Chapter 10: Testing and Debugging DSP Systems .....</i></b> | <b>423</b> |

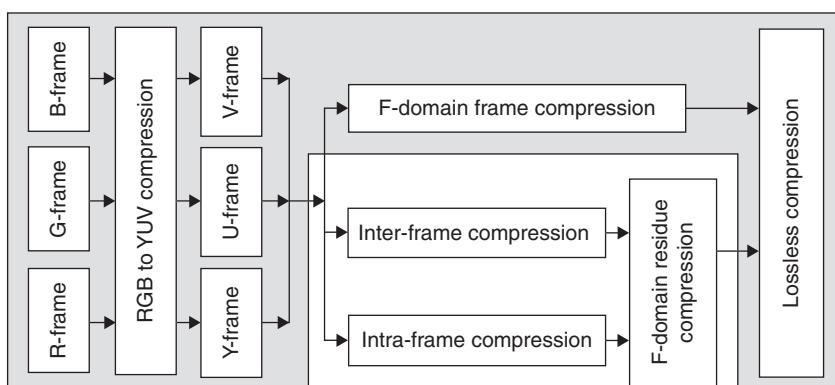

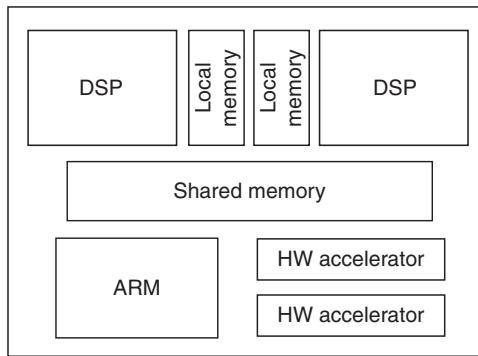

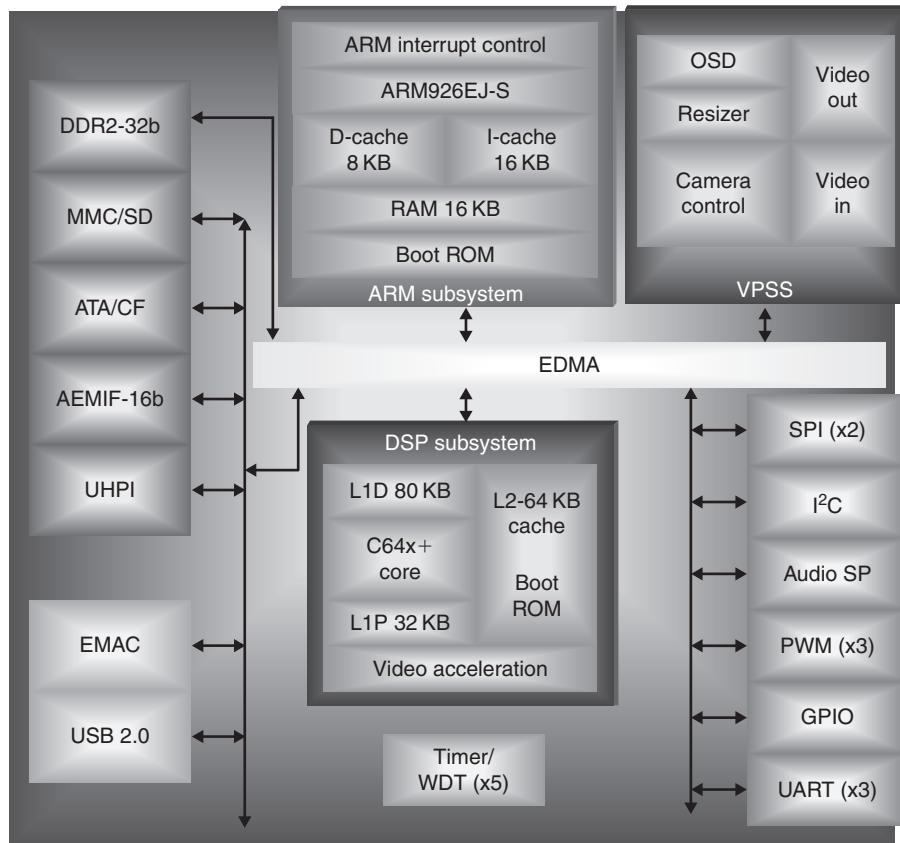

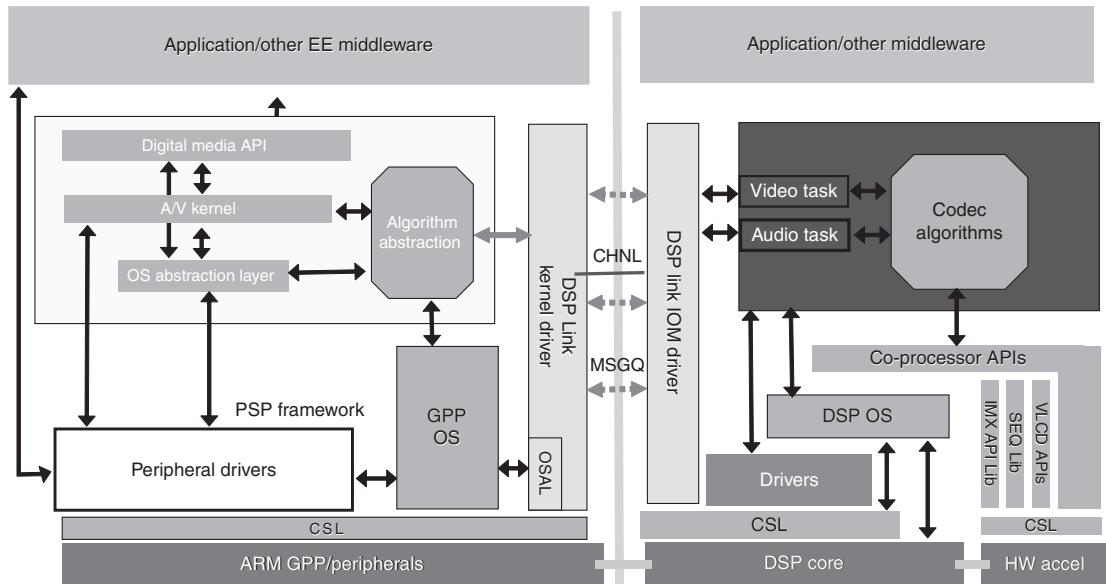

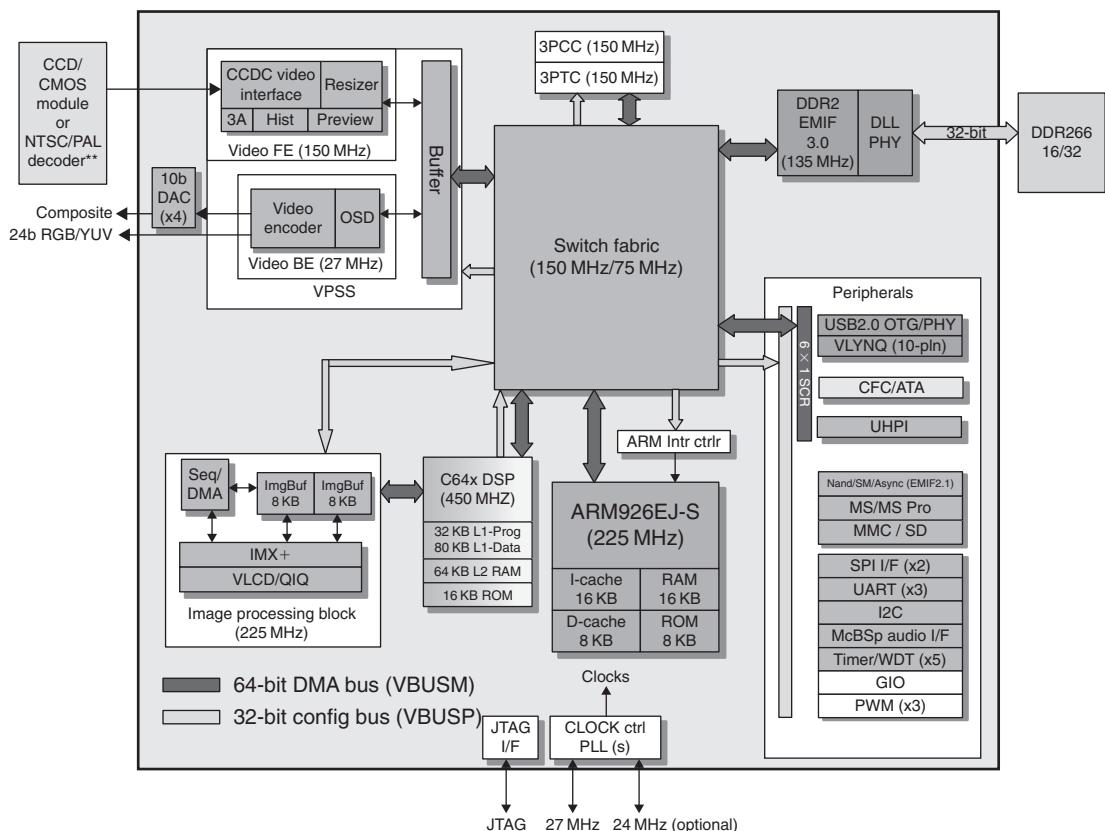

| 10.1 | Multicore System-on-a-Chip.....                                   | 423        |

| 10.2 | Software Architecture for SoC.....                                | 431        |

| 10.3 | SoC System Boot Sequence .....                                    | 435        |

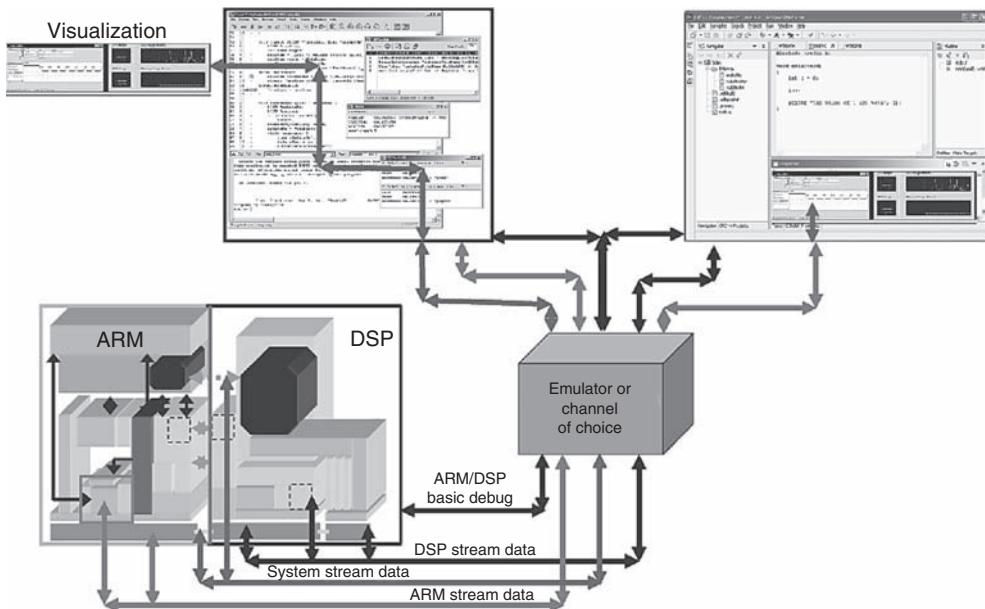

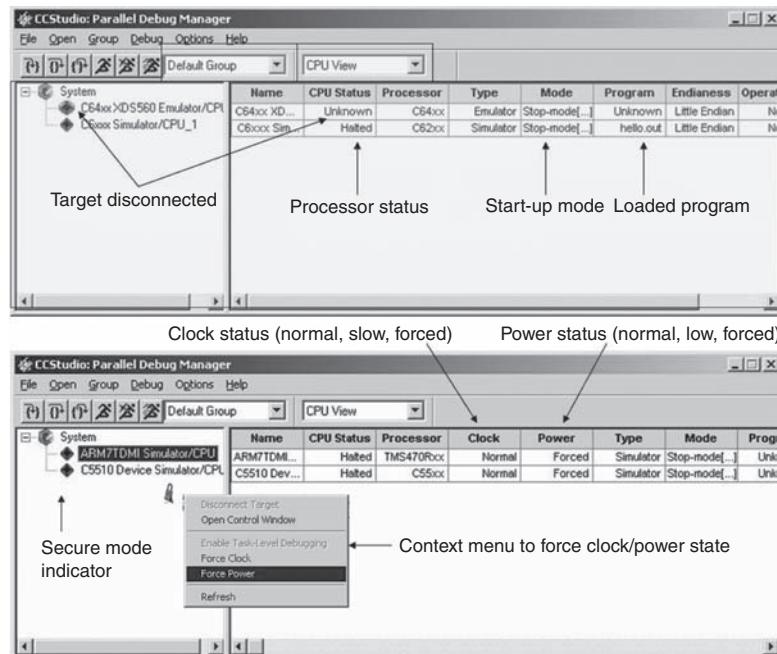

| 10.4 | Tools Support for SoC.....                                        | 436        |

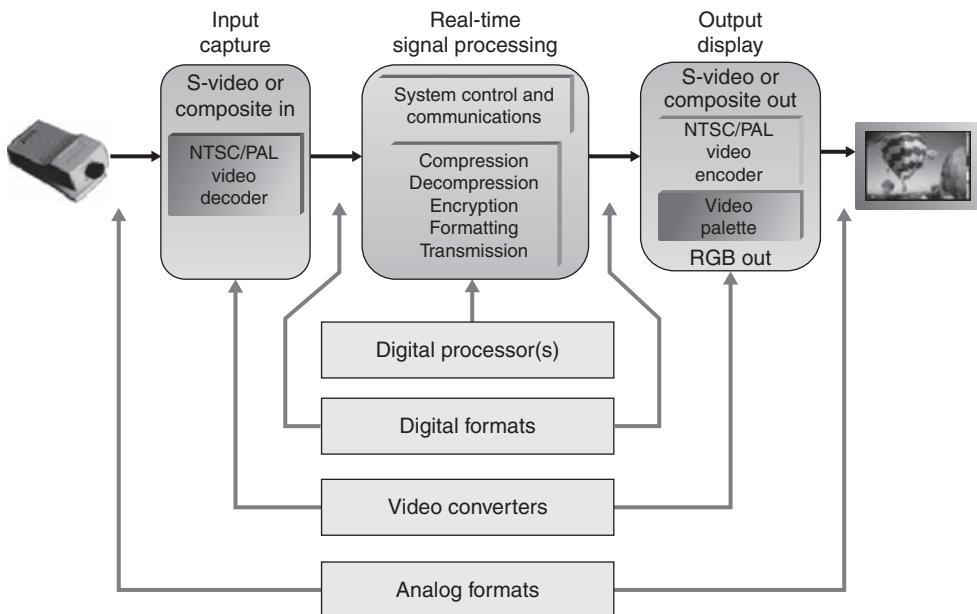

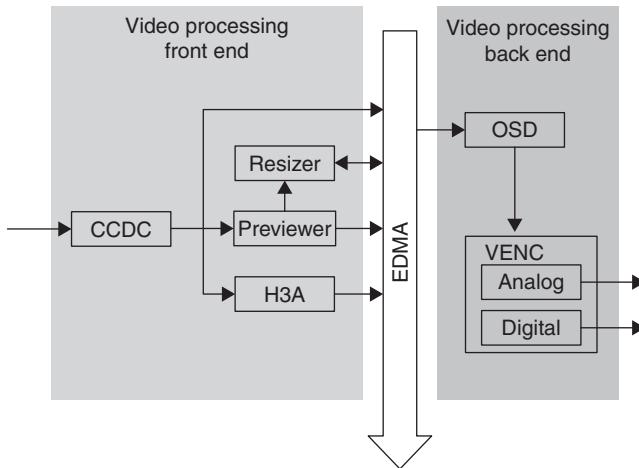

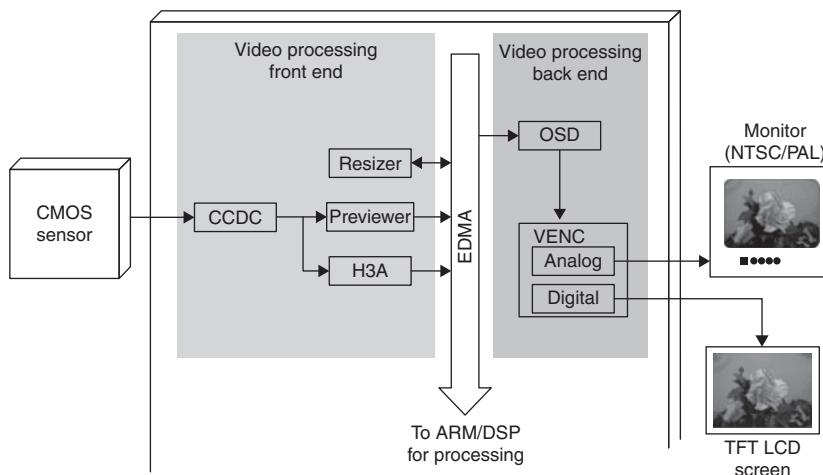

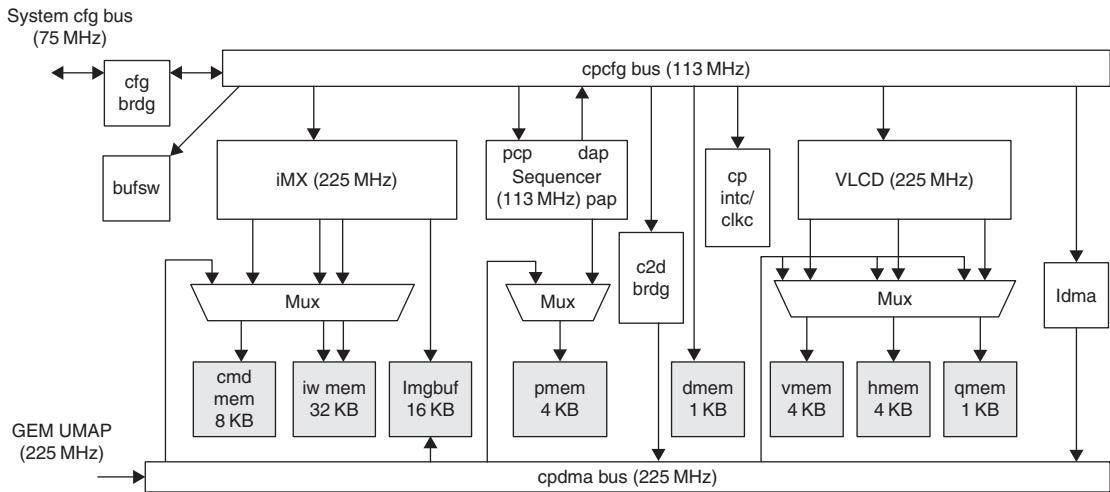

| 10.5 | A Video Processing Example of SoC .....                           | 437        |

|      | Bibliography .....                                                | 448        |

|      | <b><i>Index .....</i></b>                                         | <b>451</b> |

# *Preface*

What is this DSP thing I keep hearing about? What's so great about it? What do DSP engineers do? And how do I get in on the action? Great questions! Take a journey with me and all will be revealed...

## **Defining DSP**

First, let's figure out what DSP is. The acronym DSP has two alternate meanings: Digital Signal Processing and Digital Signal Processor. Let's look at each, starting with digital signal processing. The meaning of "digital" is obvious—it means we are working in the world of 1's and 0's, and not in the analog world. The idea of a "signal" is a bit trickier. Our friend Wikipedia defines the term as "any time-varying or spatial-varying quantity." Speech is an example of a time-varying quantity; the pitch and volume of a voice changes from one moment to the next. A photograph is an example of a space-varying quantity; the color and brightness of an image are different in different areas of the photo. Now we are left to define "processing." This is a broad concept, but it generally involves analysis and manipulation using mathematical algorithms. For example, we could analyze a voice recording to determine its pitch, and we could manipulate a photograph by adjusting its colors.

DSP applications fall into four main categories:

- Communications

- Audio, video, and imaging (sometimes referred to as media processing)

- Motion control

- Military and aerospace

Of these areas, communications and video receive the most attention. Both areas are evolving rapidly, and both impose high computational loads. In addition, both areas include systems with severely limited power budgets.

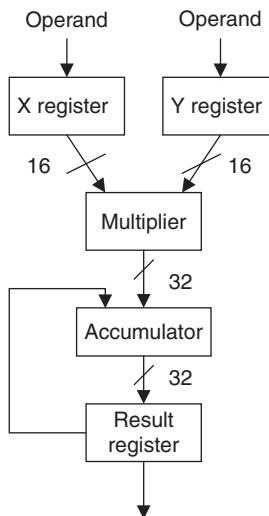

With this background, it's easy to define the term digital signal processor. A digital signal processor is a simply a processor with specialized features for signal processing. For example, many signal processing algorithms involve multiplication followed by addition, an operation

commonly referred to as a multiply accumulate or MAC. Since the MAC operation is so common in signal processing, all digital signal processors include special MAC hardware. As another example, many DSP applications have limited power budgets. Thus, many DSPs offer advanced power-saving features, such as the ability to change speeds and voltages on the fly—a feature known as dynamic frequency and voltage scaling.

It is important to note that digital signal *processing* does not require digital signal *processors*. Many signal processing systems use general-purpose processors (such as those available from ARM and MIPS) or custom hardware (built using ASICs and FPGAs). Many systems use a mix of hardware. For example, many systems contain both a DSP and a general-purpose processor (GPP).

## **The Role of the DSP Engineer**

So much for the basics. What do DSP engineers actually do? My friend Shiv Balakrishnan recently wrote an article on this topic, and I agree with his conclusion that DSP engineers typically fall into three categories:

1. System designers create algorithms and (in some cases) the overall system.

2. Hardware designers implement (1) in hardware.

3. Programmers implement (1) in software, either by using hardware created by (2) or by using off-the-shelf hardware.

This book is intended mainly for programmers. This is the most common role for DSP engineers, and the role that is easiest to address without getting into graduate-level concepts. Nonetheless, it is worth looking at each of these jobs in detail, and exploring the skill sets for each.

### ***System Designer***

The system designer focuses on the big picture. This engineer may design the overall functionality of the system, including all of the attendant algorithms, or they may focus on specific subsystems and algorithms. The latter case is common for products such as cell phones where the system complexity is too great for a single engineer.

The system designer is referred to as a domain expert because they need an expert understanding of the system requirements and how to meet them. This includes expertise on the analog world, because most DSP systems have analog inputs and outputs. For example, wireless system designers must know how signals degrade as they propagate through the air.

---

The system designer also needs top-notch algorithmic expertise. To meet these demands, the system designer often needs a master's degree or even a PhD.

The system designer builds a functional model of the system using graphical tools such as *Simulink* and *LabVIEW* as well as text-based tools like MATLAB and C. The system designer often does not get into the details of the hardware and software design, but they must understand the basics of these disciplines. Even the most brilliant design is worthless if no one can build it! System designers must also take great care to ensure that hardware designers and programmers fully understand the functional model. Among other things, this means that the system designer must provide a means of testing the hardware and software against the system model. To meet these goals, system designers are increasingly turning to Electronic System Level (ESL) tools. ESL tools perform a number of functions, including automatic generation of reference hardware and software, as well as generation of test vectors.

### ***Hardware Designer***

Once the system is designed, it's the hardware designer's turn. The role of the hardware designer varies widely. As with the system designer, the hardware designer may work on the entire system or may focus on specific subsystems. The hardware designer may create custom hardware, or they may build a system using off-the-shelf parts. For custom hardware, designers once turned to *ASICs*, but *ASIC* design has become prohibitively expensive for all but the highest-volume products. As a result, hardware designers often use *FPGAs* instead. *Structured ASICs* are also an option, particularly for medium-volume applications.

In any of these cases, the hardware designer realizes the hardware as a set of blocks. Traditionally, the designer would implement each block in hand-coded *RTL* (either *VHDL* or *Verilog*), verify it, and optimize it. While hand-coded *RTL* is still in use, hardware engineers increasingly rely on *ESL* tools to generate hardware. This is particularly true for key *DSP* algorithms like *FFTs* and *FIR* filters. *ESL* tools have become quite proficient at generating hardware for these algorithms. In addition to the custom-built blocks, most applications also include one or more programmable processors. The processors may be implemented inside an *ASIC* or *FPGA*, or the hardware designer may use off-the shelf processors.

For systems that use off-the-shelf hardware, the hardware designer's job is much simpler. However, the hardware designer still has to make many careful choices in order to meet the system requirements. The processors must have enough performance to handle the workload, the buses must have enough bandwidth to handle the data, and so on. In many cases, it is impossible to find off-the-shelf hardware that fully meets the system requirements, so the hardware designer must create a small amount of custom hardware.

For example, many systems use an FPGA to implement I/O that is not available in the off-the-shelf processor.

The upshot of all of this is that hardware designers need a variety of skills. Although ESL tools are lightening the workload, the hardware designer must have good RTL coding skills. Obviously, hardware designers must understand the algorithms they implement. They must also understand the requirements of the software so they can make wise design decisions. Although it is possible to meet all of these requirements with a bachelor's-level education, a master's degree is quite helpful.

### ***Programmer***

Next up: the programmer. The programmer writes code to implement the remaining functionality on the systems processor or processors. Like programmers in any other field, the DSP programmer generally writes in C/C++. However, DSP code is unusual for two reasons. First, DSP code often begins as a MATLAB or Simulink model. Thus, tools that convert *MATLAB to C* are drawing a great deal of interest. Second, DSP code requires heavy optimization for performance, size, and power. In many cases, this requires the programmer to optimize key sections of their code using assembly language. To achieve these extreme levels of optimization, the DSP engineer must be intimately familiar with the details of their hardware.

As mentioned earlier, many DSP systems include multiple processors. For example, many systems include both a GPP and a DSP. In recent years, multicore processors have also become commonplace. (*Multicore* processors combine two or more processor cores on a single chip.) Thus, multiprocessor programming is a critical skill for many DSP programmers.

Until recently, DSP programmers wrote most of their own software. Today, DSP programmers often use off-the-shelf software for large parts of the system. This is particularly true for speech- and media-processing *codecs*. These codecs have become highly standardized and commoditized.

Obviously, the programmer must understand the algorithms they implement. Programmers who use off-the-shelf DSP software only need to know the basics of the underlying algorithms. In either case, a bachelor's-level education is generally sufficient, but a master's-level education is helpful.

### ***DSP Project Flow***

So far we have described the three DSP roles as separate disciplines, but the three roles tend to overlap in practice. For example, a single engineer may fill all three roles in a smaller

project. It is also important to note that we have implied a linear project handoff from one discipline to the next. Projects rarely work this way in practice. Instead, most projects follow an iterative process with extensive feedback between the various roles. In addition, the system design, hardware design, and programming often proceed in parallel.

### ***The Future of DSP***

DSP was once a narrow, highly specialized field. Five years ago, DSP was nearly synonymous with telecom. If someone told you they were a DSP engineer, you had a good idea of what they did. You could be certain that they had good math skills and could explain exactly how a FIR filter works. Today, DSP is everywhere, often disguised under a moniker like “media processing.” Many of the engineers working on DSP systems have only a general understanding of the underlying algorithms. With all these changes, it is hard to clearly define exactly what a DSP engineer is, or what they do—and this confusion is likely to get worse as DSP diffuses into an ever-growing list of applications. However, one thing is certain: DSP engineering will remain an important and in-demand skill for many years to come.

This page intentionally left blank

## ***About the Editor***

**Kenton Williston** is the owner of Cabral Consulting. He has been writing about Digital Signal Processing (DSP) technology and business trends since 2001. Kenton is currently the editor of the *DSP DesignLine*, and he was previously the editor and the senior contributor for *Inside DSP*. He is an author of numerous technology reports, including the *Buyer's Guide to DSP Processors*. Kenton is a popular presenter at the Embedded Systems Conference and other venues, and he has advised the leading DSP semiconductor firms on their marketing and product-planning strategies.

In previous lives, Kenton has worked for a major telecommunications company, an engineering services firm, and (believe it or not) an oil company. Kenton received his degree in Electrical Engineering from the University of Missouri-Rolla.

This page intentionally left blank

# About the Contributors

**James Bryant** (Chapter 1) is a contributor to *Mixed Signal and DSP Design Techniques*.

**Rick Gentile** (Chapter 9) joined Analog Devices Inc. (ADI) in 2000 as a Senior DSP Applications Engineer. He currently leads the Applications Engineering Group, where he is responsible for applications engineering work on the Blackfin, SHARC and TigerSHARC processors. Prior to joining ADI, Rick was a Member of the Technical Staff at MIT Lincoln Laboratory, where he designed several signal processors used in a wide range of radar sensors. He received a B.S. in 1987 from the University of Massachusetts at Amherst and an M.S. in 1994 from Northeastern University, both in Electrical and Computer Engineering.

**Keith Jack** (Chapter 5) is Director of Product Marketing at Sigma Designs, a leading supplier of high-performance System-on-Chip (SoC) solutions for the IPTV, Blu-ray, and HDTV markets. Previously, he was Director of Product Marketing at Innovision, focused on solutions for digital televisions. Mr. Jack has also served as Strategic Marketing Manager at Harris Semiconductor and Brooktree Corporation. He has architected and introduced to market over 35 multimedia SoCs for the consumer markets, and is the author of “Video Demystified”.

**David Katz** (Chapter 9) has over 15 years of experience in circuit and system design. Currently, he is Blackfin Applications Manager at Analog Devices, Inc., where he focuses on specifying new processors. He has published over 100 embedded processing articles domestically and internationally, and he has presented several conference papers in the field. Additionally, he is co-author of *Embedded Media Processing* (Newnes 2005). Previously, he worked at Motorola, Inc., as a senior design engineer in cable modem and automation groups. David holds both a B.S. and M. Eng. in Electrical Engineering from Cornell University.

**Nasser Kehtarnavaz** (Chapter 3) is the author of *Digital Signal Processing System Design* and *Real-Time Digital Signal Processing*.

**Walt Kester** (Chapter 1) is a corporate staff applications engineer at Analog Devices. For over 35 years at Analog Devices, he has designed, developed, and given applications support for high-speed ADCs, DACs, SHAs, op amps, and analog multiplexers. Besides writing many papers and articles, he prepared and edited eleven major applications books which form the basis for the Analog Devices world-wide technical seminar series including the topics of op amps, data conversion, power management, sensor signal conditioning, mixed-signal, and practical analog design techniques. He also is the editor of *The Data Conversion Handbook*,

a 900+ page comprehensive book on data conversion published in 2005 by Elsevier. Walt has a BSEE from NC State University and MSEE from Duke University.

**Dake Liu** (Chapter 7) is a Professor and the Director of the Computer Engineering Division in the Department of Electrical Engineering at Linköping University, Linköping, Sweden. His research focuses on architectures of application specific instruction set processors (ASIP) and on-chip multi-core integrations based on VLSI. His research goal is to explore different processor architectures and inter-processor architectures and parallel programming for DSP firmware. On the processor level, his research focus is on integrated DSP-MCU solution based on homogeneous instruction set and heterogeneous architecture. On ILP (Instruction Level Parallelism) level research, his current focus is on architecture and toolchain for template based programming, especially for conflict free parallel memory accesses. On CMP (on Chip Multi Processor) level research, his current focus is on flexible low latency and low silicon cost system for real-time computing. Applications behind his research are embedded DSP computing, communications, and media signal processing. He published about 100 papers on international journals and reviewed conferences.

**Robert Meddins** (Chapter 2) is the author of *Introduction to Digital Signal Processing*.

**Robert Oshana** (Chapter 10) has over 25 years of experience in embedded and real-time systems and DSP systems development. He has numerous articles and books in this area. He is a member of the Embedded Systems Advisory board and speaks frequently at Embedded Systems Conferences worldwide. Rob is a senior member of IEEE, a licensed professional engineer (PE), and an adjunct professor at Southern Methodist University.

**Ian Poole** (Chapter 6) is an established electronics engineering consultant with considerable experience in the communications and cellular markets. He is the author of a number of books on radio and electronics and he has contributed to many magazines in the UK and worldwide. He is also winner of the inaugural Bill Orr Award for technical writing from the ARRL.

**Khalid Sayood** (Chapter 4) received his BS and MS in Electrical Engineering from the University of Rochester in 1977 and 1979, respectively, and his Ph.D. in Electrical Engineering from Texas A&M University in 1982. In 1982, he joined the University of Nebraska, where he is the Henson Professor of Engineering. His research interests include data compression, joint source channel coding, and bioinformatics.

**Dan Sheingold** (Chapter 1) is a contributor to *Mixed Signal and DSP Design Techniques*.

**Li Tan** (Chapter 8) is a Senior Professor and Curriculum Coordinator in Electronics Engineering Technology at DeVry University.

# ADCs, DACs, and Sampling Theory

Walt Kester

Dan Sheingold

James Bryant

*A chapter on analog? What's this doing in a DSP book? And at the very front of the book, no less!*

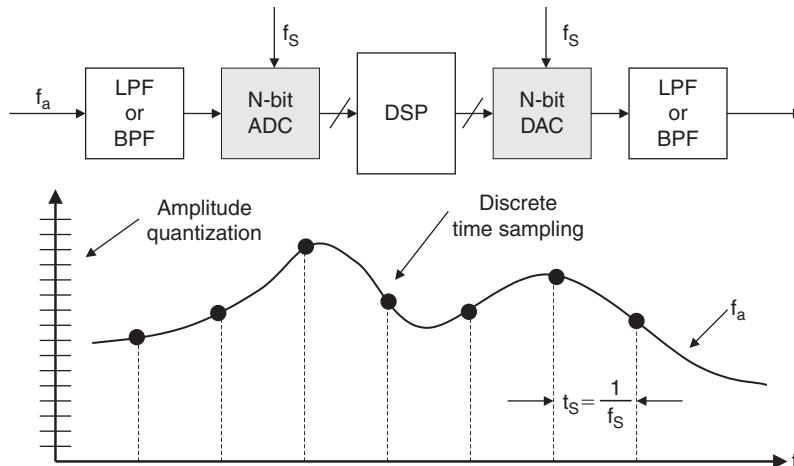

*Relax. You don't need to be an analog expert to do DSP. However, a little analog knowledge is a big help! Nearly all DSP systems have analog inputs. Before we can manipulate this analog data, we need to pass it through an analog-to-digital converter (ADC). This conversion process is always flawed—the digital data cannot capture the analog signal with perfect precision. ADCs also change the data by adding noise and distortion. What's worse, ADCs present the possibility of aliasing—a phenomenon where two signals that are obviously different in the analog world become indistinguishable in the digital world.*

*Things are just as bad on the output side. Most DSP systems have analog outputs, so we have to pipe the output through digital-to-analog converters (DACs). DACs cannot reproduce our digital signal with perfect precision—they always introduce noise and distortion.*

*If all of this sounds frightening, don't worry. As long as you understand the limitations of ADCs and DACs, these limitations are usually easy to manage. This chapter by Walt Kester will help you do just that. The author explains the principles behind ADCs and DACs, including the all-important Nyquist sampling theorem. He explains the basic operation of ADCs and DACs, and shows how even "ideal" ADCs and DACs introduce errors. He then goes on to explain the flaws of real-world ADCs and DACs.*

*The information in this chapter will be more than enough for most DSP engineers. If you want to dive deeper, I heartily recommend these series:*

*ADCs for DSP*

<http://www.dspdesignline.com/howto/202200877>

*DACs for DSP*

<http://www.dspdesignline.com/howto/205601725>

—Kenton Williston

## 1.1 Coding and Quantizing

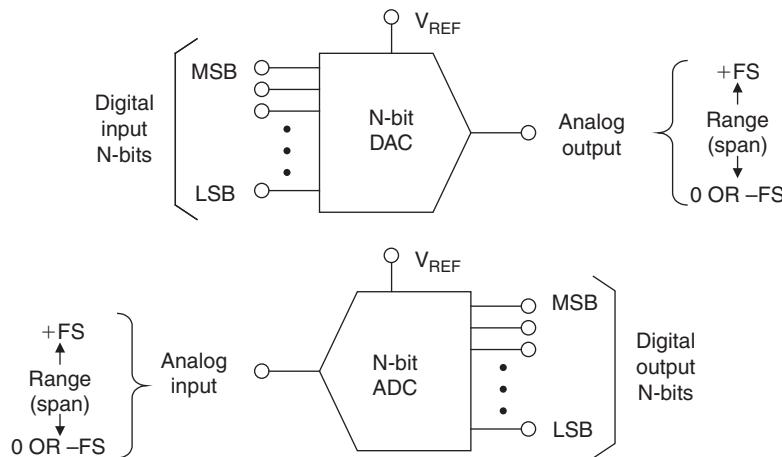

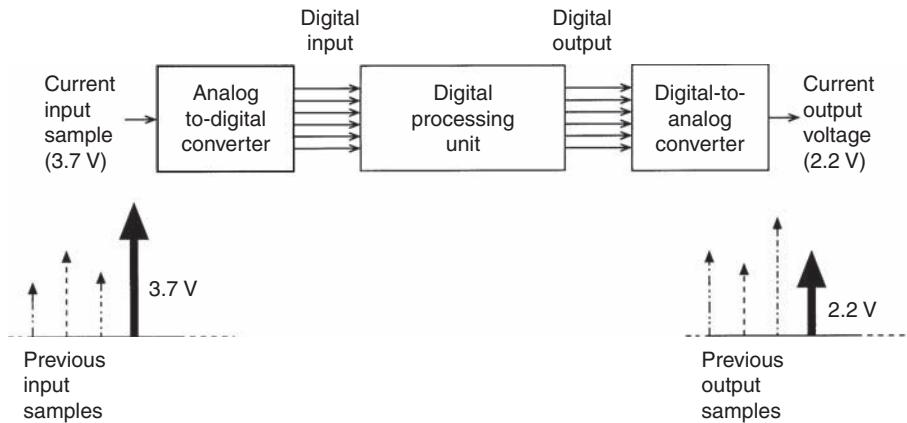

Analog-to-digital converters (ADCs) translate analog quantities, which are characteristic of most phenomena in the “real world,” to digital language, used in information processing, computing, data transmission, and control systems. Digital-to-analog converters (DACs) are used in transforming transmitted or stored data, or the results of digital processing, back to “real-world” variables for control, information display, or further analog processing. The relationships between inputs and outputs of DACs and ADCs are shown in Figure 1.1.

Analog input variables, whatever their origin, are most frequently converted by transducers into voltages or currents. These electrical quantities may appear (1) as fast or slow “DC” continuous direct measurements of a phenomenon in the time domain, (2) as modulated AC waveforms (using a wide variety of modulation techniques), (3) or in some combination, with a spatial configuration of related variables to represent shaft angles. Examples of the first are outputs of thermocouples, potentiometers on DC references, and analog computing circuitry; of the second, “chopped” optical measurements, AC strain gage or bridge outputs, and digital signals buried in noise; and of the third, synchros and resolvers.

The analog variables to be dealt with in this chapter are those involving voltages or currents representing the actual analog phenomena. They may be either wideband or narrowband. They may be either scaled from the direct measurement, or subjected to some form of analog preprocessing, such as linearization, combination, demodulation, filtering, sample-hold, etc.

**Figure 1.1: Digital-to-analog converter (DAC) and analog-to-digital converter (ADC) input and output definitions**

As part of the process, the voltages and currents are “normalized” to ranges compatible with assigned ADC input ranges. Analog output voltages or currents from DACs are direct and in normalized form, but they may be subsequently post-processed (e.g., scaled, filtered, amplified, etc.).

Information in digital form is normally represented by arbitrarily fixed voltage levels referred to “ground,” either occurring at the outputs of logic gates, or applied to their inputs. The digital numbers used are all basically binary; that is, each “bit,” or unit of information has one of two possible states. These states are “off,” “false,” or “0,” and “on,” “true,” or “1.” It is also possible to represent the two logic states by two different levels of current; however, this is much less popular than using voltages. There is also no particular reason why the voltages need be referenced to ground—as in the case of emitter-coupled-logic (ECL), positive-emitter-coupled-logic (PECL) or low-voltage-differential-signaling logic (LVDS) for example.

*Words* are groups of levels representing digital numbers; the levels may appear simultaneously in *parallel*, on a bus or groups of gate inputs or outputs, *serially* (or in a time sequence) on a single line, or as a sequence of parallel bytes (i.e., “byte-serial”) or nibbles (small bytes). For example, a 16-bit word may occupy the 16 bits of a 16-bit bus, or it may be divided into two sequential bytes for an 8-bit bus, or four 4-bit nibbles for a 4-bit bus.

Although there are several systems of logic, the most widely used choice of levels are those used in TTL (transistor-transistor logic) and, in which *true*, or 1, corresponds to a minimum output level of 2.4 V (inputs respond unequivocally to “1” for levels greater than 2.0 V); and *false*, or 0, corresponds to a maximum output level of 0.4 V (inputs respond unequivocally to “0” for anything less than 0.8 V). It should be noted that even though CMOS is more popular today than TTL, CMOS logic levels are generally made to be compatible with the older TTL logic standard.

A unique parallel or serial grouping of digital levels, or a *number*, or *code*, is assigned to each analog level which is quantized (i.e., represents a unique portion of the analog range).

A typical digital code would be this array:

$$a_7a_6a_5a_4a_3a_2a_1 = 10111001$$

It is composed of 8 bits. The “1” at the extreme left is called the *most significant bit* (MSB, or bit 1), and the one at the right is called the *least significant bit* (LSB, or bit  $N$ : 8 in this case). The meaning of the code, as either a number, a character, or a representation of an analog variable, is unknown until the *code* and the *conversion relationship* have been defined. It is important not to confuse the designation of a particular bit (i.e., bit 1, bit 2, and so on) with the subscripts associated with the “a” array. The subscripts correspond to the power of 2 associated with the weight of a particular bit in the sequence.

The best-known code (other than base-10) is *natural or straight binary* (base-2). Binary codes are most familiar in representing integers; i.e., in a natural binary integer code having  $N$  bits, the LSB has a weight of  $2^0$  (i.e., 1), the next bit has a weight of  $2^1$  (i.e., 2), and so on up to the MSB, which has a weight of  $2^{N-1}$  (i.e.,  $2^N/2$ ). The value of a binary number is obtained by adding up the weights of all non-zero bits. When the weighted bits are added up, they form a unique number having any value from 0 to  $2^N - 1$ . Each additional trailing zero bit, if present, essentially doubles the size of the number.

In converter technology, full-scale (abbreviated *FS*) is independent of the number of bits of resolution,  $N$ . A more useful coding is *fractional* binary, which is always normalized to full-scale. Integer binary can be interpreted as fractional binary if all integer values are divided by  $2^N$ . For example, the MSB has a weight of  $1/2$  (i.e.,  $2^{(N-1)}/2^N = 2^{-1}$ ), the next bit has a weight of  $1/4$  (i.e.,  $2^{-2}$ ), and so forth down to the LSB, which has a weight of  $1/2^N$  (i.e.,  $2^{-N}$ ). When the weighted bits are added up, they form a number with any of  $2^N$  values, from 0 to  $(1-2^{-N})$  of full-scale. Additional bits simply provide more fine structure without affecting full-scale range. The relationship between base-10 numbers and binary numbers (base-2) are shown in Figure 1.2 along with examples of each.

### 1.1.1 Unipolar Codes

In data conversion systems, the coding method must be related to the analog input range (or span) of an ADC or the analog output range (or span) of a DAC. The simplest case is when the input to the ADC or the output of the DAC is always a unipolar positive voltage (current outputs are very popular for DAC outputs, much less for ADC inputs). The most popular

## Whole numbers

$$\text{Number}_{10} = a_{N-1}2^{N-1} + a_{N-2}2^{N-2} + \dots + a_12^1 + a_02^0$$

MSB

↑

158

$$\begin{aligned}\text{Example: } 1011_2 &= (1 \times 2^3) + (0 \times 2^2) + (1 \times 2^1) + (1 \times 2^0) \\ &= 8 + 0 + 2 + 1 = 11_{10}\end{aligned}$$

## Fractional numbers:

$$\begin{aligned}\text{Example: } 0.1011_2 &= (1 \times 0.5) + (0 \times 0.25) + (1 \times 0.125) + (1 \times 0.0625) \\ &= 0.5 + 0 + 0.125 + 0.0625 = 0.6875_{10}\end{aligned}$$

Figure 1.2: Representing a base-10 number with a binary number (base-2)

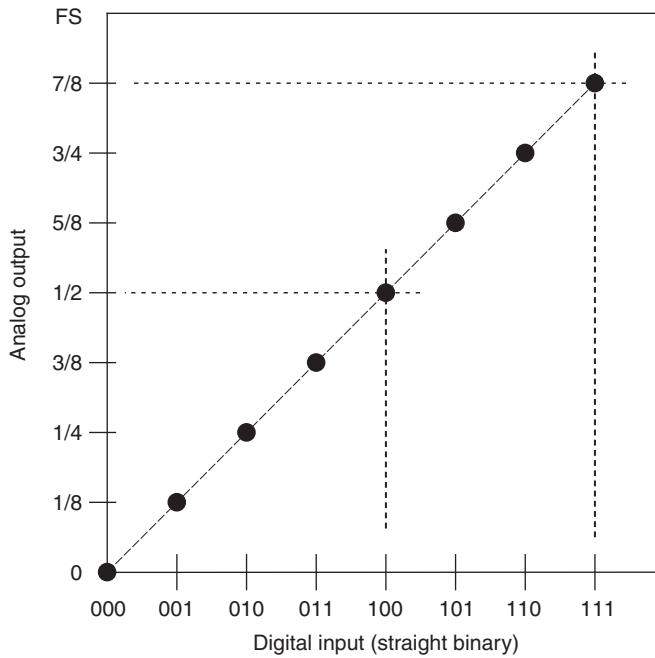

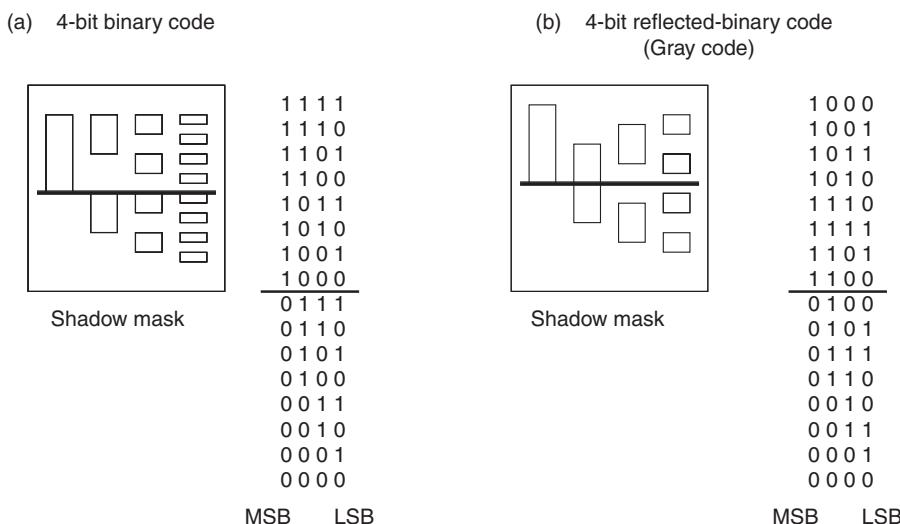

code for this type of signal is *straight binary* and is shown in Figure 1.3 for a 4-bit converter. Notice that there are 16 distinct possible levels, ranging from the all-zeros code 0000, to the all-ones code 1111. It is important to note that the analog value represented by the all-ones code is not full-scale (abbreviated FS), but FS – 1 LSB. This is a common convention in data conversion notation and applies to both ADCs and DACs. Figure 1.3 gives the base-10 equivalent number, the value of the base-2 binary code relative to full-scale (FS), and also the corresponding voltage level for each code (assuming a 10V full-scale converter). The Gray code equivalent is also shown, and will be discussed shortly.

Figure 1.4 shows the transfer function for an ideal 3-bit DAC with straight binary input coding. Notice that the analog output is zero for the all-zeros input code. As the digital input code increases, the analog output increases 1 LSB (1/8 scale in this example) per code. The most positive output voltage is 7/8 FS, corresponding to a value equal to FS – 1 LSB. The midscale output of 1/2 FS is generated when the digital input code is 100.

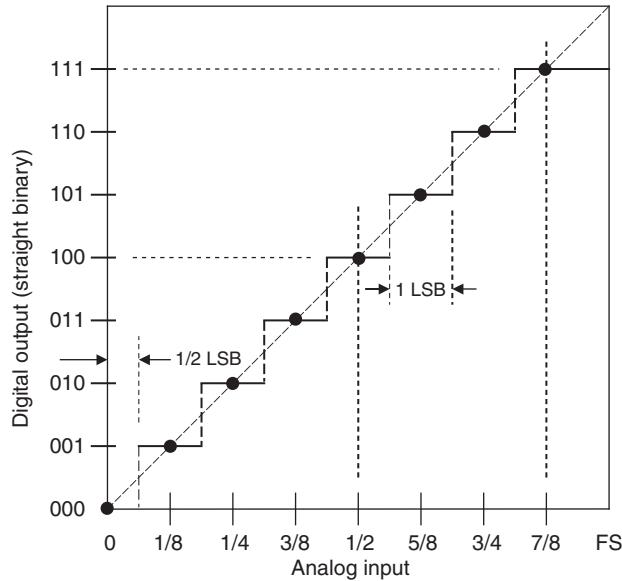

The transfer function of an ideal 3-bit ADC is shown in Figure 1.5. There is a range of analog input voltage over which the ADC will produce a given output code; this range is the *quantization uncertainty* and is equal to 1 LSB. Note that the width of the transition regions between adjacent codes is zero for an ideal ADC. In practice, however, there is always transition noise associated with these levels, and therefore the width is non-zero. It is customary to define the analog input corresponding to a given code by the *code center* which lies halfway between two adjacent transition regions (illustrated by the black dots in the

| Base 10 number | Scale                  | +10V FS | Binary  | Gray    |

|----------------|------------------------|---------|---------|---------|

| +15            | +FS – 1LSB = +15/16 FS | 9.375   | 1 1 1 1 | 1 0 0 0 |

| +14            | +7/8 FS                | 8.750   | 1 1 1 0 | 1 0 0 1 |

| +13            | +13/16 FS              | 8.125   | 1 1 0 1 | 1 0 1 1 |

| +12            | +3/4 FS                | 7.500   | 1 1 0 0 | 1 0 1 0 |

| +11            | +11/16 FS              | 6.875   | 1 0 1 1 | 1 1 1 0 |

| +10            | +5/8 FS                | 6.250   | 1 0 1 0 | 1 1 1 1 |

| +9             | +9/16 FS               | 5.625   | 1 0 0 1 | 1 1 0 1 |

| +8             | +1/2 FS                | 5.000   | 1 0 0 0 | 1 1 0 0 |

| +7             | +7/16 FS               | 4.375   | 0 1 1 1 | 0 1 0 0 |

| +6             | +3/8 FS                | 3.750   | 0 1 1 0 | 0 1 0 1 |

| +5             | +5/16 FS               | 3.125   | 0 1 0 1 | 0 1 1 1 |

| +4             | +1/4 FS                | 2.500   | 0 1 0 0 | 0 1 1 0 |

| +3             | +3/16 FS               | 1.875   | 0 0 1 1 | 0 0 1 0 |

| +2             | +1/8 FS                | 1.250   | 0 0 1 0 | 0 0 1 1 |

| +1             | 1LSB = +1/16 FS        | 0.625   | 0 0 0 1 | 0 0 0 1 |

| 0              |                        | 0.000   | 0 0 0 0 | 0 0 0 0 |

Figure 1.3: Unipolar binary codes, 4-bit converter

Figure 1.4: Transfer function for ideal unipolar 3-bit DAC

Figure 1.5: Transfer function for ideal unipolar 3-bit ADC

diagram). This requires that the first transition region occur at  $\frac{1}{2}$  LSB. The full-scale analog input voltage is defined by  $7/8$  FS, (FS – 1 LSB).

### 1.1.2 Gray Code

Another code worth mentioning at this point is the *Gray* code (or *reflective-binary*), which was invented by Elisha Gray in 1878 (Reference 1) and later re-invented by Frank Gray in 1949 (see Reference 2). The Gray code equivalent of the 4-bit straight binary code is also shown in Figure 1.3. Although it is rarely used in computer arithmetic, it has some useful properties which make it attractive to A/D conversion. Notice that in Gray code, as the number value changes, the transitions from one code to the next involve only one bit at a time. Contrast this to the binary code where all the bits change when making the transition between 0111 and 1000. Some ADCs make use of it internally and then convert the Gray code to a binary code for external use.

One of the earliest practical ADCs to use the Gray code was a 7-bit, 100kSPS electron beam encoder developed by Bell Labs and described in a 1948 reference (Reference 3).

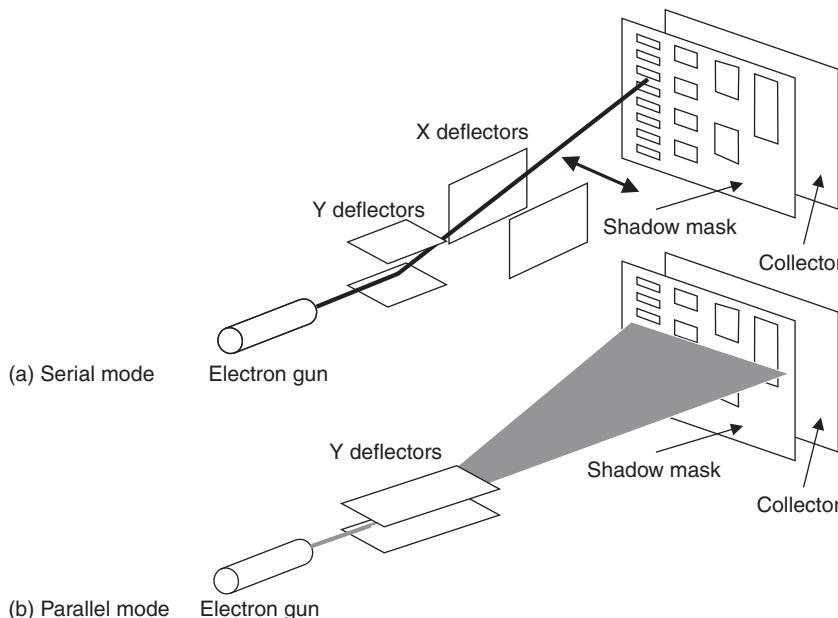

The basic electron beam coder concepts for a 4-bit device are shown in Figure 1.6. The early tubes operated in the serial mode (a). The analog signal is first passed through

Figure 1.6: The electron beam coder: (a) serial mode and (b) parallel or “Flash” mode

a sample-and-hold, and during the “hold” interval, the beam is swept horizontally across the tube. The Y-deflection for a single sweep therefore corresponds to the value of the analog signal from the sample-and-hold. The shadow mask is coded to produce the proper binary code, depending on the vertical deflection. The code is registered by the collector, and the bits are generated in serial format. Later tubes used a fan-shaped beam (shown in Figure 1.6b), creating a “Flash” converter delivering a parallel output word.

Early electron tube coders used a binary-coded shadow mask, and large errors can occur if the beam straddles two adjacent codes and illuminates both of them. The way these errors occur is illustrated in Figure 1.7a, where the horizontal line represents the beam sweep at the midscale transition point (transition between code 0111 and code 1000). For example, an error in the most significant bit (MSB) produces an error of  $\frac{1}{2}$  scale. These errors were minimized by placing fine horizontal sensing wires across the boundaries of each of the quantization levels. If the beam initially fell on one of the wires, a small voltage was added to the vertical deflection voltage which moved the beam away from the transition region.

The errors associated with binary shadow masks were eliminated by using a Gray code shadow mask as shown in Figure 1.7b. As mentioned above, the Gray code has the property that adjacent levels differ by only one digit in the corresponding Gray-coded word. Therefore, if there is an error in a bit decision for a particular level, the corresponding error after conversion to binary code is only one least significant bit (LSB). In the case of midscale, note that only the MSB changes. It is interesting to note that this same phenomenon can

Figure 1.7: Electron beam coder shadow masks for (a) binary code and (b) Gray code

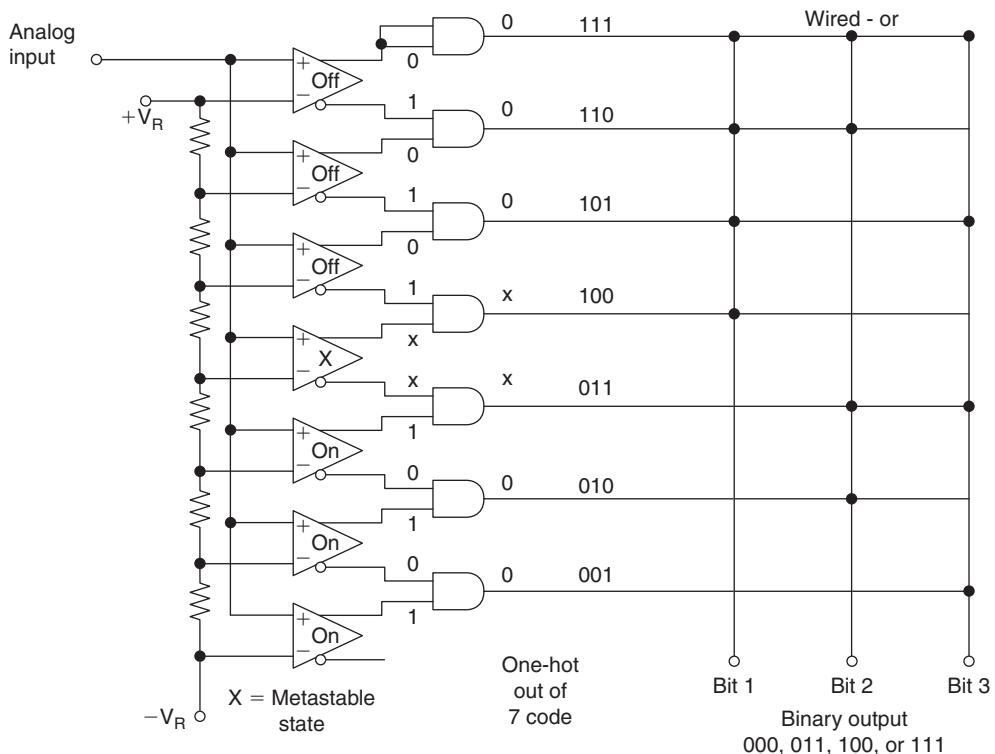

occur in modern comparator-based Flash converters due to comparator metastability. With small overdrive, there is a finite probability that the output of a comparator will generate the wrong decision in its latched output, producing the same effect if straight binary decoding techniques are used. In many cases, Gray code, or “pseudo-Gray” codes are used to decode the comparator bank. The Gray code output is then latched, converted to binary, and latched again at the final output.

As a historical note, in spite of the many mechanical and electrical problems relating to beam alignment, electron tube coding technology reached its peak in the mid-1960s with an experimental 9-bit coder capable of 12 MSPS sampling rates (Reference 4). Shortly thereafter, however, advances in all solid-state ADC techniques made the electron tube technology obsolete.

Other examples where Gray code is often used in the conversion process to minimize errors are shaft encoders (angle-to-digital) and optical encoders.

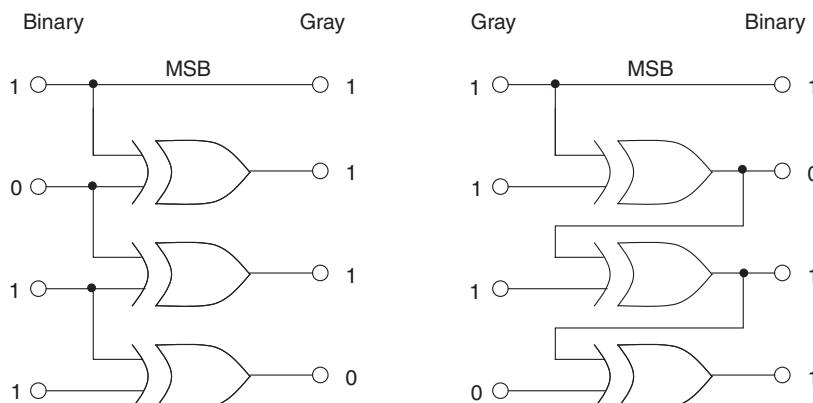

ADCs that use the Gray code internally almost always convert the Gray code output to binary for external use. The conversion from Gray-to-binary and binary-to-Gray is easily accomplished with the exclusive-or logic function as shown in Figure 1.8.

### 1.1.3 Bipolar Codes

In many systems, it is desirable to represent both positive and negative analog quantities with binary codes. Either *offset binary*, *two's complement*, *one's complement*, or *sign magnitude* codes will accomplish this, but offset binary and two's complement are by far the most

**Figure 1.8: Binary-to-Gray and Gray-to-binary conversion using the exclusive-or logic function**

| Base 10 number | Scale                | $\pm 5V$ FS | Offset binary | Twos comp. | Ones comp. | Sign mag. |

|----------------|----------------------|-------------|---------------|------------|------------|-----------|

| +7             | +FS - 1LSB = +7/8 FS | +4.375      | 1111          | 0111       | 0111       | 0111      |

| +6             | +3/4 FS              | +3.750      | 1110          | 0110       | 0110       | 0110      |

| +5             | +5/8 FS              | +3.125      | 1101          | 0101       | 0101       | 0101      |

| +4             | +1/2 FS              | +2.500      | 1100          | 0100       | 0100       | 0100      |

| +3             | +3/8 FS              | +1.875      | 1011          | 0011       | 0011       | 0011      |

| +2             | +1/4 FS              | +1.250      | 1010          | 0010       | 0010       | 0010      |

| +1             | +1/8 FS              | +0.625      | 1001          | 0001       | 0001       | 0001      |

| 0              | 0                    | 0.000       | 1000          | 0000       | *0000      | *1000     |

| -1             | -1/8 FS              | -0.625      | 0111          | 1111       | 1110       | 1001      |

| -2             | -1/4 FS              | -1.250      | 0110          | 1110       | 1101       | 1010      |

| -3             | -3/8 FS              | -1.875      | 0101          | 1101       | 1100       | 1011      |

| -4             | -1/2 FS              | -2.500      | 0100          | 1100       | 1011       | 1100      |

| -5             | -5/8 FS              | -3.125      | 0011          | 1011       | 1010       | 1101      |

| -6             | -3/4 FS              | -3.750      | 0010          | 1010       | 1001       | 1110      |

| -7             | -FS + 1LSB = -7/8 FS | -4.375      | 0001          | 1001       | 1000       | 1111...   |

| -8             | -FS                  | -5.000      | 0000          | 1000       |            |           |

Not normally used

in computations (see text)

\*    0+ 0000 0000

0- 1111 1000

Figure 1.9: Bipolar codes, 4-bit converter

popular. The relationships between these codes for a 4-bit system is shown in Figure 1.9. Note that the values are scaled for a  $\pm 5V$  full-scale input/output voltage range.

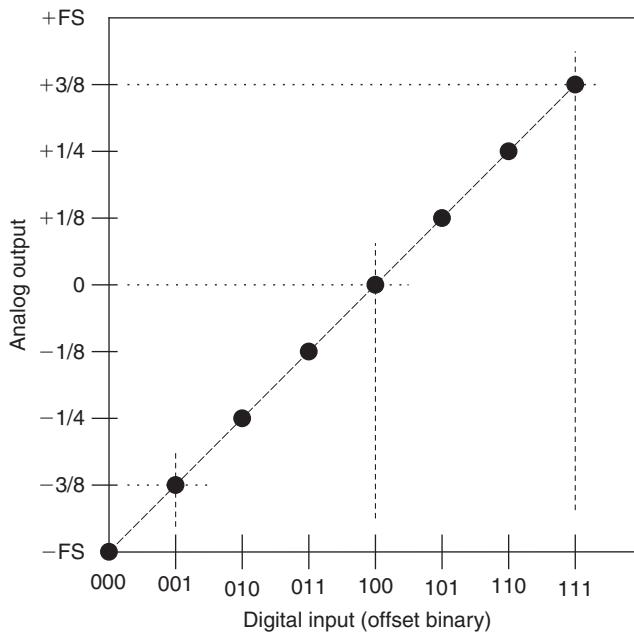

For *offset binary*, the zero signal value is assigned the code 1000. The sequence of codes is identical to that of straight binary.

The only difference between a straight and offset binary system is the half-scale offset associated with analog signal. The most negative value ( $-FS + 1$  LSB) is assigned the code 0001, and the most positive value ( $+FS - 1$  LSB) is assigned the code 1111. Note that in order to maintain perfect symmetry about midscale, the all-zeros code (0000) representing negative full-scale ( $-FS$ ) is not normally used in computation. It can be used to represent a negative off-range condition or simply assigned the value of the 0001 ( $-FS + 1$  LSB).

The relationship between the offset binary code and the analog output range of a bipolar 3-bit DAC is shown in Figure 1.10. The analog output of the DAC is zero for the zero-value input code 100. The most negative output voltage is generally defined by the 001 code ( $-FS + 1$  LSB), and the most positive by 111 ( $+FS - 1$  LSB). The output voltage for the 000 input code is available for use if desired, but makes the output nonsymmetrical about zero and complicates the mathematics.

Figure 1.10: Transfer function for ideal bipolar 3-bit DAC

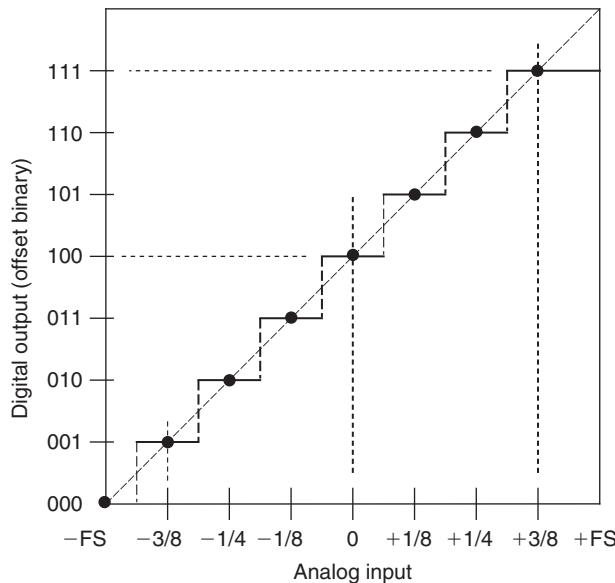

The offset binary output code for a bipolar 3-bit ADC as a function of its analog input is shown in Figure 1.11. Note that zero analog input defines the center of the midscale code 100. As in the case of bipolar DACs, the most negative input voltage is generally defined by the 001 code ( $-FS + 1$  LSB), and the most positive by 111 ( $+FS - 1$  LSB). As discussed above, the 000 output code is available for use if desired, but makes the output nonsymmetrical about zero and complicates the mathematics.

*Two's complement* is identical to offset binary with the most-significant-bit (MSB) complemented (inverted). This is obviously very easy to accomplish in a data converter, using a simple inverter or taking the complementary output of a “D” flip-flop. The popularity of two's complement coding lies in the ease with which mathematical operations can be performed in computers and DSPs. Two's complement, for conversion purposes, consists of a binary code for positive magnitudes (0 sign bit), and the two's complement of each positive number to represent its negative. The two's complement is formed arithmetically by complementing the number and adding 1 LSB. For example,  $-3/8$  FS is obtained by taking the two's complement of  $+3/8$  FS. This is done by first complementing  $+3/8$  FS, 0011, obtaining 1100. Adding 1 LSB, we obtain 1101.

Figure 1.11: Transfer function for ideal bipolar 3-bit ADC

Two's complement makes subtraction easy. For example, to subtract  $3/8$  FS from  $4/8$  FS, add  $4/8$  to  $-3/8$ , or 0100 to 1101. The result is 0001, or  $1/8$ , disregarding the extra carry.

*One's complement* can also be used to represent negative numbers, although it is much less popular than two's complement and rarely used today. The one's complement is obtained by simply complementing all of a positive number's digits. For instance, the one's complement of  $3/8$  FS (0011) is 1100. A one's complemented code can be formed by complementing each positive value to obtain its corresponding negative value. This includes zero, which is then represented by either of two codes, 0000 (referred to as  $0+$ ) or 1111 (referred to as  $0-$ ). This ambiguity must be dealt with mathematically, and presents obvious problems relating to ADCs and DACs for which there is a single code that represents zero.

*Sign-magnitude* would appear to be the most straightforward way of expressing signed analog quantities digitally. Simply determine the code appropriate for the magnitude and add a polarity bit. Sign-magnitude BCD is popular in bipolar digital voltmeters, but has the problem of two allowable codes for zero. It is therefore unpopular for most applications involving ADCs or DACs.

Figure 1.12 summarizes the relationships between the various bipolar codes: offset binary, two's complement, one's complement, and sign-magnitude, and shows how to convert between them.

| To convert from<br>To | Sign magnitude                                                      | Two's complement                               | Offset binary                                                        | One's complement                              |

|-----------------------|---------------------------------------------------------------------|------------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------|

| Sign magnitude        | No change                                                           | If MSB = 1, complement other bits, add 00...01 | Complement MSB<br>If new MSB = 1, complement other bits, add 00...01 | If MSB = 1, complement other bits             |

| Two's complement      | If MSB = 1, complement other bits, add 00...01                      | No Change                                      | Complement MSB                                                       | If MSB = 1, add 00...01                       |

| Offset binary         | Complement MSB<br>If new MSB = 0 complement other bits, add 00...01 | Complement MSB                                 | No change                                                            | Complement MSB<br>If new MSB = 0, add 00...01 |

| One's complement      | If MSB = 1, complement other bits                                   | If MSB = 1, add 11...11                        | Complement MSB<br>If new MSB = 1, add 11...11                        | No change                                     |

Figure 1.12: Relationships among bipolar codes

The last code to be considered in this section is *binary-coded decimal (BCD)*, where each base-10 digit (0 to 9) in a decimal number is represented as the corresponding 4-bit straight binary word as shown in Figure 1.13. The minimum digit 0 is represented as 0000, and the digit 9 by 1001. This code is relatively inefficient, since only 10 of the 16 code states for each decade are used. It is, however, a very useful code for interfacing to decimal displays such as in digital voltmeters.

#### 1.1.4 Complementary Codes

Some forms of data converters (for example, early DACs using monolithic NPN quad current switches), require standard codes such as natural binary or BCD, but with all bits represented by their complements. Such codes are called *complementary codes*. All the codes discussed thus far have complementary codes which can be obtained by this method. A *complementary* code should not be confused with a *one's complement* or a *two's complement* code.

In a 4-bit complementary-binary converter, 0 is represented by 1111, half-scale by 0111, and FS – 1 LSB by 0000. In practice, the complementary code can usually be obtained by using the complementary output of a register rather than the true output, since both are available.

| Base 10 number | Scale                  | +10V FS | Decade 1 | Decade 2 | Decade 3 | Decade 4 |

|----------------|------------------------|---------|----------|----------|----------|----------|

| +15            | +FS - 1LSB = +15/16 FS | 9.375   | 1 001    | 0 011    | 0 111    | 0 101    |

| +14            | +7/8 FS                | 8.750   | 1 000    | 0 111    | 0 101    | 0 000    |

| +13            | +13/16 FS              | 8.125   | 1 000    | 0 001    | 0 010    | 0 101    |

| +12            | +3/4 FS                | 7.500   | 0 111    | 0 101    | 0 000    | 0 000    |

| +11            | +11/16 FS              | 6.875   | 0 110    | 1 000    | 0 111    | 0 101    |

| +10            | +5/8 FS                | 6.250   | 0 110    | 0 010    | 0 101    | 0 000    |

| +9             | +9/16 FS               | 5.625   | 0 101    | 0 110    | 0 010    | 0 101    |

| +8             | +1/2 FS                | 5.000   | 0 101    | 0 000    | 0 000    | 0 000    |

| +7             | +7/16 FS               | 4.375   | 0 100    | 0 011    | 0 111    | 0 101    |

| +6             | +3/8 FS                | 3.750   | 0 011    | 0 111    | 0 101    | 0 000    |

| +5             | +5/16 FS               | 3.125   | 0 011    | 0 001    | 0 010    | 0 101    |

| +4             | +1/4 FS                | 2.500   | 0 010    | 0 101    | 0 000    | 0 000    |

| +3             | +3/16 FS               | 1.875   | 0 001    | 1 000    | 0 111    | 0 101    |

| +2             | +1/8 FS                | 1.250   | 0 001    | 0 010    | 0 101    | 0 000    |

| +1             | 1LSB = +1/16 FS        | 0.625   | 0 000    | 0 110    | 0 010    | 0 101    |

| 0              |                        | 0.000   | 0 000    | 0 000    | 0 000    | 0 000    |

Figure 1.13: Binary-coded decimal (BCD) code

Sometimes the complementary code is useful in inverting the analog output of a DAC. Today many DACs provide differential outputs which allow the polarity inversion to be accomplished without modifying the input code. Similarly, many ADCs provide differential logic inputs which can be used to accomplish the polarity inversion.

### 1.1.5 DAC and ADC Static Transfer Functions and DC Errors

The most important thing to remember about both DACs and ADCs is that either the input or output is digital, and therefore the signal is quantized. That is, an N-bit word represents one of  $2^N$  possible states, and therefore an N-bit DAC (with a fixed reference) can have only  $2^N$  possible analog outputs, and an N-bit ADC can have only  $2^N$  possible digital outputs. As previously discussed, the analog signals will generally be voltages or currents.

The resolution of data converters may be expressed in several different ways: the weight of the least significant bit (LSB), parts per million of full-scale (ppm FS), millivolts (mV), etc. Different devices (even from the same manufacturer) will be specified differently, so converter users must learn to translate between the different types of specifications if they are to compare devices successfully. The size of the least significant bit for various resolutions is shown in Figure 1.14.

Before we can consider the various architectures used in data converters, it is necessary to consider the performance to be expected, and the specifications which are important. The

| Resolution N | $2^N$      | Voltage (10V FS)          | ppm FS  | % FS     | dB FS |

|--------------|------------|---------------------------|---------|----------|-------|

| 2-bit        | 4          | 2.5 V                     | 250,000 | 25       | -12   |

| 4-bit        | 16         | 625 mV                    | 62,500  | 6.25     | -24   |

| 6-bit        | 64         | 156 mV                    | 15,625  | 1.56     | -36   |

| 8-bit        | 256        | 39.1 mV                   | 3,906   | 0.39     | -48   |

| 10-bit       | 1,024      | 9.77 mV (10 mV)           | 977     | 0.098    | -60   |

| 12-bit       | 4,096      | 2.44 mV                   | 244     | 0.024    | -72   |

| 14-bit       | 16,384     | 610 $\mu$ V               | 61      | 0.0061   | -84   |

| 16-bit       | 65,536     | 153 $\mu$ V               | 15      | 0.0015   | -96   |

| 18-bit       | 262,144    | 38 $\mu$ V                | 4       | 0.0004   | -108  |

| 20-bit       | 1,048,576  | 9.54 $\mu$ V (10 $\mu$ V) | 1       | 0.0001   | -120  |

| 22-bit       | 4,194,304  | 2.38 $\mu$ V              | 0.24    | 0.000024 | -132  |

| 24-bit       | 16,777,216 | 596 $\mu$ V*              | 0.06    | 0.000006 | -144  |

\*600nV is the Johnson Noise in a 10 kHz BW of a 2.2k $\Omega$  Resistor @ 25°C

Remember: 10 bits and 10V FS yields an LSB of 10 mV, 1000 ppm, or 0.1%.

all other values may be calculated by powers of 2.

**Figure 1.14: Quantization: the size of a least significant bit (LSB)**

following sections will consider the definition of errors and specifications used for data converters. This is important in understanding the strengths and weaknesses of different ADC/DAC architectures.

The first applications of data converters were in measurement and control where the exact timing of the conversion was usually unimportant, and the data rate was slow. In such applications, the DC specifications of converters are important, but timing and AC specifications are not. Today many, if not most, converters are used in *sampling* and *reconstruction* systems where AC specifications are critical (and DC ones may not be)—these will be considered in Section 1.3 of this chapter.

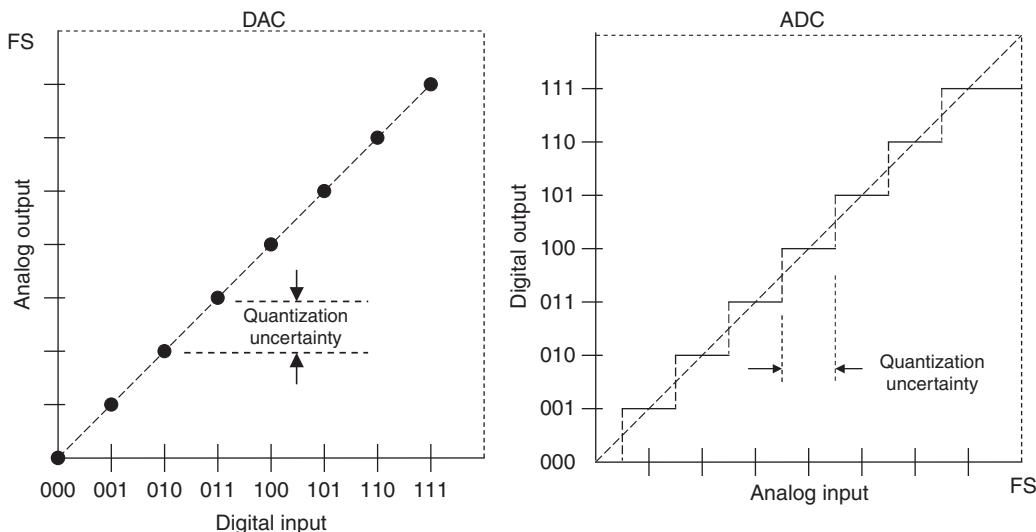

Figure 1.15 shows the ideal transfer characteristics for a 3-bit unipolar DAC and a 3-bit unipolar ADC. In a DAC, both the input and the output are quantized, and the graph consists of eight points. While it is reasonable to discuss the line through these points, it is very important to remember that the actual transfer characteristic is *not* a line, but a number of discrete points.

The input to an ADC is analog and is not quantized, but its output is quantized. The transfer characteristic therefore consists of eight horizontal steps. When considering the offset, gain

Figure 1.15: Transfer functions for ideal 3-bit DAC and ADC

and linearity of an ADC we consider the line joining the midpoints of these steps—often referred to as the *code centers*.

For both DACs and ADCs, digital full-scale (all “1”s) corresponds to 1 LSB below the analog full-scale (FS). The (ideal) ADC transitions take place at  $\frac{1}{2}$  LSB above zero, and thereafter every LSB, until  $\frac{1}{2}$  LSB below analog full-scale. Since the analog input to an ADC can take any value, but the digital output is quantized, there may be a difference of up to  $\frac{1}{2}$  LSB between the actual analog input and the exact value of the digital output. This is known as the *quantization error* or *quantization uncertainty* as shown in Figure 1.15. In AC (sampling) applications this quantization error gives rise to *quantization noise* which will be discussed in Section 1.3 of this chapter.

As previously discussed, there are many possible digital coding schemes for data converters: *straight binary*, *offset binary*, *one’s complement*, *two’s complement*, *sign magnitude*, *Gray code*, *BCD*, and others. This section, being devoted mainly to the *analog* issues surrounding data converters, will use simple *binary* and *offset binary* in its examples and will not consider the merits and disadvantages of these, or any other forms of digital code.

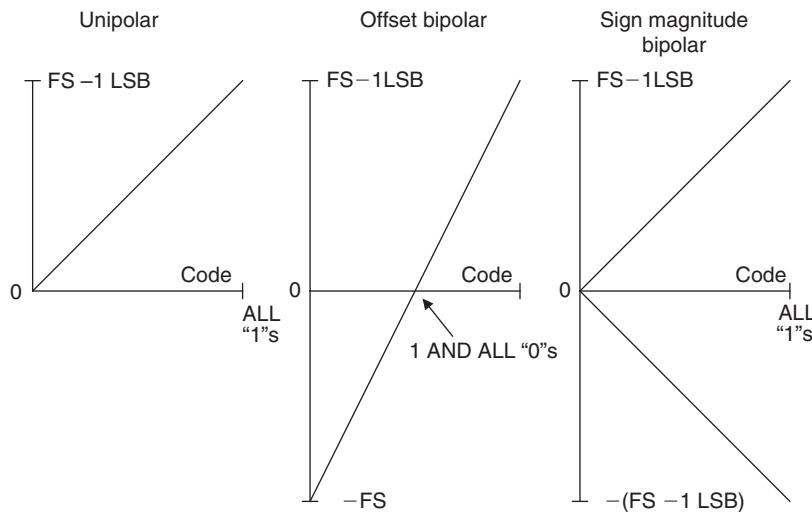

The examples in Figure 1.15 use *unipolar* converters, whose analog port has only a single polarity. These are the simplest type, but *bipolar* converters are generally more useful in real-world applications. There are two types of bipolar converters: the simpler is merely a unipolar converter with an accurate 1 MSB of negative offset (and many converters are arranged

Figure 1.16: Unipolar and bipolar converters

so that this offset may be switched in and out so that they can be used as either unipolar or bipolar converters at will), but the other, known as a *sign-magnitude* converter is more complex, and has  $N$  bits of magnitude information and an additional bit which corresponds to the sign of the analog signal.

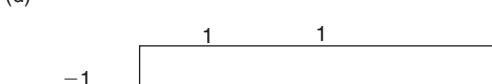

Sign-magnitude DACs are quite rare, and sign-magnitude ADCs are found mostly in digital voltmeters (DVMs). The unipolar, offset binary, and sign-magnitude representations are shown in Figure 1.16.

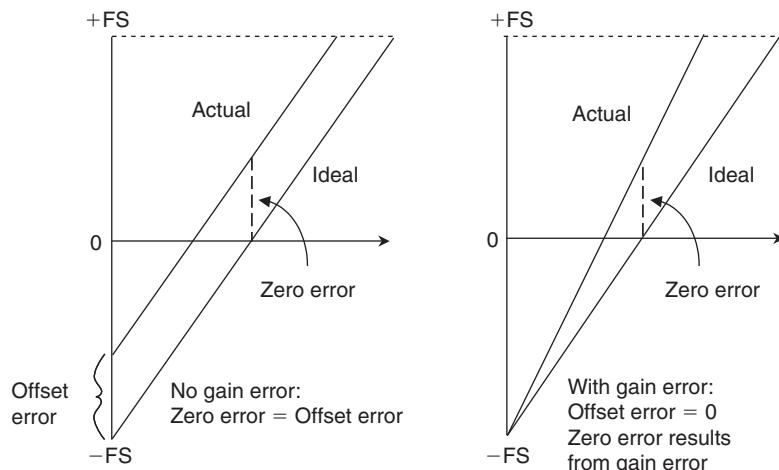

The four DC errors in a data converter are *offset error*, *gain error*, and two types of *linearity error (differential and integral)*. Offset and gain errors are analogous to offset and gain errors in amplifiers as shown in Figure 1.17 for a bipolar input range. (Though offset error and zero error, which are identical in amplifiers and unipolar data converters, are not identical in bipolar converters and should be carefully distinguished.)

The transfer characteristics of both DACs and ADCs may be expressed as a straight line given by  $D = K + GA$ , where  $D$  is the digital code,  $A$  is the analog signal, and  $K$  and  $G$  are constants. In a unipolar converter, the ideal value of  $K$  is zero; in an offset bipolar converter it is  $-1$  MSB. The offset error is the amount by which the actual value of  $K$  differs from its ideal value.

The gain error is the amount by which  $G$  differs from its ideal value, and is generally expressed as the percentage difference between the two, although it may be defined as the gain error contribution (in mV or LSB) to the total error at full scale. These errors can usually

be trimmed by the data converter user. Note, however, that amplifier offset is trimmed at zero input, and then the gain is trimmed near to full scale. The trim algorithm for a bipolar data converter is not so straightforward.

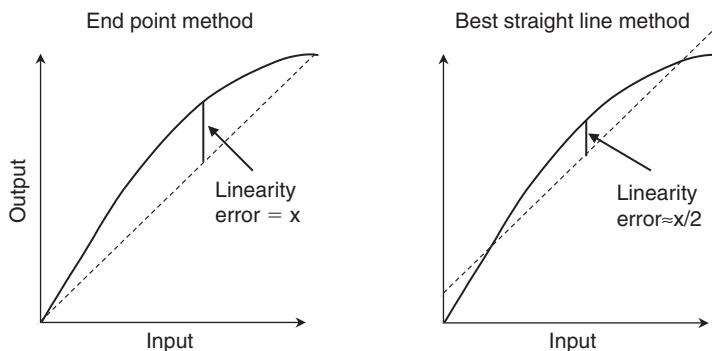

The integral linearity error of a converter is also analogous to the linearity error of an amplifier, and is defined as the maximum deviation of the actual transfer characteristic of the converter from a straight line, and is generally expressed as a percentage of full scale (but may be given in LSBs). For an ADC, the most popular convention is to draw the straight line through the mid-points of the codes, or the code centers. There are two common ways of choosing the straight line: *end point* and *best straight line* as shown in Figure 1.18.

Figure 1.17: Bipolar data converter offset and gain error

Figure 1.18: Method of measuring integral linearity errors (same converter on both graphs)

In the *end point* system, the deviation is measured from the straight line through the origin and the full-scale point (after gain adjustment). This is the most useful integral linearity measurement for measurement and control applications of data converters (since error budgets depend on deviation from the ideal transfer characteristic, not from some arbitrary “best fit”), and is the one normally adopted by Analog Devices, Inc.

However, the *best straight line* does give a better prediction of distortion in AC applications, and also gives a lower value of “linearity error” on a data sheet. The best fit straight line is drawn through the transfer characteristic of the device using standard curve-fitting techniques, and the maximum deviation is measured from this line. In general, the integral linearity error measured in this way is only 50% of the value measured by end point methods. This makes the method good for producing impressive data sheets, but it is less useful for error budget analysis. For AC applications it is better to specify distortion than DC linearity, so it is rarely necessary to use the best straight line method to define converter linearity.

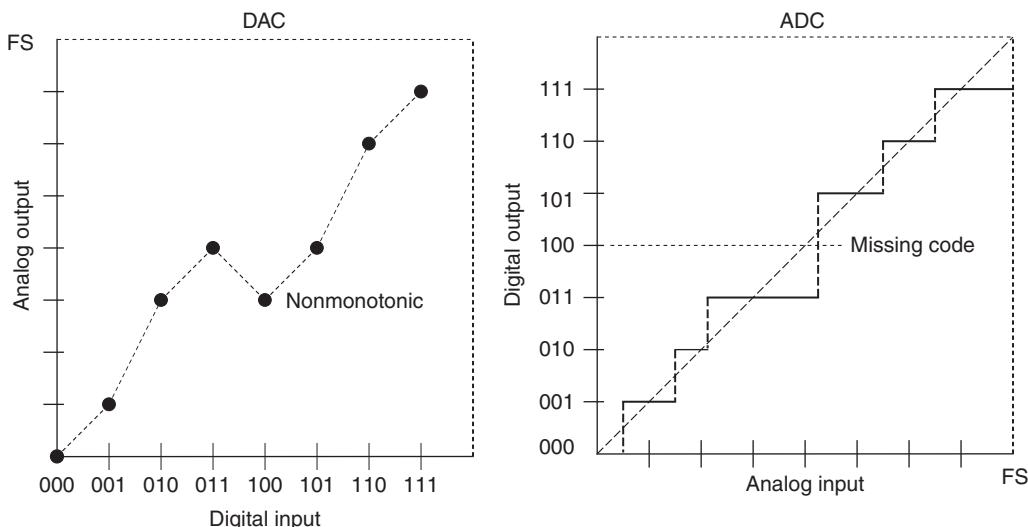

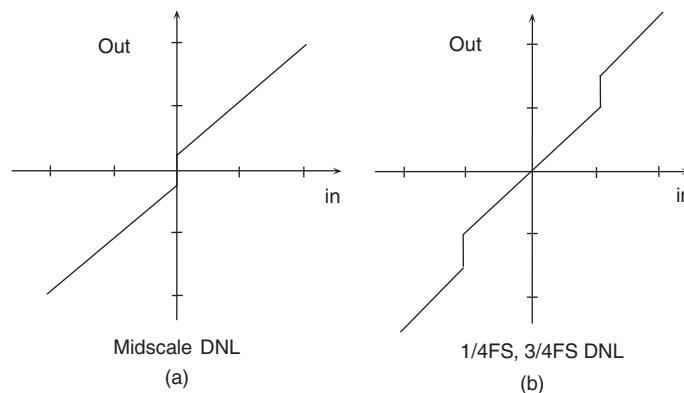

The other type of converter nonlinearity is *differential nonlinearity* (DNL). This relates to the linearity of the code transitions of the converter. In the ideal case, a change of 1 LSB in digital code corresponds to a change of exactly 1 LSB of analog signal. In a DAC, a change of 1 LSB in digital code produces exactly 1 LSB change of analog output, while in an ADC there should be exactly 1 LSB change of analog input to move from one digital transition to the next. Differential linearity error is defined as the maximum amount of deviation of any quantum (or LSB change) in the entire transfer function from its ideal size of 1 LSB.

Figure 1.19: Transfer functions for nonideal 3-bit DAC and ADC

Where the change in analog signal corresponding to 1 LSB digital change is more or less than 1 LSB, there is said to be a DNL error. The DNL error of a converter is normally defined as the maximum value of DNL to be found at any transition across the range of the converter. Figure 1.19 shows the nonideal transfer functions for a DAC and an ADC and shows the effects of the DNL error.

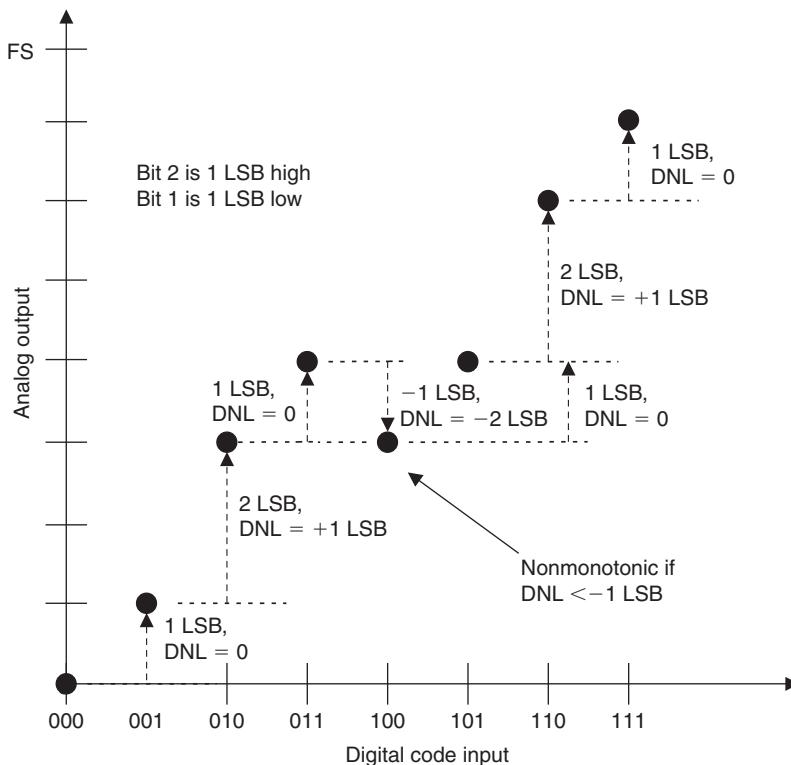

The DNL of a DAC is examined more closely in Figure 1.20. If the DNL of a DAC is less than  $-1$  LSB at any transition, the DAC is *nonmonotonic*; i.e., its transfer characteristic contains one or more localized maxima or minima. A DNL greater than  $+1$  LSB does not cause nonmonotonicity, but is still undesirable. In many DAC applications (especially closed-loop systems where nonmonotonicity can change negative feedback to positive feedback), it is critically important that DACs are monotonic. DAC monotonicity is often explicitly specified on data sheets, although if the DNL is guaranteed to be less than 1 LSB (i.e.,  $|DNL| \leq 1$  LSB), the device must be monotonic, even without an explicit guarantee.

Figure 1.20: Details of DAC differential nonlinearity

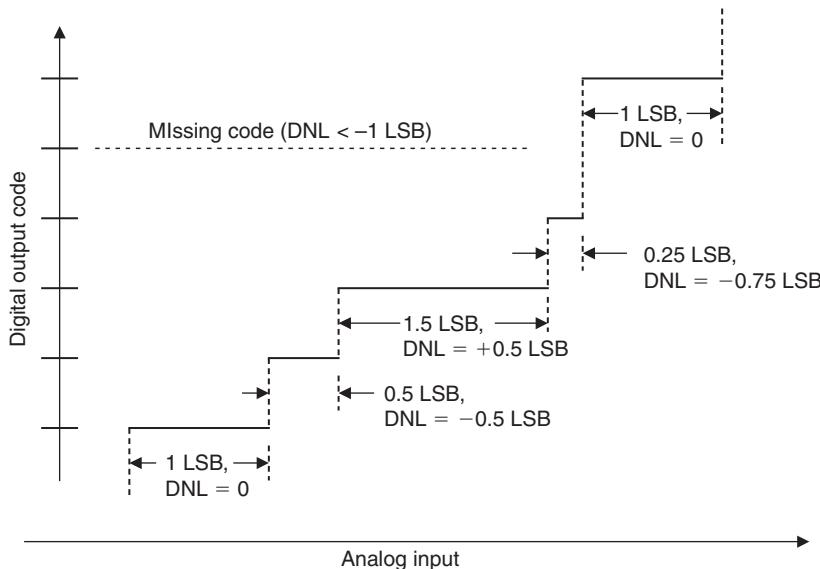

In Figure 1.21, the DNL of an ADC is examined more closely on an expanded scale. ADCs can be nonmonotonic, but a more common result of excess DNL in ADCs is *missing codes*. Missing codes in an ADC are as objectionable as nonmonotonicity in a DAC. Again, they result from  $DNL < -1$  LSB.

Not only can ADCs have missing codes, they can also be nonmonotonic as shown in Figure 1.22. As in the case of DACs, this can present major problems—especially in servo applications.

In a DAC, there can be no missing codes—each digital input word will produce a corresponding analog output. However, DACs can be nonmonotonic as previously discussed. In a straight binary DAC, the most likely place a nonmonotonic condition can develop is at midscale between the two codes: 011...11 and 100...00. If a nonmonotonic condition occurs here, it is generally because the DAC is not properly calibrated or trimmed. A successive approximation ADC with an internal nonmonotonic DAC will generally produce missing codes but remain monotonic. However, it is possible for an ADC to be nonmonotonic—again depending on the particular conversion architecture. Figure 1.22 shows the transfer function of an ADC, which is nonmonotonic and has a missing code.

ADCs that use the *subranging* architecture divide the input range into a number of coarse segments, and each coarse segment is further divided into smaller segments—and

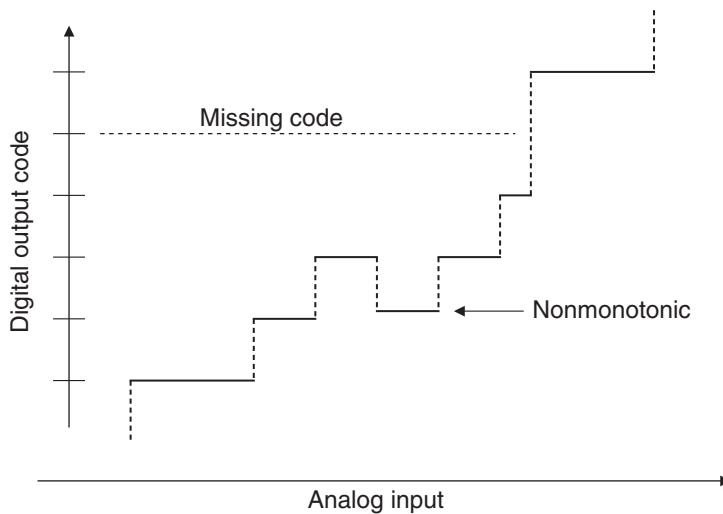

Figure 1.21: Details of ADC differential nonlinearity

Figure 1.22: Nonmonotonic ADC with missing code

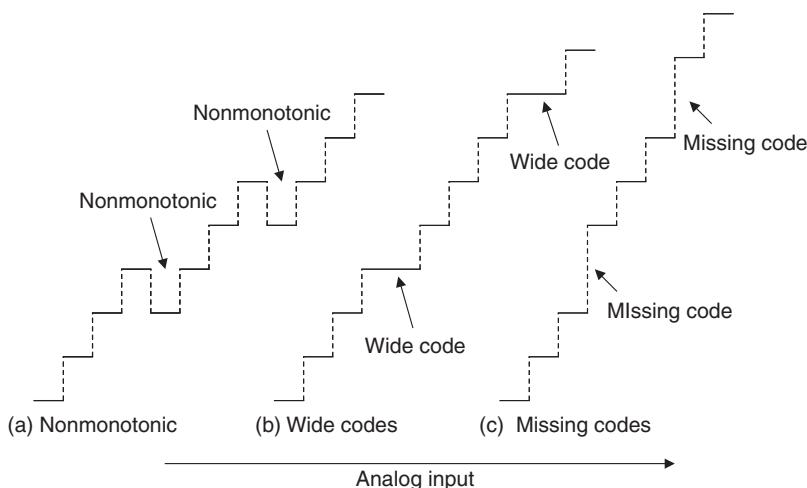

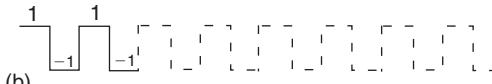

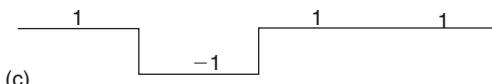

ultimately the final code is derived. An improperly trimmed subranging ADC may exhibit nonmonotonicity, wide codes, or missing codes at the subranging points as shown in Figure 1.23 a, b, and c, respectively. This type of ADC should be trimmed so that drift due to aging or temperature produces wide codes at the sensitive points rather than nonmonotonic or missing codes.

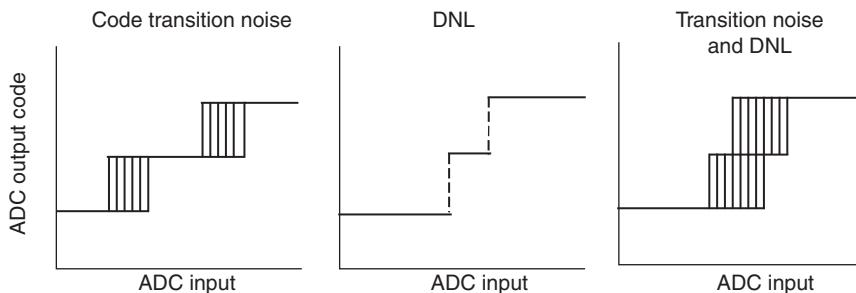

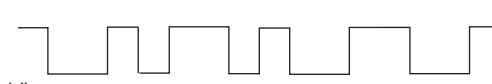

Defining missing codes is more difficult than defining nonmonotonicity. All ADCs suffer from some inherent transition noise as shown in Figure 1.24 (think of it as the flicker between adjacent values of the last digit of a DVM). As resolutions and bandwidths become higher, the range of input over which transition noise occurs may approach, or even exceed, 1 LSB. High resolution wideband ADCs generally have internal noise sources that can be reflected to the input as effective input noise summed with the signal. The effect of this noise, especially if combined with a negative DNL error, may be that there are some (or even all) codes where transition noise is present for the whole range of inputs. Therefore, there are some codes for which there is *no* input that will *guarantee* that code as an output, although there may be a range of inputs that will *sometimes* produce that code.

For low resolution ADCs, it may be reasonable to define *no missing codes* as a combination of transition noise and DNL, which guarantees some level (perhaps 0.2 LSB) of noise-free code for all codes. However, this is impossible to achieve at the very high resolutions achieved by modern sigma-delta ADCs, or even at lower resolutions in wide bandwidth

Figure 1.23: Errors associated with improperly trimmed subranging ADC

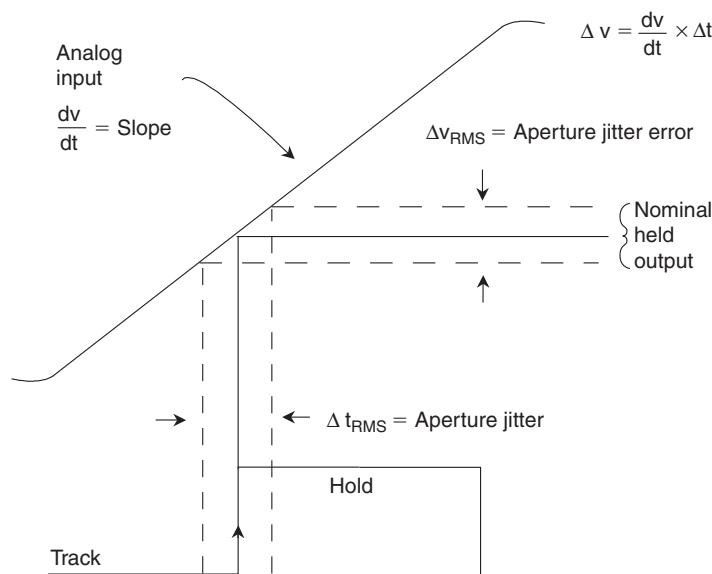

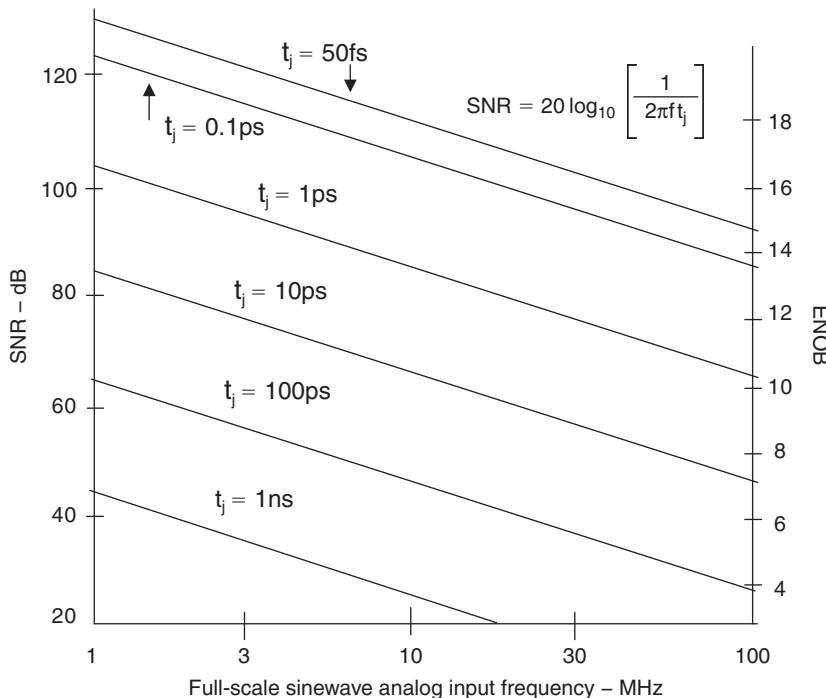

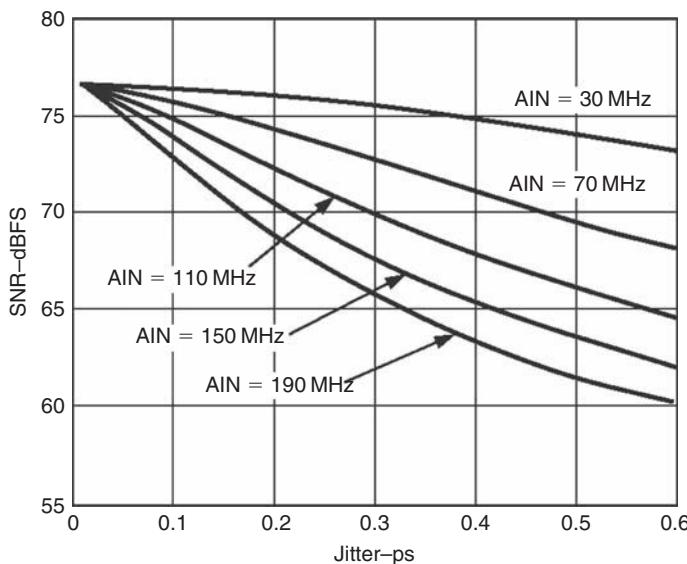

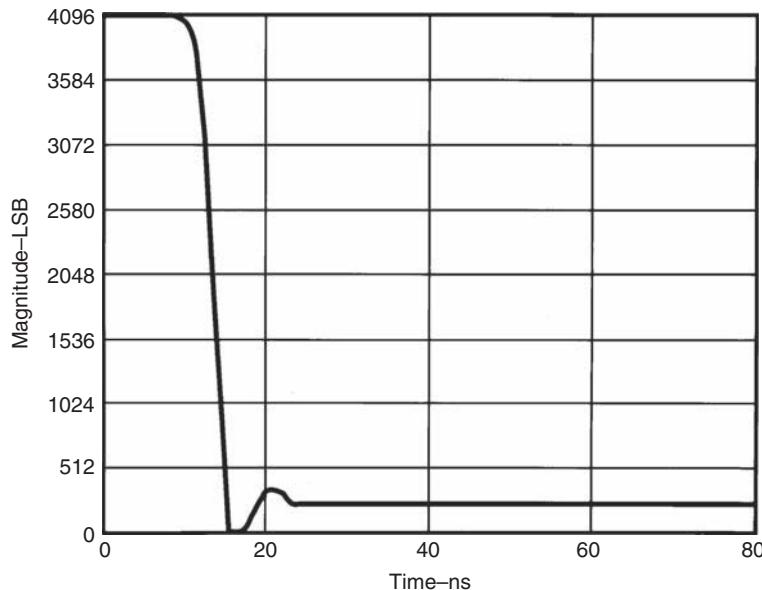

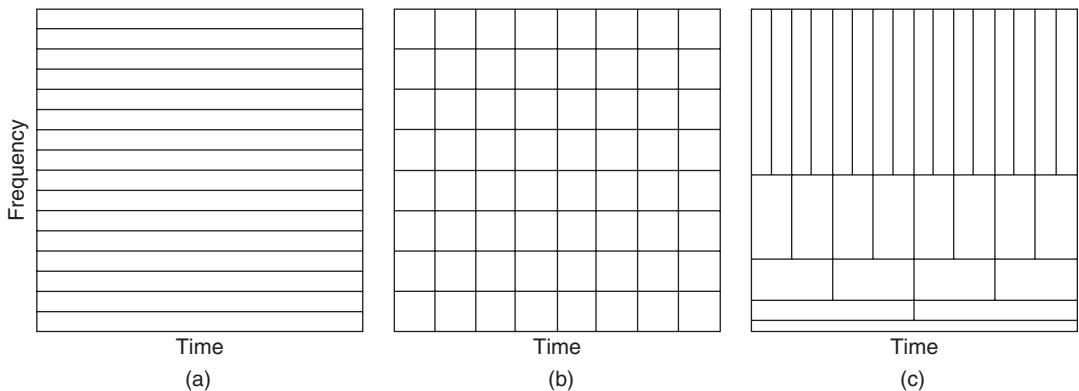

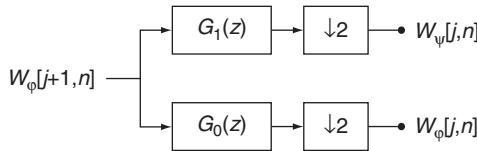

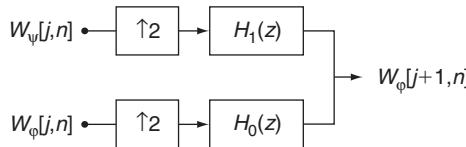

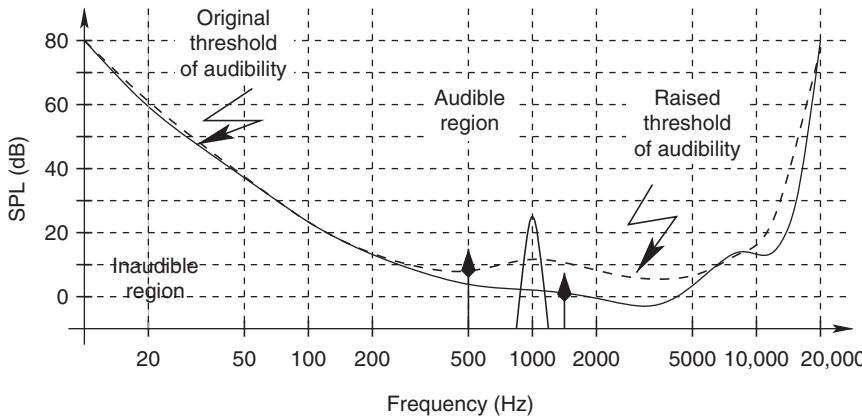

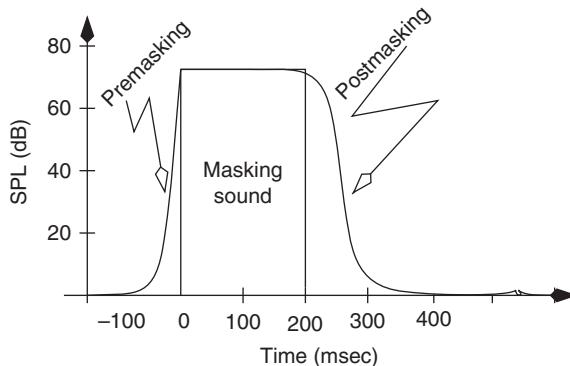

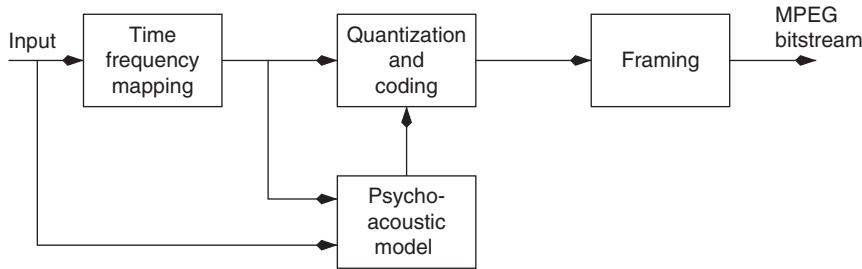

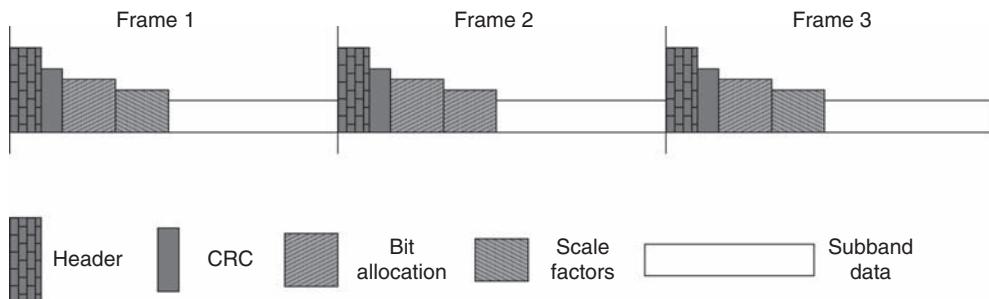

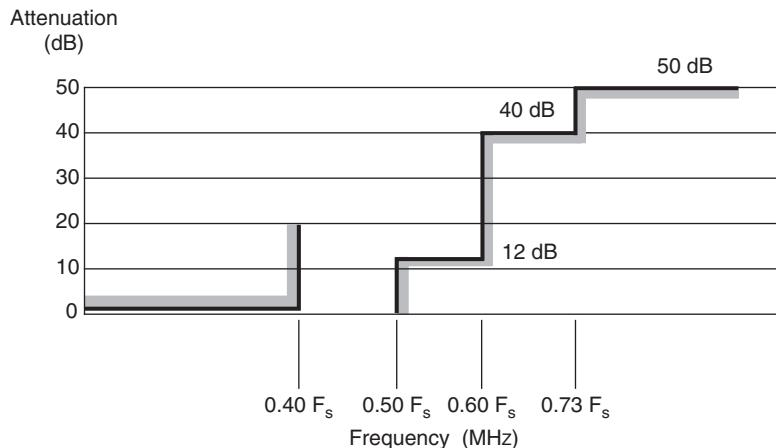

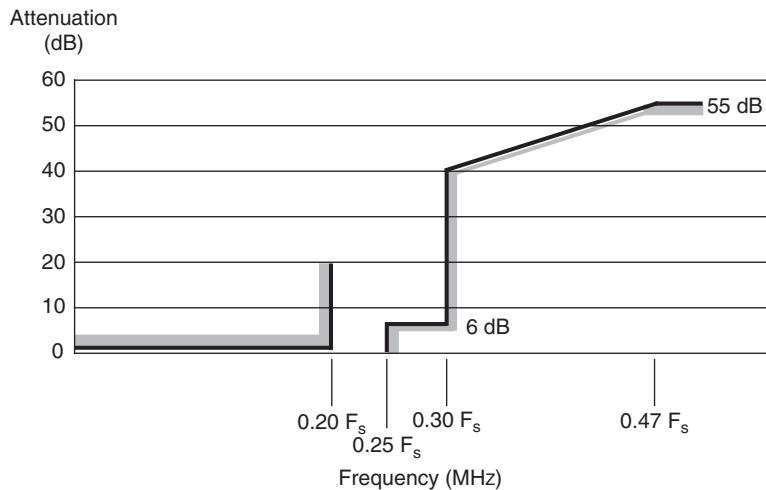

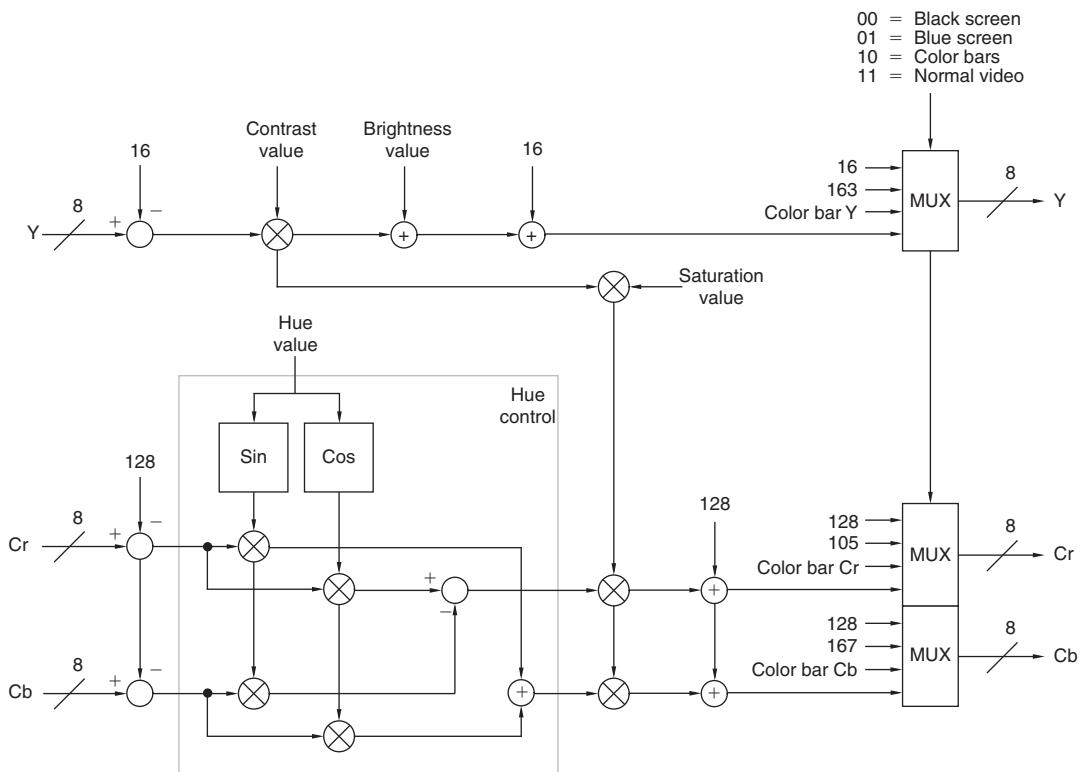

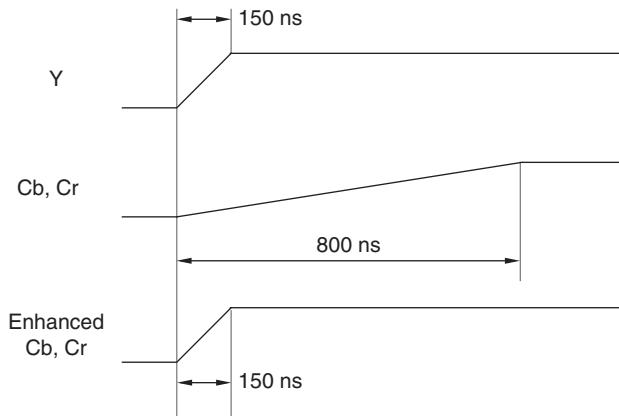

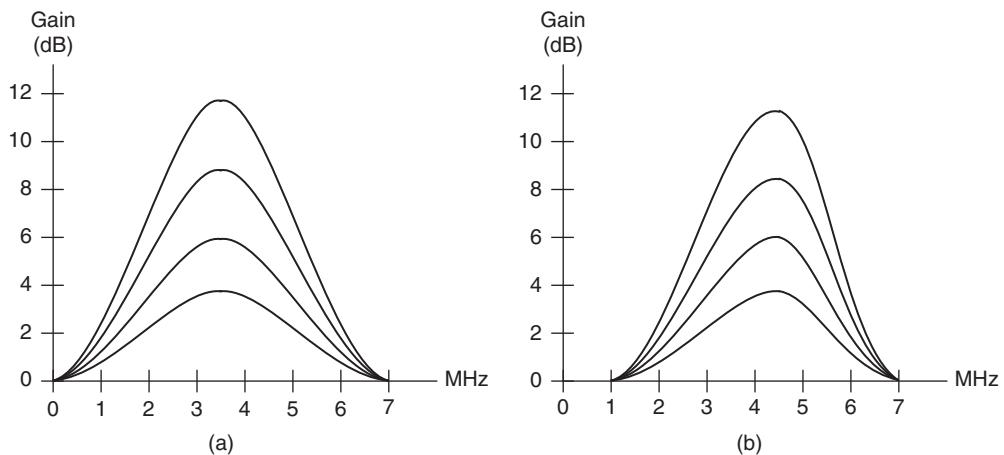

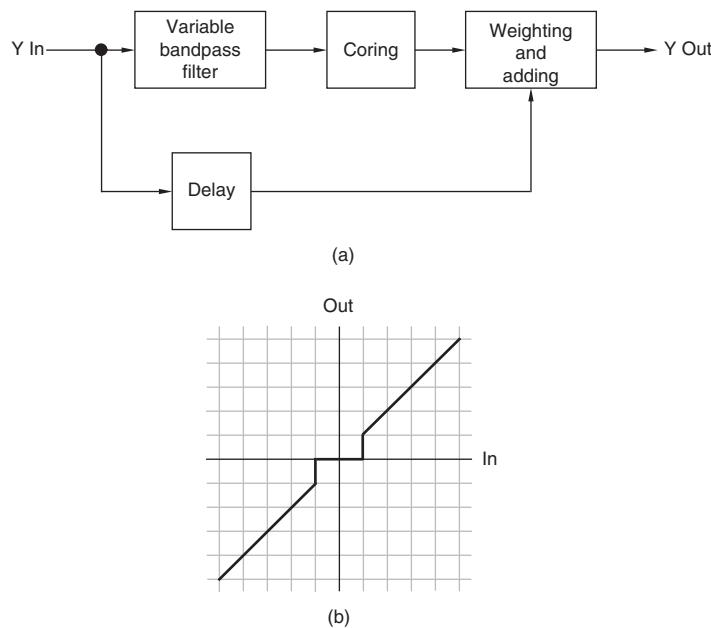

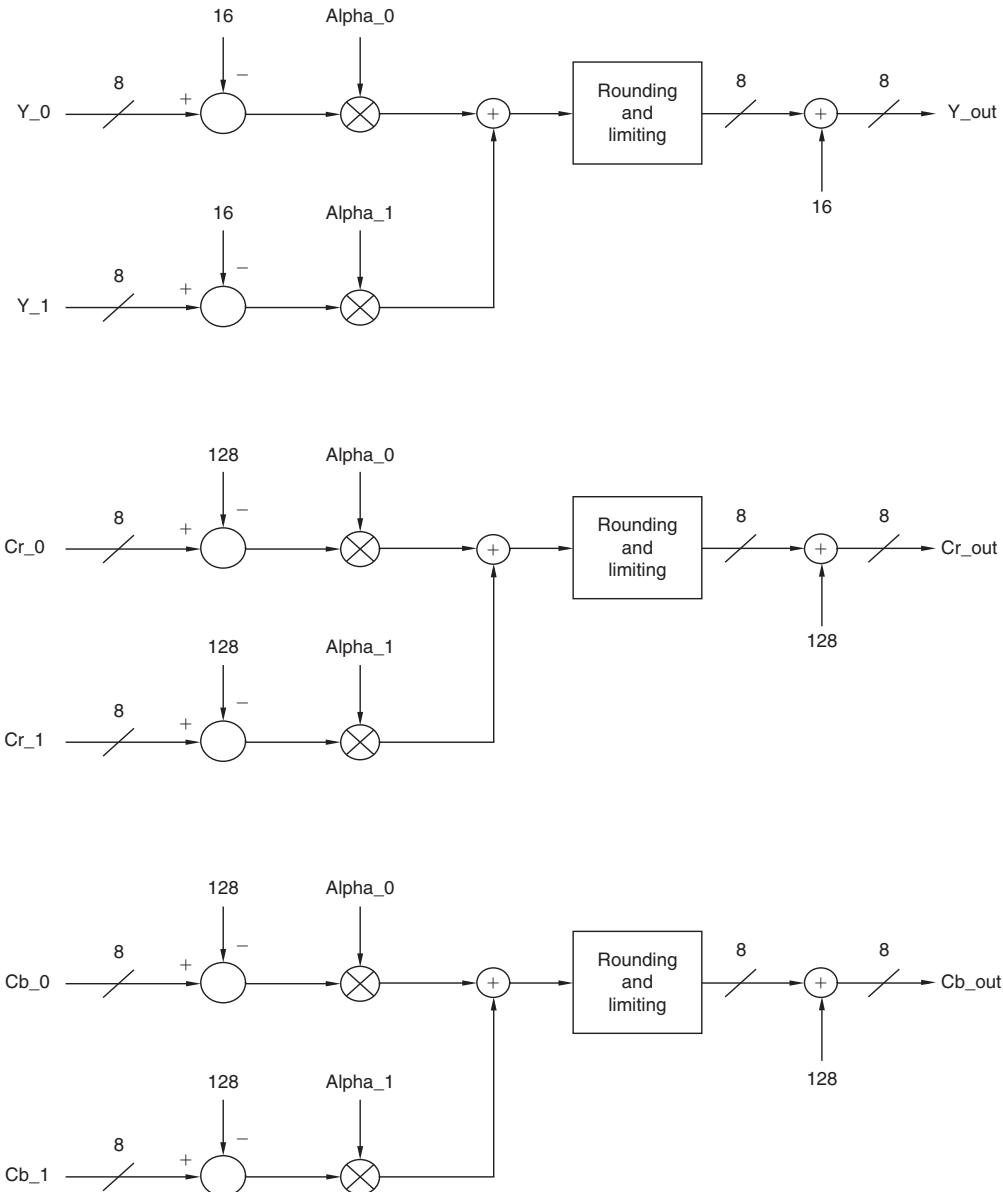

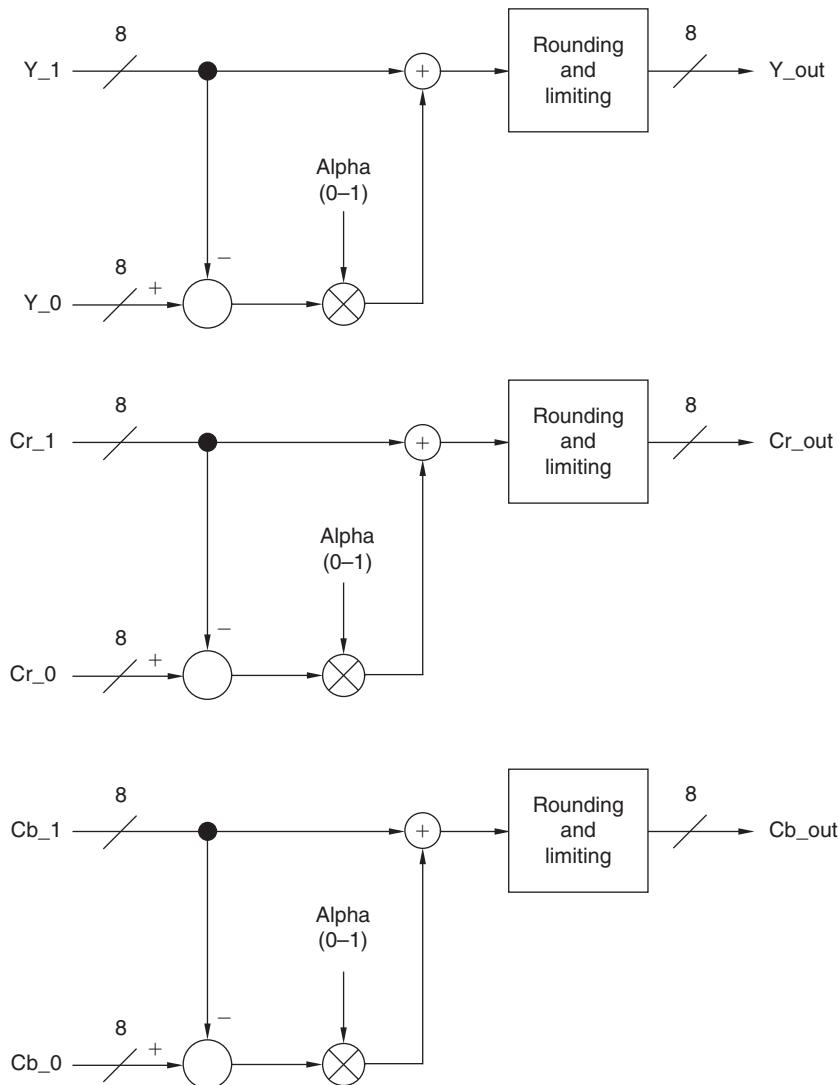

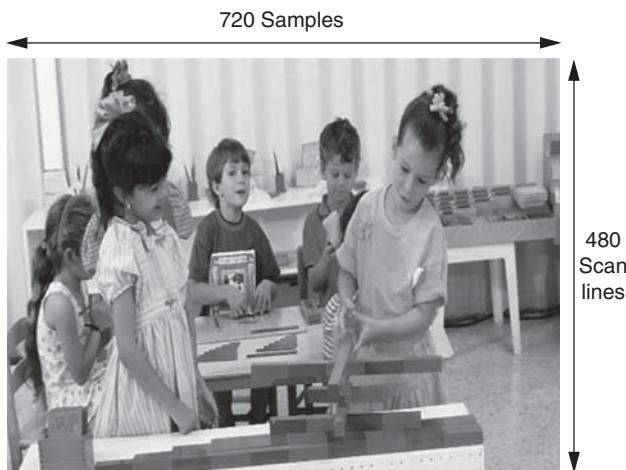

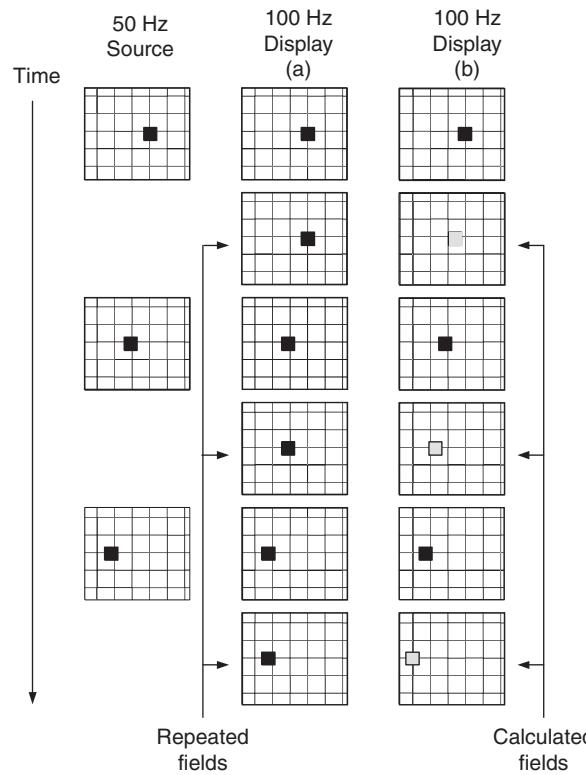

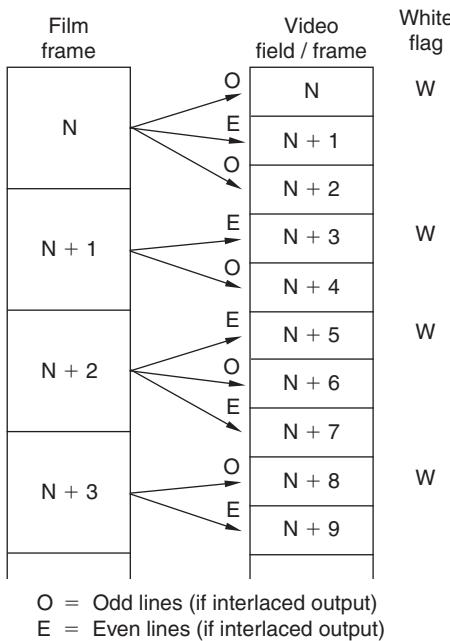

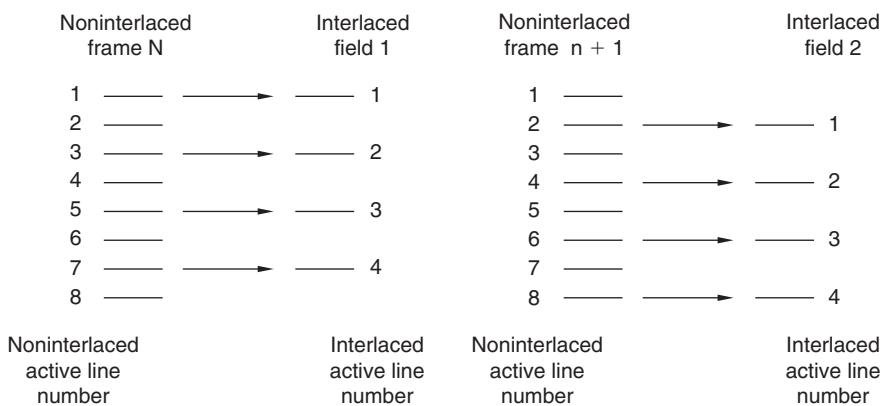

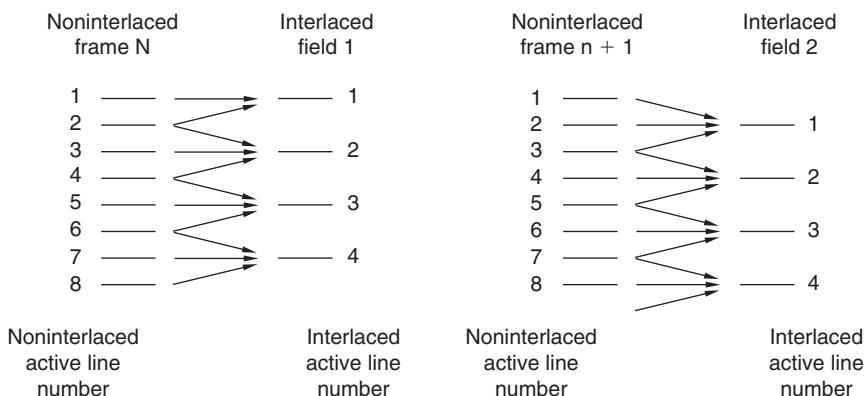

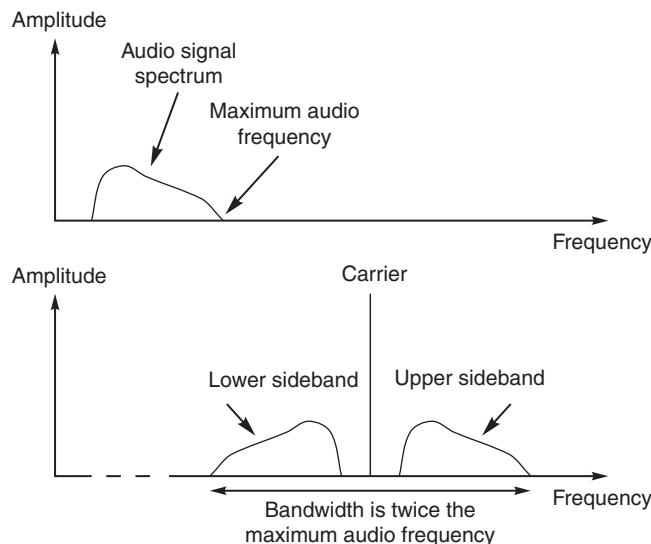

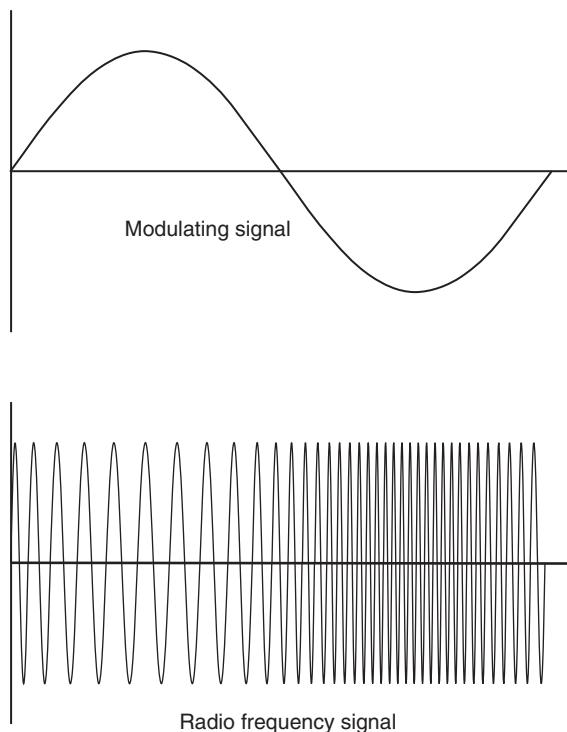

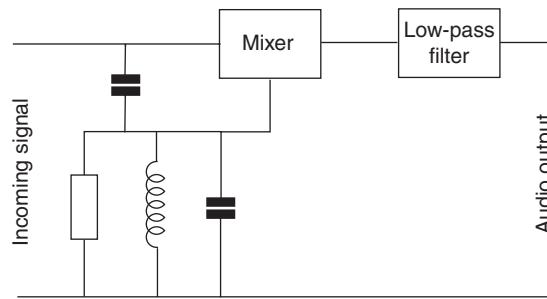

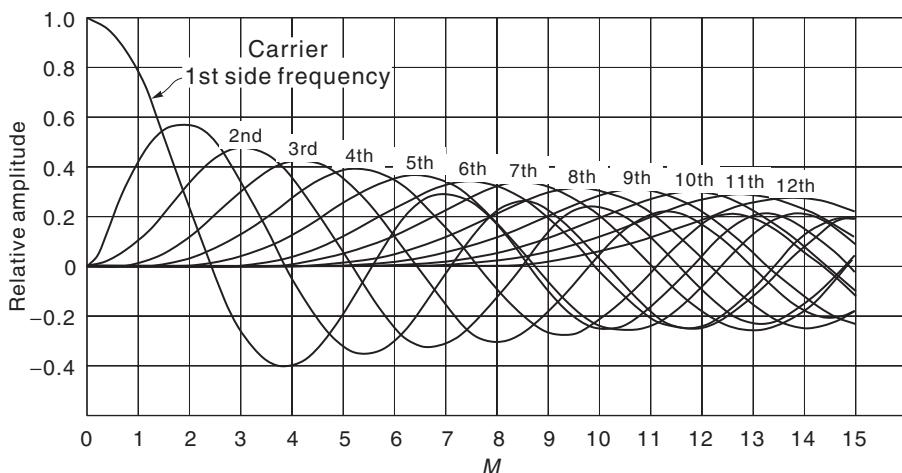

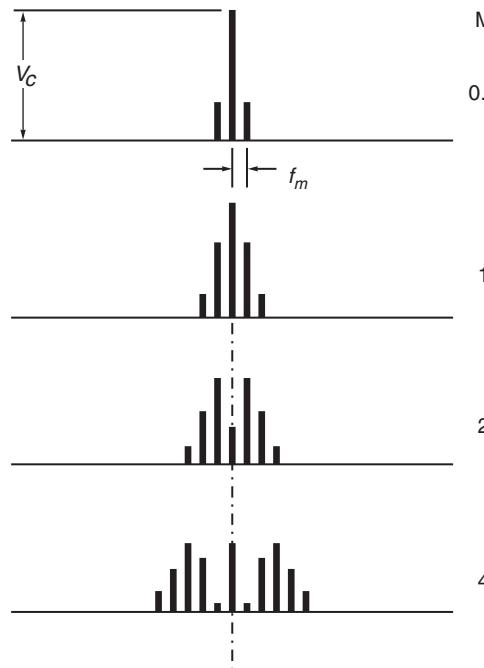

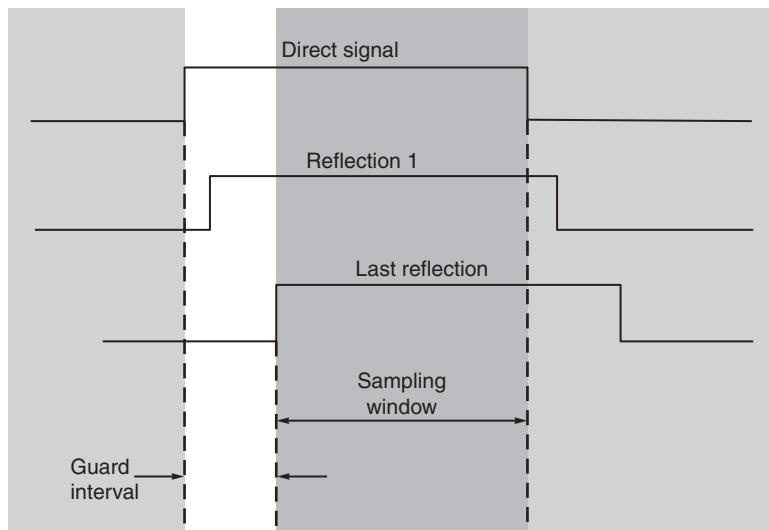

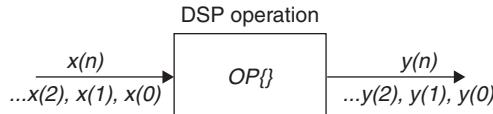

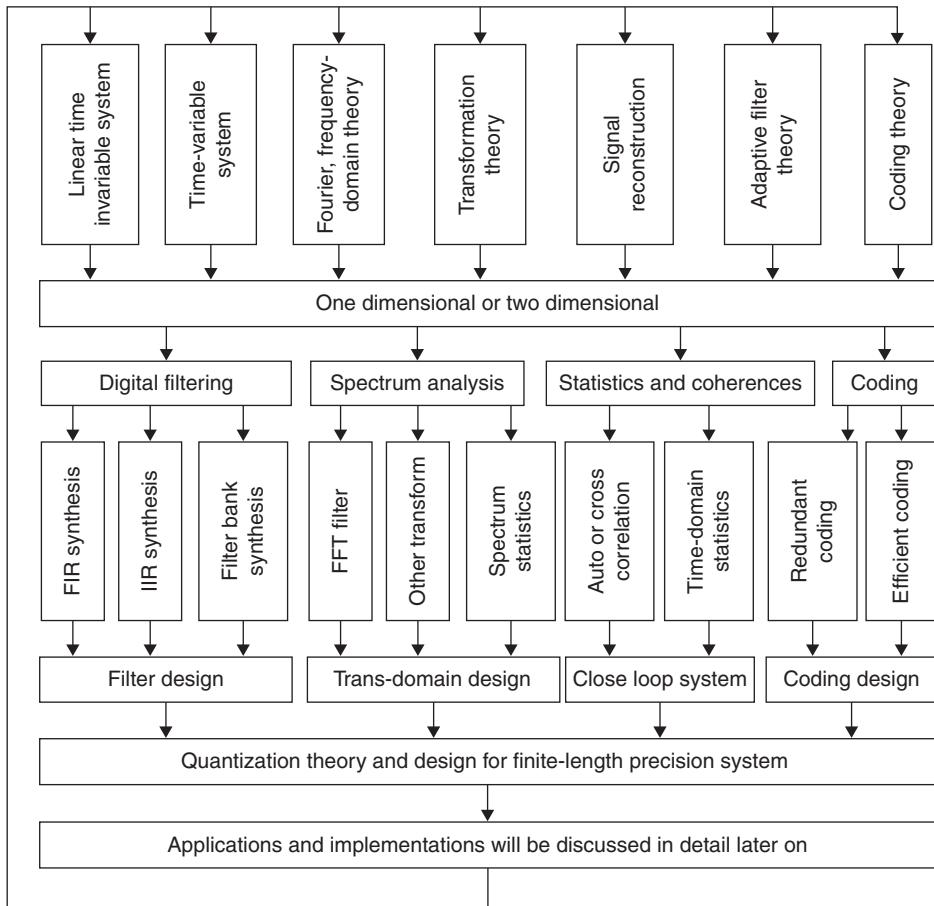

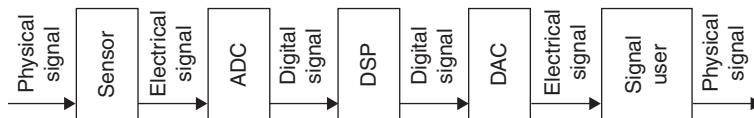

Figure 1.24: Combined effects of code transition noise and DNL