SERIES IN MATERIALS SCIENCE AND ENGINEERING

# STRAINED-SI HETEROSTRUCTURE FIELD EFFECT DEVICES

C K MAITI

S CHATTOPADHYAY

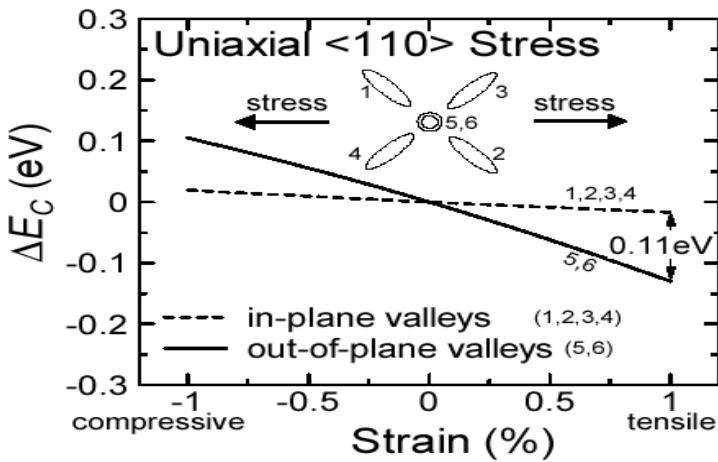

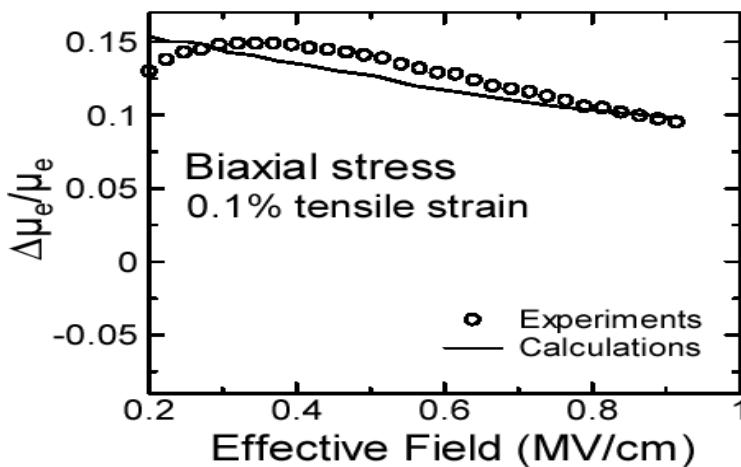

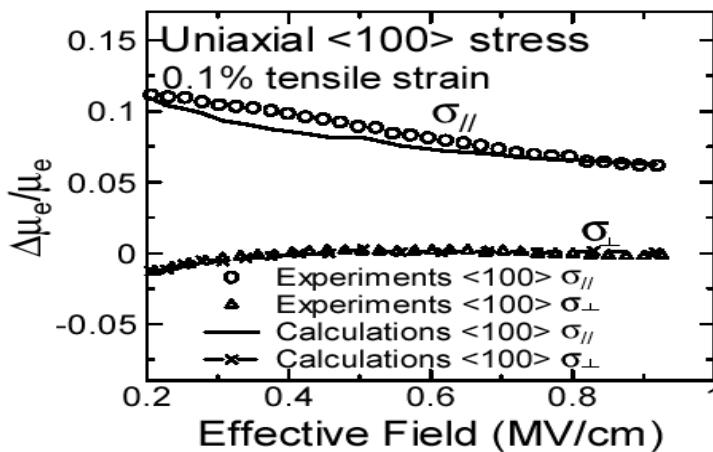

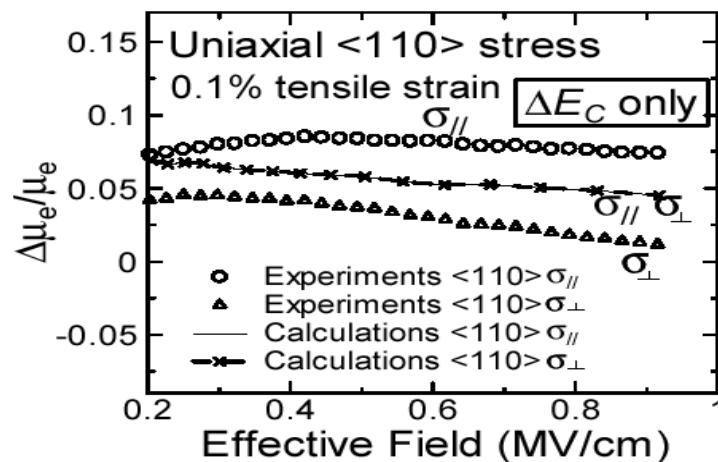

L K BERI

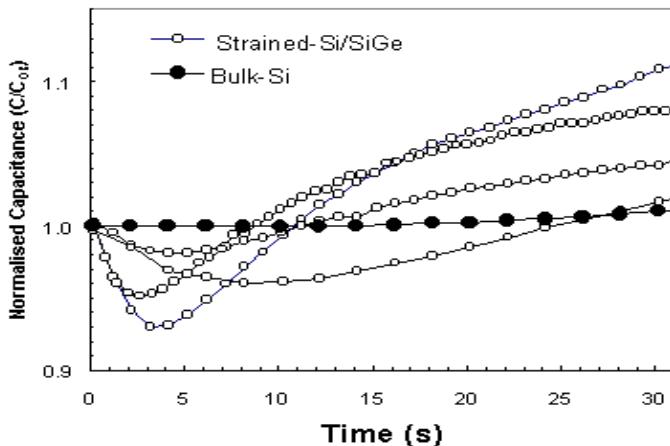

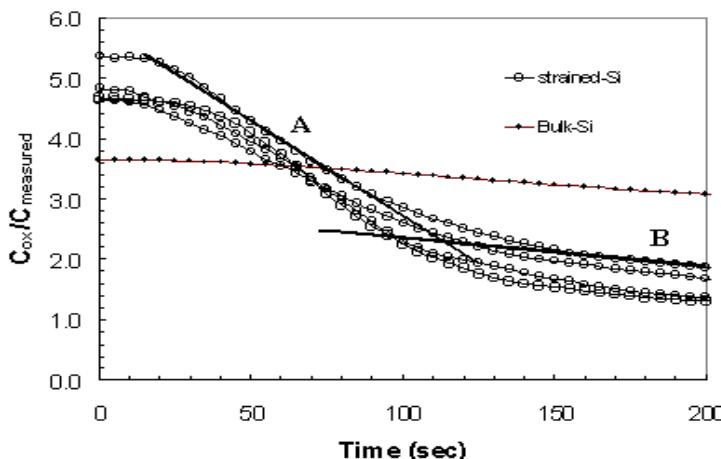

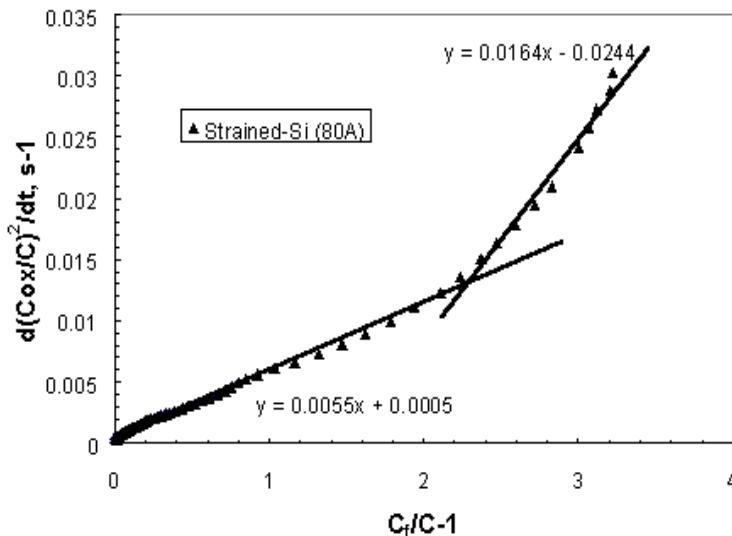

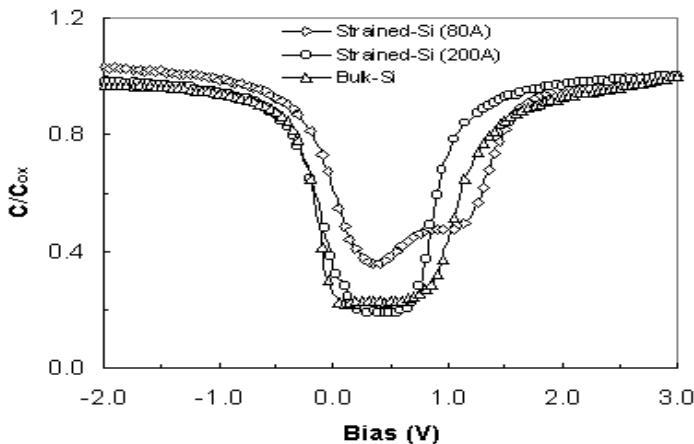

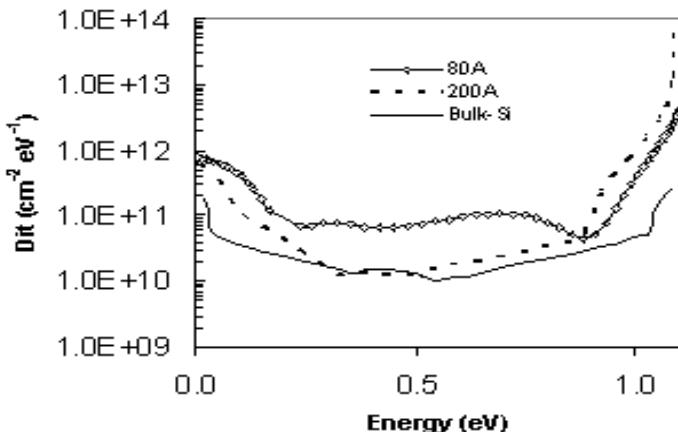

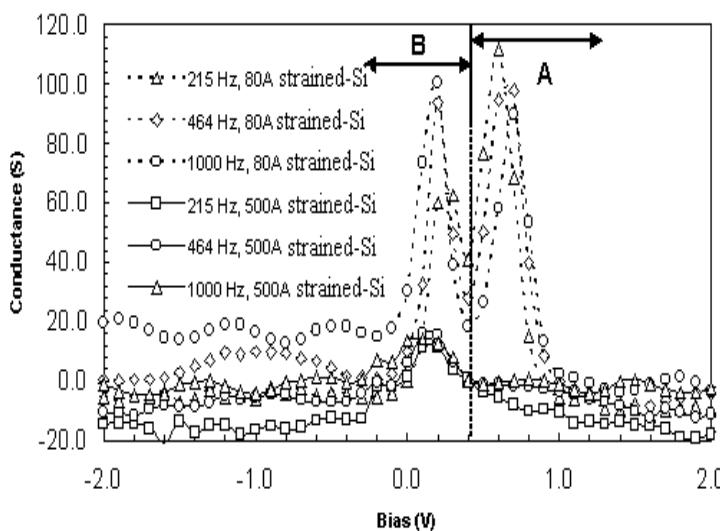

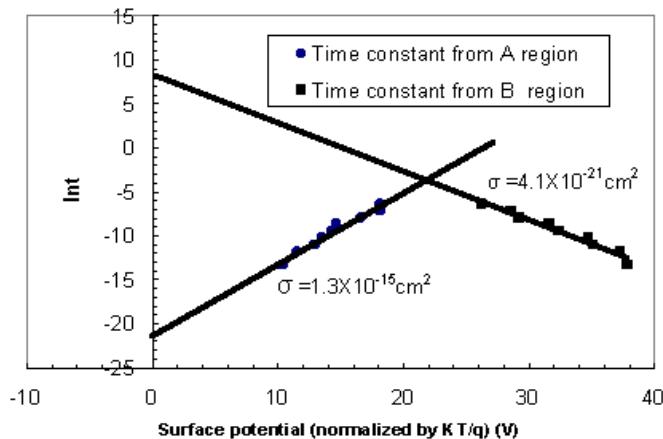

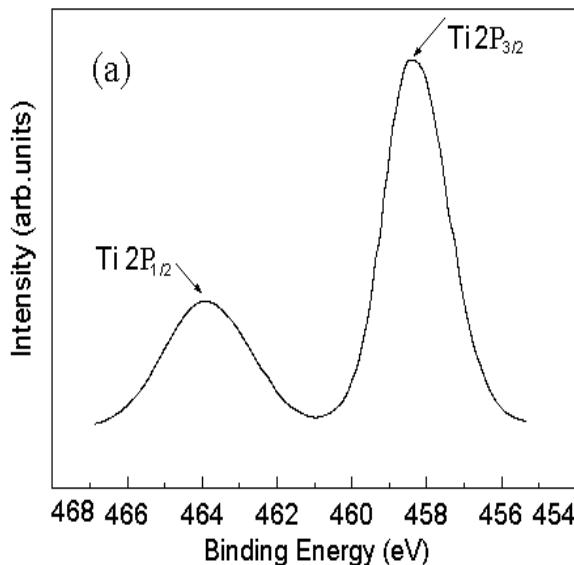

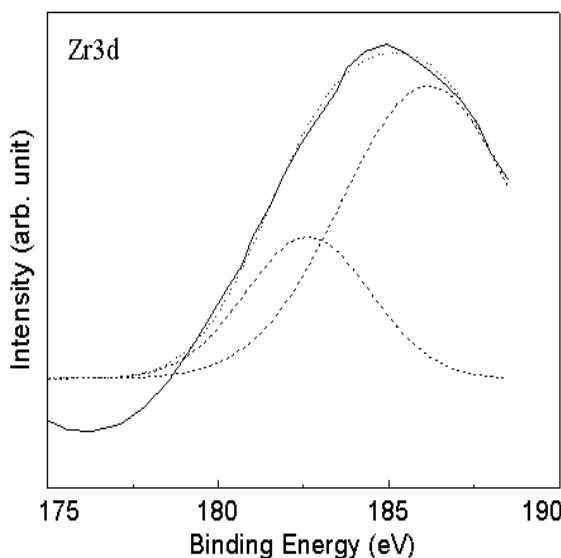

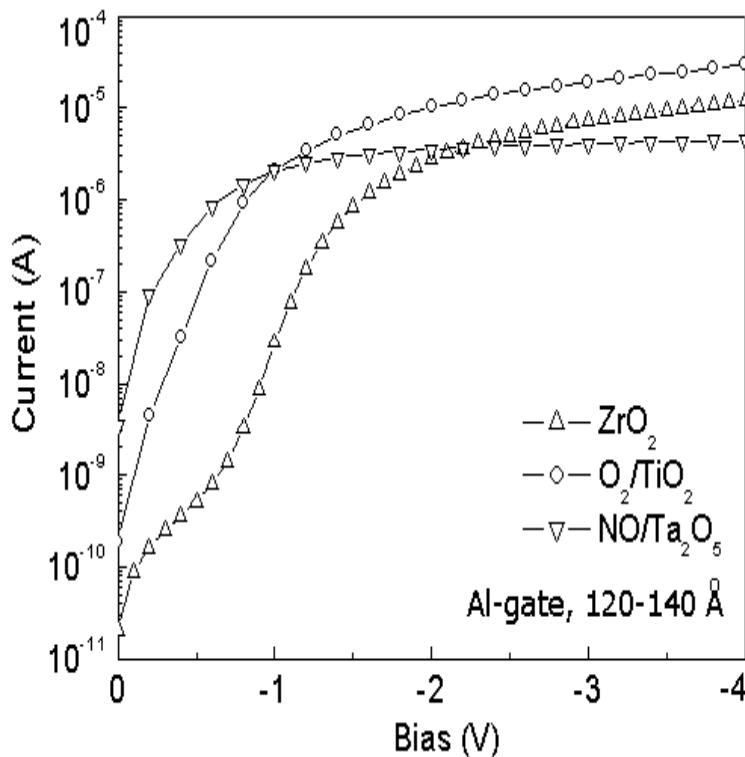

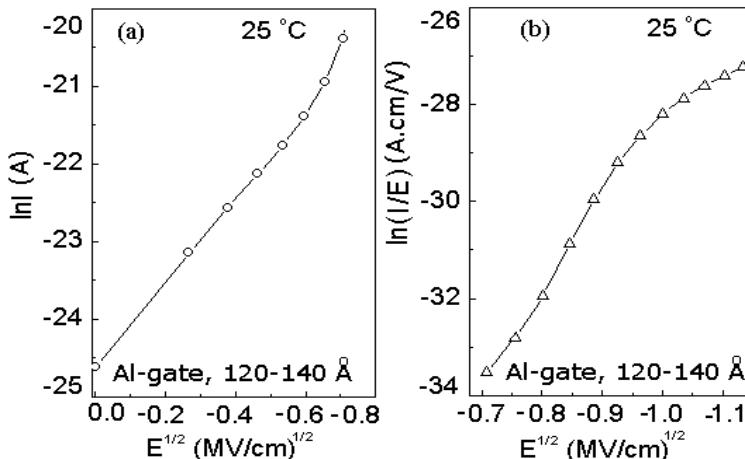

Taylor & Francis

Taylor & Francis Group

# Strained-Si Heterostructure Field Effect Devices

# **Series in Materials Science and Engineering**

*Series Editors:* **Alwyn Eades**, Lehigh University, Bethlehem, PA, USA

**Evan Ma**, Johns Hopkins University, Baltimore, MD, USA

*Other books in the series:*

## **Spintronic Materials and Technology**

Y B Xu, S M Thompson (Eds)

## **Fundamentals of Fibre Reinforced Composite Materials**

A R Bunsell, J Renard

## **Novel Nanocrystalline Alloys and Magnetic Nanomaterials**

B Cantor (Ed)

## **3-D Nanoelectronic Computer Architecture and Implementation**

D Crawley, K Nikolic, M Forshaw (Eds)

## **Computer Modelling of Heat and Fluid Flow in Materials Processing**

C P Hong

## **High-K Gate Dielectrics**

M Houssa (Ed)

## **Metal and Ceramic Matrix Composites**

B Cantor, F P E Dunne, I C Stone (Eds)

## **High Pressure Surface Science and Engineering**

Y Gogotsi, V Domnick (Eds)

## **Physical Methods for Materials Characterisation, Second Edition**

P E J Flewitt, R K Wild

## **Topics in the Theory of Solid Materials**

J M Vail

## **Solidification and Casting**

B Cantor, K O'Reilly (Eds)

## **Fundamentals of Ceramics**

M W Barsoum

## **Aerospace Materials**

B Cantor, H Assender, P Grant (Eds)

## **Physical Methods for Materials Characterisation**

P E J Flewitt, R K Wild

Series in Materials Science and Engineering

# Strained-Si Heterostructure Field Effect Devices

**C K Maiti**

*Indian Institute of Technology, India*

**S Chattopadhyay**

*University of Newcastle, UK*

**L K Bera**

*Kulim Hi-Tech, Kedah, Malaysia*

**Taylor & Francis**

Taylor & Francis Group

New York London

CRC Press

Taylor & Francis Group

6000 Broken Sound Parkway NW, Suite 300

Boca Raton, FL 33487-2742

© 2007 by Taylor & Francis Group, LLC

CRC Press is an imprint of Taylor & Francis Group, an Informa business

No claim to original U.S. Government works

Printed in the United States of America on acid-free paper

10 9 8 7 6 5 4 3 2 1

International Standard Book Number-10: 0-7503-0993-8 (Hardcover)

International Standard Book Number-13: 978-0-7503-0993-6 (Hardcover)

This book contains information obtained from authentic and highly regarded sources. Reprinted material is quoted with permission, and sources are indicated. A wide variety of references are listed. Reasonable efforts have been made to publish reliable data and information, but the author and the publisher cannot assume responsibility for the validity of all materials or for the consequences of their use.

No part of this book may be reprinted, reproduced, transmitted, or utilized in any form by any electronic, mechanical, or other means, now known or hereafter invented, including photocopying, microfilming, and recording, or in any information storage or retrieval system, without written permission from the publishers.

For permission to photocopy or use material electronically from this work, please access [www.copyright.com](http://www.copyright.com) (<http://www.copyright.com/>) or contact the Copyright Clearance Center, Inc. (CCC) 222 Rosewood Drive, Danvers, MA 01923, 978-750-8400. CCC is a not-for-profit organization that provides licenses and registration for a variety of users. For organizations that have been granted a photocopy license by the CCC, a separate system of payment has been arranged.

**Trademark Notice:** Product or corporate names may be trademarks or registered trademarks, and are used only for identification and explanation without intent to infringe.

---

**Library of Congress Cataloging-in-Publication Data**

---

Maiti, C. K.

Strained-Si heterostructure field effect devices / C.K. Maiti, L.K. Bera, and S. Chattopadhyay.

p. cm.

Includes bibliographical references and index.

ISBN-13: 978-0-7503-0993-6 (alk. paper)

1. Metal oxide semiconductor field-effect transistors. 2. Silicon--Electrical properties. 1. Bera, L. K. II. Chattopadhyay, Swapan, 1952- III. Title. IV. Title: Strained silicon heterostructure field effect devices.

TK7871.95.M27 2007

621.3815'284--dc22

2006031518

---

Visit the Taylor & Francis Web site at

<http://www.taylorandfrancis.com>

and the CRC Press Web site at

<http://www.crcpress.com>

---

## *Dedication*

WHERE ARE WE HEADING?

The principal applications of any

sufficiently new and innovative technology

always have been

- and will continue to be -

applications created by that new technology

..... **Herbert Kroemer**

We dedicate this Monograph

Strained-Si Heterostructure Field Effect Devices

to YOU, Sir.

---

## *Preface*

Soon after Bardeen, Brattain, and Shockley invented the solid-state device in 1947, the microelectronics revolution started. Today, the world market for semiconductors is beyond 200 billion dollars, of which 80% is dominated by CMOS and interestingly, Si devices account for 97% of all microelectronics. The semiconductor sales have doubled in every three technology generations. However, the semiconductor industry is now facing tremendous challenges to extend the integrated circuit (IC) performance to meet the ever-increasing demand for complex functionality. Innovations in both the device structures and new materials are needed to continue with the Si CMOS roadmap.

While introducing new structure innovations has always been an important part of device scaling, the integration of new materials is facing serious hurdles in order to meet the aggressive specifications of the International Technology Roadmap for Semiconductors (ITRS). Although the idea of using silicon-germanium (SiGe) and silicon strained-layer epitaxy toward bandgap engineering in semiconductor devices is an old one, this concept has become a reality only during the last two decades. It is expected that strained-Si will set a new technology roadmap for the CMOS industry with enhanced performance, however, with a minimum change in the existing Si infrastructure. This is a solution the industry has been searching for the last few years.

Since the mid-nineties, there is a growing interest in bipolar and MOSFETs designed with SiGe and strained-Si/SiGe as channels because of the potential enhancement in performance due to improved carrier transport properties. Recent integration of III-V layers on Si substrates has created tremendous interest, even though the direct application of such technologies may not take place in the near future. Novel channel materials may also support operation at high power or temperature and lead to increased radiation hardness, and band structure engineering would offer design flexibility and monolithic optoelectronic circuits would likely become manufacturable. While the new devices are expected to be highly innovative, they still have to meet the fundamental criteria of functional capability and economic viability.

The purpose of the monograph is to survey the R&D strategy and address the research needs associated with the front-end aspects of extending CMOS technology via strain engineering. Areas covered include transistor structures, front-end materials and processes along with their characterization, modeling and simulation. Although lithography, back-end processes, circuit architecture, design and test are very important areas that need to be addressed for extending the CMOS, they are beyond the scope of this monograph.

As the new device structures are expected to provide advanced features from the materials in current use, the “material limit” is also being reached. Additional performance boosts can only be expected from new materials with superior electronic properties. Such properties may include high mobility (in channel), high dielectric constant (gate dielectric), controllable work functions (gate electrode), or low-resistivity (source/drain and associated contacts). The integration challenges are far more complex than those involved in the fabrication of bulk materials with specified properties.

Epitaxial technologies continue to emerge as a dominant processing step for Si-based devices. The process development for strained-Si on SiGe further points towards epitaxial processes playing an increasingly important role in future electronic and optoelectronic devices. Introduction of new materials brings in new metrology needs. These include metrologies for high spatial-resolution strain measurement, atomic force microscopy for surface analysis, dopant profiling and dose monitoring in small area and nonplanar topographies, and characterization of surface mobility in new substrates, such as, SiGe and strained-Si. Similar requirements are in the modeling and simulation, with the understanding that the new modeling and simulation tools have to be provided with the supporting database and model parameters for the materials involved.

Extension of CMOS to 22-nm node and beyond may require new nonclassical MOSFET structures coupled with advanced materials and processes. Classes of new materials include high-k gate dielectrics, metal and midgap gate metal electrodes, strained-Si and silicon-germanium alloys. These new materials will lower the gate leakage current and gate resistance and reduce the poly-gate electrode depletion capacitance, and increase the device speed. Nonclassical CMOS structures offer better control of short-channel effects, improved  $I_{on}$  via higher channel mobility, lower load capacitance and lower propagation delay time. These structures also offer lower  $I_{off}$  and lower switching energy.

Currently, strained-Si is the performance booster for extending Moore’s law. Local strain (process-induced strain) approach towards strained-Si engineering, perhaps would be the simplest among the possible approaches. However, scaling issues of local strain approach may require wafer-level uniaxial strain to provide most of the total strain for future device generations. It is now believed that wafer scale (substrate-induced) strained-Si will be as effective as silicon-on-insulator (SOI) technology in terms of extending CMOS performance. Additionally, the combination of new device structures and new materials enables new operating principles that may provide new behavior and functionality beyond the constraints of bulk planar or classical CMOS. Implementation into manufacturing of nonclassical MOSFET device structures integrated with new materials and processes (for example, a strained-Si channel integrated with a new high-k gate dielectric material) will be interesting.

The theoretical assessment via simulation of nanodevices is a challenge be-

## *Preface*

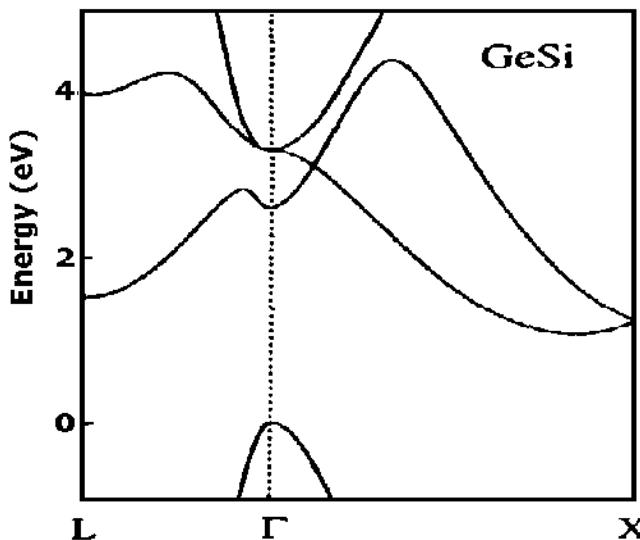

cause band structures, arbitrary wafer orientation, quantum effects, and electrostatics all are needed to be considered simultaneously. A systematic analysis of the strain effects on bandstructure and mobility in deeply scaled n- and p-MOSFETs with Si, SiGe, strained-Si and Ge channel is essential. In order to assess and compare the performances of nanoscale CMOS devices with novel channel materials (e.g., SiGe, strained-Si, and Ge), a new simulation approach is also necessary.

In this book, current status and future trends in the strained-Si materials and devices are discussed. This book is devoted to research and development (R&D) Engineers and Scientists who are actively involved in extending the roadmap for Si CMOS devices mainly via strain engineering. This monograph may also serve as a reference for postgraduate and research students. By introducing a diversity of R&D activities and results in this book, we hope to ignite even more novel concepts and innovative thinking in the field.

**C K Maiti**

**Indian Institute of Technology, Kharagpur, India**

**S Chattopadhyay**

**University of Newcastle, UK**

**and**

**L K Bera**

**Kulim Hi-Tech, Kedah, Malaysia**

---

# Contents

|                   |                                                        |           |

|-------------------|--------------------------------------------------------|-----------|

| <b>1</b>          | <b>Introduction</b>                                    | <b>1</b>  |

| 1.1               | Heterostructure Field-Effect Devices                   | 7         |

| 1.2               | Substrate Engineering                                  | 8         |

| 1.2.1             | Substrate-Induced Strain Engineering                   | 9         |

| 1.2.2             | Process-Induced Stress Engineering                     | 10        |

| 1.2.3             | Orientation-Dependent Mobility Engineering             | 11        |

| 1.3               | Gate Dielectrics on Engineered Substrates              | 12        |

| 1.4               | Strained-Si Technology: Process Integration            | 13        |

| 1.5               | Nonclassical CMOS Structures                           | 14        |

| 1.6               | Strain-Engineered Hetero-FETs: Modeling and Simulation | 16        |

| 1.7               | Summary                                                | 17        |

| <b>References</b> |                                                        | <b>18</b> |

| <b>2</b>          | <b>Strain Engineering in Microelectronics</b>          | <b>23</b> |

| 2.1               | Stress Induced During Manufacturing                    | 26        |

| 2.2               | Global vs. Local Strain                                | 32        |

| 2.3               | Substrate-Induced Strain                               | 35        |

| 2.4               | Process-Induced Stress                                 | 37        |

| 2.4.1             | Mechanical Stress Control                              | 43        |

| 2.4.2             | Substrate Orientation Dependence                       | 46        |

| 2.4.3             | Strained-Ge                                            | 48        |

| 2.5               | Stress/Strain Analysis                                 | 48        |

| 2.6               | Summary                                                | 52        |

| <b>References</b> |                                                        | <b>53</b> |

| <b>3</b>          | <b>Strain-Engineered Substrates</b>                    | <b>59</b> |

| 3.1               | Epitaxy                                                | 60        |

| 3.2               | Heteroepitaxy and Strain Control                       | 64        |

| 3.3               | Engineered Substrates: Technology                      | 71        |

| 3.3.1             | Virtual Substrates                                     | 73        |

| 3.3.2             | Substrate Specifications                               | 79        |

| 3.3.3             | Strained-Si on Insulator                               | 81        |

| 3.3.4             | Smart-Cut                                              | 87        |

| 3.3.5             | Hybrid Substrates                                      | 89        |

| 3.3.6             | GeOI Substrates                                        | 90        |

|                   |                                                            |            |

|-------------------|------------------------------------------------------------|------------|

| 3.4               | Characterization of Strained Layers                        | 93         |

| 3.4.1             | XRD                                                        | 96         |

| 3.4.2             | SIMS                                                       | 100        |

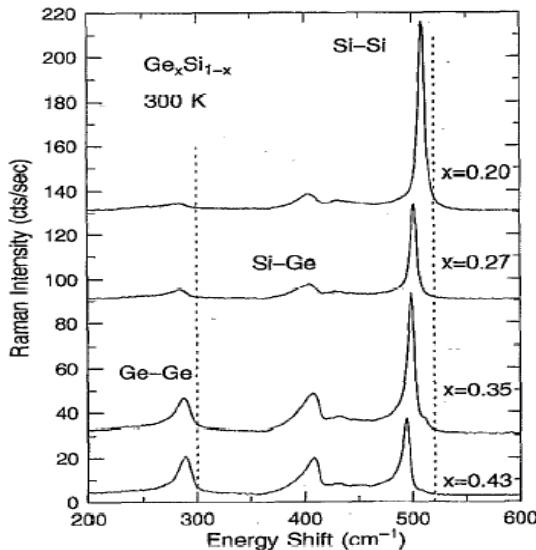

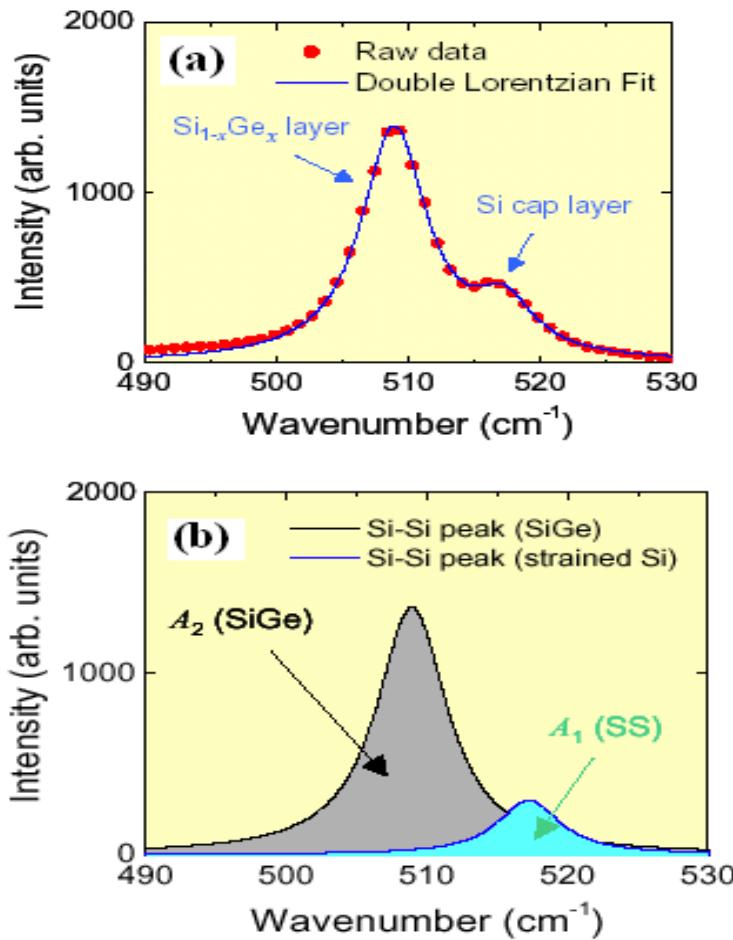

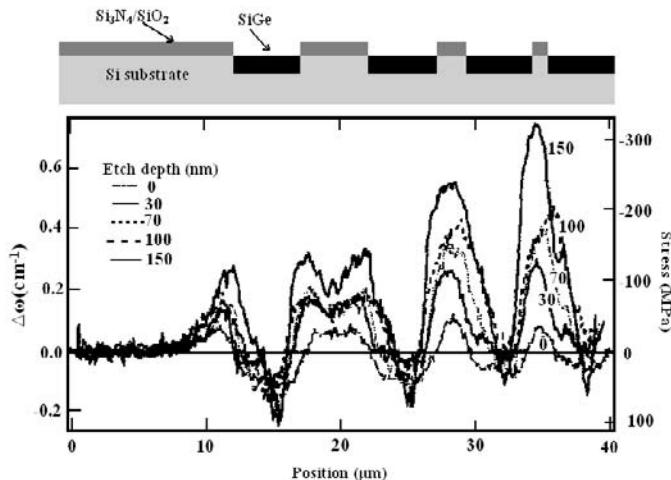

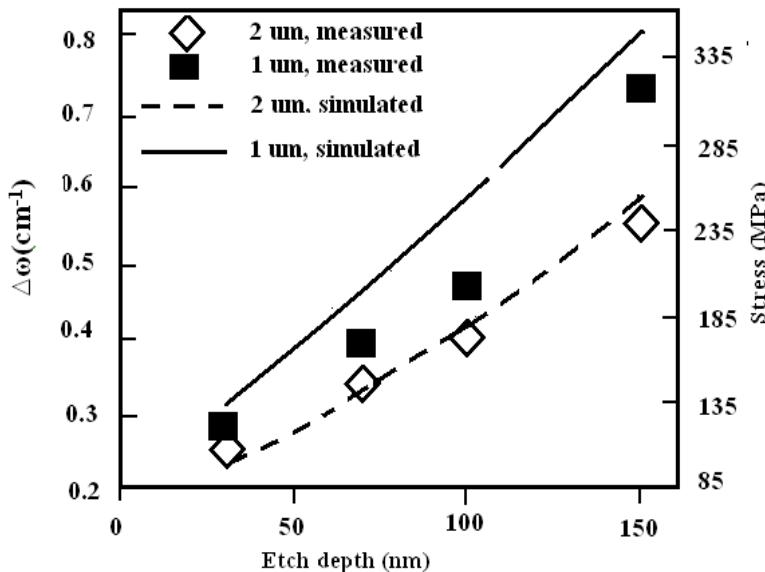

| 3.4.3             | Raman                                                      | 101        |

| 3.5               | Engineered Substrates                                      | 106        |

| 3.5.1             | Mobility Comparison                                        | 106        |

| 3.5.2             | Thermal Conductivity                                       | 109        |

| 3.6               | Summary                                                    | 111        |

| <b>References</b> |                                                            | <b>111</b> |

| <b>4</b>          | <b>Electronic Properties of Engineered Substrates</b>      | <b>119</b> |

| 4.1               | Substrate-induced Strained-Si                              | 120        |

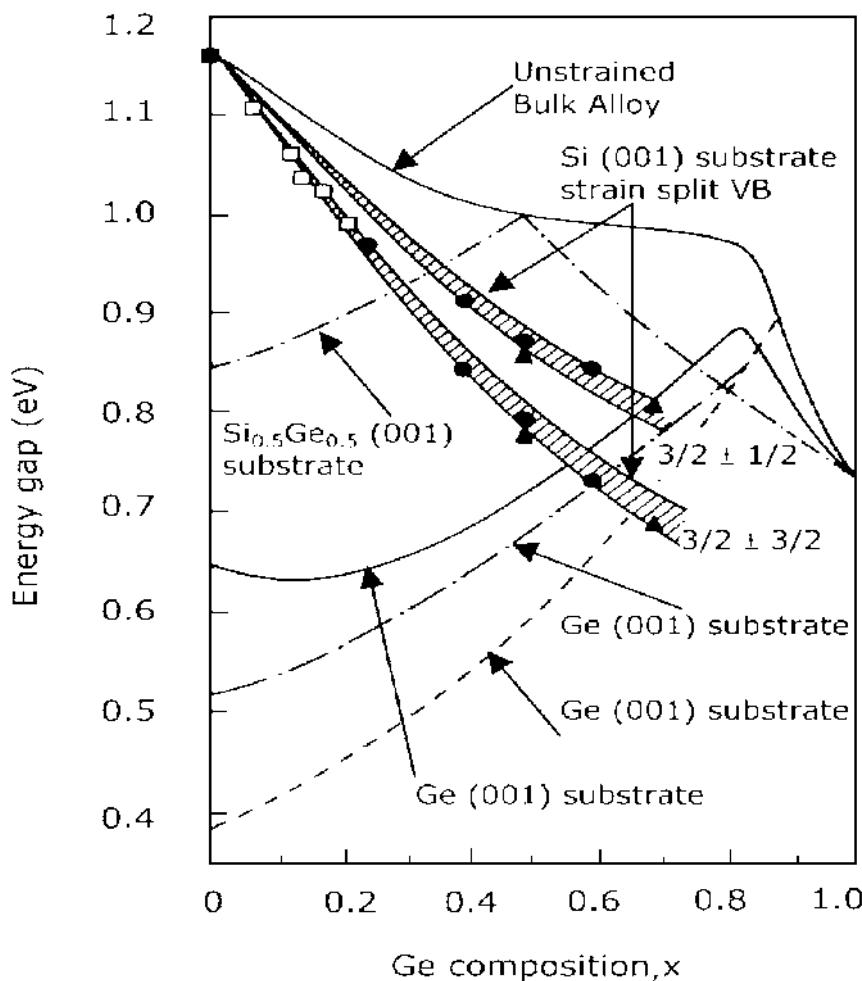

| 4.1.1             | Energy Gap and Band Structure                              | 122        |

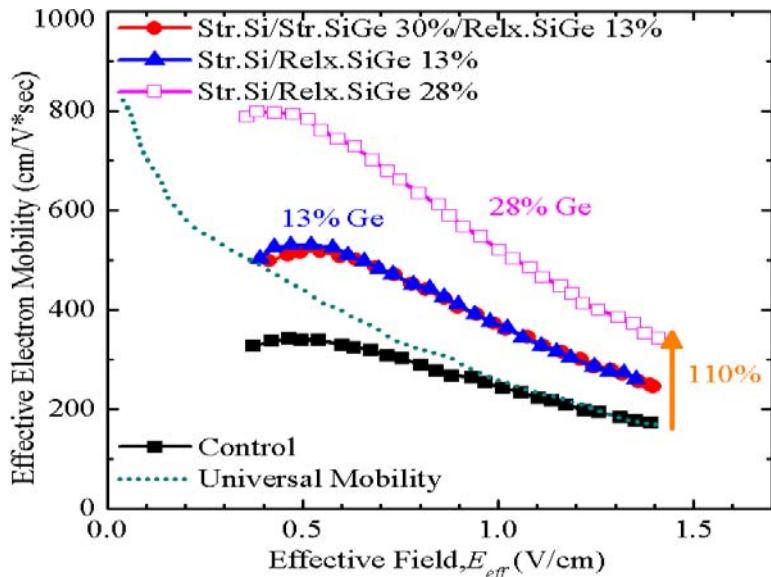

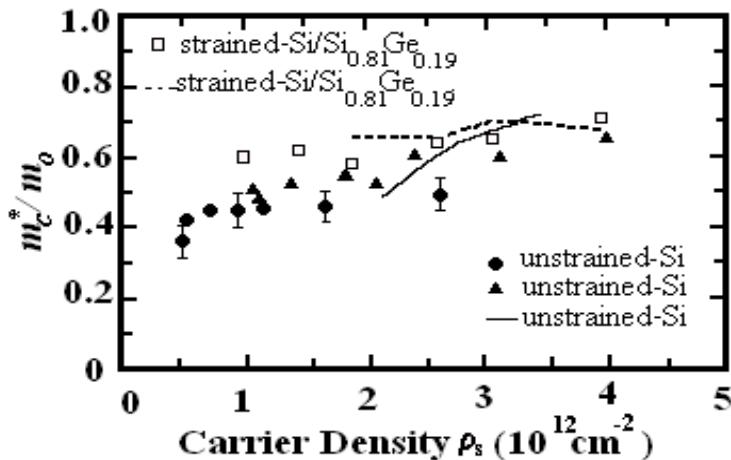

| 4.1.2             | Electron Mobility                                          | 134        |

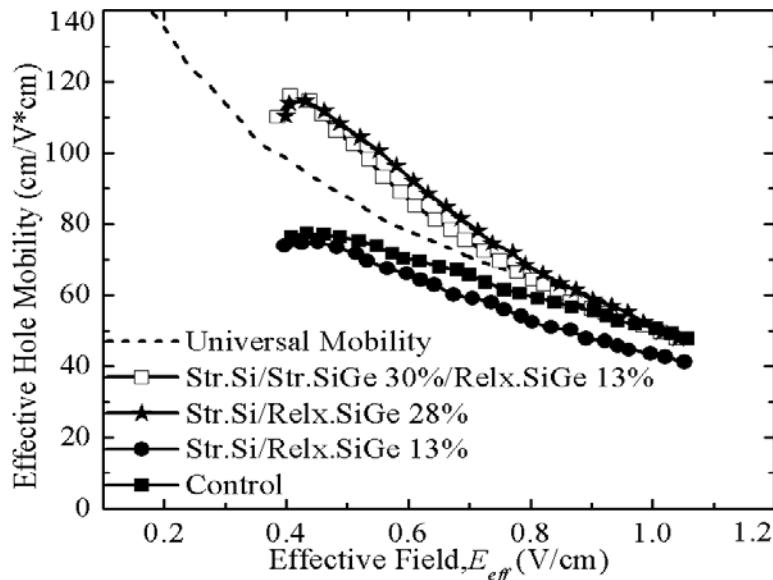

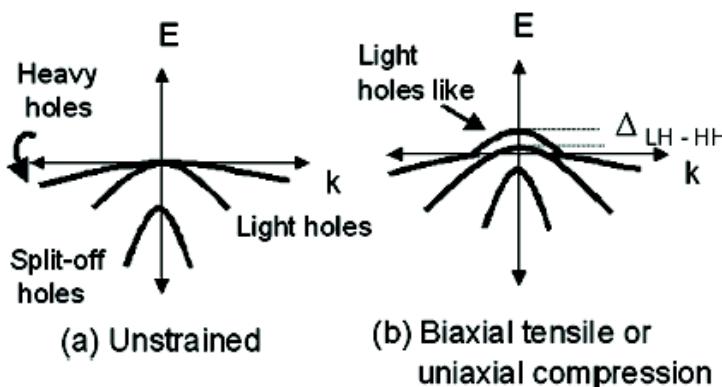

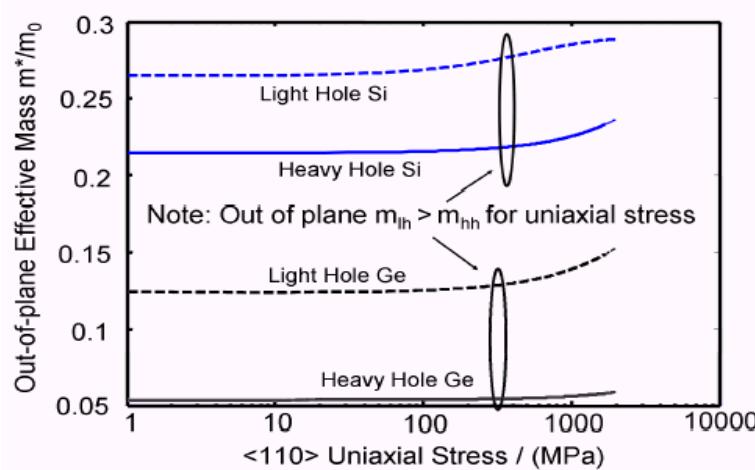

| 4.1.3             | Hole Mobility                                              | 138        |

| 4.1.4             | Field Dependence                                           | 141        |

| 4.1.5             | Doping Dependence                                          | 145        |

| 4.2               | Carrier Lifetime                                           | 146        |

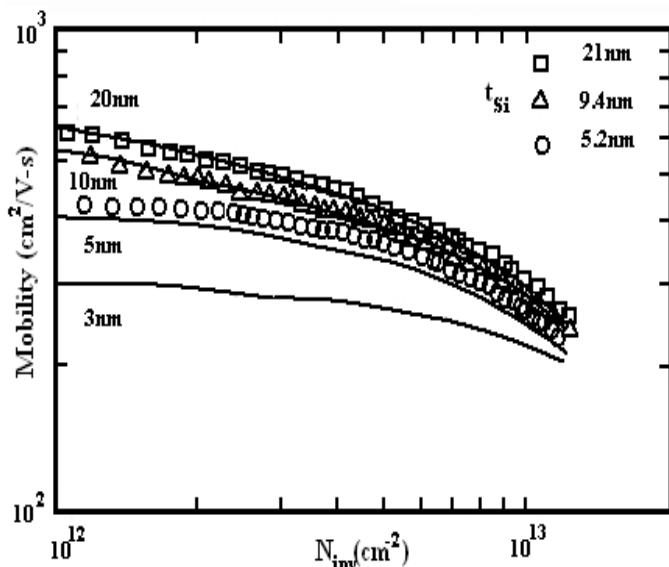

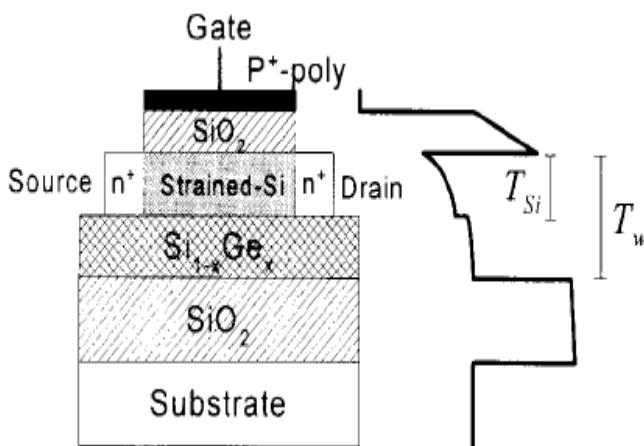

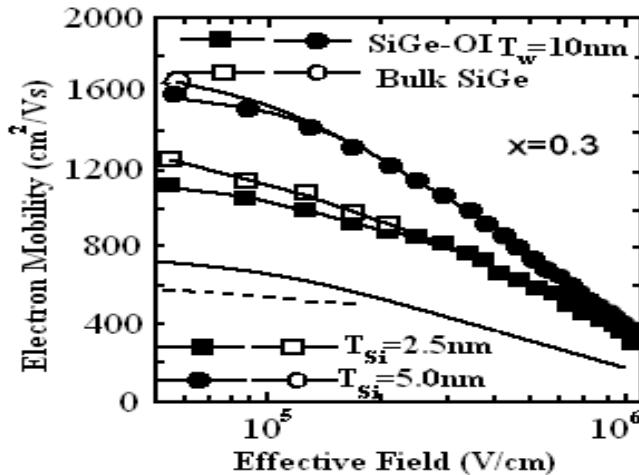

| 4.3               | Mobility: Thickness Dependence                             | 150        |

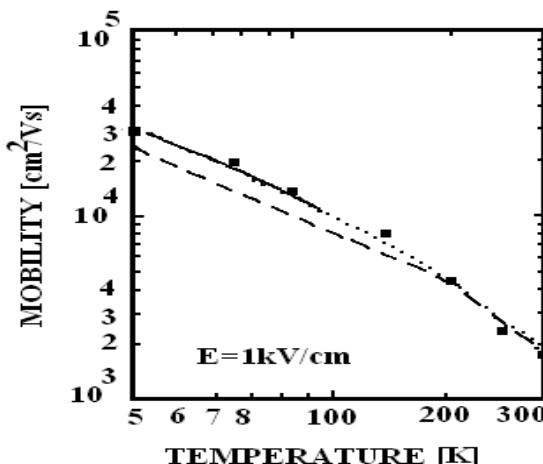

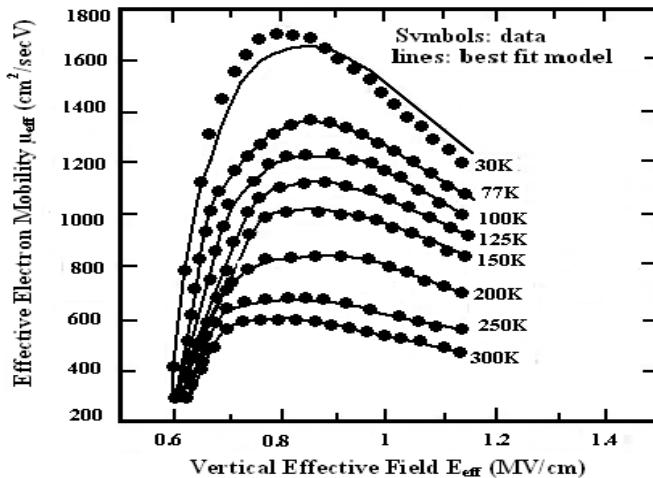

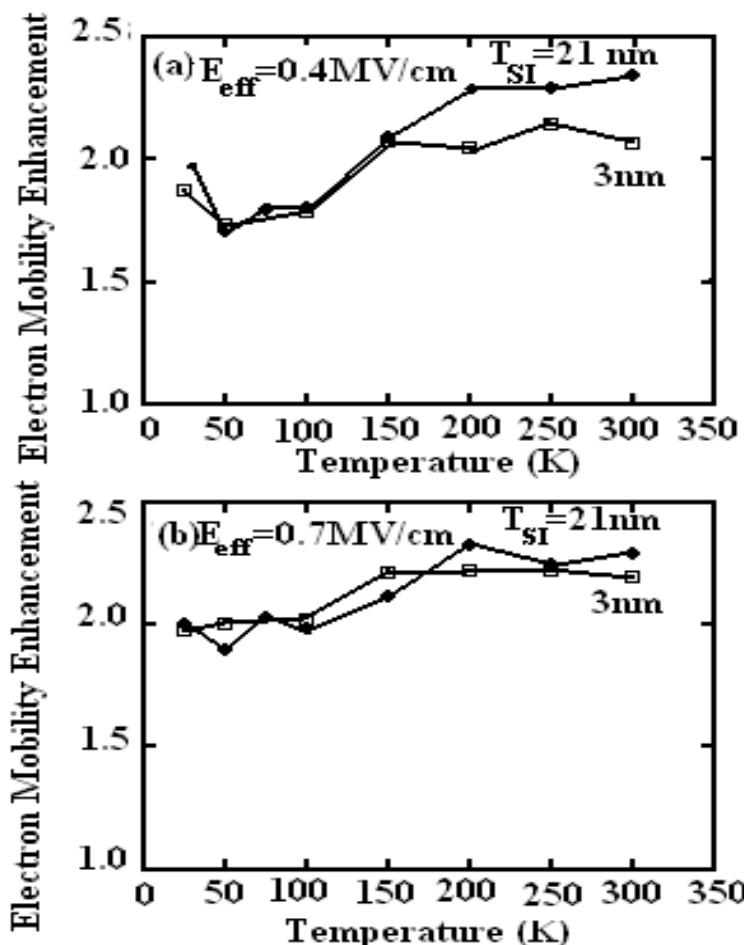

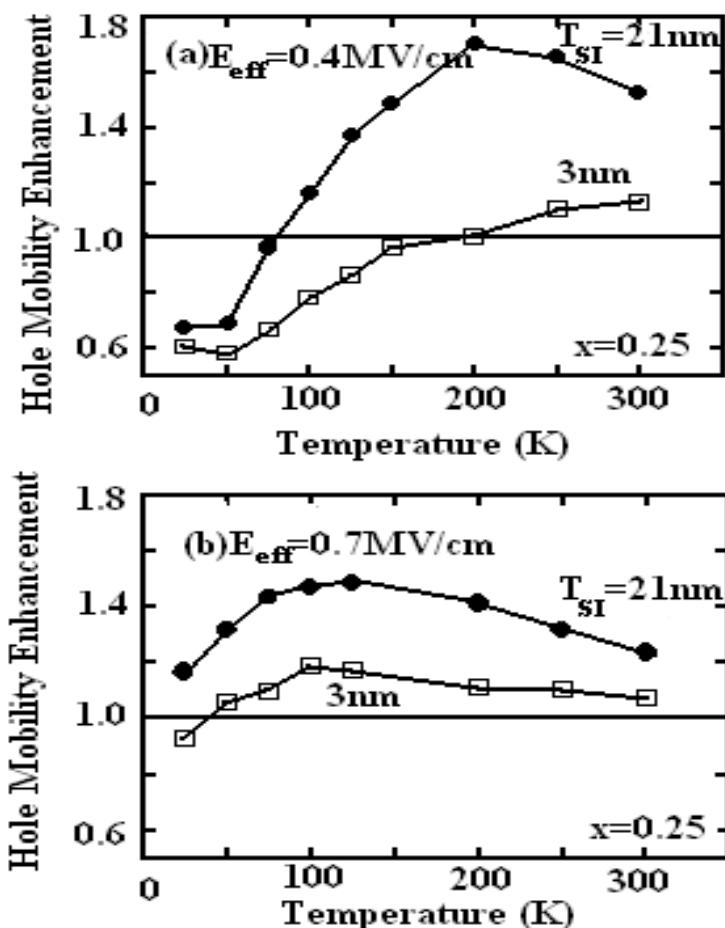

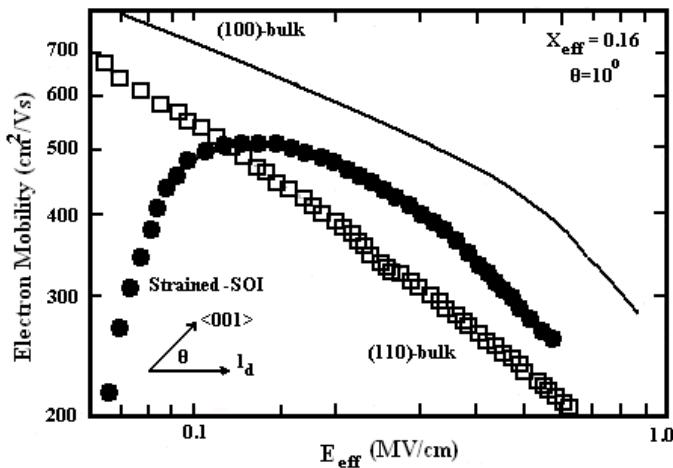

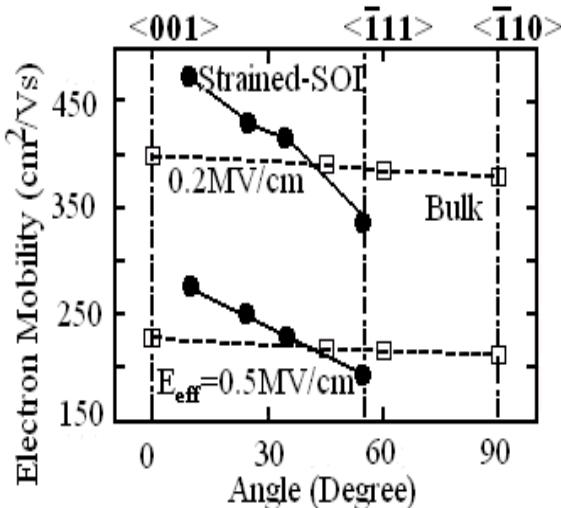

| 4.4               | Mobility: Temperature Dependence                           | 157        |

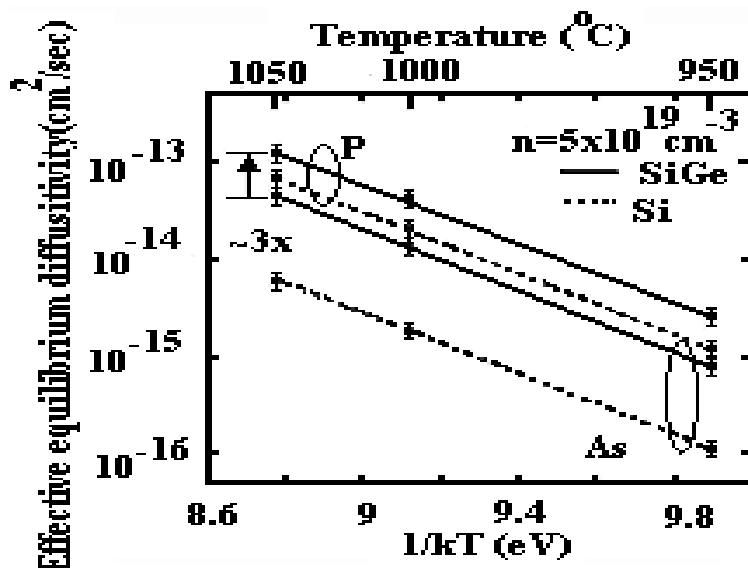

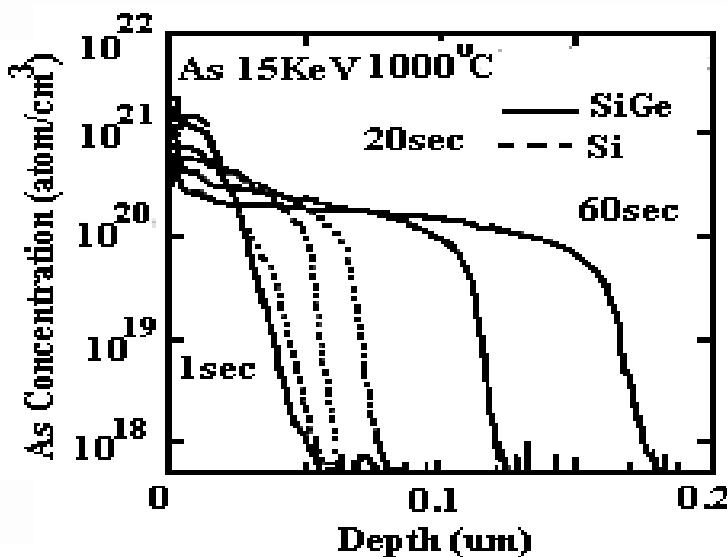

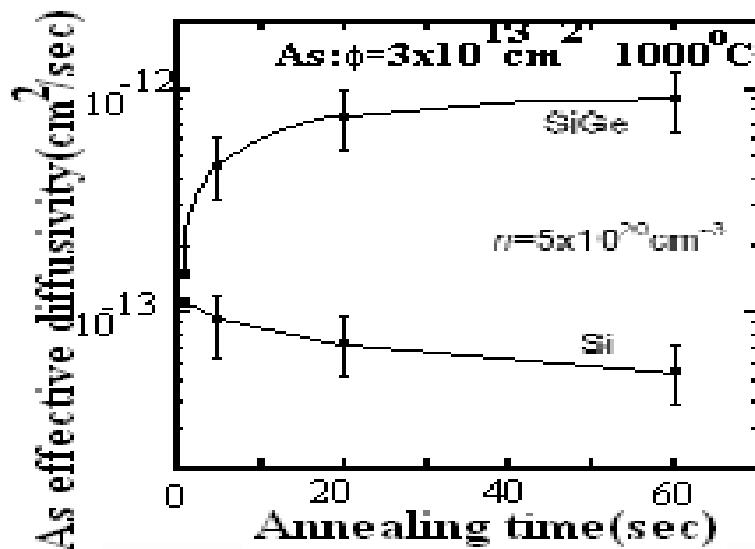

| 4.5               | Diffusion in Strained-Si                                   | 159        |

| 4.6               | Process-induced Strained-Si                                | 160        |

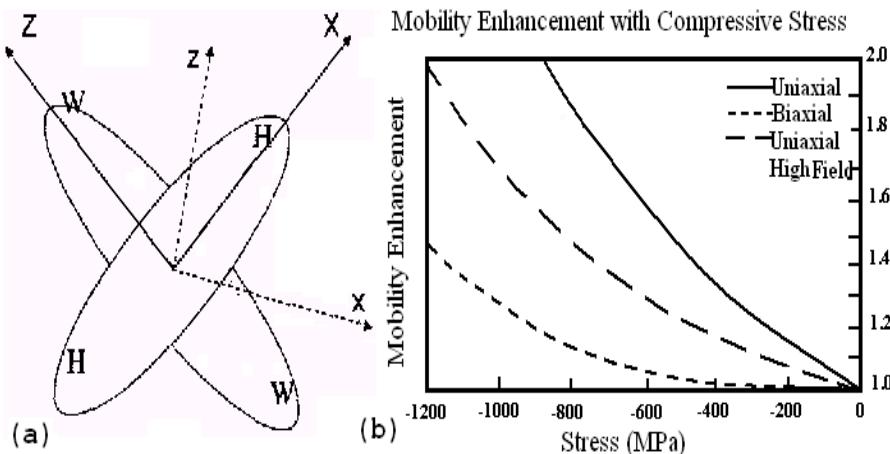

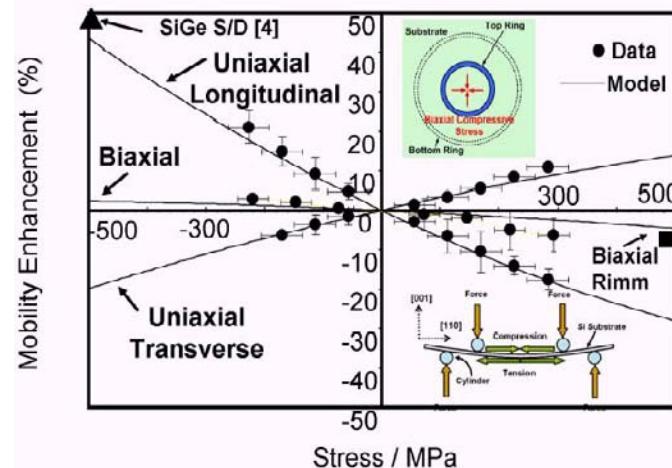

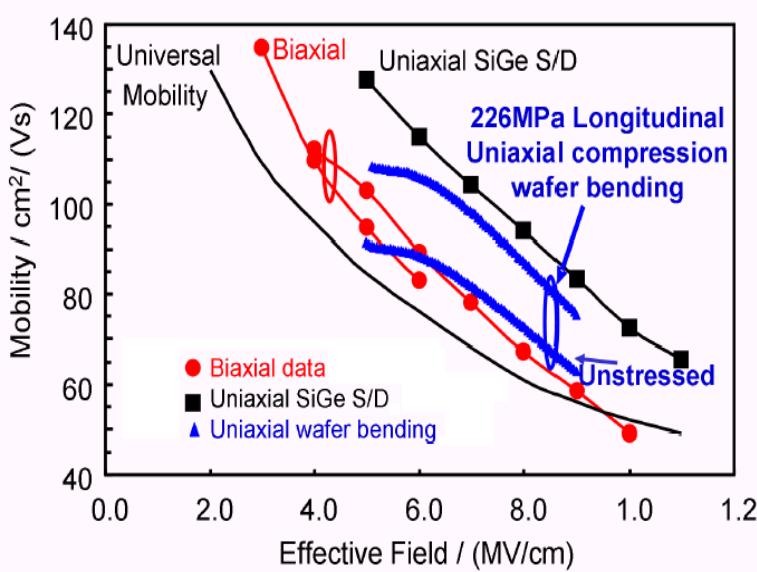

| 4.6.1             | Hole Mobility                                              | 166        |

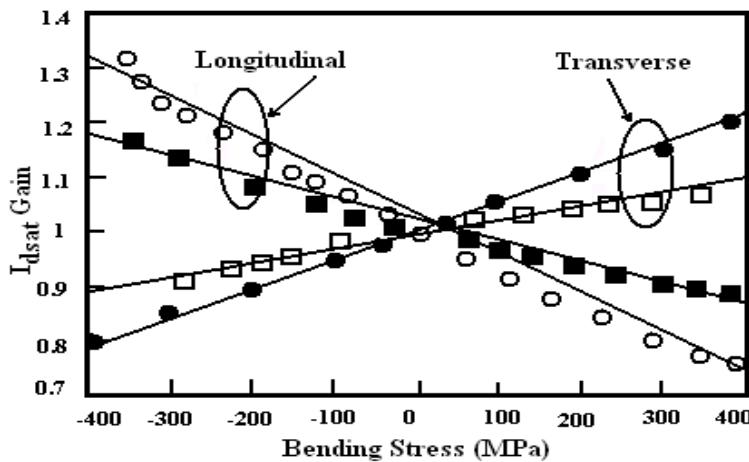

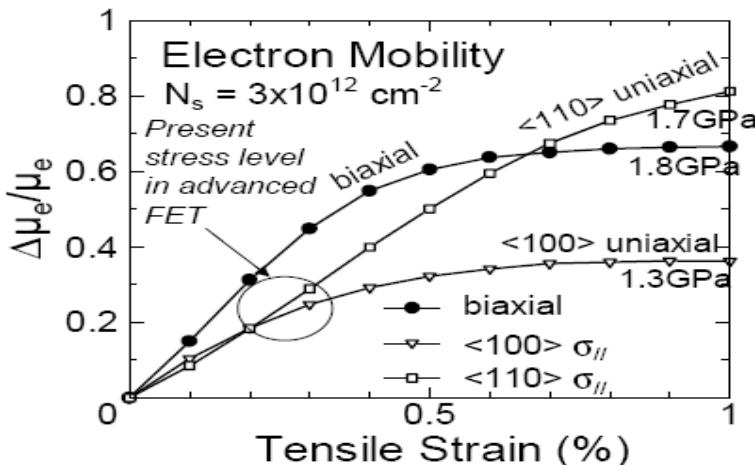

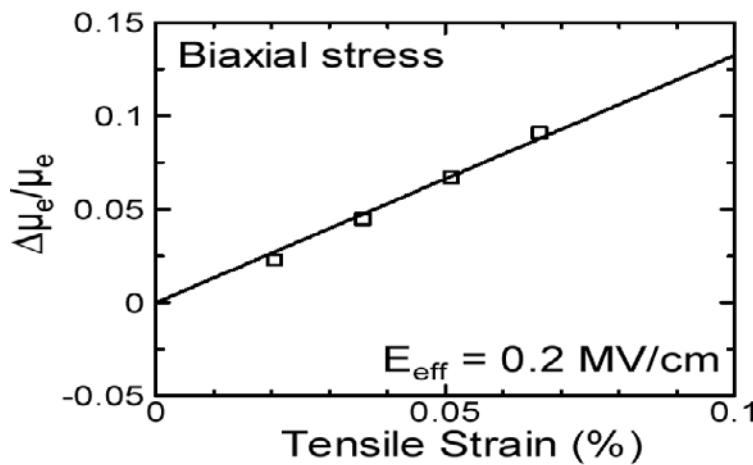

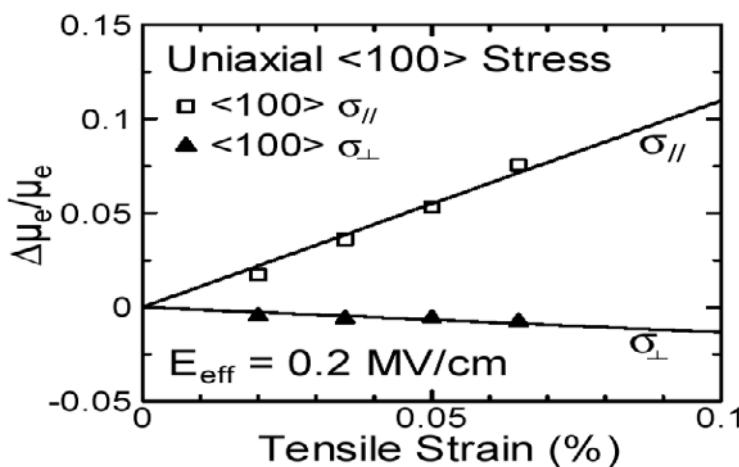

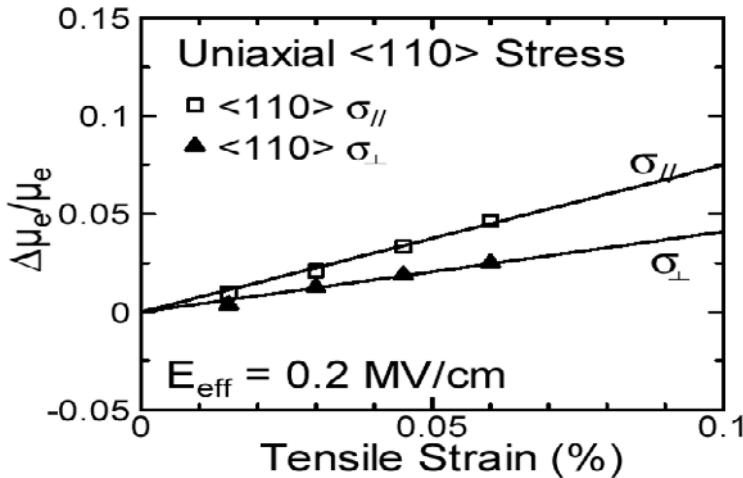

| 4.6.2             | Electron Mobility                                          | 170        |

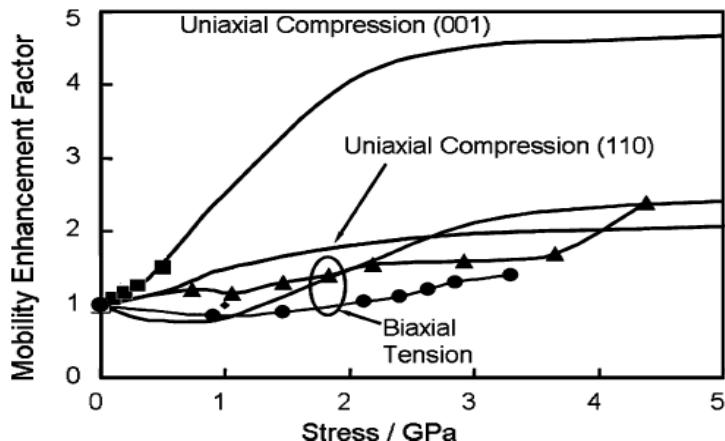

| 4.7               | Uniaxial vs. Biaxial Strain Engineering                    | 176        |

| 4.8               | Summary                                                    | 179        |

| <b>References</b> |                                                            | <b>180</b> |

| <b>5</b>          | <b>Gate Dielectrics on Engineered Substrates</b>           | <b>189</b> |

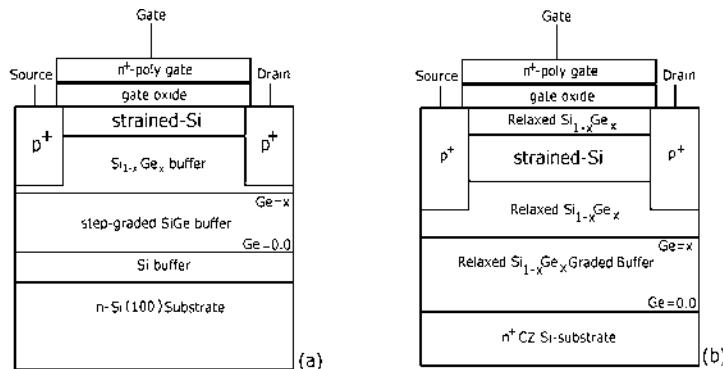

| 5.1               | Strained-Si MOSFET Structures                              | 190        |

| 5.2               | Thermal Oxidation of Strained-Si                           | 191        |

| 5.2.1             | Ge Diffusion                                               | 193        |

| 5.2.2             | Kinetics: Oxidation of $\text{Si}_{1-x}\text{Ge}_x$ Layers | 197        |

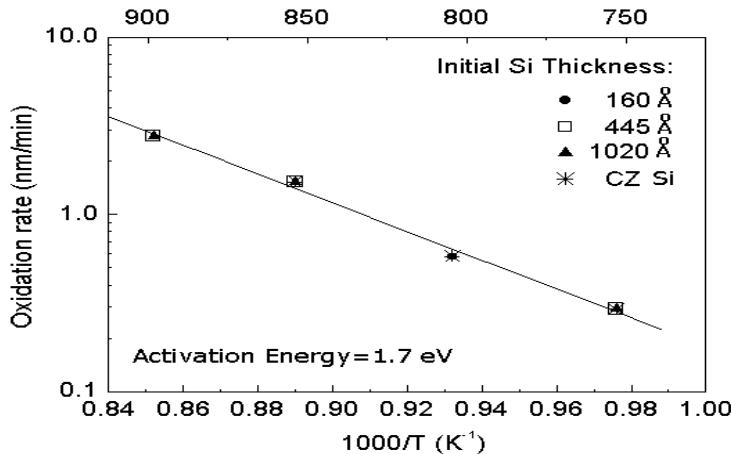

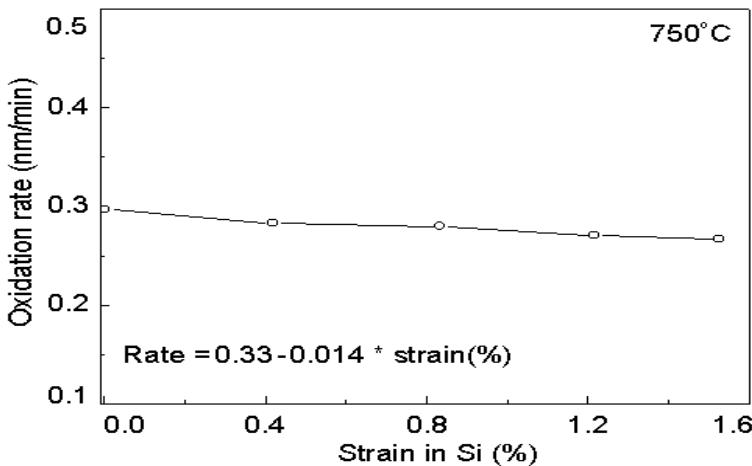

| 5.2.3             | Oxidation of Strained-Si Layers                            | 198        |

| 5.3               | Rapid Thermal Oxidation                                    | 200        |

| 5.4               | Plasma Nitridation of Strained-Si                          | 203        |

| 5.5               | Effect of Surface Roughness                                | 207        |

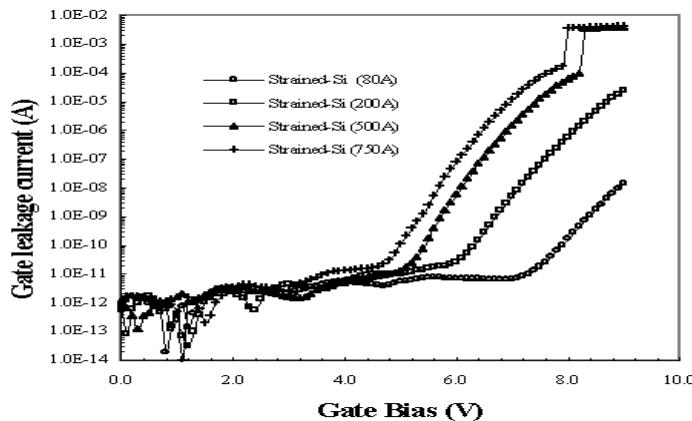

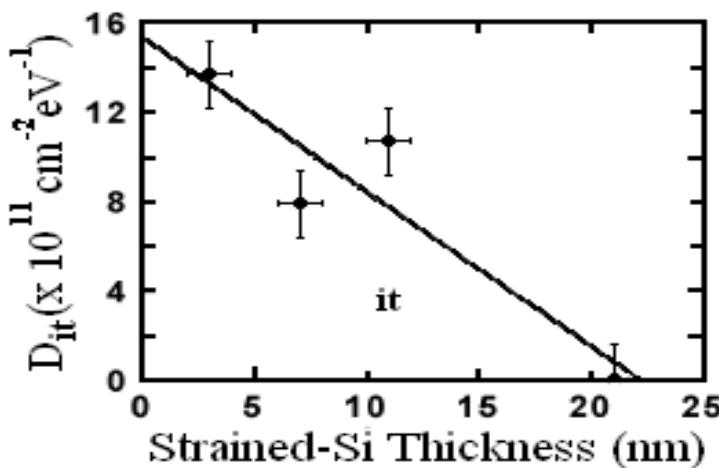

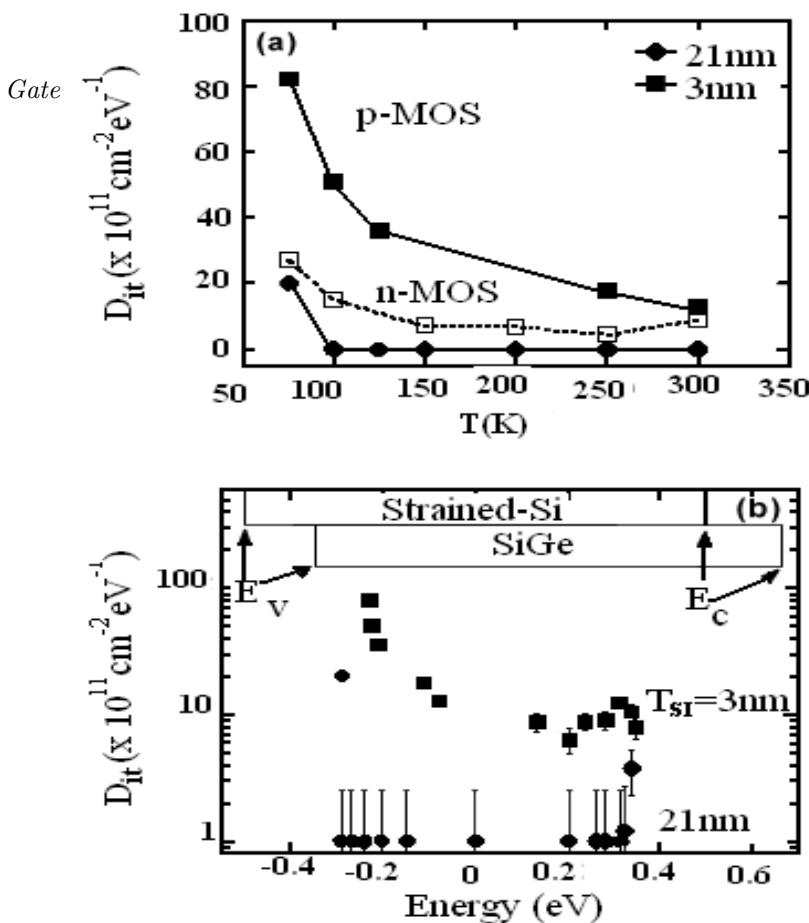

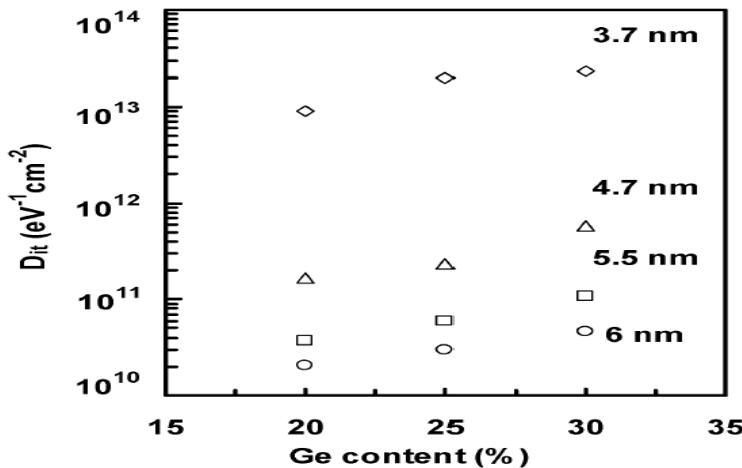

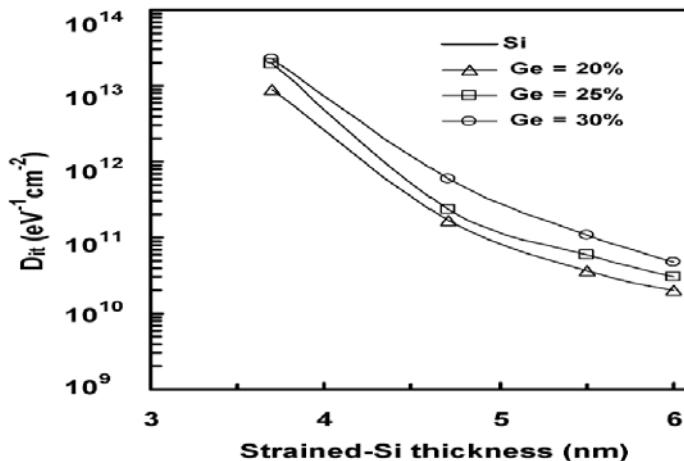

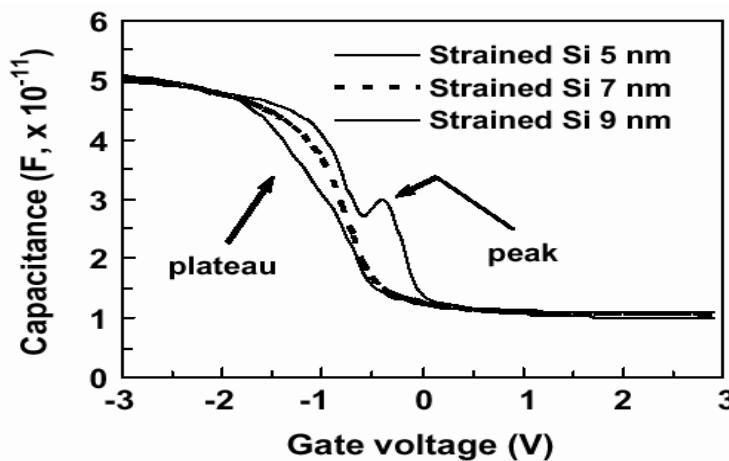

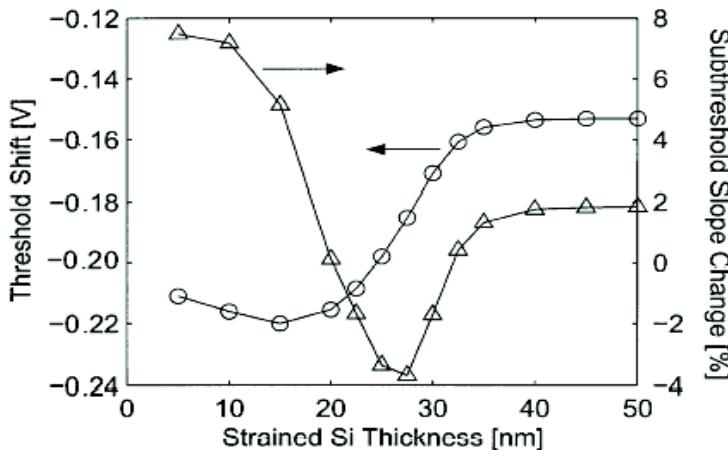

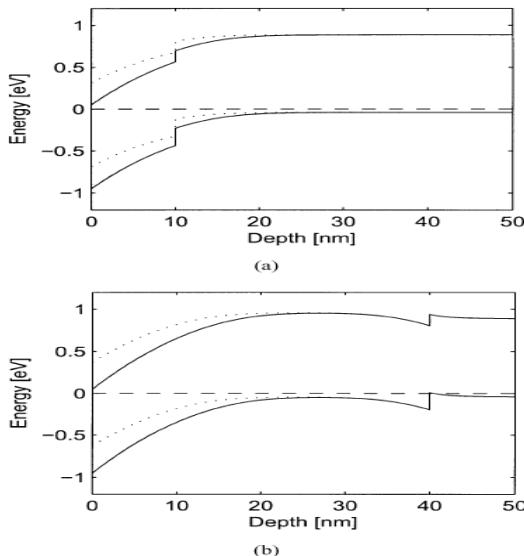

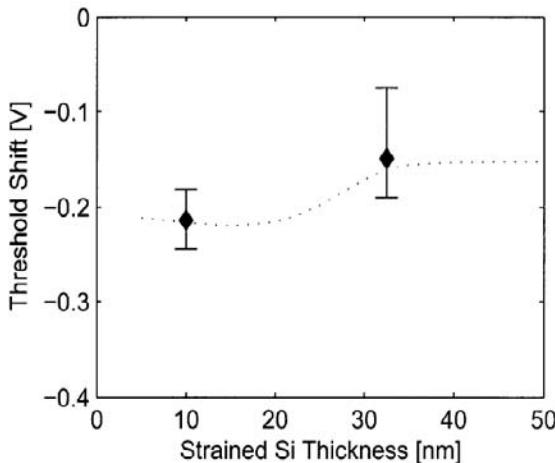

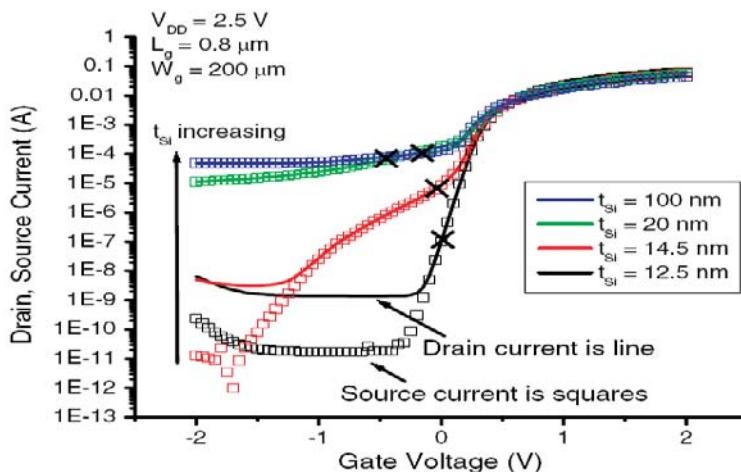

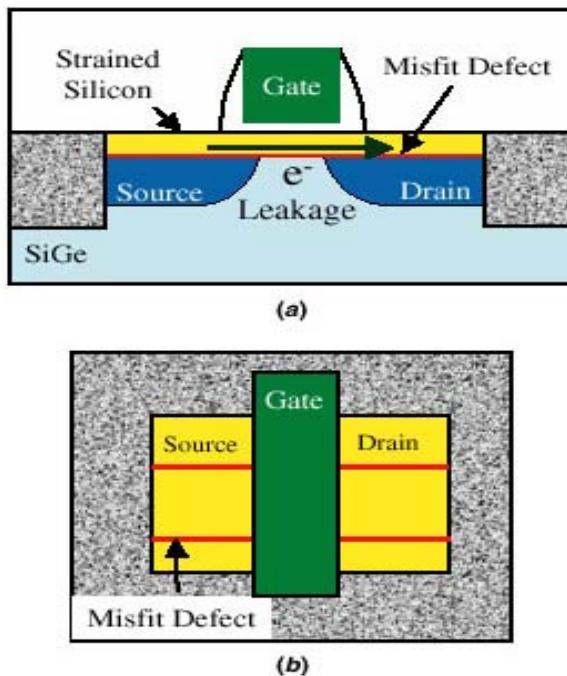

| 5.6               | Effect of Strained-Si Layer Thickness                      | 210        |

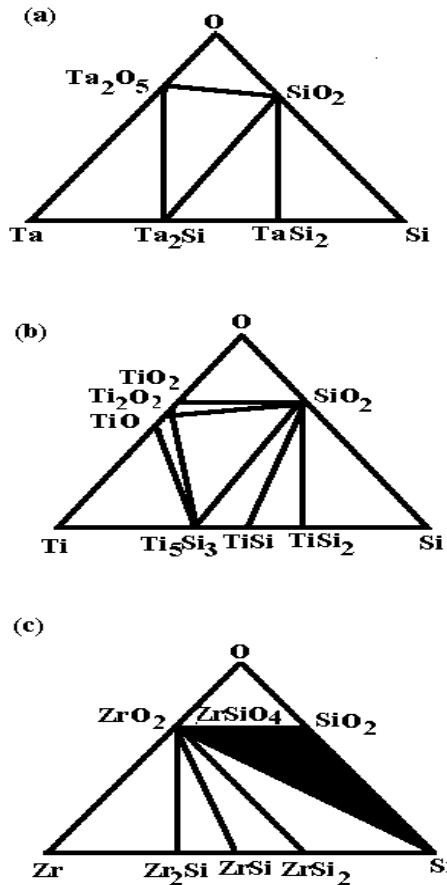

| 5.7               | High-k Gate Dielectrics on Strained-Si                     | 220        |

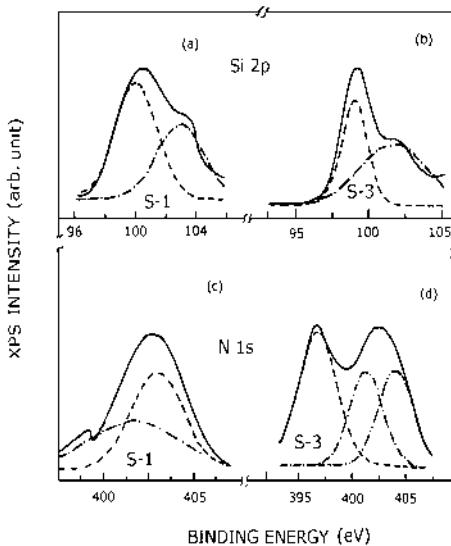

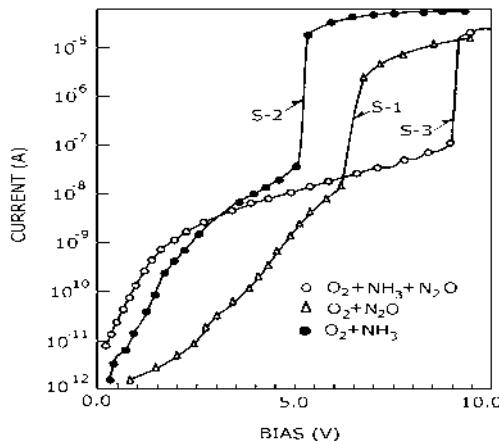

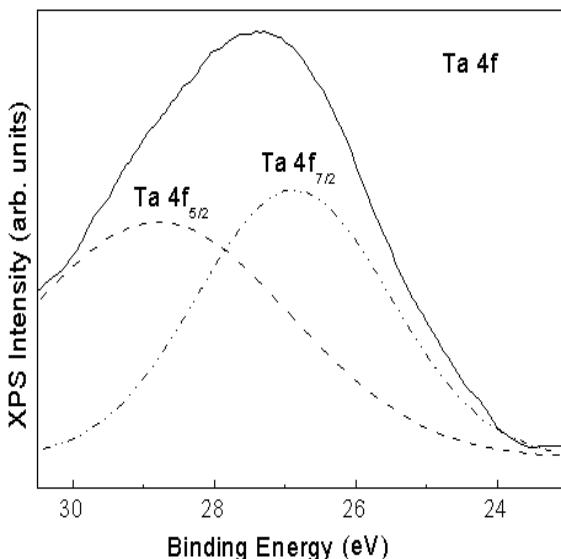

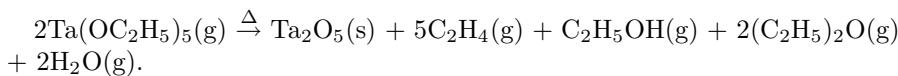

| 5.7.1             | Microwave Plasma Deposition                                | 225        |

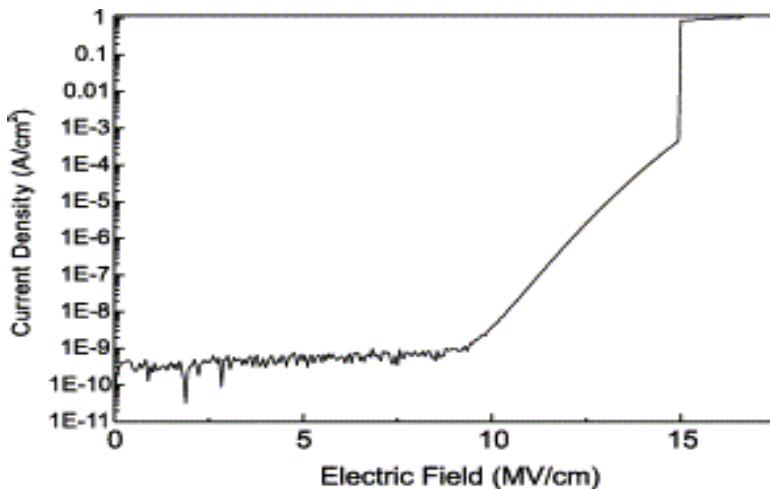

| 5.7.2             | Chemical Analysis                                          | 226        |

| 5.7.3             | Conduction Mechanism                                       | 230        |

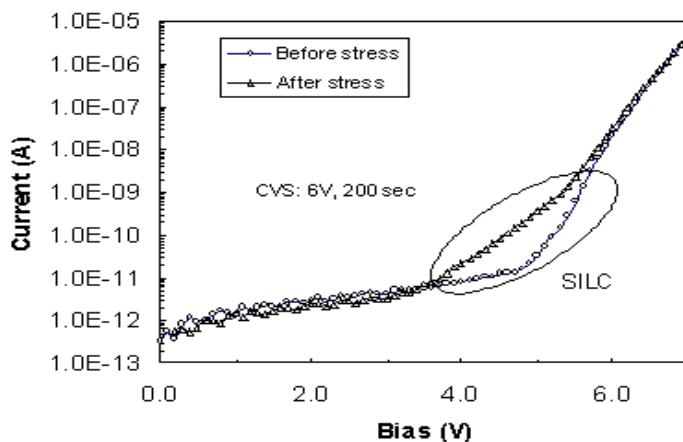

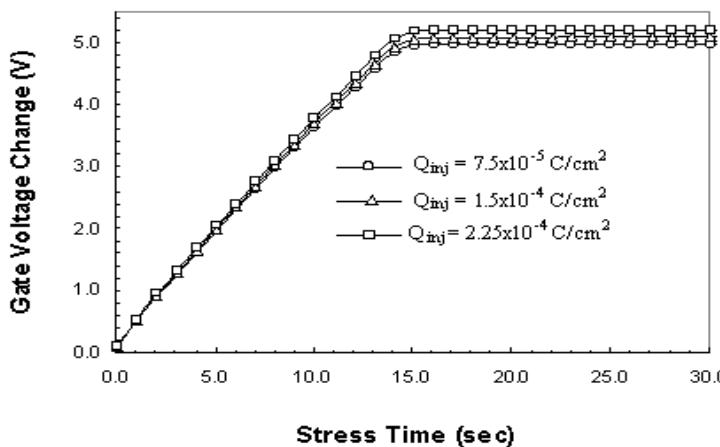

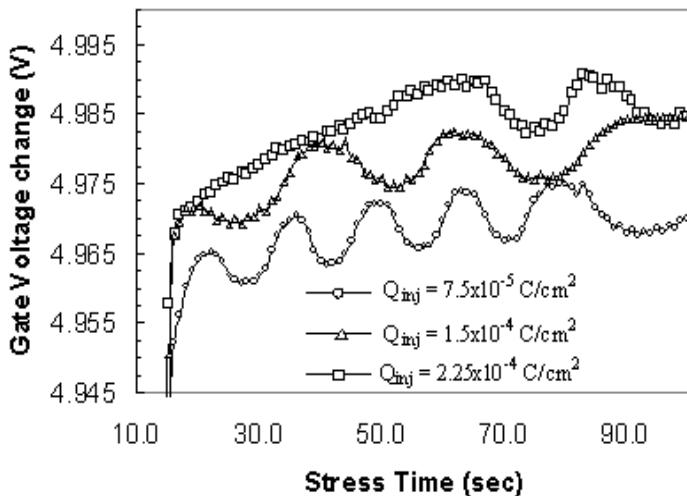

| 5.7.4             | Reliability Issues                                         | 232        |

## Table of Contents

|                   |                                                        |            |

|-------------------|--------------------------------------------------------|------------|

| 5.8               | Gate Dielectrics on Ge . . . . .                       | 234        |

| 5.9               | Summary . . . . .                                      | 234        |

| <b>References</b> |                                                        | <b>235</b> |

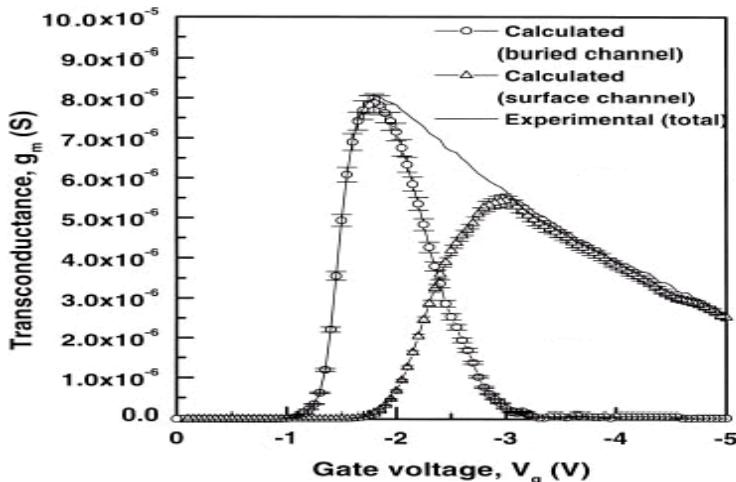

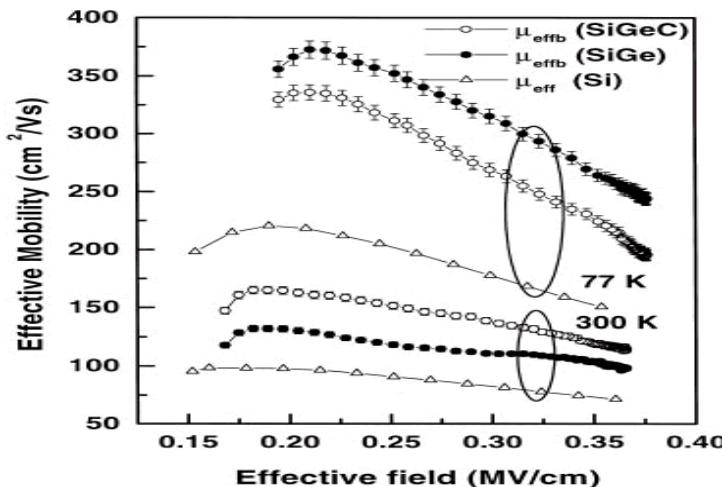

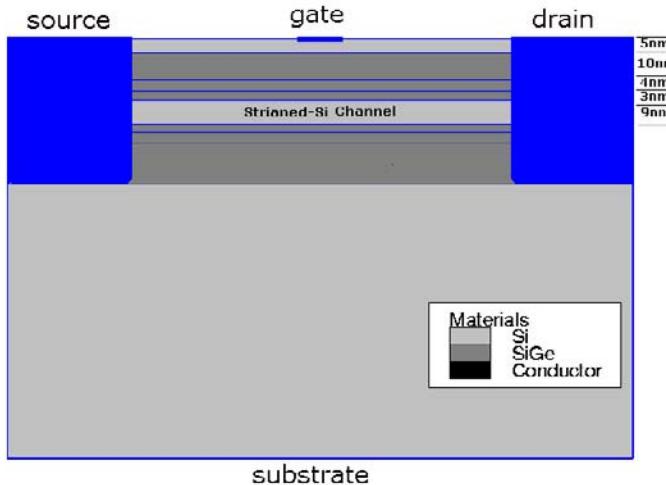

| <b>6</b>          | <b>Heterostructure SiGe/SiGeC MOSFETs</b>              | <b>245</b> |

| 6.1               | SiGe/SiGeC: Material Parameters . . . . .              | 247        |

| 6.2               | SiGe Hetero-FETs: Structures and Operation . . . . .   | 250        |

| 6.3               | SiGe p-MOSFETs on SOI . . . . .                        | 267        |

| 6.4               | SiGeC Hetero-FETs . . . . .                            | 273        |

| 6.5               | SiGe-based HEMTs . . . . .                             | 277        |

| 6.6               | Design Issues . . . . .                                | 281        |

| 6.6.1             | Gate Engineering . . . . .                             | 281        |

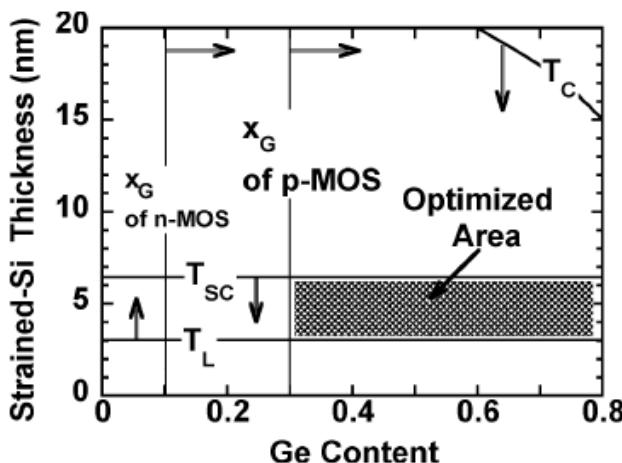

| 6.6.2             | Layer Design . . . . .                                 | 286        |

| 6.7               | Summary . . . . .                                      | 287        |

| <b>References</b> |                                                        | <b>288</b> |

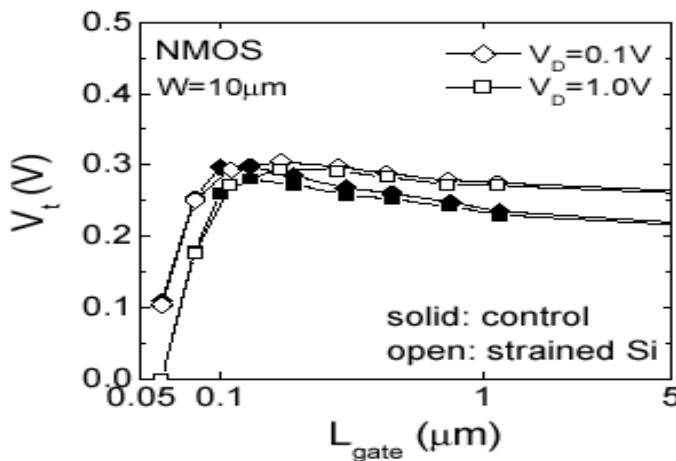

| <b>7</b>          | <b>Strained-Si Heterostructure MOSFETs</b>             | <b>295</b> |

| 7.1               | Operating Principle . . . . .                          | 296        |

| 7.1.1             | Threshold Voltage . . . . .                            | 297        |

| 7.2               | Uniaxial Stress: Process Flow . . . . .                | 306        |

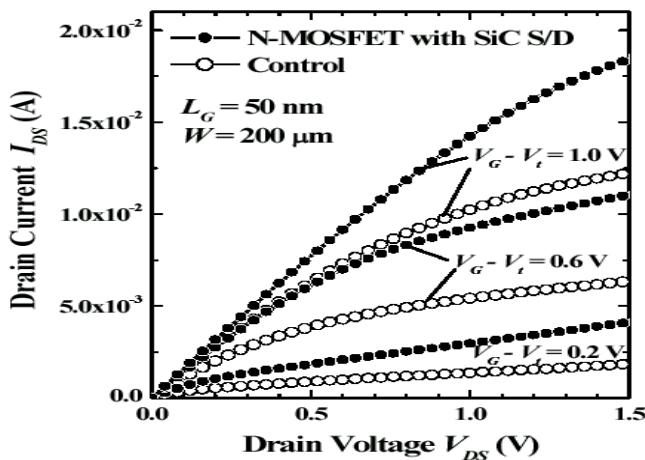

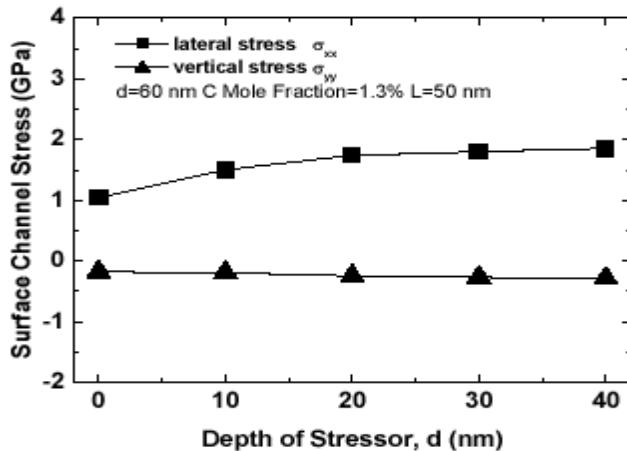

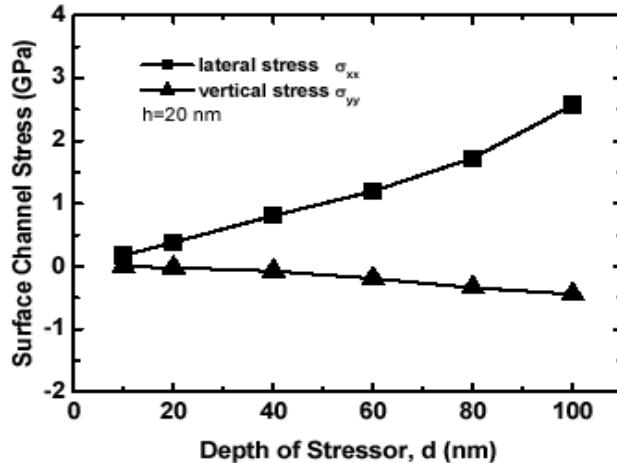

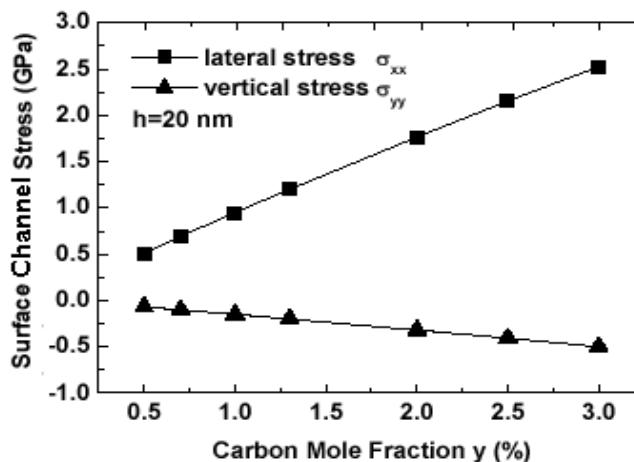

| 7.3               | Strained-Si MOSFETs with SiC-Stressor . . . . .        | 309        |

| 7.4               | Biaxial Strain: Process Flow . . . . .                 | 315        |

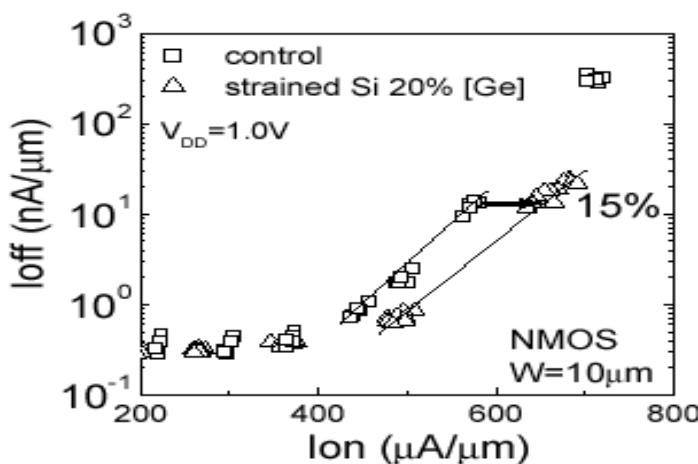

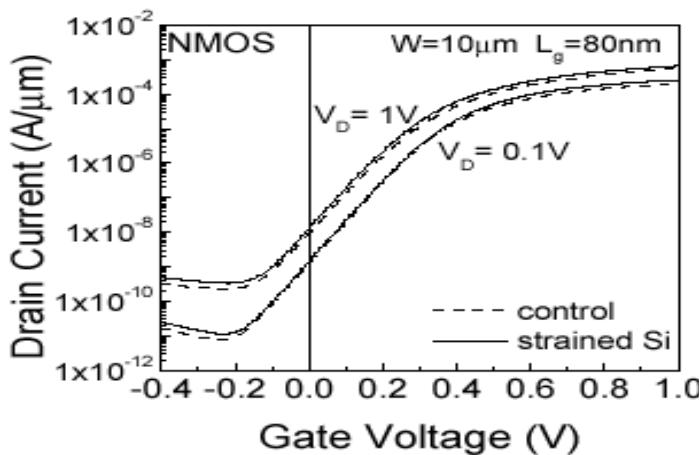

| 7.5               | Scaling of Strained-Si MOSFETs . . . . .               | 323        |

| 7.5.1             | Layout Dependence . . . . .                            | 333        |

| 7.5.2             | Thickness Dependence . . . . .                         | 338        |

| 7.5.3             | Orientation Dependence . . . . .                       | 341        |

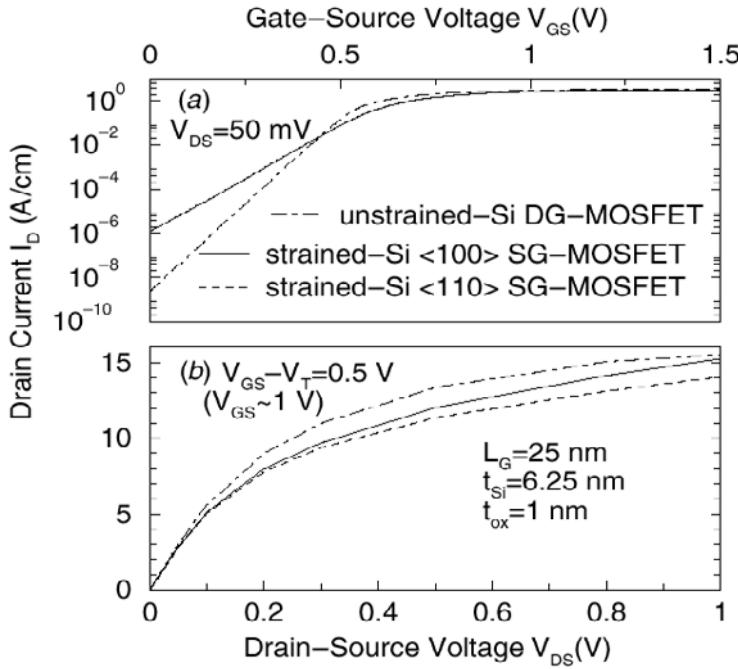

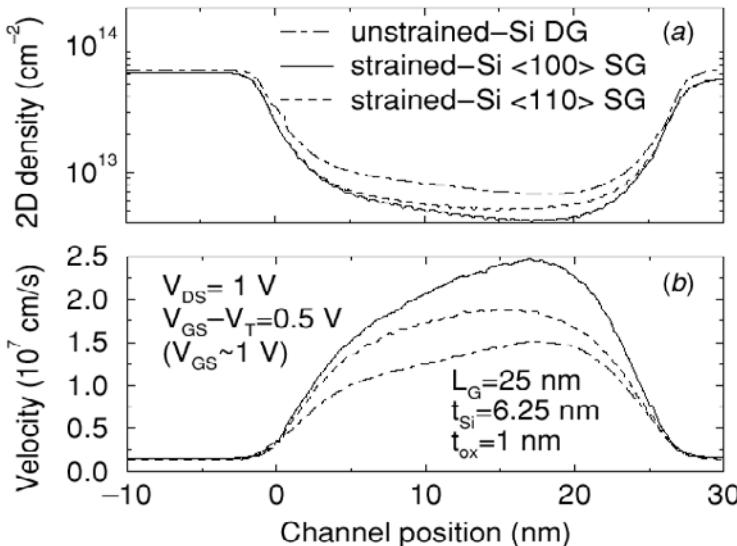

| 7.5.4             | Hetero-FETs: Single Gate vs. Double Gate . . . . .     | 344        |

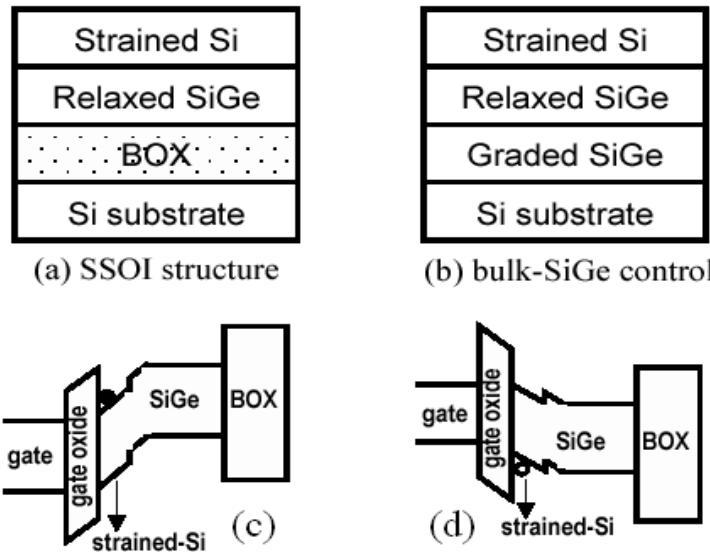

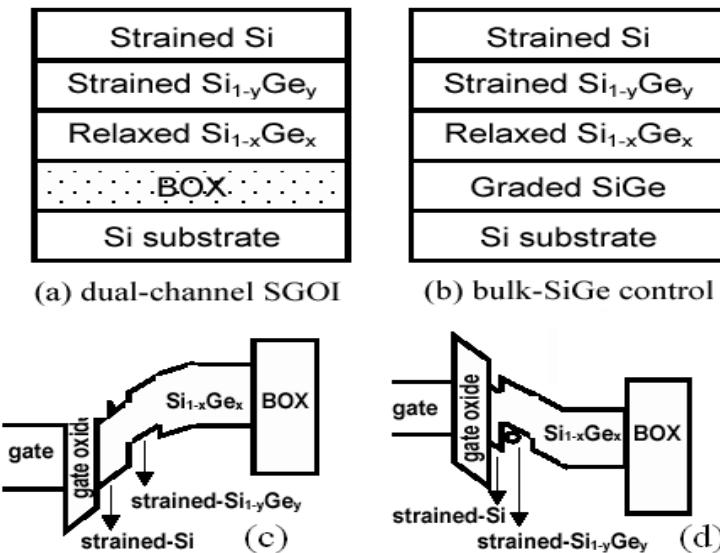

| 7.5.5             | Hetero-FET: Dual Channel Structure . . . . .           | 346        |

| 7.6               | Strained-Si MOSFETs: Reliability . . . . .             | 353        |

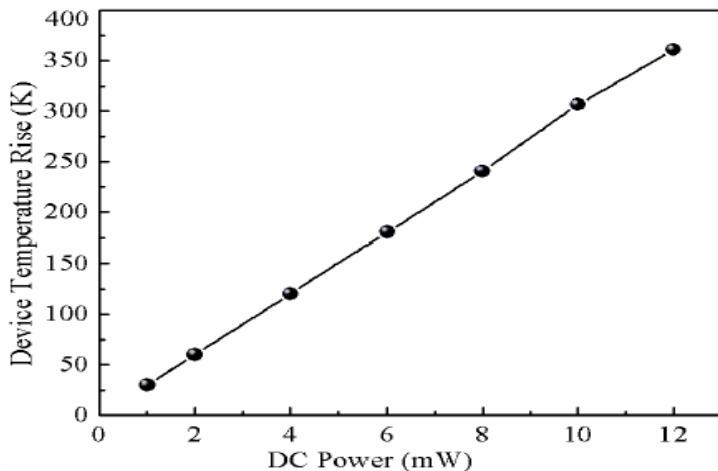

| 7.6.1             | Self-heating . . . . .                                 | 358        |

| 7.7               | Industry Example: TSMC . . . . .                       | 360        |

| 7.8               | Industry Example: AMD . . . . .                        | 370        |

| 7.9               | Summary . . . . .                                      | 371        |

| <b>References</b> |                                                        | <b>376</b> |

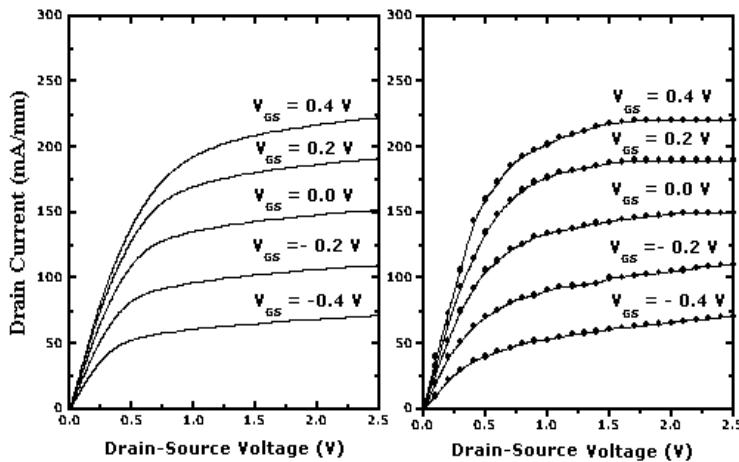

| <b>8</b>          | <b>Modeling and Simulation of Hetero-FETs</b>          | <b>385</b> |

| 8.1               | Simulation of Hetero-FETs . . . . .                    | 386        |

| 8.2               | Strained-Si Material Parameters for Modeling . . . . . | 387        |

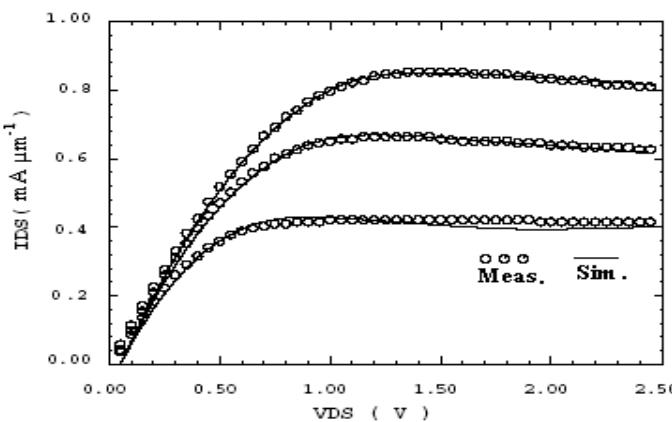

| 8.3               | Simulation of Strained-Si n-MOSFETs . . . . .          | 390        |

| 8.4               | Characterization of Strained-Si Hetero-FETs . . . . .  | 399        |

| 8.5               | TCAD: Strain-engineered Hetero-FETs . . . . .          | 400        |

| 8.6               | SPICE Parameter Extraction . . . . .                   | 409        |

|                   |                        |            |

|-------------------|------------------------|------------|

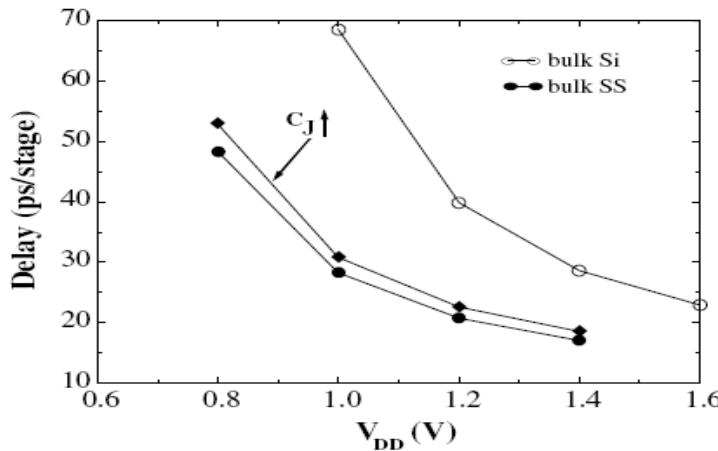

| 8.7               | Performance Assessment | 412        |

| 8.8               | Summary                | 415        |

| <b>References</b> |                        | <b>417</b> |

| <b>Index</b>      |                        | <b>421</b> |

## *Introduction*

Technology changes along the lines of materials; we had the Stone Age, the Bronze Age and the Iron Age. Maybe the last century will go down in history as the Silicon Age. The field of material sciences has always provided the innovations for new technology. Silicon has been the workhorse of the semiconductor industry over the past 50 years, the majority of the improvements in devices has been achieved via device scaling.

For the field-effect devices, as described in two patents of Lilienfeld [1, 2] and in a later patent by Heil [3], it took 35 years to turn their ideas into a usable structure where a substantial modulation of the conduction could be achieved. To reach this point fundamental insight into the characteristics of semiconductor had to be obtained. In the forties and fifties of the last century, the development of the semiconductor technology was directed toward bipolar devices, whereas field effect devices received hardly any attention. The first working metal oxide semiconductor field-effect transistor (MOSFET) became available in 1960 [4]. This foundation let the MOSFET technique live up to its potential and developed over the next 40 years into a technology of great importance for the fabrication of ever faster devices of ever-smaller dimensions at an ever-lower price.

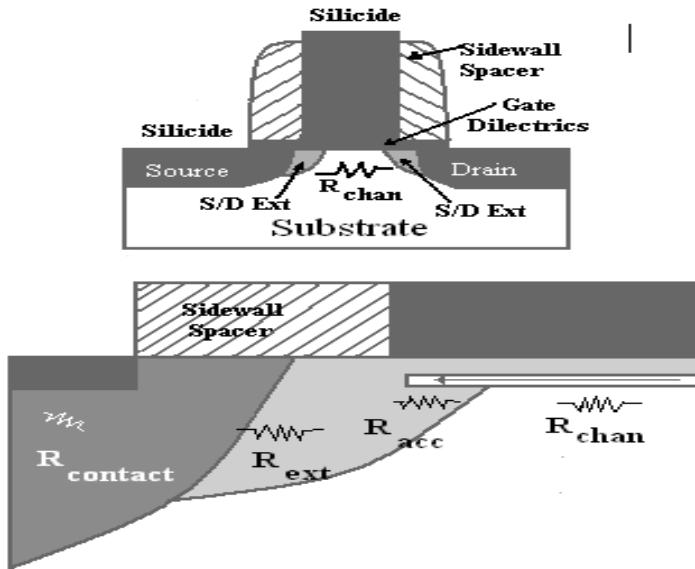

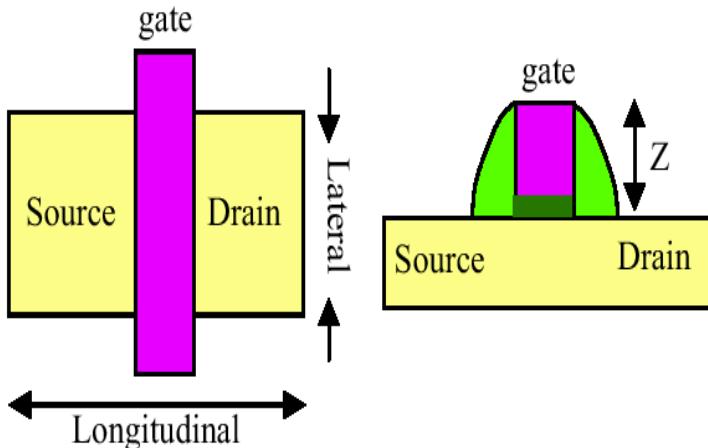

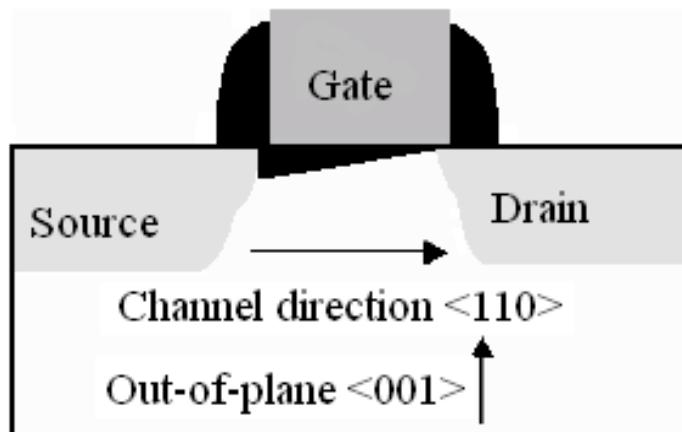

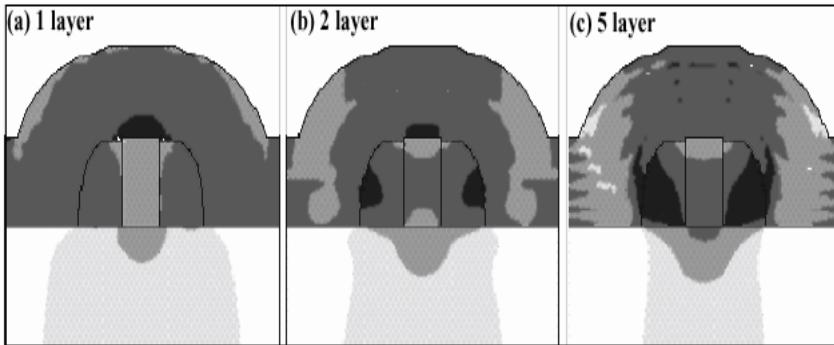

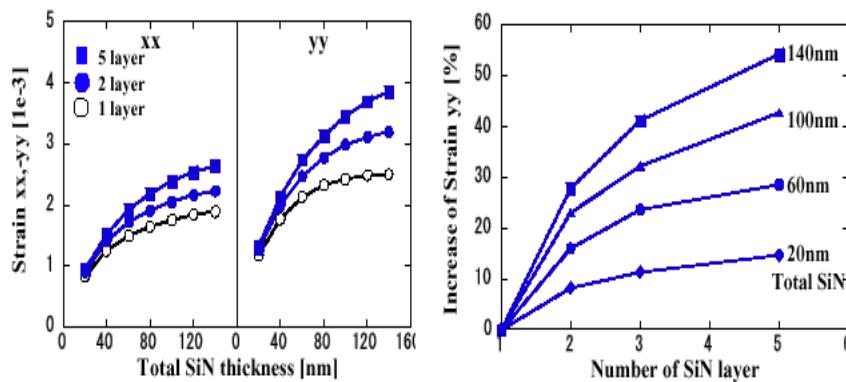

Fig. 1.1 schematically illustrates the basic MOSFET device used in today's silicon chips. The basic fabrication process steps to manufacture such a device have been broadly described in reference [5]. There are no serious competitors to replace this device in the foreseeable future. The basic structure will continue to evolve to allow continued performance improvements, but fundamental changes are unlikely in the next 10 years. The evolution of Si semiconductor technology has so far followed a trend described by Moore's law, an industry axiom that predicts that the number of transistors on a chip will double every 18 months, largely due to continued miniaturization known as scaling. Scaling involves shrinking all of the critical dimensions of the device (such as the gate or channel length and gate oxide thickness) by roughly the same factor. This in turn reduces the length of the path that electrons and holes have to travel, making the current in the devices flow faster and consume less power. Scaling is becoming more challenging with each successive technology node, as fundamental technological limits of existing processes and materials are being reached. The huge costs of scaling CMOS devices have left the Si industry at a crossroad as Si chips can no longer shrink in size.

Silicon has so far served us well, but its fundamental properties in terms

**FIGURE 1.1**

Schematic cross-section of a modern MOS transistor. After J. D. Plummer and P. B. Griffin, *Proc. IEEE*, Vol. 89, 2001(240-258). With permission.

of carrier mobility and associated intrinsic performance are limited. These limitations are now being exposed for various applications and the base Si substrate material is being replaced for many devices. Also, continued transistor scaling will not be as straightforward in the future, as fundamental limits are being reached not only in some of the key materials and processes, but most importantly in the power density of these ultrasmall devices. With gate lengths below 50-nm and gate oxides only a few atomic layers thick in modern technologies, the amount of leakage current, in particular, is beginning to dominate device behavior and limiting the capabilities of the conventional downscaling. The major technology barriers to scaling CMOS and improving performance now are: scaling power supply voltage, sustaining low leakage current, and increasing drive current.

As scaling of Si CMOS is approaching its limits, innovative device structures and materials are actively being investigated to boost the performance. Manufacturing practices in the Si CMOS industry are currently experiencing difficulty, where new approaches are necessary in order to maintain improved product capability within reasonable economic constraints. When approaching the 22-nm technology node, advanced device structures will be needed to overcome fluctuation problems associated with the small number of dopants in the active region. While the new devices are expected to be highly innovative, they still have to satisfy the fundamental criteria of functional scalability

**TABLE 1.1**

Evolution of CMOS technology.

| Technology node<br>μm | Year | Metal<br>level | Supply<br>voltage (V) | Oxide<br>thickness (Å) | V <sub>t</sub> (V) |

|-----------------------|------|----------------|-----------------------|------------------------|--------------------|

| 0.7                   | 1988 | 2              | 5.0                   | 200                    | 0.7                |

| 0.5                   | 1992 | 3              | 3.3                   | 120                    | 0.6                |

| 0.35                  | 1994 | 5              | 3.3                   | 75                     | 0.5                |

| 0.25                  | 1996 | 6              | 2.5                   | 65                     | 0.45               |

| 0.18                  | 1999 | 7              | 1.9                   | 50                     | 0.40               |

| 0.12                  | 2001 | 8              | 1.5                   | 40                     | 0.30               |

| 90-nm                 | 2004 | 8-9            | 1.0                   | 35                     | 0.25               |

and economic viability.

The improved transport properties of new channel materials, such as strained-Si, SiGe, Ge and III-V semiconductors, along with new device designs, such as dual-gate, tri-gate or FinFETs, are expected to enhance the performance of nanoscale CMOS devices. Novel process techniques, such as atomic layer deposition (ALD), high-k dielectrics, and metal gates are now being used in exploratory device structures. New materials in the channel promise reduced series resistance and higher drive currents. As the end of the Si roadmap is approached, strained-Si channel will offer a way to improve the MOSFET drive current along with transistor downscaling.

Current nanometer-scaled MOSFETs are true short-channel devices, the structure of which has to withstand drain-induced barrier lowering (DIBL) without exceeding the maximum source-drain leakage current that can be tolerated by the application. Devices dimensions are now well into tens of nanometer regime and serious doubts are being raised regarding the ability to scale down the gate length of conventional bulk-Si MOSFET below 30 nm. Because the subthreshold slope and built-in potentials cannot be scaled, the threshold voltage cannot be reduced too much without the leakage current becoming excessive. Although the total power dissipation could be managed by forced cooling, the power dissipation through drain-to-source and gate-to-channel leakage currents will become increasingly detrimental to circuit operation and will limit overall performance.

Table 1.1 shows a set of key MOSFET parameters and their evolution with time and the technology node. It is important to note that there has been a tremendous increase in number of metal interconnects leading to increased circuit density and reduction in power supply voltage with lower power consumption. Reduction in the gate oxide thickness down to atomic scale values, although increasing the speed, leads to higher leakage current. The power supply decrease is the consequence of the reduction of the MOS gate oxide thickness, which, however, induces a lower oxide breakdown voltage. One also notices the slow decrease of the threshold voltage of the MOS devices. The results indicate that even if highly idealized device structures are assumed,

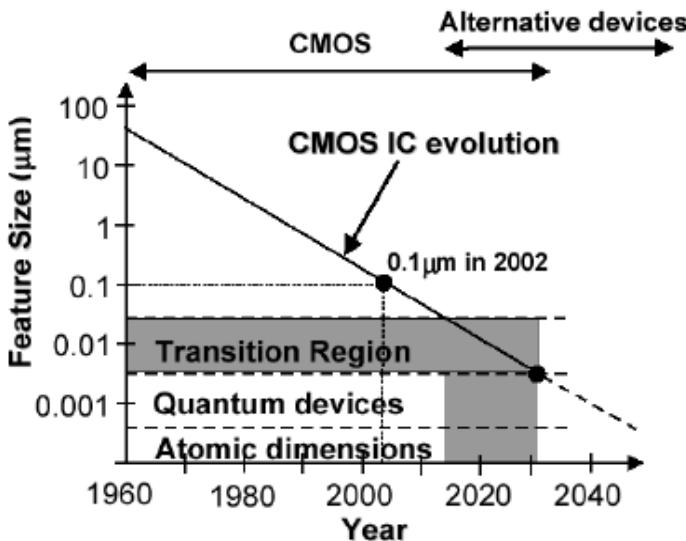

**FIGURE 1.2**

Feature size vs. time in silicon ICs. After J. D. Plummer and P. B. Griffin, *Proc. IEEE*, Vol. 89, 2001(240-258). With permission.

only limited improvements over the conventional MOSFETs can be achieved by the channel engineering techniques. Most of the history represented in Fig. 1.2 has been achieved with MOS transistors, and with a limited number of materials such as Si, SiO<sub>2</sub>, Al, Si<sub>3</sub>N<sub>4</sub>, TiSi<sub>2</sub>, TiN, and W. Fig. 1.2 summarizes the trends in feature size over time.

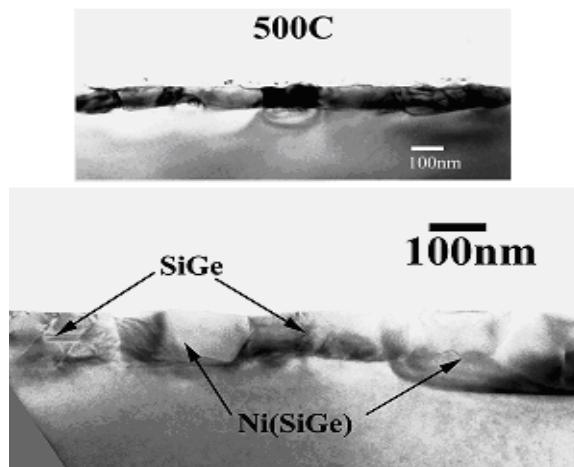

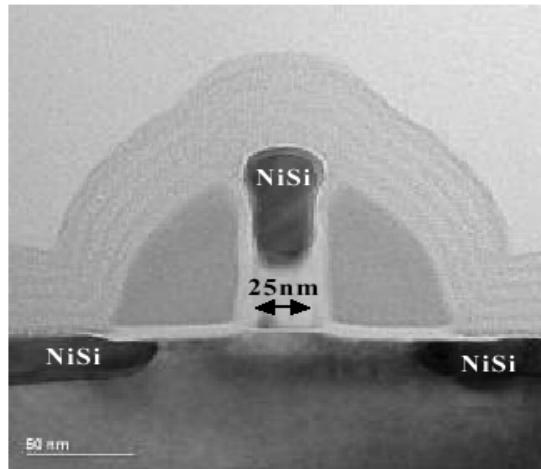

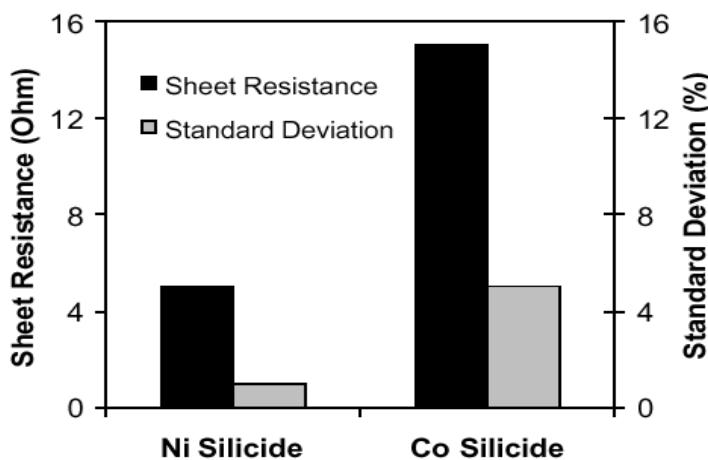

Recently a 65-nm generation logic technology with 1.2-nm physical gate oxide, 35-nm gate length, enhanced channel strain, NiSi, 8 layers of Cu interconnect, and low-k interlayer dielectric (ILD) for dense high performance logic has been reported [6]. Transistor gate length is scaled down to 35-nm while not scaling the gate oxide as a means to improve performance and reduce power. Increased nMOS and pMOS drive currents are achieved by enhanced channel strain and junction engineering. The supply voltage cannot be scaled as fast as the dimensions of the devices, resulting in larger electric fields and reliability issues. Because the subthreshold slope and built-in potentials cannot be scaled, the threshold voltage cannot be reduced too much without the leakage current becoming excessive.

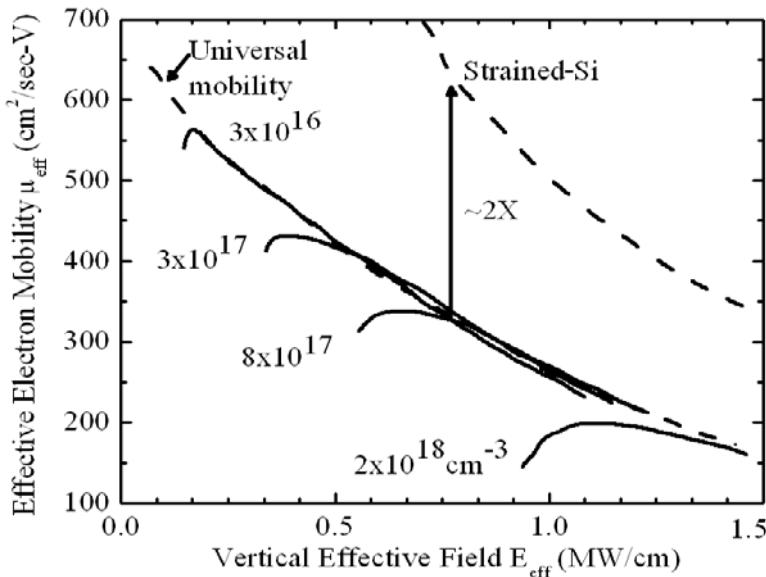

Higher channel dopant concentrations and more abrupt, shallower source-drain (SD) junctions have been used to control short-channel effects (SCE) at very short gate lengths. Doping requires quite precise profile design and process control, whereas increasing channel doping concentration degrades carrier mobility, lowering the drain current. Statistical fluctuation of channel

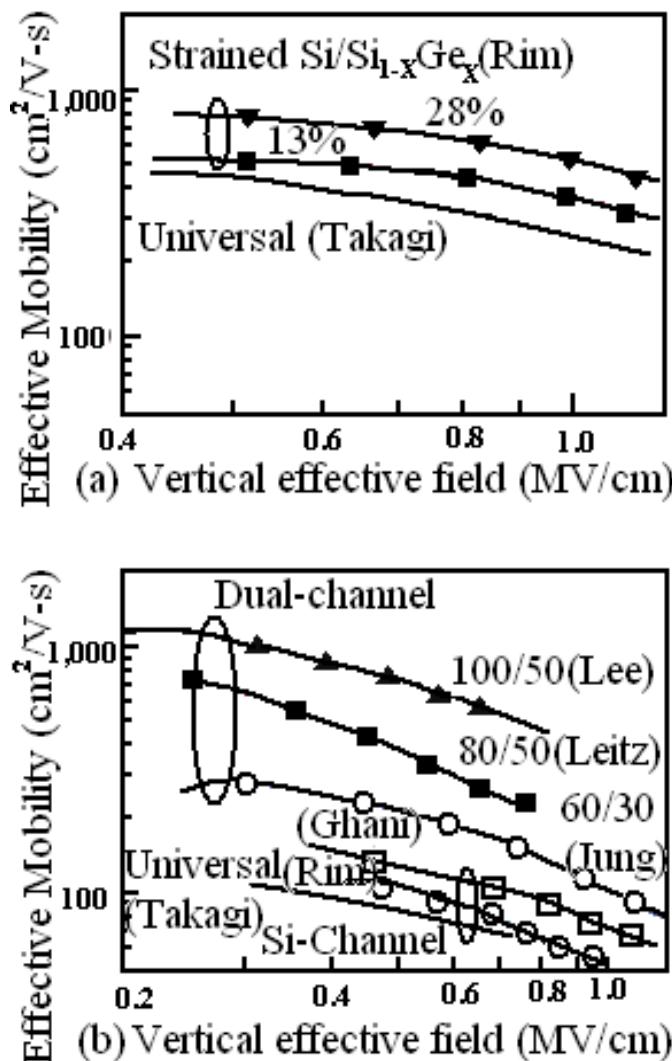

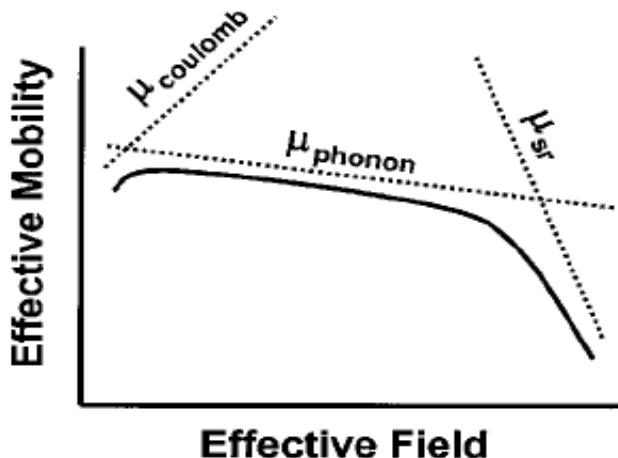

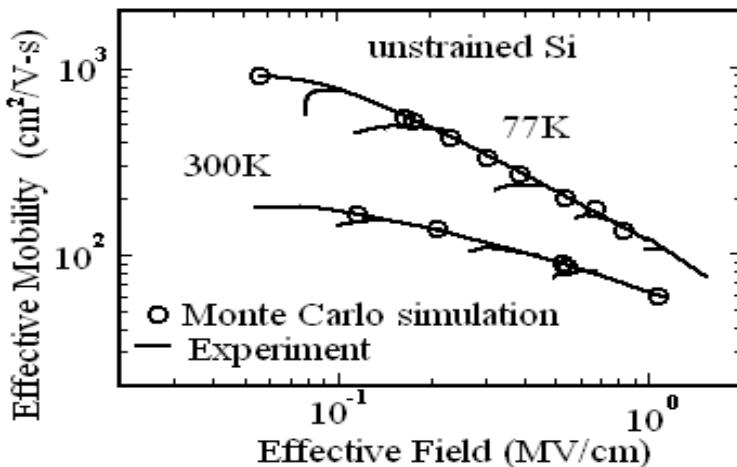

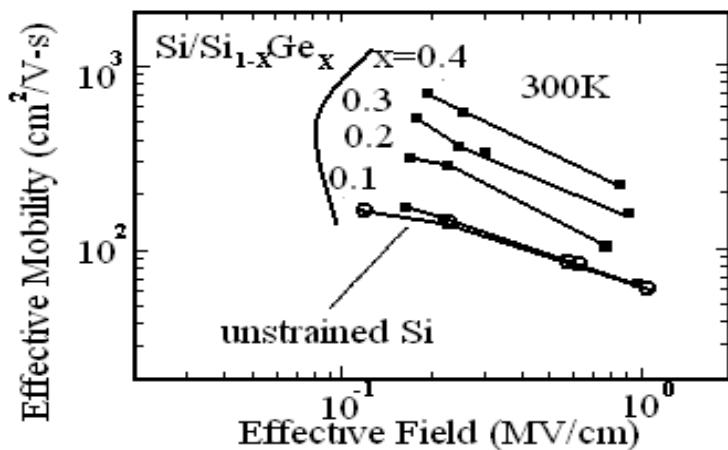

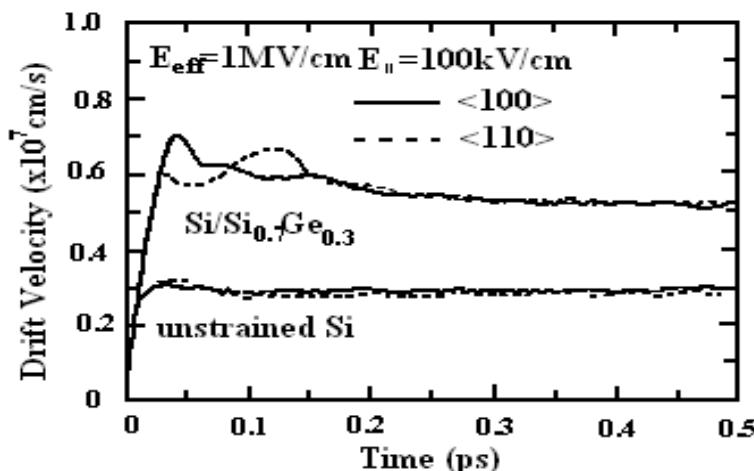

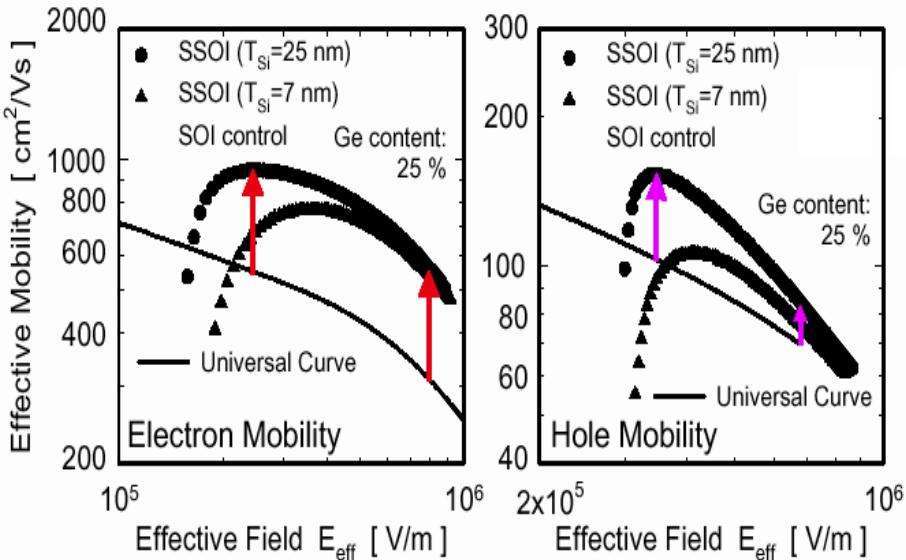

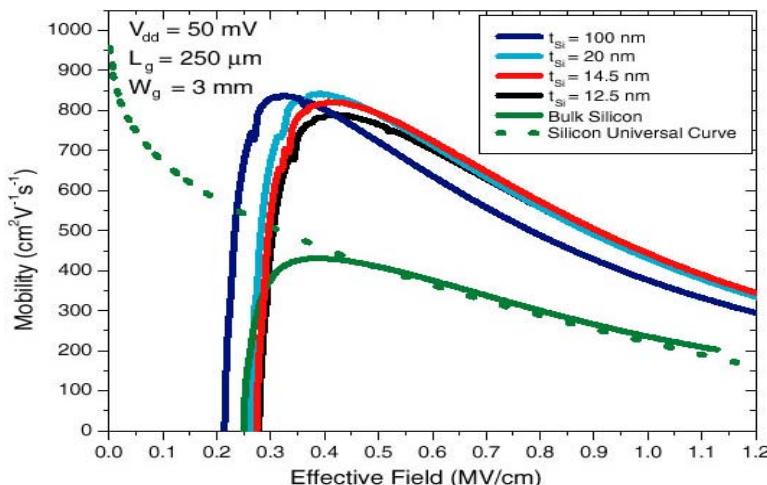

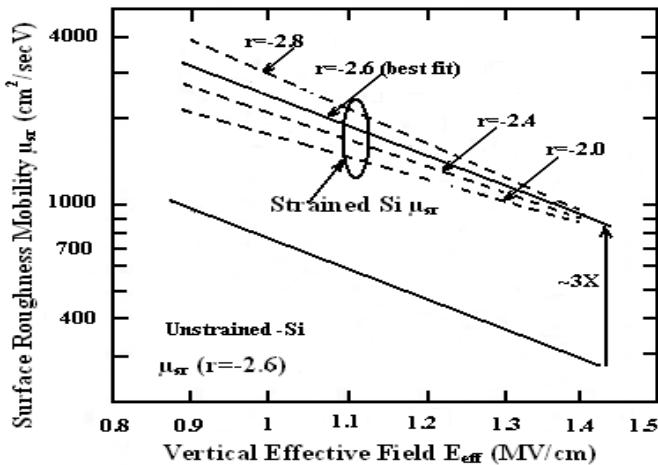

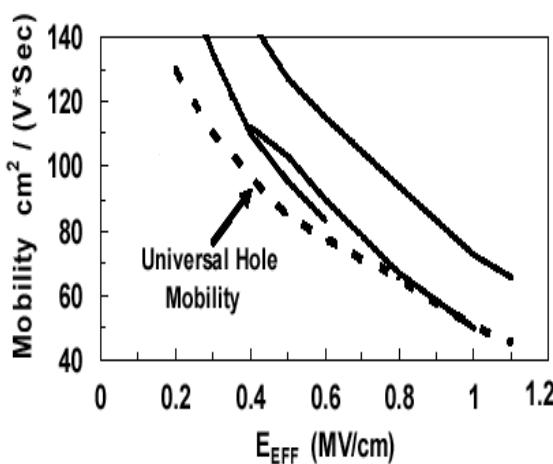

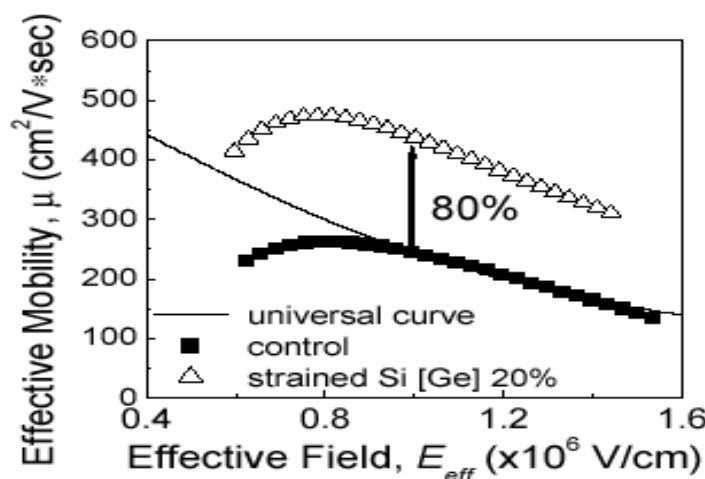

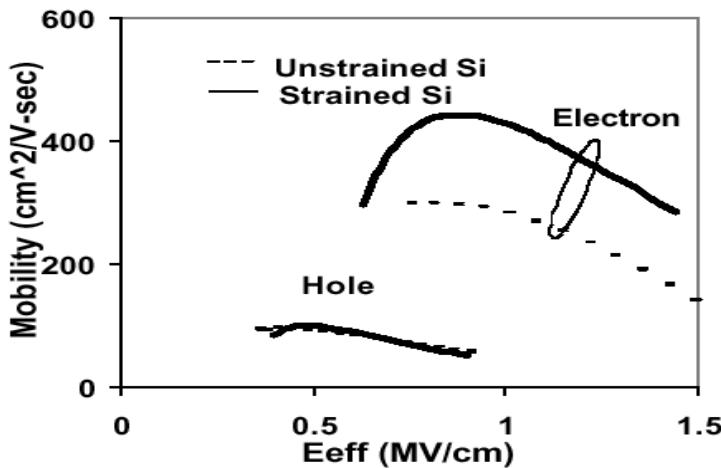

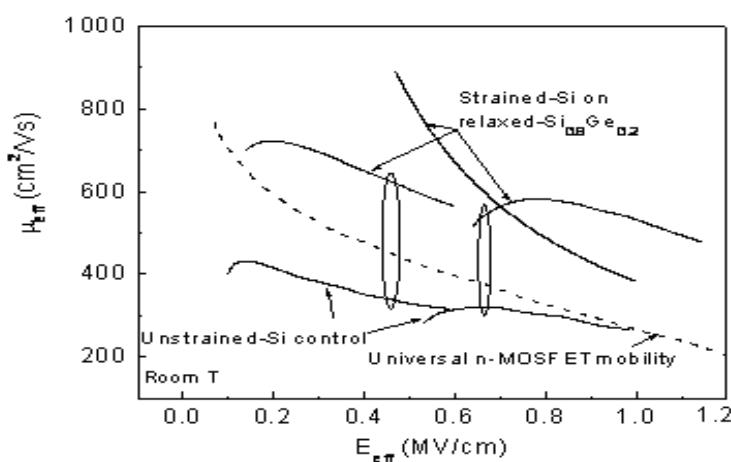

**FIGURE 1.3**

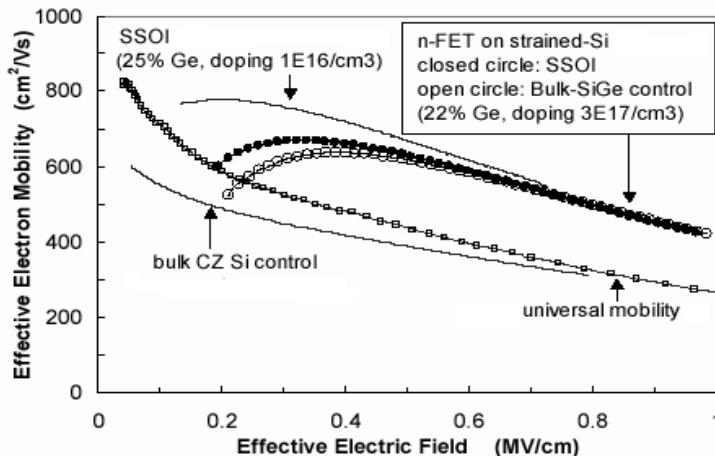

Channel transport and universal mobility in Si. Electron mobility may be enhanced ( $\sim 2\times$ ) by substrate-induced strain in Si. After S.-I. Takagi, ULIS 2004 Lecture Materials.

dopants causes increasing variation of the threshold voltage, posing difficulty in circuit design while scaling the supply voltage. These result in detrimental effects such as degraded mobility, dopant fluctuation effects, and increased series resistance.

In order to circumvent some of the scaling issues, new materials and device architectures are being integrated into CMOS devices in order to maintain the historic CMOS performance trend. The important research needs may be organized into six major categories;

- (a) Substrate Engineering,

- (b) Gate Stack,

- (c) Junctions and Contacts,

- (d) CMOS Compatible Device Structures,

- (e) Technology Modeling and Simulation, and

- (f) Characterization.

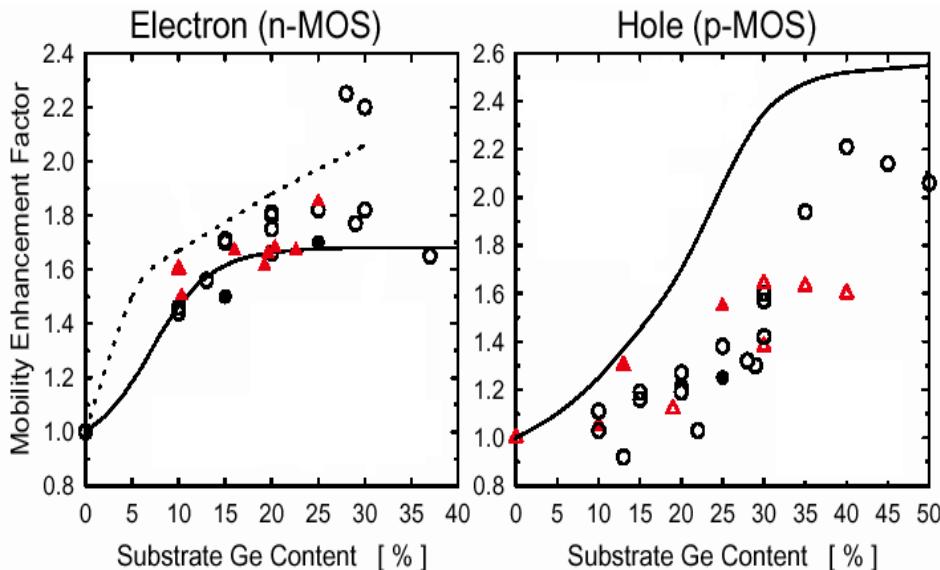

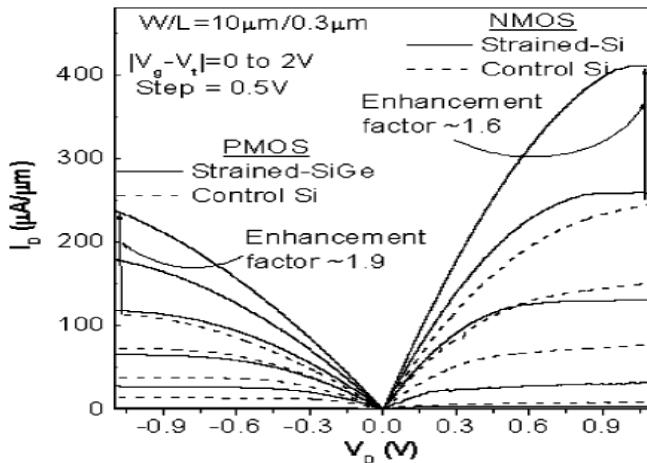

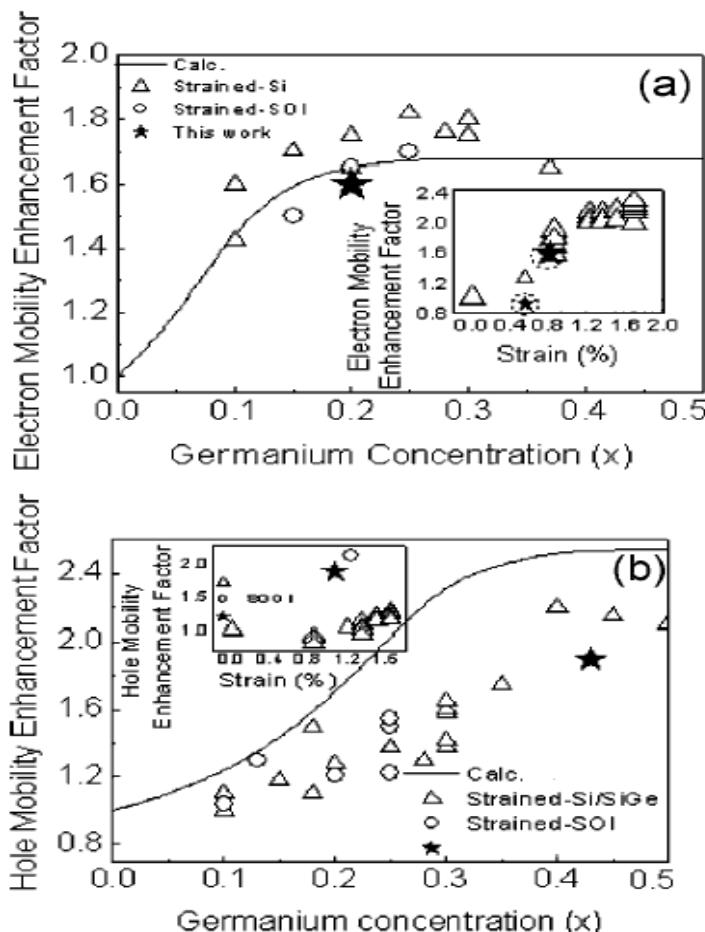

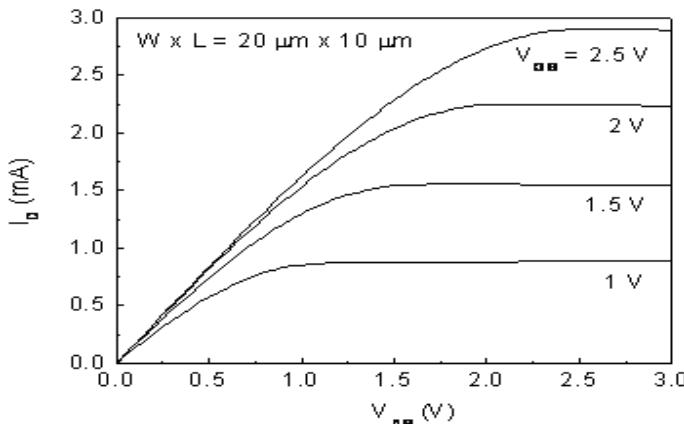

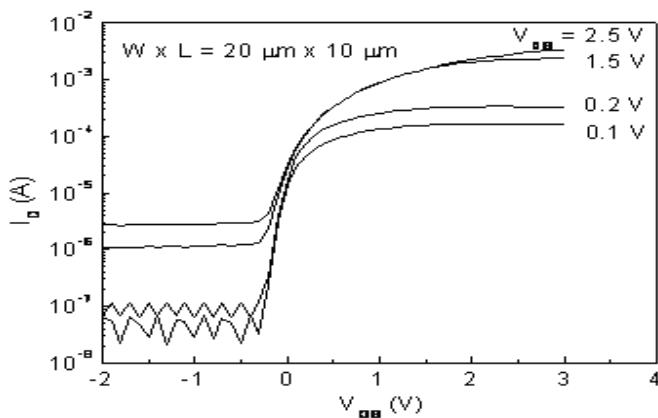

Given the limitations associated with further reduction of the gate length in the quest to continue to increase device speed, the only alternative is to enhance the carrier (electrons and holes) mobility in the channel. Mobility can be improved by using a variety of new Si technologies, including strained silicon (strained-Si), silicon-germanium (SiGe), SiGe on silicon-on-insulator, as well as combinations of these materials (see Fig. 1.3). The impact of

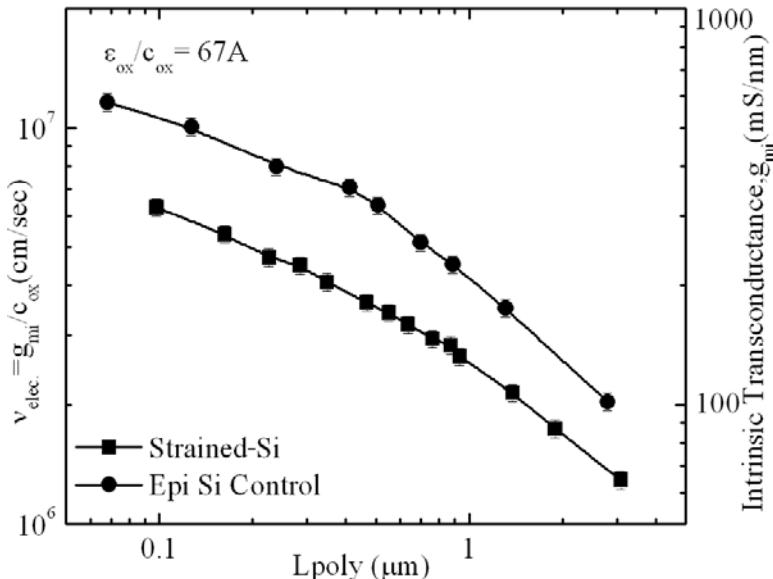

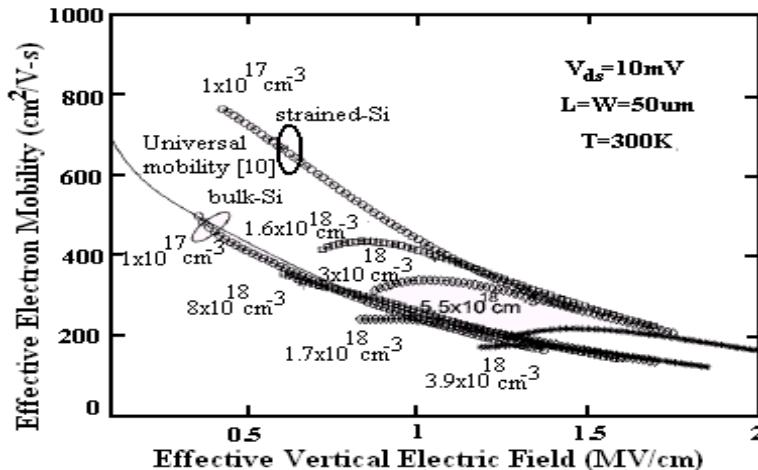

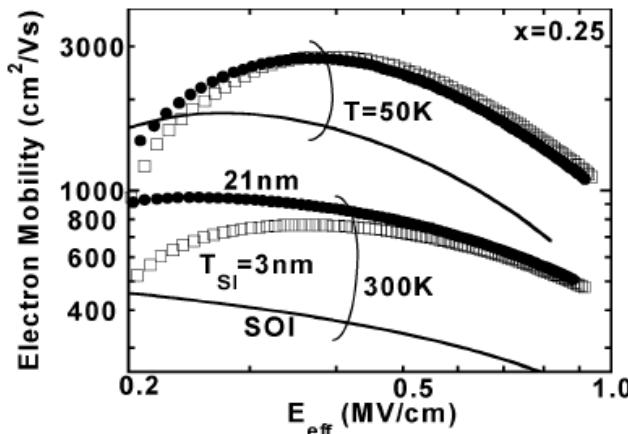

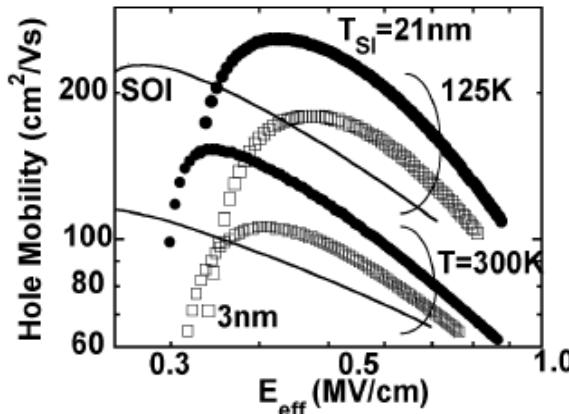

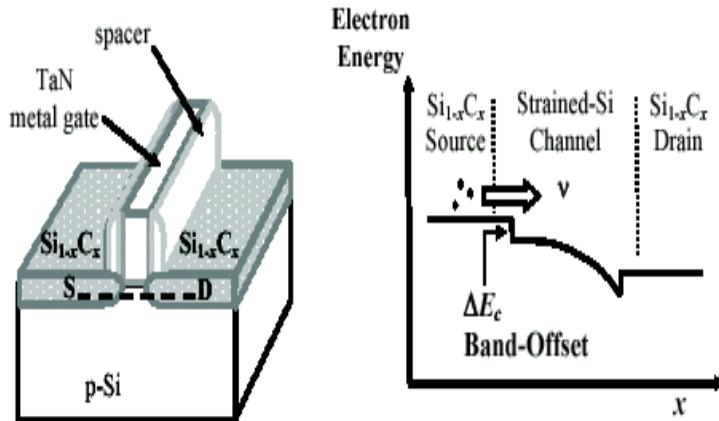

**FIGURE 1.4**

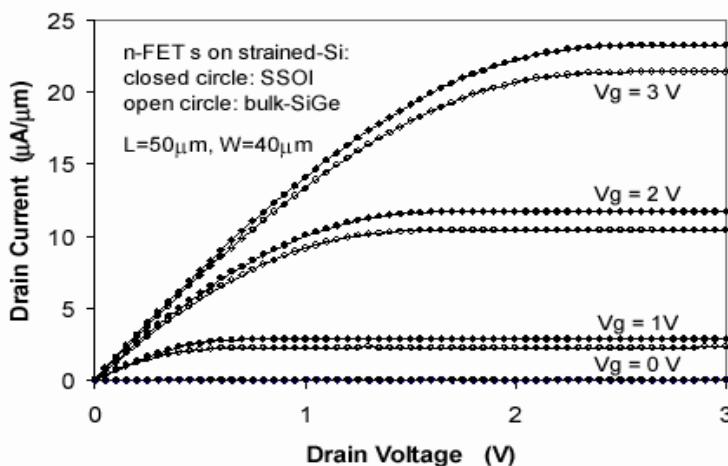

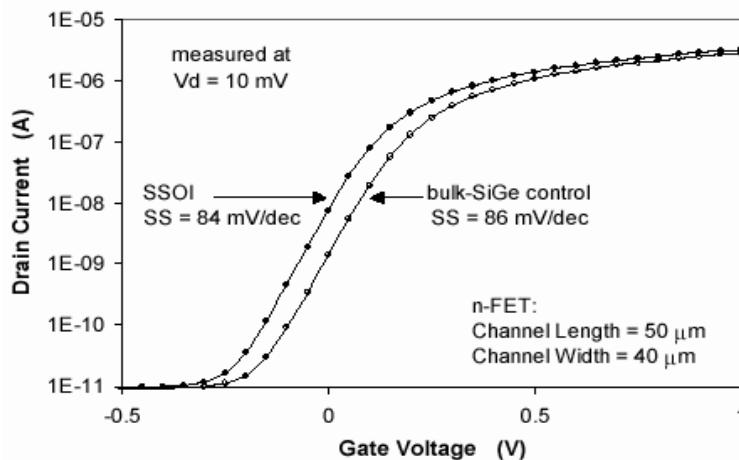

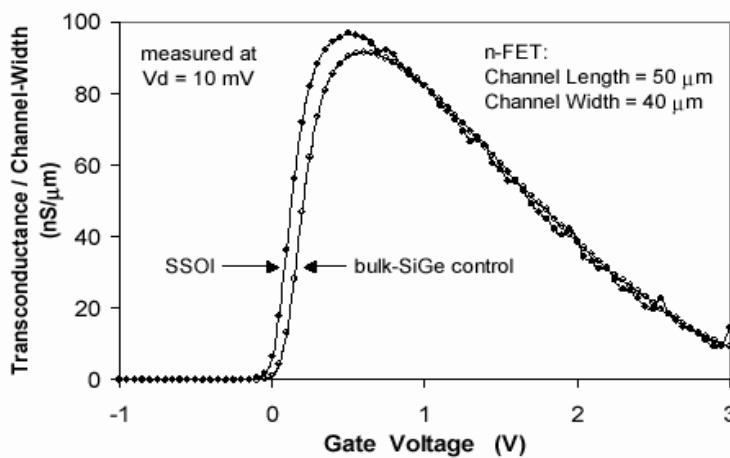

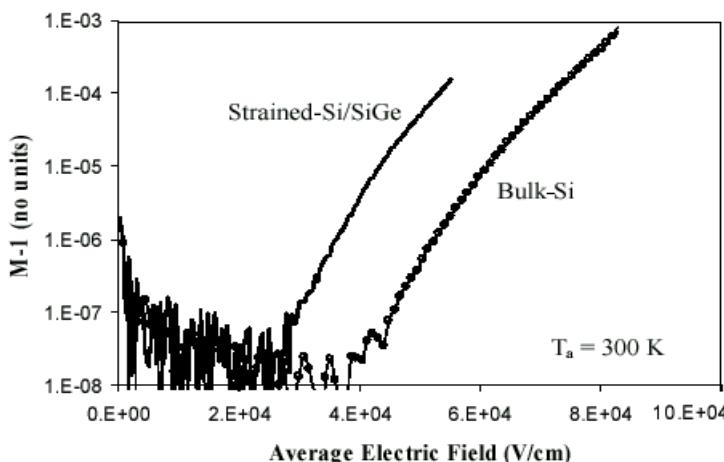

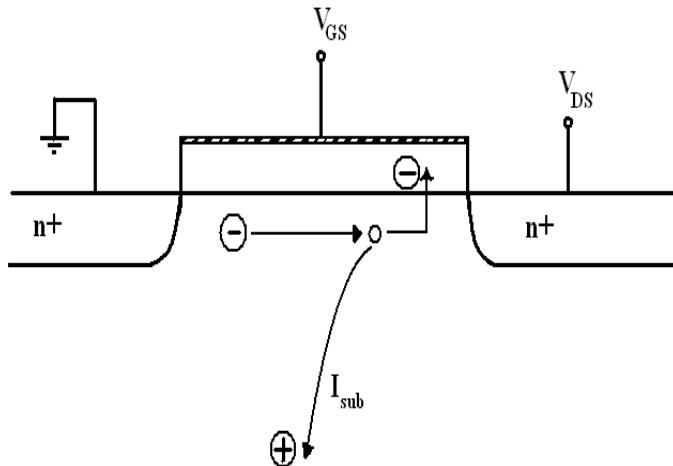

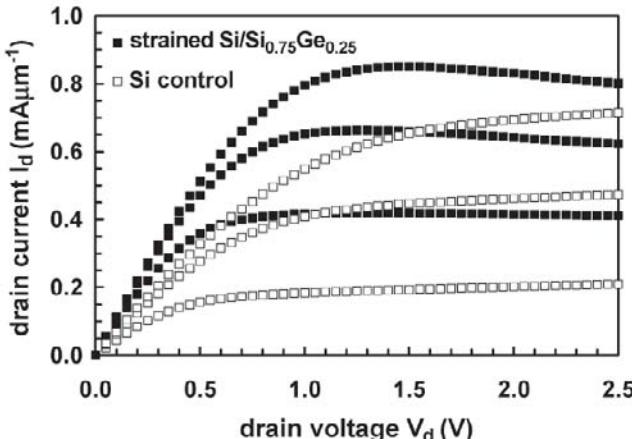

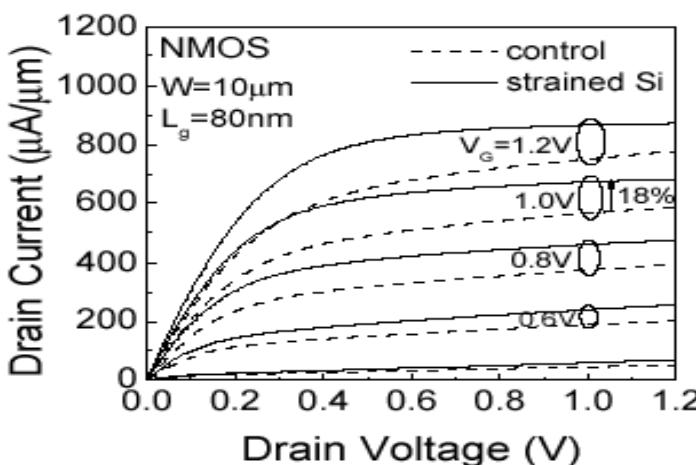

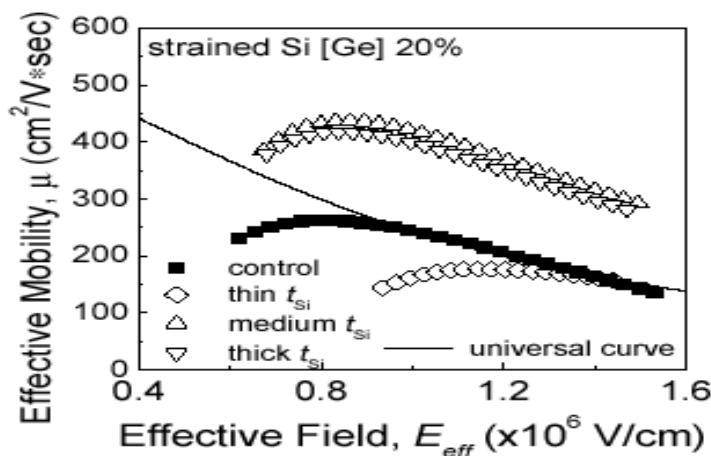

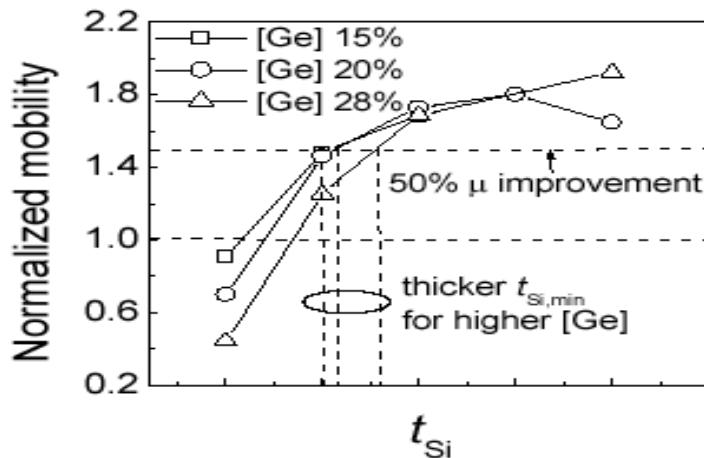

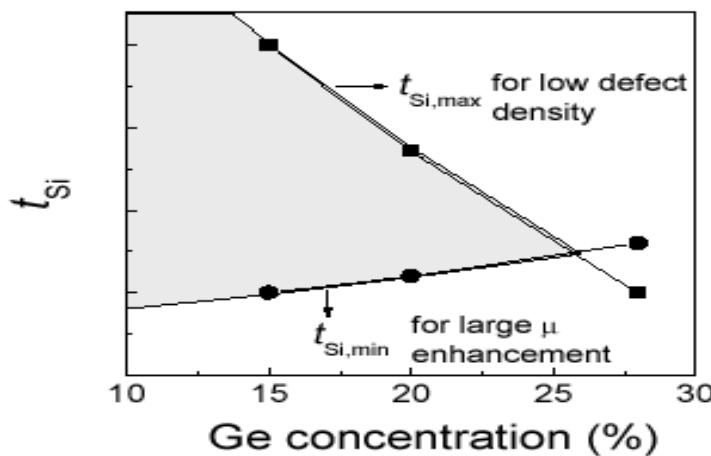

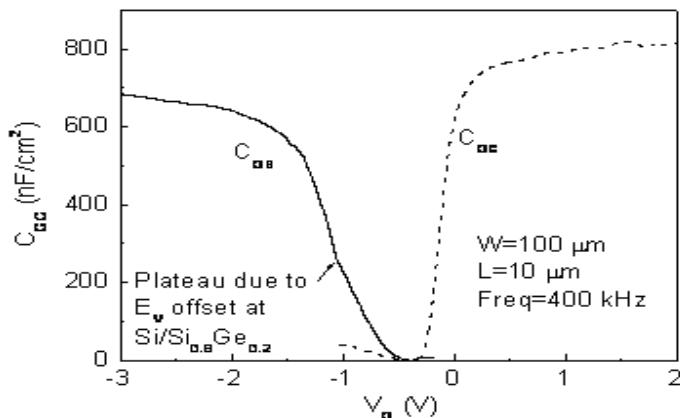

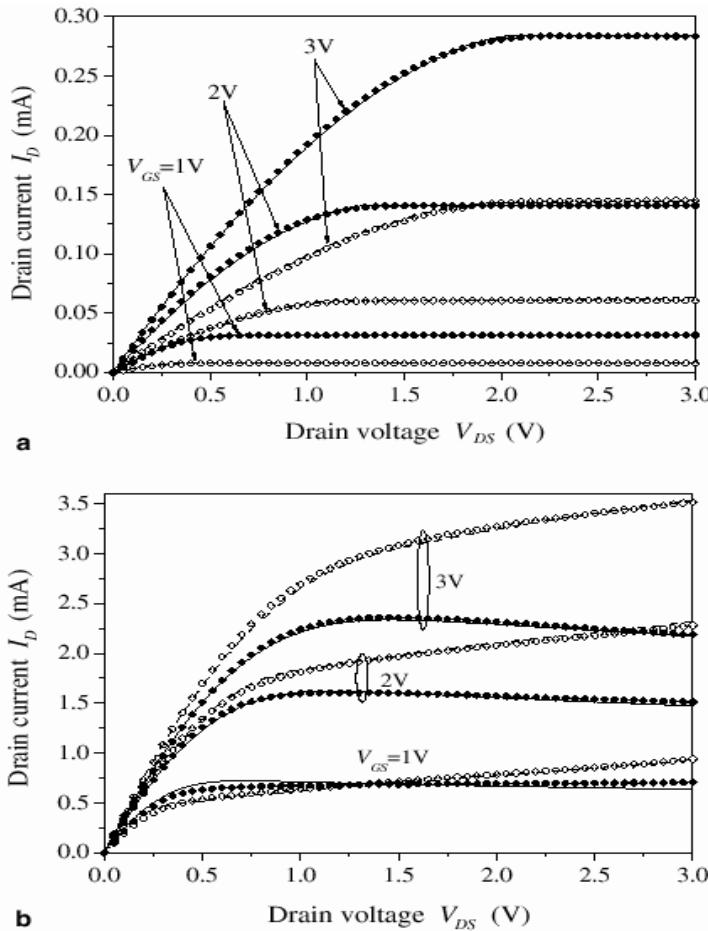

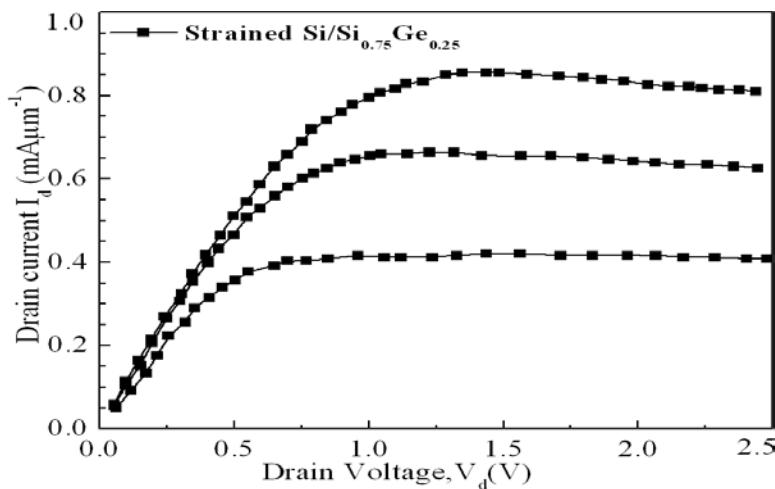

Biaxial strain increases electron mobility above the universal Si mobility curve. Both  $I_d$  and  $g_m$  are enhanced. After K. Rim et al., *IEEE IEDM Tech. Dig.*, 1998(707-710). With permission.

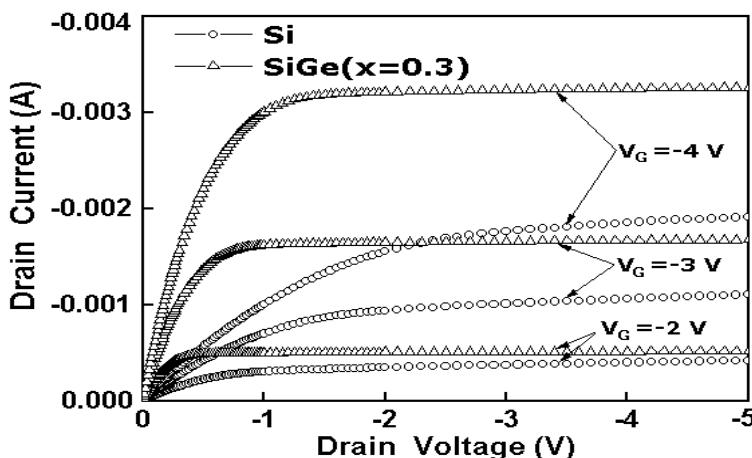

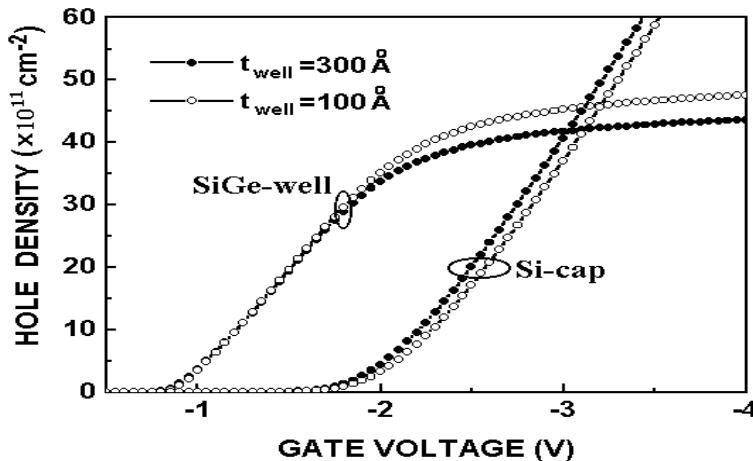

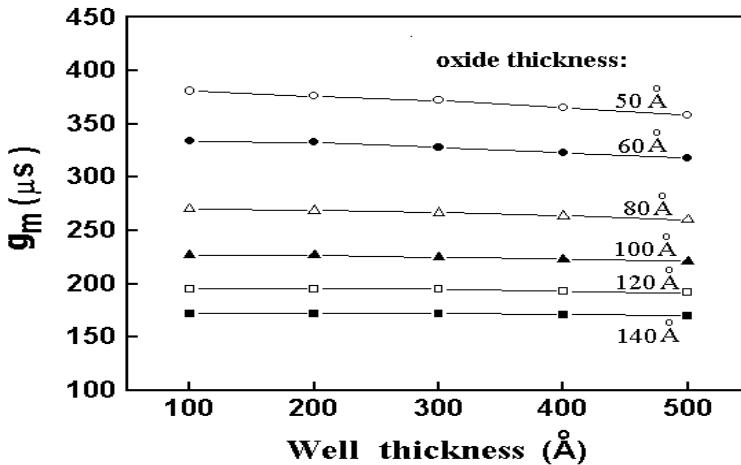

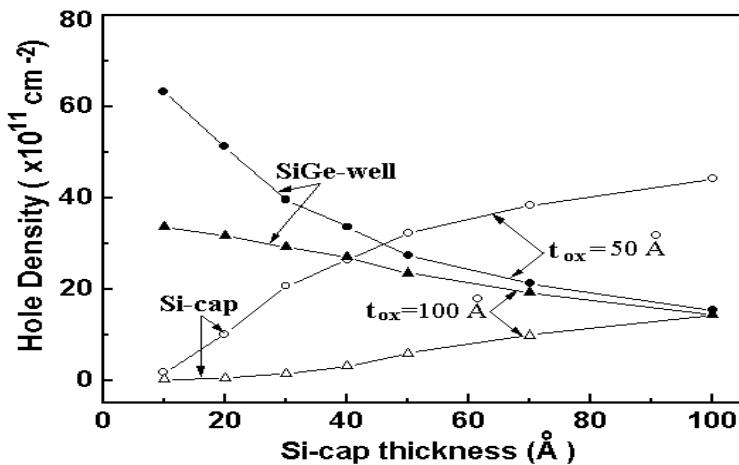

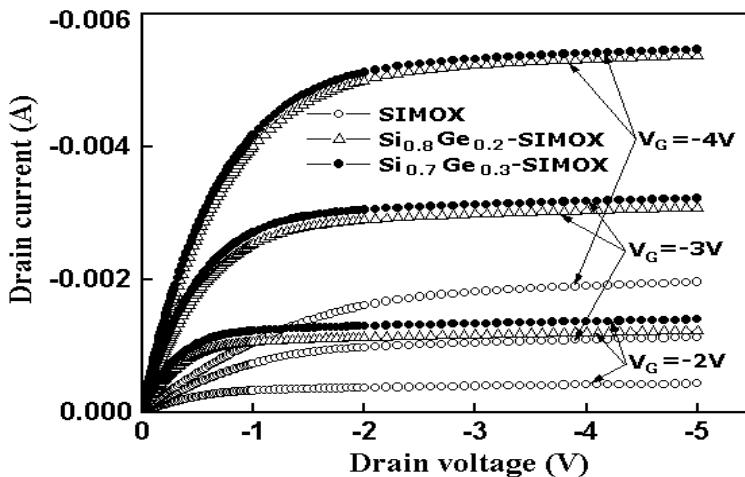

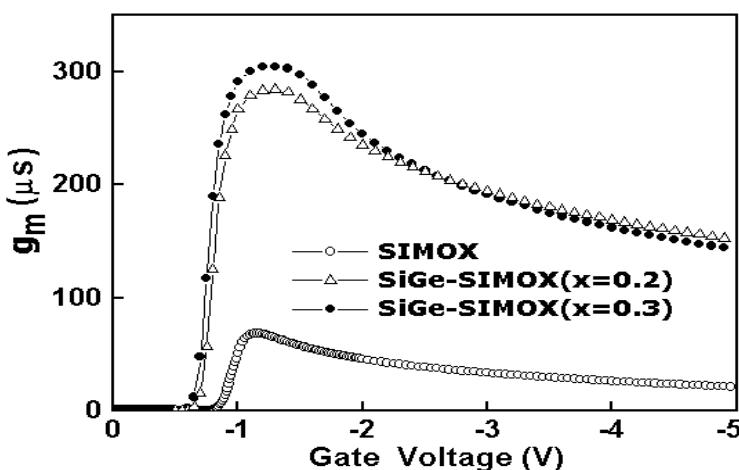

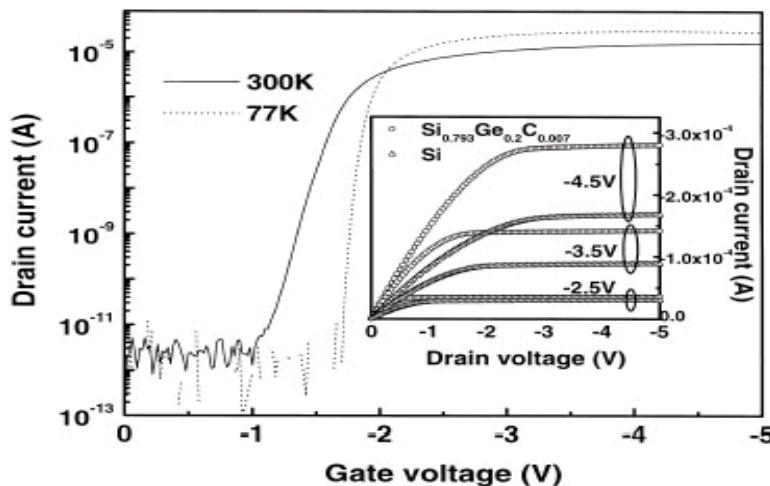

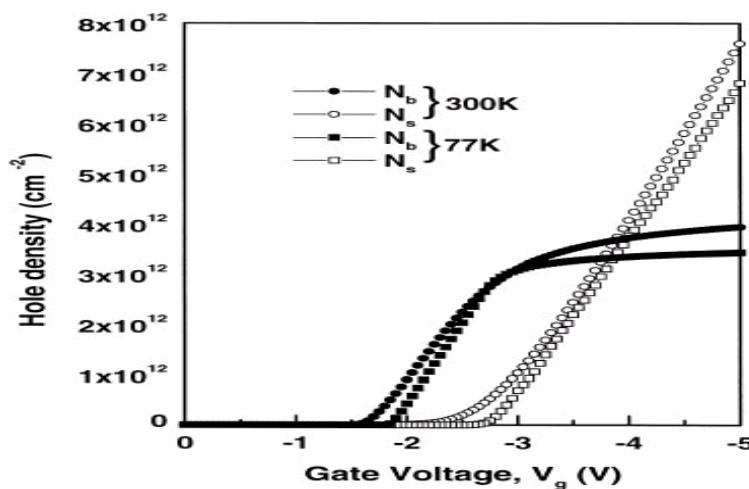

enhanced mobility on drive current in a strained-Si n-MOSFET is shown in Fig. 1.4. One of the most promising alternatives for the replacement of bulk-Si substrates in the CMOS industry is now the heterostructure Silicon technology. For the Si substrate, silicon-on-insulator, which improves chip performance via capacitance reduction, has been introduced in production and is on the roadmap of most major Si chip companies. Faster chips can be made by using other materials such as gallium arsenide. But gallium arsenide is much more expensive than Si. Worse yet, making chips of it requires an entirely different process than that used for Si.

Increasingly new materials need to be introduced in technology development due to physical limits which otherwise would prevent further scaling. This is required especially for gate stacks, interconnect structures, and photoresists. In consequence, equipment, process, device, and circuit models must be extended to include these new materials. Furthermore, computational material science needs to be developed and applied to contribute to the assessment and selection of new materials in order to reduce the experimental effort. An excellent review of CMOS material and structural changes during the past 40 years, and their future trends, can be found in reference [7].

In this book, we will focus primarily on “front-end” issues (structures, processes, and materials associated with the switching devices). However, the objective of this chapter is to highlight some of these new innovations, and to

survey the current progress and potential. We shall focus on front-end materials and processes, as well as advanced transistor structures. It is particularly intended to address the research needs associated with the front-end aspects of extending CMOS technology.

Areas including transistor structures, front-end materials and front-end processes, along with their characterization and modeling/simulation infrastructure to extend front-end fabrication of CMOS from the 65-nm node to its ultimate limit at or beyond the 22-nm node, will be covered. Research needs related to “beyond CMOS” technologies will also be addressed. Historically, new process generations have been limited by the lithographic capability to transfer ultra-small patterns required by the new technology. However, the needs associated with lithography, back-end processing, design, and test are beyond the scope of this book.

---

## 1.1 Heterostructure Field-Effect Devices

Although the SiGe HBTs at present dominate the commercial silicon heterostructure devices, the first Si-based heterostructure field-effect transistor (hetero-FET) was demonstrated in 1986 [8]. These earliest hetero-FETs were Schottky-gated, III-V-like n- and p-channel modulation doped devices, which gave rise to a variety SiGe-based MODFET topologies. Recently, the field-effect devices have centered on strained-Si MOSFETs, because of their better compatibility with mainstream CMOS processing, and the impressive mobility enhancements that have been realized in aggressively scaled gate lengths. Two fundamentally different ways of producing strained-Si CMOS exist, utilizing both biaxial and uniaxial strain techniques.

Strained-Si technology, the introduction of elastic strain in Si transistor channels, is the most widely accepted method for enhancing the carrier mobility of Si. There are two variants to strained-Si technology that have been researched and demonstrated: (a) local (process-induced) strain introduction via transistor module engineering and (b) global (wafer-scale) strain introduction via SiGe (SiGe) epitaxial processes (and layer transfer processes for global strain with SOI). Besides using substrate to provide stress in channel, strain effects induced during the fabrication process can increase the channel mobility. Both tensile and compressive stresses can be introduced to the channel in any one of the three dimensions by different process techniques. Several stress-transfer techniques (such as etch-stop liner and stress transfer via strained-SiGe) using extra integration process into an existing baseline process have been reported. In addition, new preparation techniques of strained-Si surface (e.g., biaxial tensile stress) and different substrate orientation to enhance mobility will be introduced. The challenges and importance of

**TABLE 1.2**

Reported enhancements in MOSFETs with local and global strain engineering techniques.

| Manufacturer              | Strain Type        | $L_g$ (nm) | nMOS $I_{dsat}$ Enhancement | pMOS $I_{dsat}$ Enhancement | Ref. |

|---------------------------|--------------------|------------|-----------------------------|-----------------------------|------|

| Freescale/TSMC/<br>SOITEC | Global<br>(on SOI) | 150        | 28%                         | 12%                         | [11] |

| IBM                       | Global             | 67         | 35%                         | N/A                         | [12] |

| IBM/Sony/Toshiba          | Local              | 45         | 11%                         | 20%                         | [13] |

| AMD/Chartered             | (on SOI)           |            |                             |                             |      |

| Intel                     | Local              | 45         | 10%                         | 25%                         | [14] |

| Intel                     | Global             | 140        | 24%                         | N/A                         | [15] |

| Toshiba                   | Global             | 40         | N/A                         | 19%                         | [16] |

| AMD                       | Local<br>(on SOI)  | 40         | 13%                         | 20%                         | [17] |

| AMD                       | Global             | 25         | 25%                         | N/A                         | [18] |

| TSMC                      | Global             | 60         | 15%                         | N/A                         | [19] |

each method will be discussed and compared. In addition, we shall highlight how the stress oriented from the layout geometry affects the device electrical behavior. The issues and improvement in the circuit level device modeling will be discussed.

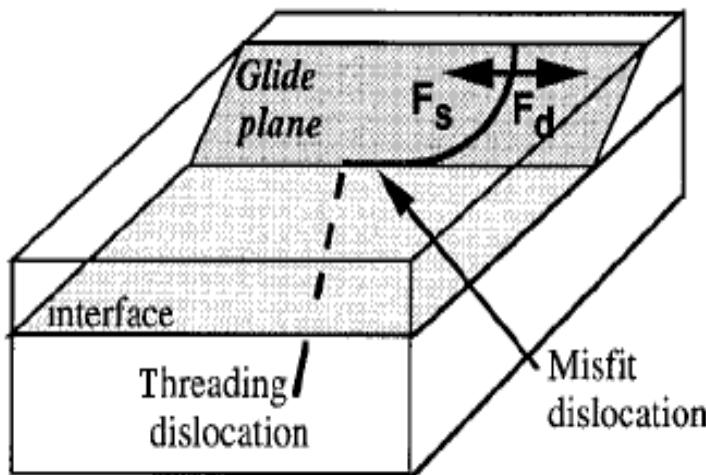

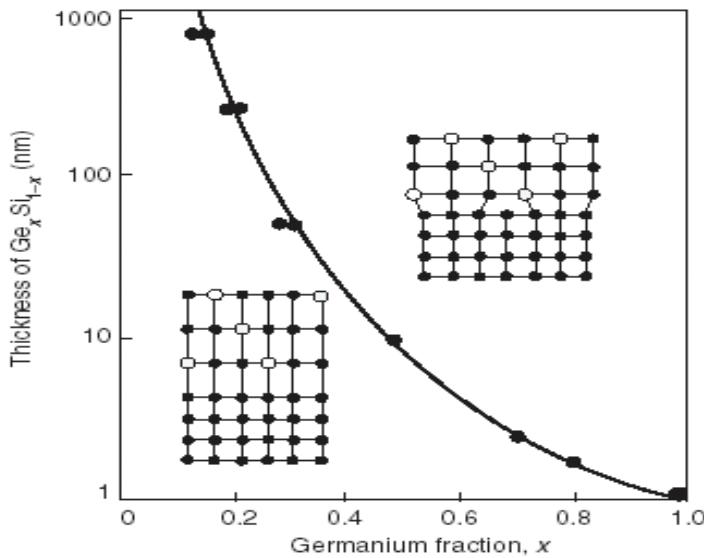

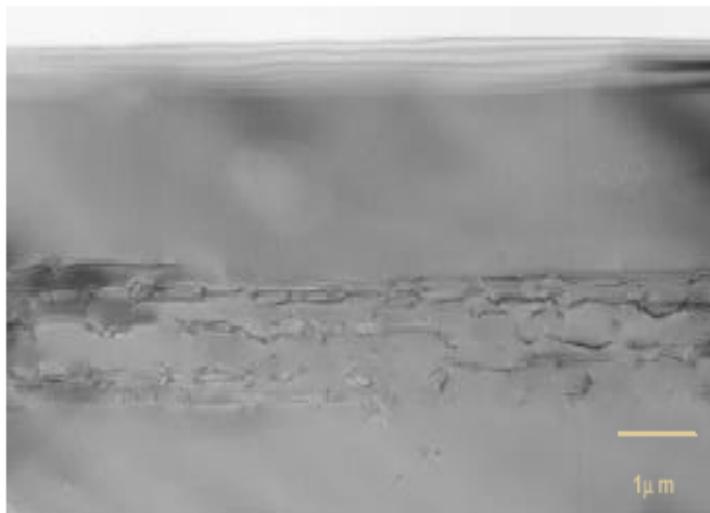

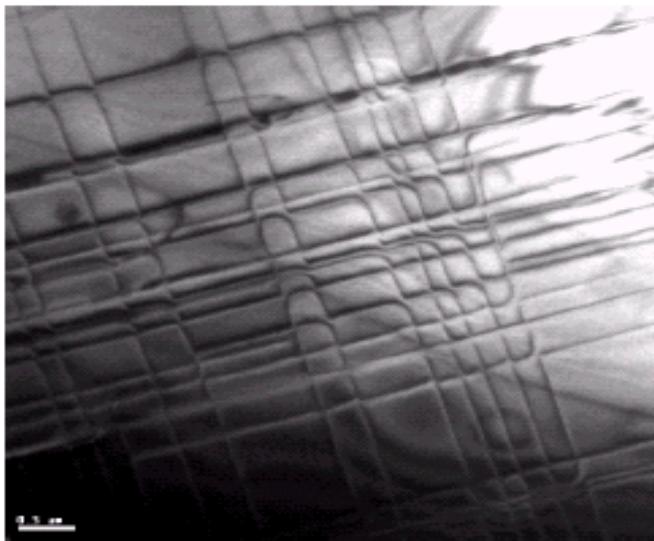

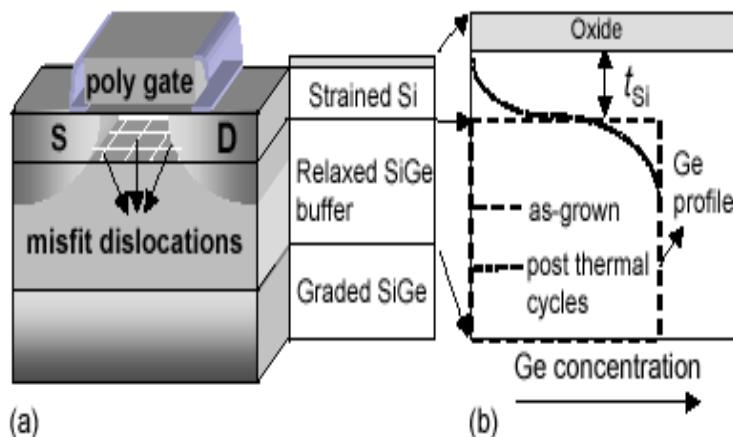

Channel engineering in the form of strained-Si on relaxed-SiGe substrate, compressive SiGe in the channel or in recessed SD region has received much attention as materials options to increase drive current in CMOS devices [9]. However, there exists many challenges such as dislocations, surface roughness, Ge and dopant diffusion which need to be addressed for successful integration of strained-Si in mainstream CMOS technology. High-k gate dielectrics offer another opportunity to enhance CMOS devices by enabling scaling the effective oxide thickness (EOT) of gate dielectrics to below 1-nm with significantly reduction of gate leakage currents. However, the implementation of high-k gate dielectrics is still problematic in CMOS devices. The use of high-k dielectrics can result both in mobility and reliability degradation [10]. Table 1.2 summarizes several transistor performance results based upon global and local strain engineering techniques.

## 1.2 Substrate Engineering

Introduction of strain to delay the need for integration of new materials, such as high-k and further channel/gate scaling by at least one generation, may be viewed as a viable technology node extender. Mobility enhancement in Si has

been demonstrated utilizing engineered substrates, for example, by straining the Si channel. Electron and hole mobility may also be optimized separately by patterning substrates to expose different Si crystal faces for each device. Even faster complementary MOS (CMOS) logic operation would be attainable with high mobility channel materials, e.g., Ge or III-V semiconductors. New metrology needs for material and structure characterization are rising. These include metrologies for high spatial-resolution strain measurement of patterned surfaces, dopant profiling and dose monitoring in small area and nonplanar topographies, and characterization of surface mobility in new substrates such as SiGe and strained-Si.

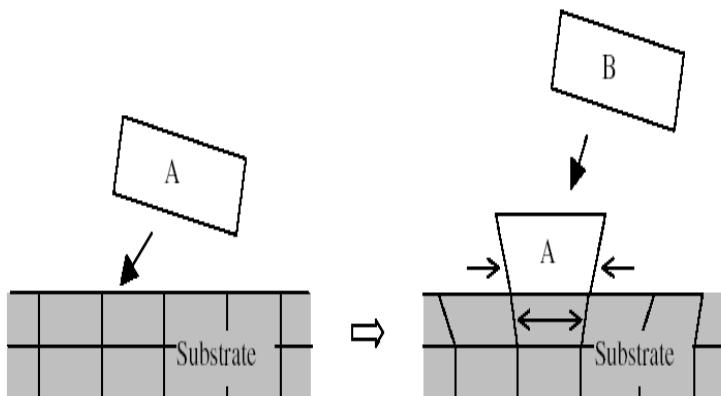

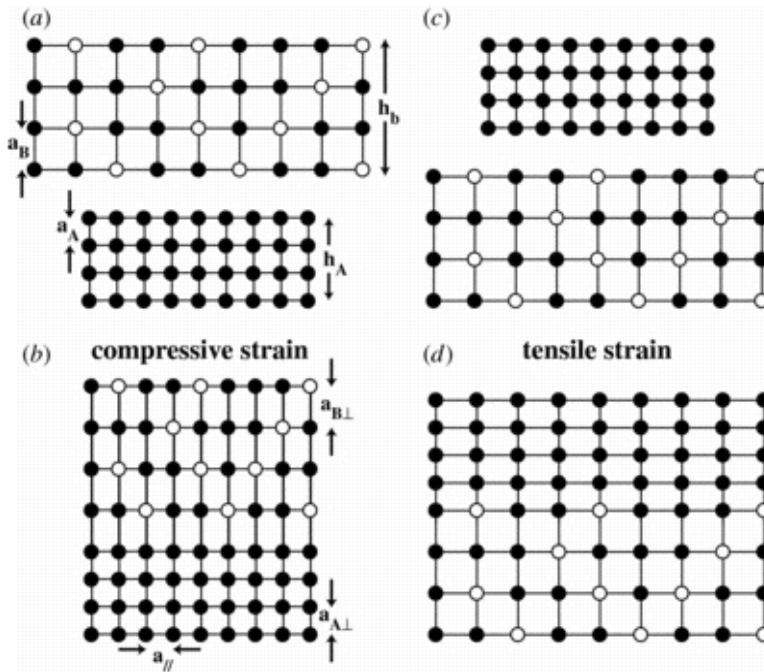

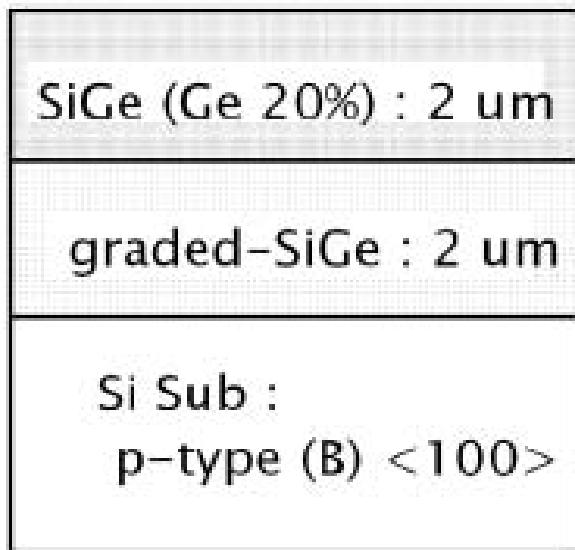

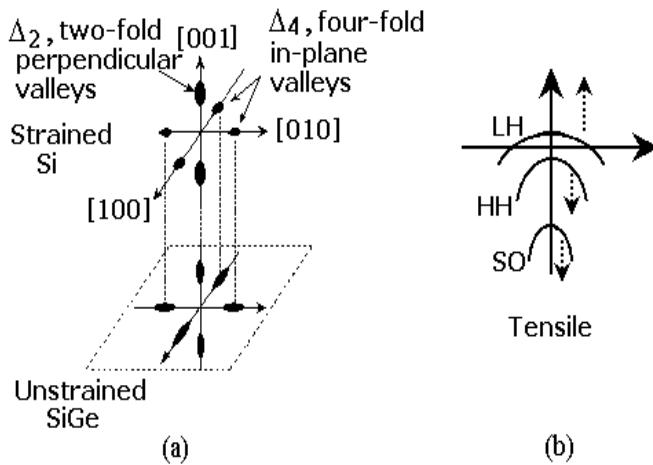

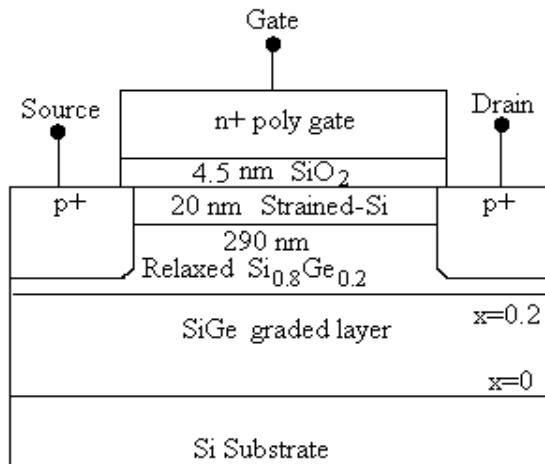

### 1.2.1 Substrate-Induced Strain Engineering

Strained-Si technology enables improvements in CMOS performance and functionality via replacement of the bulk, crystalline-Si substrate with a Si substrate that contains a tetragonally distorted, biaxially strained-Si thin film at the surface. In fact, the improved performance comes from the properties of the strained-Si itself. Rather than shrinking the size of the transistor, strained-Si technology changes the nature of the wafer itself by slightly stretching the placement of the atoms. This increases mobility permitting electrons to travel faster. In strained-Si technology, the substrate fabrication involves generally UHV epitaxy techniques for large-scale production. However, strained-Si layers have also been produced using industry-standard low-pressure Si epitaxy systems, such as the ASM Epsilon and Applied Materials Epi Centura platforms.

The strained-Si layer is produced by depositing a thin layer of Si on an alloy layer of Si and Ge onto a Si substrate. The top Si layer is strained at the Si/SiGe interface because lattice of SiGe exerts a strain on the thinner top Si layer, stretching the Si lattice slightly. Further, by controlling the amount of Ge in the bottom SiGe layer, the amount of strain produced in the overlying Si layer can be manipulated. It was discovered that the lattice mismatch between Si and Ge atoms could be accommodated by a finite degree of lattice distortion [20]. This distortion or strain actually offers the advantage of allowing electrons and holes to move faster (or have higher mobility). This increase in carrier mobility is attributed to a modified Si band structure that lowers the resistance to electron and hole movement in the material. As a result, the use of strained-Si increases electron and hole mobility, and results in higher drive current (10-35%). Increased drive current means increased transistor speed and a 30% speed gain can be translated into roughly two-times lower power consumption. Thus, strained-Si offers a relatively easy way to make more powerful chips with low-power consumption.

Besides strained-Si in the traditional (100) plane, it may be advantageous to change the crystal orientation to optimize CMOS circuit performance. The carrier mobility of inversion layers depends on surface orientation and current flow directions, due to asymmetry of the carrier effective masses in the Si

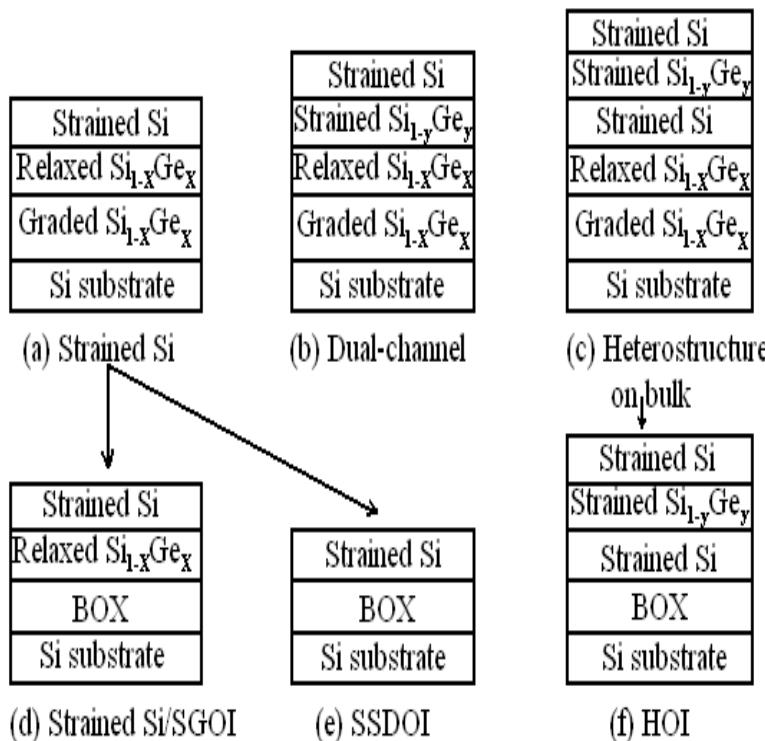

crystal lattice [21]. Recent progress has also demonstrated the evolution of the strained-Si bulk MOS structure, such as the strained-Si on SiGe on insulator (SGOI) MOSFET [22, 23], and the strained-Si directly on insulator (SSDOI) MOSFET [24, 25, 26]. Having a highly strained-Si channel [27] or using a different orientation (110) substrate [28] in p-type MOSFETs, the performance match between the n- and p-MOSFET for CMOS applications might be achieved.

Strained-Si holds out the promise of a big performance enhancement without the need for a major overhaul of the existing chip manufacturing process. However, strained-Si wafers cost more, while a standard eight-inch wafer is about \$120, the strained-Si wafer may cost 2 to 3 times more. Growing the kinds of SiGe-graded layers required to produce strained-Si typically poses two problems: (a) defect propagation into the strained-Si layer and (b) surface crosshatch. Chemical-mechanical polishing in conjunction with epitaxy techniques developed by Amberwave, makes grading of the epitaxial layer for producing good strained-Si layer.

Freescale Semiconductor and the Soitec have made an important advancement in strained-Si technology for next-generation devices. They have announced an approximate 70% increase in electron mobility, as well as high compatibility with existing SOI CMOS processes while optimizing CMOS device performance at the sub-65 nm nodes using strained silicon-on-insulator (SSOI) engineered substrates.

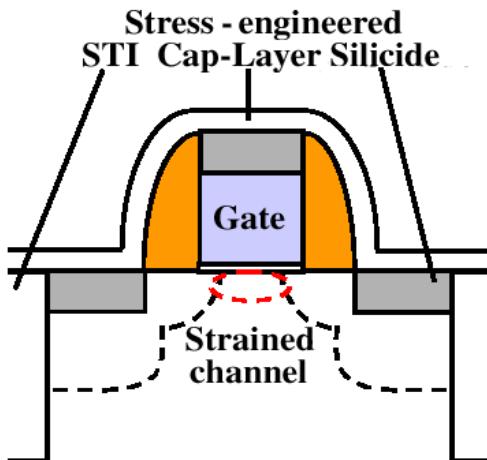

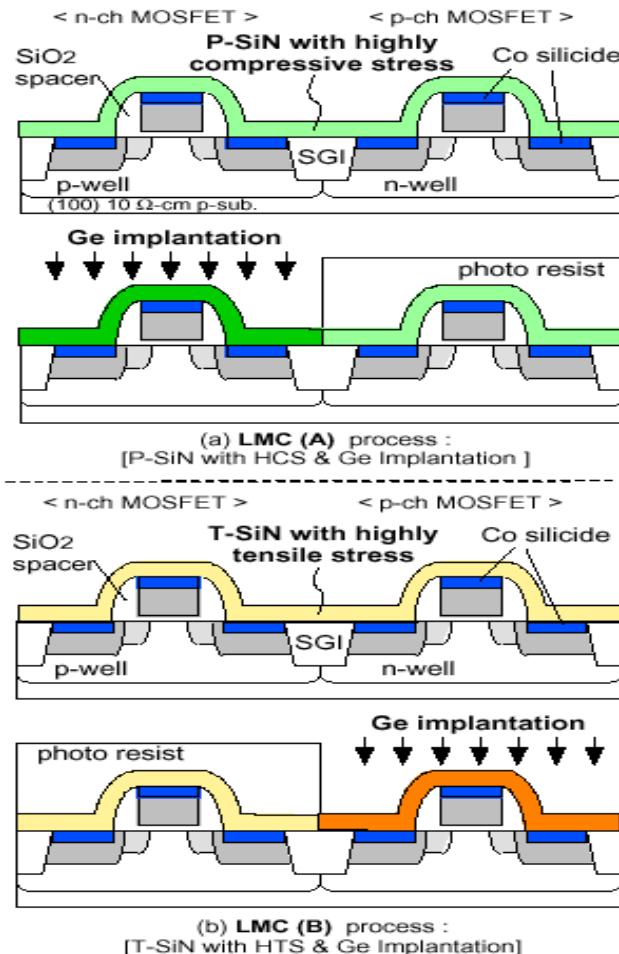

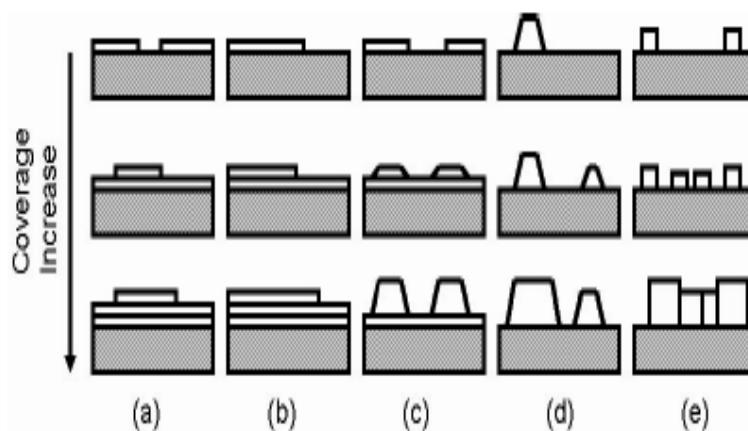

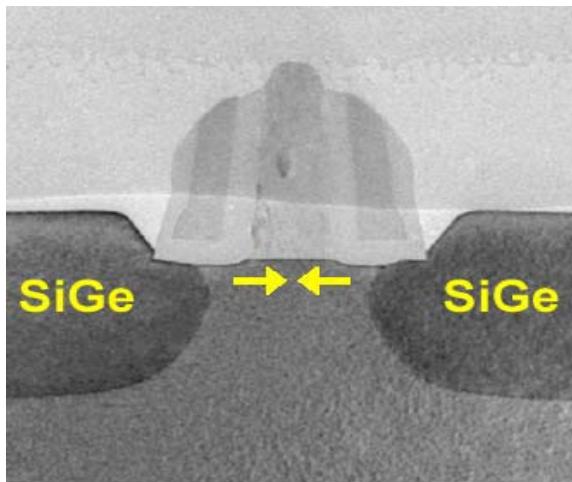

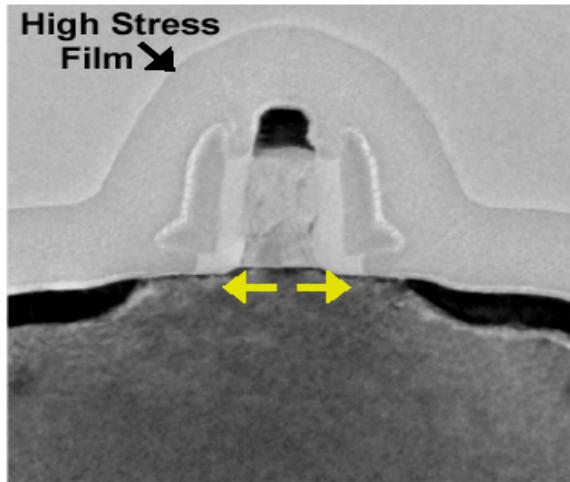

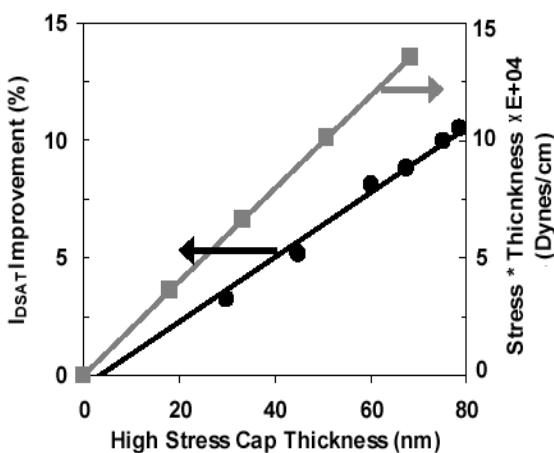

### 1.2.2 Process-Induced Stress Engineering

Process-induced stress requires different stress types (compressive and tensile for n- and p-channel, respectively) to simultaneously improve both n- and p-channel devices. For the last several years, strain developed during semiconductor manufacturing was becoming recognized as offering the best potential to enhance performance in sub-100 nm process technologies. A novel strained transistor architecture has been developed, incorporating epitaxially grown strained-SiGe source-drain regions for p-MOSFETs and a highly tensile silicon nitride capping layer for n-MOSFETs [14]. Although process-induced stress has been used to achieve significant mobility enhancements in short-channel devices (e.g.,  $\sim 2\times$  for holes in 65-nm technology), the Si/SiGe materials system has the potential to achieve very large improvements in mobility.

Intel's approach to form strained-Si through a MOS transistor channel is by using embedded SiGe, which attributed to uniaxial compressive channel stress. Intel's announcement that it would put strained-Si into production in its 90-nm process for forthcoming Pentium 4 processors has underlined the growing gap between the technologies. The integrated Intel process combines strained-Si processing, copper interconnects, and low-k dielectric materials with high-performance, and low-power transistors. The transistors in Intel's 90-nm process have gate lengths of 50-nm and have the gate oxide thickness of 1.2 nm. Thinner gate oxides and ultra-shallow doping profiles help make

**FIGURE 1.5**

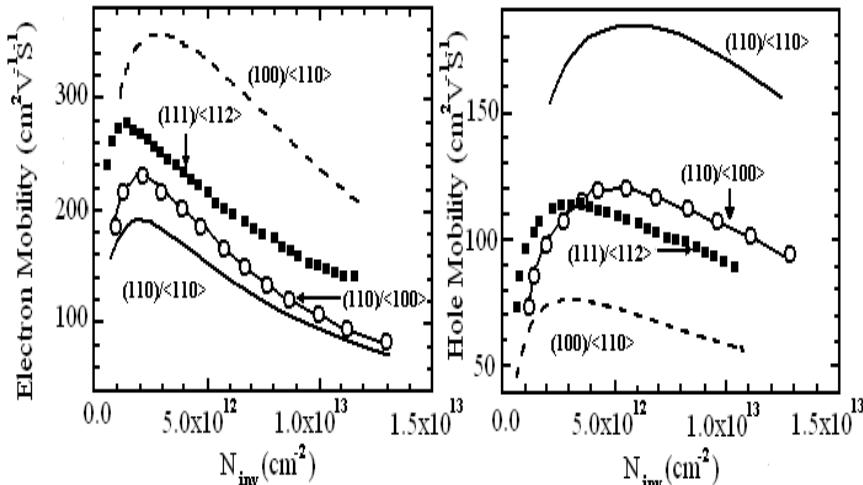

Carrier mobility in the inversion layer with various substrate orientations. Electron mobility is highest on (100) substrate while hole mobility is highest on (110) substrate with current flow along <110> direction. The gate oxides (about 2-nm thick) were grown simultaneously in N<sub>2</sub>O ambient at 800°C in conventional thermal furnace. After M. Yang et al., *IEEE IEDM Tech Dig.*, 2003(453-456). With permission.

sure the transistor works properly with such a short channel length.

Although putting a controlled layer of Ge into place is a challenging task, the improvement in the current drive and, therefore, the switching speed of transistors is expected to outweigh the extra cost involved in using the strained-Si technology. However, in this approach, it is difficult to predict how much advantage may be achieved as one has to overcome the surface defects that can interfere with gate formation.

### 1.2.3 Orientation-Dependent Mobility Engineering

Besides substrate-induced and process-induced stress engineering, wafer substrate orientation and channel orientation can improve mobility. Different surface orientation and direction of applied field for different in-plane stress provide different interaction with carrier transport [29]. Another approach to improve on the mobility and current drive capabilities of Si involves the exploitation of the mobility anisotropy of Si. Fig. 1.5 shows the mobility of electrons and holes for different surface orientations and in the case of the (110) surface, two different in-plane channel directions. It is well-known that electron mobility is highest for the traditional Si substrate/transistor configu-

ration, which includes a (100) surface with a  $<110>$  channel direction, while hole mobility is highest for a (110) surface with a  $<110>$  channel direction. A hybrid substrate configuration [28] has been proposed to allow for the ultimate mobility configuration for each carrier. It should also be noted that even without a change in surface orientation from the traditional (100) surface, hole mobility has been reported to increase via rotation of the channel direction by  $45^\circ$  from the  $<110>$  direction to the  $<100>$  direction [30, 31, 32]. This effect has been reported to be used in 90-nm node products [33]. As with conventional Si surface and channel geometries, the introduction of strain in tandem with different substrate/channel orientations is under investigation [34, 35].

---

### 1.3 Gate Dielectrics on Engineered Substrates

Perhaps the most significant sign of the change in the Si industry is that the new materials, such as high-k materials, are being taken seriously as replacements for  $\text{SiO}_2$  as a gate dielectric and isolation layer. The  $\text{SiO}(N)$  gate insulator in Si-based MOSFETs has been scaled close to its physical thickness limit. To further increase chip performance by using novel materials, the focus has been on high-permittivity (high-k) gate insulators and on metal gate electrodes; increasing the carrier mobility in the channel is the next challenge.

New materials such as high permittivity dielectrics will eventually replace the thermal gate oxide or oxynitride to reduce gate leakage and further improve the drive current with scalable equivalent oxide thickness (EOT). A good high-k material will need to be thermally and chemically stable, have reasonable dielectric value, and result in good silicon and gate electrode interface properties. The high-k dielectric thickness needs to be carefully chosen to avoid interfering with the scalability of the device.

The concurrent reduction of the gate oxide thickness with the channel length results in a large tunneling current. As the gate oxide scales below 15 Å, the gate leakage current is becoming larger than the off-state current of the device required for low power consumption at the 65-nm technology node and beyond. Excessive gate leakage current due to ultra-thin oxide films will necessitate the introduction of high-k material. The technology barriers with high-k dielectric and metal gate are:

- Scaling  $\text{SiO}_2$  gate dielectrics

- Doping limits in silicon and polysilicon

- Ion implantation limits

- Threshold voltage scaling limits

- Bulk CMOS structure limits

---

## 1.4 Strained-Si Technology: Process Integration

The next consideration for strained-Si is the fabrication of strained-Si devices and circuits. Strained-Si technology provides great performance benefits for CMOS, but as with any new technology that is introduced to a manufacturing infrastructure, the ease with which it is adopted is very dependent on the number and severity of changes the new technology requires. Strained-Si technology has attracted the attention of chip designers since the mid-1990s. The strained-Si is a technology based on growing a layer of SiGe alloy on top of a Si wafer. About 4.18% lattice mismatch between Si and Ge causes crystalline defects in SiGe film made by epitaxial deposition. During the deposition of SiGe layers, it is important to avoid a surface defect problem called crosshatch. The ability to neutralize the crosshatch problem enables one to deposit up to 100% Ge in the SiGe layer. Amberwave's strained-Si technology eliminates the surface roughness and defect problems that plague other strained-Si technologies.

Although the majority of early studies have mainly focused on the mobility and performance of long-channel devices, recent studies have shown possible performance improvement of strained-Si MOSFETs with even sub-100 nm gate lengths. The typical process steps used for the fabrication of CMOS circuits were used for strained-Si substrates, which means that no equipment changes or specialty processes are required. The semiconductor R&D community has striven for more than 10 years to develop strained-Si as a cost-effective manufacturing alternative.

One feature of strained-Si technology that distinguishes it most from bulk-Si technology is the fact that the thickness of strained-Si layer, which is limited in thickness due to critical thickness constraints, cannot be stripped indiscriminately. This limits the use of aggressive cleaning strips and other processes that are commonplace in the Si industry. In practice, as long as approximately 5-nm of strained-Si remains at the end of the processing sequence, the transistors will exhibit optimal performance.

It is important to note that the equipment and processes used in standard epitaxial Si wafer processing can be readily implemented for the manufacture of strained-Si substrates and no new manufacturing infrastructure is required. However, there may be specific modules that need to be modified, as the material properties of the strained-Si substrate are somewhat different from bulk-Si. For example, dopant activation and dopant diffusion characteristics are altered due to the presence of Ge in the substrate. This results in different thermal budgets for strained-Si technology.

The presence of the SiGe layer in strained-Si substrate leads to several material- and integration-related challenges. For example, SiGe strain relaxation layer induces high density of defects in strained-Si. Dopant diffusion rate in SiGe is significantly different from that in Si. Boron diffusion is retarded

while arsenic diffusion is enhanced. Additional efforts in junction engineering to control short channel effects and to set the MOSFET threshold voltages to the desired values are required. Significant device self-heating is also observed in strained-Si/SiGe devices because of the lower thermal conductivity in SiGe. The strained-Si technology faces three key challenges: short-channel effect, silicon dislocations, and keeping the strain level during manufacturing. However, strained-Si technology has not shown any known yield-limiting issues so far. Although early research has focused primarily on n-MOSFET devices for the ease of electron mobility, however, recent demonstrations in current improvements are of more than 40% in p-MOSFETs.

Fabrication of strained-Si circuits with symmetric n- and p-MOSFET with high drive current has been demonstrated. It is also possible to build dual-gate devices by combining strained-Si with an SOI substrate in an attempt to overcome difficult performance problems with CMOS scaling. As the infrastructure for circuit design does not change with strained-Si technology, one can expect the SPICE models and design libraries similar to those available today from the fabrication will remain almost the same.

---

## 1.5 Nonclassical CMOS Structures

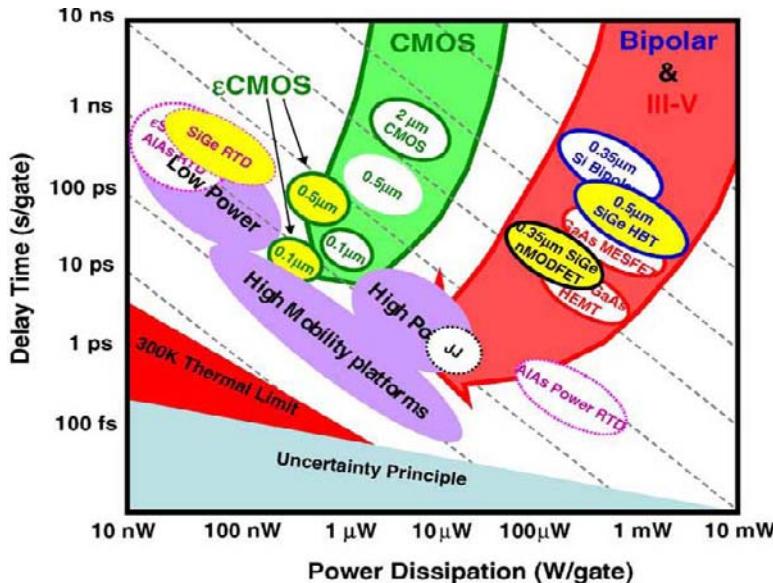

So far, industry focus has concentrated on transistor scaling via shortening of the transistor gate length and transistors fabricated at technology nodes below  $0.13\text{ }\mu\text{m}$  show a rapid decrease in drive current. Existing capabilities of conventional Si substrates will not be able to meet ITRS roadmap specifications. Fig. 1.6 is a plot of device delay vs. the power consumed for various material systems [36]. Fig. 1.6 shows a plot of  $I/CV$ , essentially the figure of merit for digital ICs, which is directly correlated to power-delay product. It is apparent that unless drive current enhancements are introduced, productive scaling would end [37]. New substrate materials are being implemented to continue this scaling [38, 39, 40, 41]. With the use of biaxial strained-Si layers, drive current enhancements were shown to be achievable with implementation of strain, as seen in the strained-Si curve for  $I/CV$ , based on the assumption of a gate-independent enhancement of 20%. For the present, it is thus possible to stay at a given technology and obtain increase in drive current without further scaling.

For over four decades now, the semiconductor industry has relied mostly on shrinking transistor geometries for improvements in both circuit performance and density, resulting in a consistent reduction of cost per function for each new technology node. These include strained-Si, SiGe, high-k gate dielectrics, metal gates, ultrathin body fully depleted SOI (FDSOI), and then multi-gated devices (e.g., FinFET). As CMOS technology continues to scale down, the

**FIGURE 1.6**

Power-delay product for digital integrated circuits. This diagram shows how both materials and device affect the power-delay product. The dashed lines are lines of equal switching energy. Regions are indicated that can benefit most from engineered substrates with higher mobility layers (i.e., materials with lower power-delay product). Low power, high power, and scaled high mobility platform regions are indicated. After D. J. Paul, *Thin Solid Films*, Vol. 321, 1998(172-180). With permission.

FDSOI and double-gate FET (DGFET) technologies offer potential solutions to control short-channel effects by reducing the silicon film thickness and a concurrent scaling of the buried oxide thickness.

Nonclassical MOS transistor structures such as thin-body silicon-on-insulator and double-gate transistors can be scaled more aggressively than the classical bulk-Si structure, and hence may be adapted within the next five years, at the 65-nm technology node (25-nm physical gate length). These advanced structures have distinctly different materials and process technology requirements and associated challenges.

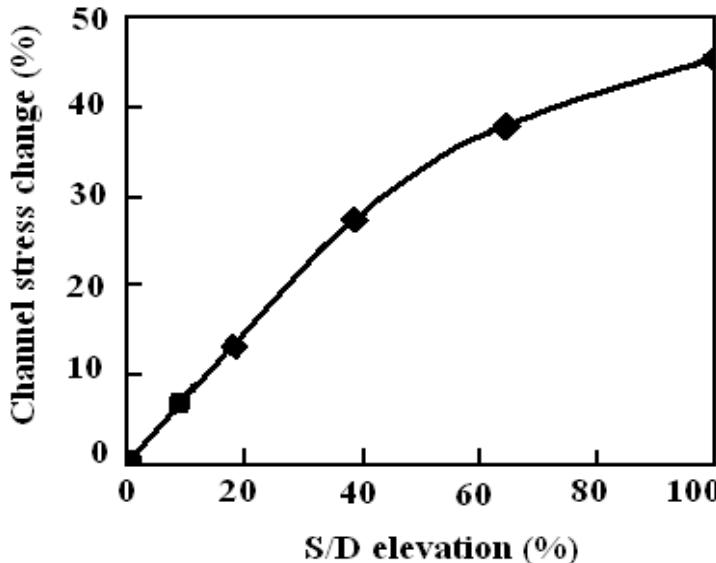

To continue MOSFET scaling to less than  $L_g = 20$  nm, it is quite likely that the device structure will change to advanced nonclassical CMOS such as multiple-gate, ultrathin body (UTB) MOSFETs. In these devices, various “technology boosters” such as mobility enhancement by strained-Si, elevated source/drain, high-k gate dielectric, and metal gate electrode, will likely be simultaneously implemented with the new device structure. In UTB MOSFETs having less than 10-nm Si thickness, various quantum effects will impact the electric characteristics. Toward the end of the roadmap, devices will increase-

ingly be operated in the quasiballistic mode, where the current gain will be enhanced by parameters different from those currently known. Choice of the optimum device structures, their physical characterization, and construction of cost-effective processing flows will become very important along with construction of their circuit architecture. Nanotubes and nanowires may finally be long-term alternatives due to their aspect ratios, which bring them close to being ideal one-dimensional (1D) systems.

However, each of the aforementioned components can result in incremental improvements to CMOS devices; it is anticipated that once the device shrinks beyond the 90-nm node, multiple combinations of these components will be required to achieve the requisite performance improvement and power consumption reduction.

---

## **1.6 Strain-Engineered Hetero-FETs: Modeling and Simulation**

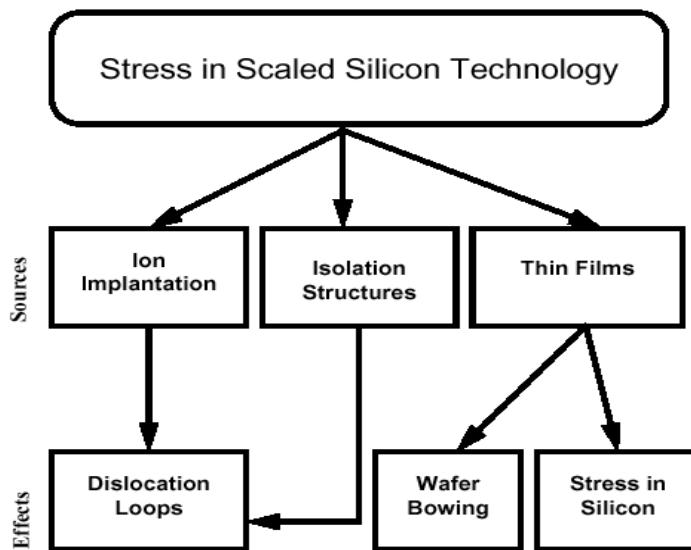

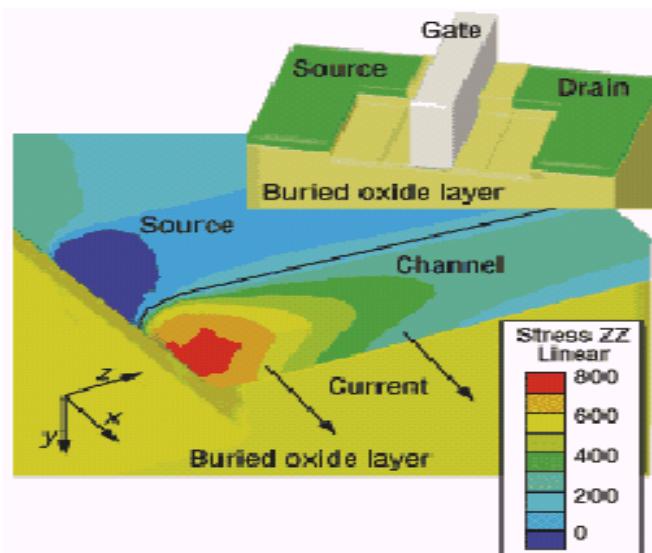

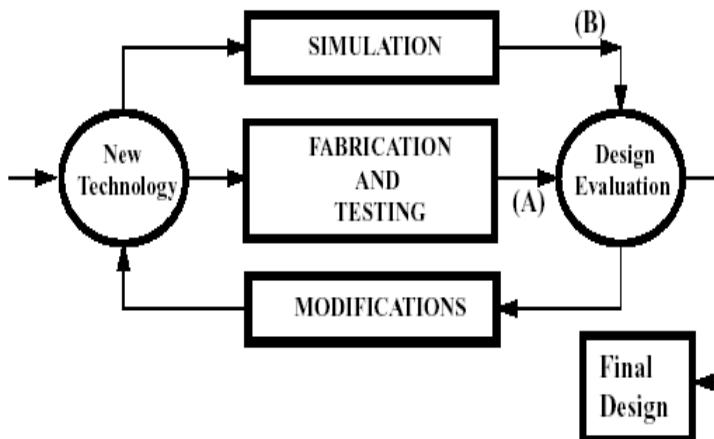

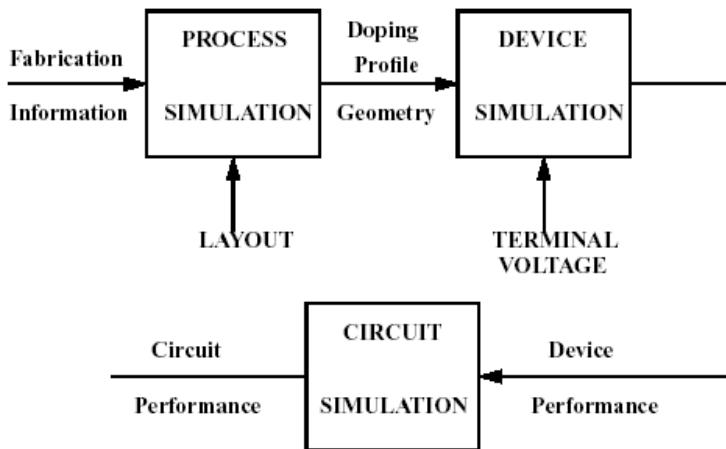

With the adoption of stress engineering as a key component of the new device architectures, modeling of the front-end stress and associated stress enhancement of mobility has become increasingly important for scaling of CMOS devices [14, 42]. The sources of stress in silicon technology come from a variety of strain generated by different processes such as oxidation, thermal mismatch, intrinsic stress, and dopants. Stress modeling is becoming a very important part of the simulation methodology needed to help evaluate and engineer improved device performance due to stress. However, it must be used along with calibrated process simulation for doping profiles and a device simulator that correctly models the change in device characteristics due to stress.

In the area of modeling, as atomic distances are approached, understanding and modeling the complex operation of nano transistors become extremely challenging. Bottoms-up chemical perspective of engineering molecular architecture and correlating precise molecular components with device function will offer new insights into fundamental semiconductor dynamics, facilitate cost-effective manufacturing, and stimulate new possibilities. In addition, a new concern arises about whether the scaling could continue. Also aggressive scaling of the gate length for high-performance applications makes device parameter optimization quite difficult. Ultrashallow junction formation for suppressing the short-channel effect cannot be achieved without incurring a significant increase of parasitic resistance.

Emerging nanoscale semiconductor physical phenomena need to include the following:

- Microscale to nanoscale dimensions

- Single dopant effects

- Surface/interface dominance

- Interface-to-interface interactions in nanoscale devices

- Materials fabrication - reaction kinetics and defects and dislocation

- Nonperiodicity effects

- High field effects

- Single-particle transport phenomena

Advanced MOSFET device physics should include:

- MOSFET structure design

- Short-channel effects

- Electric field distributions in channel and source/drain

- Equilibrium bulk and interface properties which determine performance

- Gate oxide/semiconductor interface control and engineering

- Transient charge carrier transport

---

## 1.7 Summary

Attempts are being made to identify the avenues of research solutions proposed by ITRS to address the future technology needs extending front-end fabrication of CMOS from the 65-nm node to its ultimate limit at or beyond the 22-nm node. Emphasis is being placed on front-end processing and materials, and device structures, along with the supporting characterization, modeling, and simulation techniques. A multidisciplinary effort is required to lead this exciting field to fruition.

In this chapter, we have presented several issues involved with new materials and structures being introduced into Si CMOS technology, and presented some possible potential solutions to enable high-performance and low-power CMOS for the 45-nm technology node and beyond. Various technology innovations (“technology boosters”), such as strained-Si, metal gate, ultrathin body SOI MOSFETs, and multiple-gate MOSFETs, including FinFETs, have been introduced. The proposed solutions should be pursued concurrently with circuit design and architecture improvements, particularly to manage power dissipation.

In the view of the limitations to increase device performance through continued scaling, manufacturers now may find an opportunity in strained-Si to get a reasonable performance enhancement with a relatively simple change in starting materials and hence the cost. However, there are many reasons to believe that continued device scaling will not be as straightforward in the future as it has been in the past. Practical and/or fundamental limits are being approached and substantial changes to device technologies and structures are

going to be required. While “inventions” and new materials have largely not been needed for the past 30 years, they surely will be needed over the next 15 years. This period will likely be the most challenging that the semiconductor industry has faced because it is likely that during this period we will really understand how far Moore’s law can be extended.

With highly creative discoveries and developments of new materials, processes, and transistor structures, many of the challenges have been met so far. Communication between scientists and engineers working in the fields of (a) physics, chemistry, growth, and fabrication of novel substrate materials, (b) device fabrication, (c) characterization, and (d) modeling needs to be increased. However, it may be noted that most of the industry has not yet embraced most of the advanced substrates and device structures that have been demonstrated at the research level.

---

## References

- [1] J. E. Lilienfeld, “Method and apparatus for controlling electric currents,” US Patent 1745175, 1925.

- [2] J. E. Lilienfeld, US Patent 1900018, 1928.

- [3] O. Heil, British Patent 439457, 1935.

- [4] D. Kahng, US Patent 3102230, 1960.

- [5] J. D. Plummer, M. D. Deal, and P. B. Griffin, *Silicon VLSI Technology - Fundamentals, Practice and Modeling*. Prentice Hall, Upper Saddle River, NJ, 2000.

- [6] P. Bai, C. Auth, S. Balakrishnan, M. Bost, R. Brain, V. Chikarmane, R. Heussner, M. Hussein, J. Hwang, D. Ingerly, R. James, J. Jeong, C. Kenyon, E. Lee, S-H. Lee, N. Lindert, M. Liu, Z. Ma, T. Marieb, A. Murthy, R. Nagisetty, S. Natarajan, J. Neirynck, A. Ott, C. Parker, J. Sebastian, R. Shaheed, S. Sivakumar, J. Steigerwald, S. Tyagi, C. Weber, B. Woolery, A. Yeoh, K. Zhang, and M. Bohr, “A 65 nm logic technology featuring 35 nm gate lengths, enhanced channel strain, 8 Cu interconnect layers, low-k ILD and  $0.57 \mu\text{m}^2$  SRAM Cell,” *IEEE IEDM Tech. Dig.*, pp. 657–660, 2004.

- [7] S. E. Thompson, R. S. Chau, T. Ghani, K. Mistry, S. Tyagi, and M. T. Bohr, “In search of ‘forever’ continued transistor scaling one new material at a time,” *IEEE Trans. Semicond. Manufacturing*, vol. 18, pp. 26–36, 2005.

- [8] T. P. Pearsall and J. C. Bean, "Enhancement-mode and depletion-mode p-channel  $Ge_xSi_{1-x}$  modulation-doped FETs," *IEEE Electron Dev. Lett.*, vol. 7, pp. 308–310, 1986.

- [9] C. K. Maiti, L. K. Bera, and S. Chattopadhyay, "Strained-Si heterostructure field effect transistors," *Semicond. Sci. Technol.*, vol. 13, pp. 1225–1246, 1998.

- [10] M. Houssa, *High-k Gate dielectrics*. Institute of Physics Publishing, Bristol, 2003.

- [11] A. V. Y. Thean, T. White, M. Sadaka, L. McCormick, M. Ramon, R. Mora, P. Beckage, M. Canonicco, X.-D. Wang, S. Zollner, S. Murphy, V. van Der Pas, M. Zavala, R. Noble, O. Zia, L.-G. Kang, V. Kolagunta, N. Cave, J. Cheek, M. Mendicino, B.-Y. Nguyen, M. Orlowski, S. Venkatesan, J. Mogab, C. H. Chang, Y. H. Chiu, H. C. Tuan, Y. C. See, M. S. Liang, Y. C. Sun, I. Cayrefourcq, F. Metral, M. Kennard, and C. Mazure, "Performance of super-critical strained-Si directly on insulator (SC-SSOI) CMOS based on high-performance PD-SOI technology," *IEEE VLSI Tech. Symp. Dig.*, pp. 134–135, 2005.

- [12] K. Rim, S. Koester, M. Hargrove, J. Chu, P. M. Mooney, J. Ott, T. Kanarsky, P. Ronsheim, M. Ieong, A. Grill, and H.-S. P. Wong, "Strained Si NMOSFETs for high performance CMOS technology," *VLSI Technology*, pp. 59–60, 2001.

- [13] H. S. Yang, R. Malik, S. Narasimha, Y. Li, R. Divakaruni, P. Agnello, S. Allen, A. Antreasyan, J. C. Arnold, K. Bandy, M. Belyansky, A. Bonnoit, G. Bronner, V. Chan, X. Chen, Z. Chen, D. Chidambaram, A. Chou, W. Clark, S. W. Crowder, B. Engel, H. Harifuchi, S. F. Huang, R. Jagannathan, F. F. Jamin, Y. Kohyama, H. Kuroda, C. W. Lai, H. K. Lee, W.-H. Lee, E. H. Lim, W. Lai, A. Mallikarjunan, K. Matsumoto, A. McKnight, J. Nayak, H. Y. Ng, S. Panda, R. Rengarajan, M. Steigerwalt, S. Subbanna, K. Subramanian, J. Sudijono, G. Sudo, S.-P. Sun, B. Tessier, Y. Toyoshima, P. Tran, R. Wise, R. Wong, I. Y. Yang, C. H. Wann, L. T. Su, M. Horstmann, Th. Feudel, A. Wei, K. Frohberg, G. Burbach, M. Gerhardt, M. Lenski, R. Stephan, K. Wieczorek, M. Schaller, H. Salz, J. Hohage, H. Ruelke, J. Klais, P. Huebler, S. Luning, R. van Bentum, G. Grasshoff, C. Schwan, E. Ehrichs, S. Goad, J. Buller, S. Krishnan, D. Greenlaw, M. Raab, and N. Kepler, "Dual stress liner for high performance sub-45 nm gate length SOI CMOS manufacturing," *IEEE IEDM Tech. Dig.*, pp. 1075–1077, 2004.

- [14] T. Ghani, M. Armstrong, C. Auth, M. Bost, P. Charvat, G. Glass, T. Hoffmann, K. Johnson, C. Kenyon, J. Klaus, B. McIntyre, K. Mistry, A. Murthy, J. Sandford, M. Silberstein, S. Sivakumar, P. Smith, K. Zawadzki, S. Thompson, and M. Bohr, "A 90 nm high volume manu-

facturing logic technology featuring novel 45 nm gate length strained silicon CMOS,” *IEEE IEDM Tech. Dig.*, pp. 978–980, 2003.

- [15] S. Datta, G. Dewey, M. Doczy, B. S. Doyle, B. Jin, J. Kavalieros, R. Kotlyar, M. Metz, N. Zelick, and R. Chau, “High mobility Si/SiGe strained channel MOS transistors with HfO<sub>2</sub>/TiN gate stack,” *IEEE IEDM Tech. Dig.*, pp. 653–656, 2003.

- [16] T. Sanuki, A. Oishi, Y. Morimasa, S. Aota, T. Kinoshita, R. Hasumi, Y. Takegawa, K. Isobe, H. Yoshimura, M. Iwai, K. Sunouchi, and T. Noguchi, “Scalability of strained silicon CMOSFET and high drive current enhancement in the 40 nm gate length technology,” *IEEE IEDM Tech. Dig.*, pp. 65–68, 2003.

- [17] M. Horstmann, D. Greenlaw, Th. Feudel, A. Wei, K. Frohberg, G. Burbach, M. Gerhardt, M. Lenski, R. Stephan, K. Wieczorek, M. Schaller, J. Hohage, H. Ruelke, J. Klais, P. Huebler, S. Luning, R. van Bentum, G. Grasshoff, C. Schwan, J. Cheek, J. Buller, S. Krishnan, M. Raab, and N. Kepler, “Sub-50 nm gate length SOI transistor development for high performance microprocessors,” *Mat. Sci. and Eng. B*, vol. 114-115, pp. 3–8, 2004.

- [18] J. Goo, Q. Xiang, Y. Takamura, H. Wang, J. Pan, F. Arasnja, E. N. Panton, P. Besser, M. V. Sidorov, E. Adem, A. Lochtefeld, G. Braithwaite, M. T. Currie, R. Hammond, M. T. Bulsara, and M. Lin, “Scalability of strained-Si nMOSFETs down to 25 nm gate length,” *IEEE Electron Dev. Lett.*, vol. 24, pp. 351–353, 2003.

- [19] H. C.-H. Wang, Y.-P. Wang, S.-J. Chen, C.-H. Ge, S. M. Ting, J.-Y. Kung, R.-L. Hwang, H.-K. Chiu, L. C. Sheu, P.-Y. Tsai, L.-G. Yao, S.-C. Chen, H.-J. Tao, Y.-C. Yeo, W.-C. Lee, and C. Hu, “Substrate-strained silicon technology: process integration,” *IEEE IEDM Tech. Dig.*, pp. 61–64, 2003.

- [20] J. W. Matthews and A. E. Blakeslee, “Defects in epitaxial multilayers - I. Misfit dislocations,” *J. Crystal Growth*, vol. 27, pp. 118–125, 1974.

- [21] T. Sato, Y. Takeishi, H. Hara, and Y. Okamoto, “Mobility anisotropy of electrons in inversion layers on oxidized silicon surfaces,” *Phys. Rev. B*, vol. 4, pp. 1950–1960, 1971.

- [22] S. Takagi, T. Mizuno, N. Sugiyama, T. Tezuka, and A. Kurobe, “Strained-Si-on-insulator (strained-SOI) MOSFETs - concept, structures and device characteristics,” *IEICE Trans. on Electron.*, vol. E84-C, pp. 1043–1050, 2000.

- [23] H.-S. P. Wong, “Beyond the conventional transistor,” *IBM J. Res. & Dev.*, vol. 46, pp. 133–168, 2002.

- [24] T. A. Langdo, A. Lochtefeld, M. T. Currie, R. Hammond, V. K. Yang, J. A. Carlin, C. J. Vineis, G. Braithwaite, H. Badawi, M. T. Bulsara, and E. A. Fitzgerald, "Preparation of novel SiGe-free strained-Si on insulator substrates," *Proc. IEEE Int. SOI Conf.*, pp. 211–212, 2002.

- [25] K. Rim, R. Anderson, D. Boyd, F. Cardone, K. Chan, H. Chen, S. Christiansen, J. Chu, K. Jenkins, T. Kanarsky, S. Koester, B. H. Lee, K. Lee, V. Mazzeo, A. Mocuta, D. Mocuta, P. M. Mooney, P. Oldiges, J. Ott, P. Ronsheim, R. Roy, A. Steegen, M. Yang, H. Zhu, M. Ieong, and H.-S. P. Wong, "Strained-Si CMOS (SS CMOS) technology: opportunities and challenges," *Solid-State Electron.*, vol. 47, pp. 1133–1139, 2003.

- [26] K. Rim, K. Chan, L. Shi, D. Boyd, J. Ott, N. Klymko, F. Cardone, L. Tai, S. Koester, M. Cobb, D. Canaperi, B. To, E. Duch, I. Babich, R. Carruthers, P. Saunders, G. Walker, Y. Zhang, M. Steen, and M. Ieong, "Fabrication and mobility characteristics of ultrathin strained-Si directly on insulator (SSDOI) MOSFETs," *IEEE IEDM Tech. Dig.*, pp. 49–52, 2003.

- [27] K. Rim, J. Chu, H. Chen, K. A. Jenkins, T. Kanarsky, K. Lee, A. Mocuta, H. Zhu, R. Roy, J. Newbury, J. Ott, K. Petrarca, P. Mooney, D. Lacey, S. Koester, K. Chan, D. Boyd, M. Leong, and H.-S. Wong, "Characteristics and device design of sub-100 nm strained-Si n- and p-MOSFETs," *IEEE VLSI Tech. Symp. Dig.*, pp. 98–99, 2002.

- [28] M. Yang, M. Ieong, L. Shi, K. Chan, V. Chan, A. Chou, E. Gusev, K. Jenkins, D. Boyd, Y. Ninomiya, D. Pendleton, Y. Surpris, D. Heenan, J. Ott, K. Guarini, C. D'Emic, M. Cobb, P. Mooney, B. To, N. Rovedo, J. Benedict, R. Mo, and H. Ng, "High performance CMOS fabricated on hybrid substrate with different crystal orientations," *IEEE IEDM Tech. Dig.*, pp. 453–456, 2003.

- [29] M. V. Fischetti, Z. Ren, P. M. Solomon, M. Yang, and K. Rim, "Six-band  $k\cdot p$  calculation of the hole mobility in silicon inversion layers: Dependence on surface orientation, strain, and silicon thickness," *J. Appl. Phys.*, vol. 94, pp. 1079–1095, 2003.

- [30] H. Sayama, Y. Nishida, H. Oda, T. Oishi, S. Shimizu, T. Kunikiyo, K. Sonoda, Y. Inoue, and M. Inuishi, "Effect of  $<100>$  channel direction for high performance SCE immune pMOSFET with less than  $0.15 \mu\text{m}$  gate length," *IEEE IEDM Tech. Dig.*, pp. 657–660, 1999.

- [31] T. Matsumoto, S. Maeda, H. Dang, T. Uchida, K. Ota, Y. Hirano, H. Sayama, T. Iwamatsu, T. Ipposhi, H. Oda, S. Maegawa, Y. Inoue, and T. Nishimura, "Novel SOI wafer engineering using low stress and high mobility CMOSFET with  $<100>$ -channel for embedded RF/Analog applications," *IEEE IEDM Tech. Dig.*, pp. 663–666, 2002.

- [32] T. Komoda, A. Oishi, T. Sanuki, K. Kasai, H. Yoshimura, K. Ohno, M. Iwai, M. Saito, F. Matsuoka, N. Nagashima, and T. Noguchi, "Mobility improvement for 45 nm node by combination of optimized stress control and channel orientation design," *IEEE IEDM Tech. Dig.*, pp. 217–220, 2004.

- [33] D. James, "2004 - The year of 90 nm: a review of 90 nm devices," *IEEE/SEMI ASMC Proc.*, pp. 1–6, 2005.

- [34] T. Mizuno, N. Sugiyama, T. Tezuka, and S. Takagi, "[110] strained-SOI n-MOSFETs with higher electron mobility," *IEEE Electron Dev. Lett.*, vol. 24, pp. 266–268, 2003.

- [35] T. Mizuno, N. Sugiyama, T. Tezuka, Y. Moriyama, S. Nakaharai, T. Maeda, and S. Takagi, "Physical mechanism for high hole mobility in (110)-surface strained- and unstrained-MOSFETs," *IEEE IEDM Tech. Dig.*, pp. 809–812, 2003.

- [36] D. J. Paul, "Silicon germanium heterostructures in electronics: the present and the future," *Thin Solid Films*, vol. 321, pp. 172–180, 1998.

- [37] Semiconductor Industry Association, "International Technology Roadmap for Semiconductors." San Jose, Calif., 2005.

- [38] D. K. Nayak, K. Goto, A. Yutani, J. Murota, and Y. Shiraki, "High-mobility strained-Si PMOSFETs," *IEEE Trans. Electron Dev.*, vol. 43, pp. 1709–1715, 1996.

- [39] D. K. Nayak, J. C. S. Woo, J. S. Park, K. L. Wang, and K. P. MacWilliams, "High-mobility p-channel metal-oxide-semiconductor field-effect transistor on strained-Si," *Appl. Phys. Lett.*, vol. 62, pp. 2853–2855, 1993.

- [40] C. K. Maiti, L. K. Bera, S. S. Dey, D. K. Nayak, and N. B. Chakrabarti, "Hole mobility enhancement in strained-Si p-MOSFETs under high vertical fields," *Solid-State Electron.*, vol. 41, pp. 1863–1869, 1997.

- [41] J. Welser, J. L. Hoyt, S. Takagi, and J. F. Gibbons, "Strain dependence of the performance enhancement in strained-Si n-MOSFETs," *IEEE IEDM Tech. Dig.*, pp. 373–376, 1994.

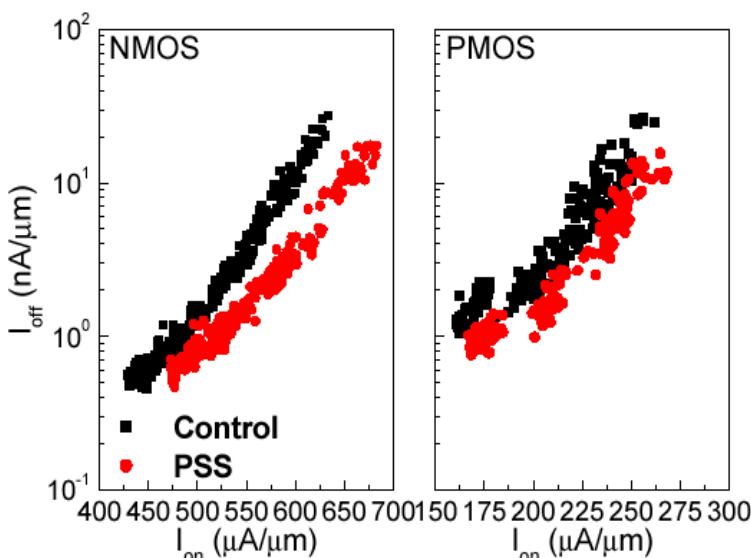

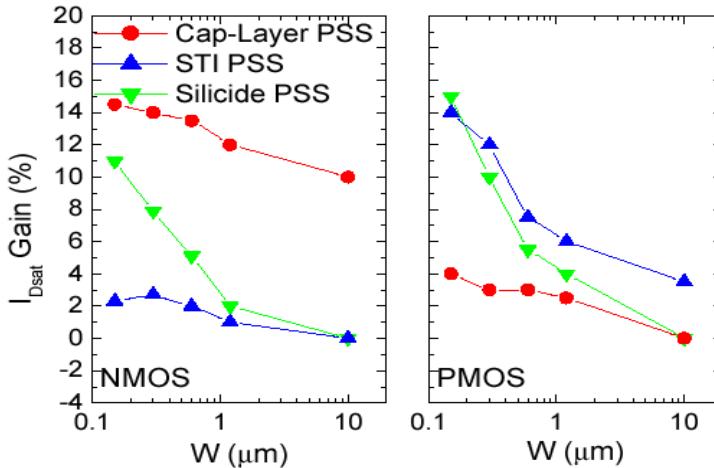

- [42] C.-H. Ge, C.-C. Lin, C.-H. Ko, C.-C. Huang, Y.-C. Huang, B.-W. Chan, B.-C. Perng, C.-C. Sheu, P.-Y. Tsai, L.-G. Yao, C.-L. Wu, T.-L. Lee, C.-J. Chen, C.-T. Wang, S.-C. Lin, Y.-C. Yeo, and C. Hu, "Process-strained Si (PSS) CMOS technology featuring 3D strain engineering," *IEEE IEDM Tech. Dig.*, pp. 73–76, 2003.

## 2

---

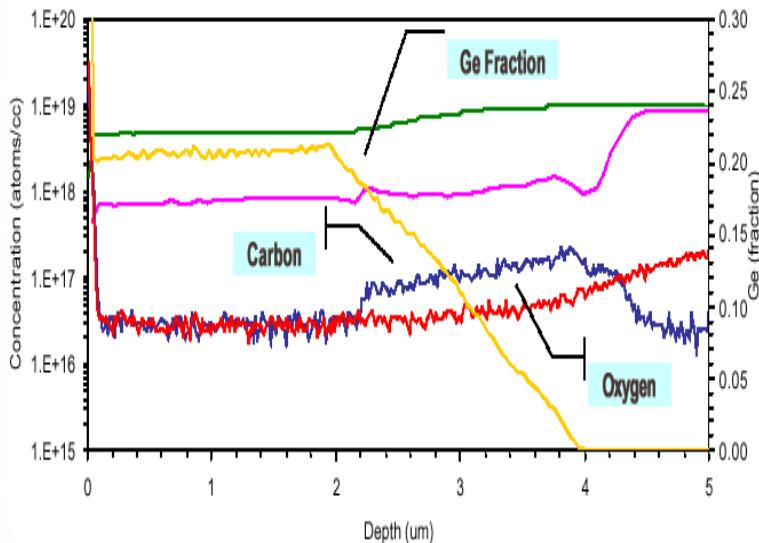

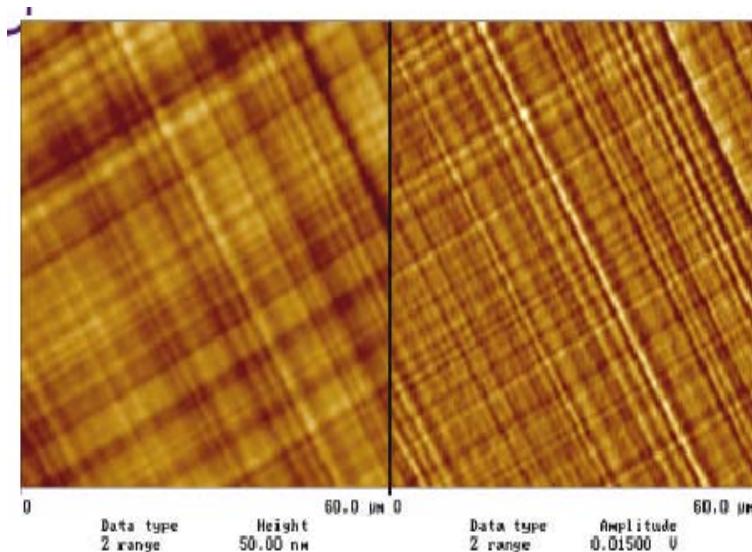

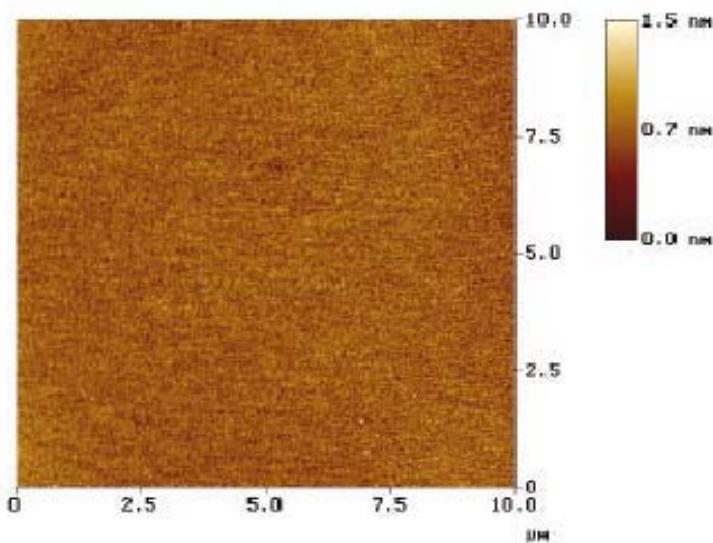

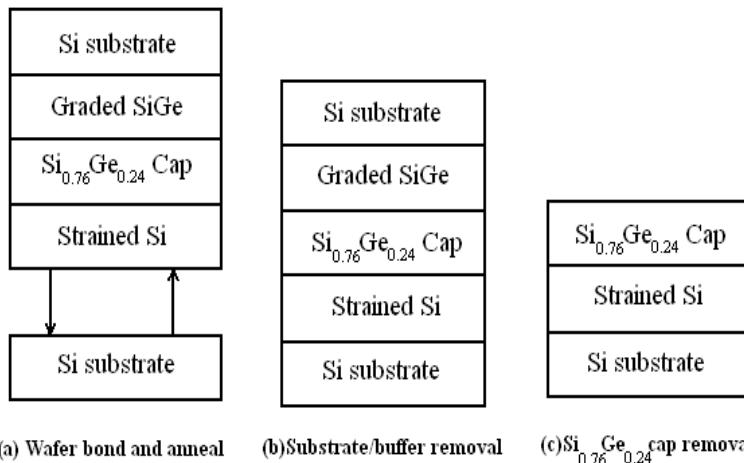

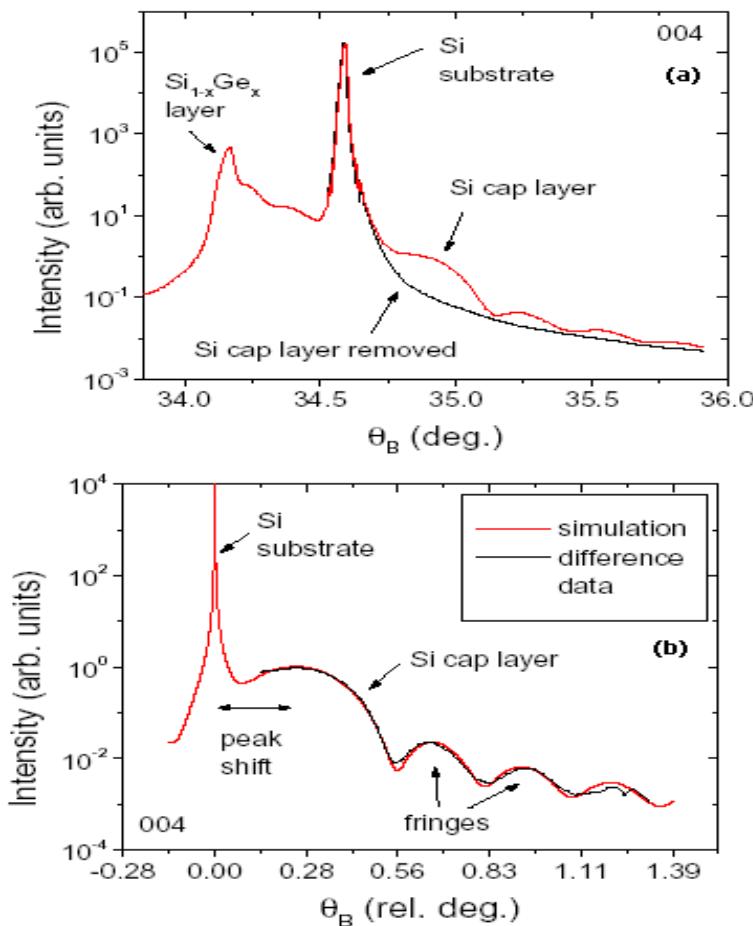

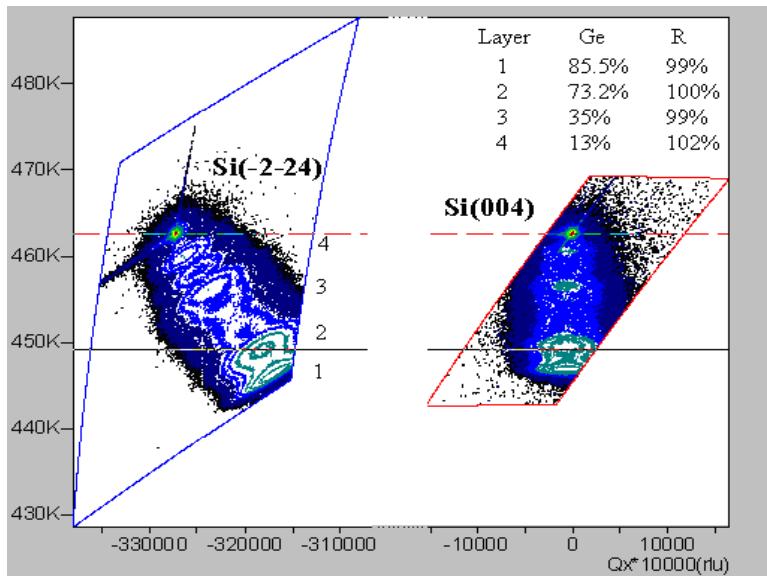

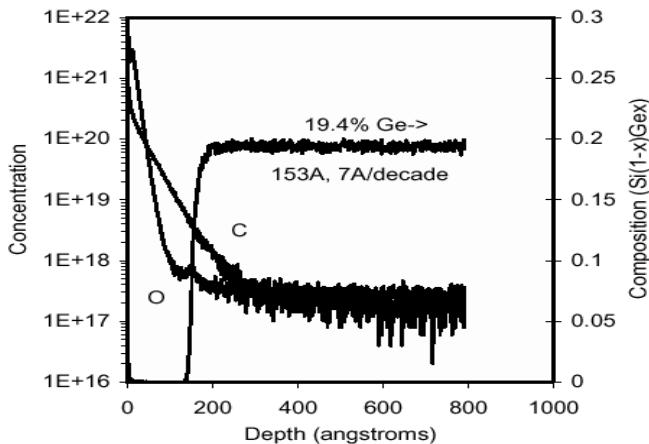

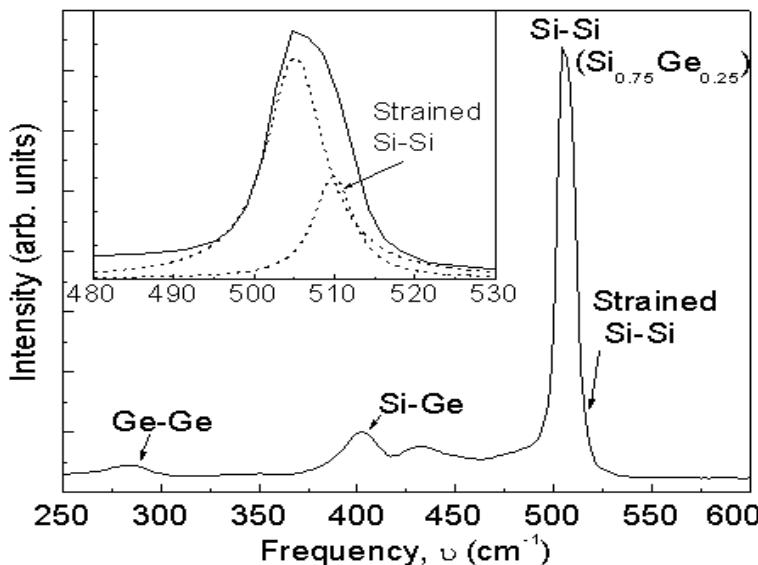

### *Strain Engineering in Microelectronics*