Charles Chiang

Jamil Kawa

# Design for Manufacturability and Yield for Nano-Scale CMOS

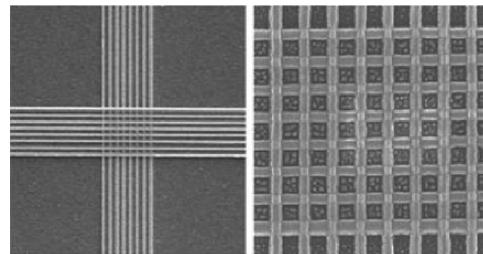

DESIGN FOR MANUFACTURABILITY AND YIELD

FOR NANO-SCALE CMOS

## **Series on Integrated Circuits and Systems**

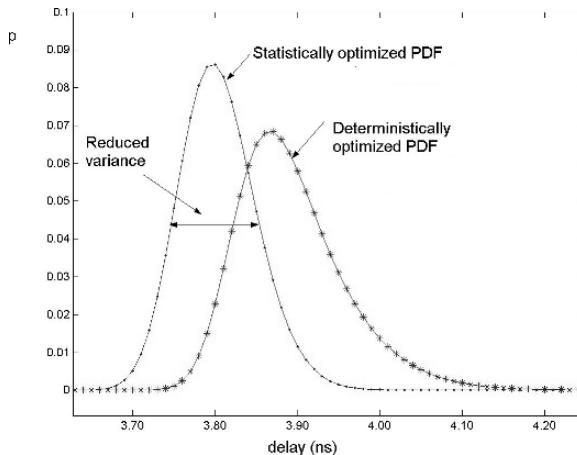

Series Editor: Anantha Chandrakasan

Massachusetts Institute of Technology

Cambridge, Massachusetts

---

Low Power Methodology Manual: For System-on-Chip Design

Michael Keating, David Flynn, Rob Aitken, Alan Gibbons, and Kaijian Shi

ISBN 978-0-387-71818-7

Modern Circuit Placement: Best Practices and Results

Gi-Joon Nam and Jason Cong

ISBN 978-0-387-36837-5

CMOS Biotechnology

Hakho Lee, Donhee Ham and Robert M. Westervelt

ISBN 978-0-387-36836-8

SAT-Based Scalable Formal Verification Solutions

Malay Ganai and Aarti Gupta

ISBN 978-0-387-69166-4, 2007

Ultra-Low Voltage Nano-Scale Memories

Kiyoo Itoh, Masashi Horiguchi and Hitoshi Tanaka

ISBN 978-0-387-33398-4, 2007

Routing Congestion in VLSI Circuits: Estimation and Optimization

Prashant Saxena, Rupesh S. Shelar, Sachin Sapatnekar

ISBN 978-0-387-30037-5, 2007

Ultra-Low Power Wireless Technologies for Sensor Networks

Brian Otis and Jan Rabaeij

ISBN 978-0-387-30930-9, 2007

Sub-Threshold Design for Ultra Low-Power Systems

Alice Wang, Benton H. Calhoun and Anantha Chandrakasan

ISBN 978-0-387-33515-5, 2006

High Performance Energy Efficient Microprocessor Design

Vojin Oklobdzija and Ram Krishnamurthy (Eds.)

ISBN 978-0-387-28594-8, 2006

Abstraction Refinement for Large Scale Model Checking

Chao Wang, Gary D. Hachtel, and Fabio Somenzi

ISBN 978-0-387-28594-2, 2006

A Practical Introduction to PSL

Cindy Eisner and Dana Fisman

ISBN 978-0-387-35313-5, 2006

Thermal and Power Management of Integrated Systems

Arman Vassighi and Manoj Sachdev

ISBN 978-0-387-25762-4, 2006

Leakage in Nanometer CMOS Technologies

Siva G. Narendra and Anantha Chandrakasan

ISBN 978-0-387-25737-2, 2005

Statistical Analysis and Optimization for VLSI: Timing and Power

Ashish Srivastava, Dennis Sylvester, and David Blaauw

ISBN 978-0-387-26049-9, 2005

# DESIGN FOR MANUFACTURABILITY AND YIELD FOR NANO-SCALE CMOS

*by*

**CHARLES C. CHIANG**

*Synopsys Inc.*

*Mountain View, CA, USA*

*and*

**JAMIL KAWA**

*Synopsys Inc.*

*Mountain View, CA, USA*

A C.I.P. Catalogue record for this book is available from the Library of Congress.

ISBN 978-1-4020-5187-6 (HB)

ISBN 978-1-4020-5188-3 (e-book)

---

Published by Springer,

P.O. Box 17, 3300 AA Dordrecht, The Netherlands.

[www.springer.com](http://www.springer.com)

*Printed on acid-free paper*

The contributing authors of this book have used figures and content published in IEEE conferences and journals (© IEEE). Those figures and content from IEEE publications that are included in this book are printed with permission from the IEEE

All Rights Reserved

© 2007 Springer

No part of this work may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, microfilming, recording or otherwise, without written permission from the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work.

*To my wife Susan

(Show-Hsing) and my

daughters Wei Diana and

Ann - Charles*

*To my wife Zeina and my

children Nura, Tamara,

and Rami - Jamil*

# Contents

|                                                                    |           |

|--------------------------------------------------------------------|-----------|

| List of Figures                                                    | xiii      |

| List of Tables                                                     | xix       |

| Preface                                                            | xxi       |

| Acknowledgments                                                    | xxvii     |

| <b>1. INTRODUCTION</b>                                             | <b>1</b>  |

| 1.1 What is DFM/DFY                                                | 1         |

| 1.2 DFM/DFY Critical for IC Manufacturing                          | 2         |

| 1.2.1 New Materials                                                | 3         |

| 1.2.2 Sub-wavelength Lithography                                   | 6         |

| 1.2.3 New Devices                                                  | 9         |

| 1.2.4 Proliferation of Processes                                   | 12        |

| 1.2.5 Intra-die Variability                                        | 14        |

| 1.2.6 Error Free Masks Too Costly                                  | 15        |

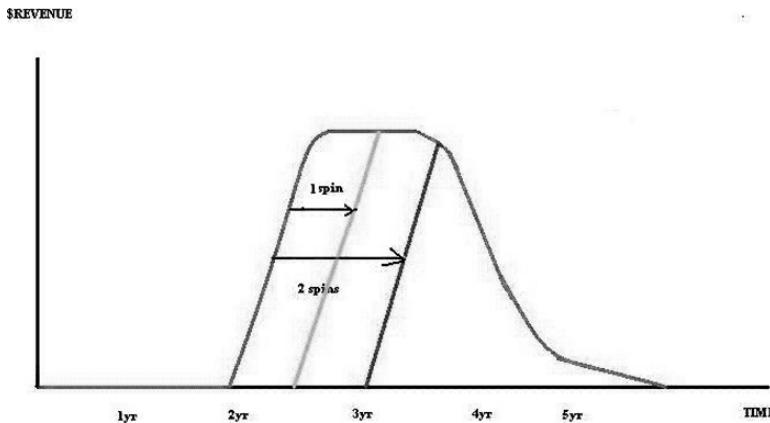

| 1.2.7 Cost of a Silicon Spin                                       | 15        |

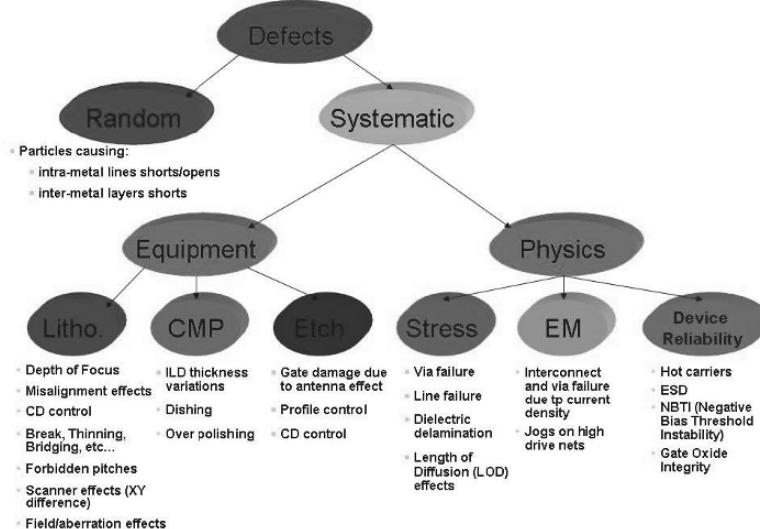

| 1.3 DFM Categories and Classifications                             | 16        |

| 1.3.1 First Time Failures                                          | 16        |

| 1.3.2 Time Related Failures                                        | 17        |

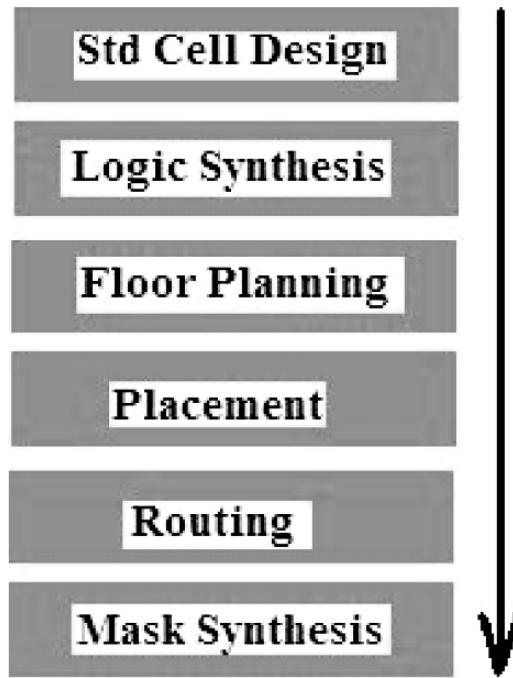

| 1.4 How Do Various DFM Solutions Tie up with Specific Design Flows | 17        |

| 1.5 DFM and DFY: Fully Intertwined                                 | 19        |

| <b>2. RANDOM DEFECTS</b>                                           | <b>21</b> |

| 2.1 Types of Defects                                               | 21        |

| 2.2 Concept of Critical Area                                       | 22        |

|       |                                                      |    |

|-------|------------------------------------------------------|----|

| 2.3   | Basic Models of Yield for Random Defects             | 23 |

| 2.4   | Critical Area Analysis (CAA)                         | 24 |

| 2.4.1 | Classical Methods of CA Extraction                   | 24 |

| 2.4.2 | Approximations                                       | 25 |

| 2.4.3 | Comparison of Approximate and Traditional CA         | 26 |

| 2.5   | Mathematical Formulation of Approximation Method     | 26 |

| 2.5.1 | Short Critical Area - Mathematical Formulation       | 27 |

| 2.5.2 | Open Critical Area - Mathematical Formulation        | 31 |

| 2.6   | Improving Critical Area                              | 34 |

| 2.6.1 | Cell Library Yield Grading                           | 34 |

| 2.6.2 | Average CA Yield Improvement                         | 36 |

| 2.6.3 | Weighted Average CA Yield Improvement                | 41 |

| 2.6.4 | Key Benefits of the Proposed Algorithm               | 47 |

| 2.7   | Experimental Results                                 | 48 |

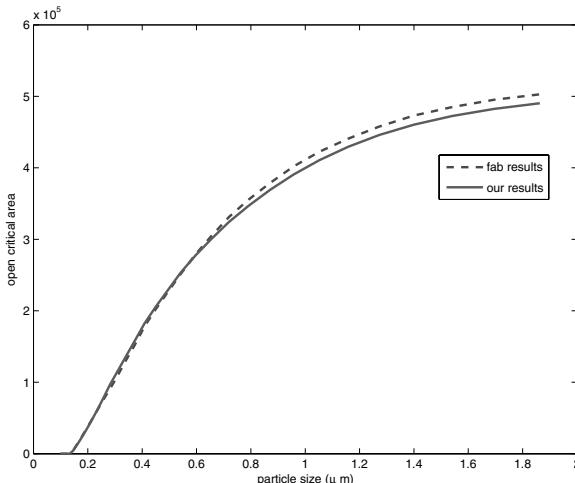

| 2.7.1 | Validation of Fast Critical Area Analysis Evaluation | 48 |

| 2.7.2 | Comparison of Critical Area Reductions               | 48 |

| 2.7.3 | Discussion                                           | 50 |

| 2.8   | Conclusions                                          | 51 |

| 3.    | SYSTEMATIC YIELD - LITHOGRAPHY                       | 53 |

| 3.1   | Introduction                                         | 53 |

| 3.2   | Optics Fundamentals                                  | 53 |

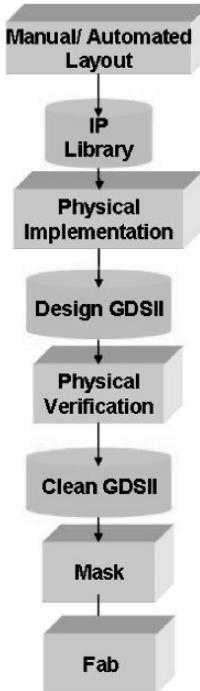

| 3.3   | Basic Design Flow                                    | 55 |

| 3.4   | Lithography and Process Issues                       | 57 |

| 3.4.1 | Masks Writing                                        | 57 |

| 3.4.2 | Optical System Interactions                          | 57 |

| 3.4.3 | Resist                                               | 57 |

| 3.4.4 | Etch                                                 | 58 |

| 3.5   | Resolution Enhancement Technique (RET)               | 58 |

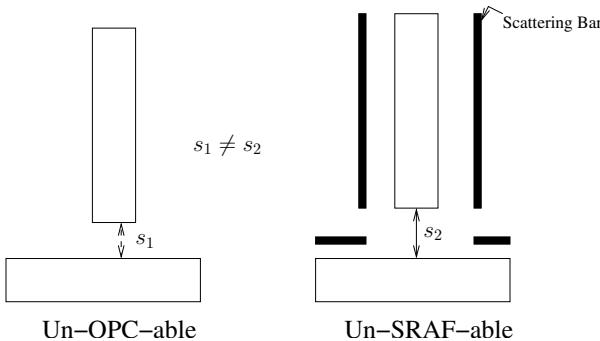

| 3.5.1 | Optical Proximity Correction (OPC)                   | 59 |

| 3.5.2 | Sub Resolution Assist Feature (SRAF)                 | 63 |

| 3.5.3 | Phase Shift Masks (PSM)                              | 65 |

| 3.5.4 | Off Axis Illumination (OAI)                          | 71 |

| 3.6   | Other Optical Techniques                             | 73 |

| 3.6.1 | Immersion Technology                                 | 73 |

| 3.6.2 | Double Dipole Lithography (DDL)                      | 73 |

|        |                                                        |     |

|--------|--------------------------------------------------------|-----|

| 3.6.3  | Chromeless Phase Lithography (CPL)                     | 74  |

| 3.7    | Lithography Aware Routing                              | 74  |

| 3.8    | RET and Lithography Verification                       | 75  |

| 3.8.1  | Lithography Rule Check (LRC)                           | 76  |

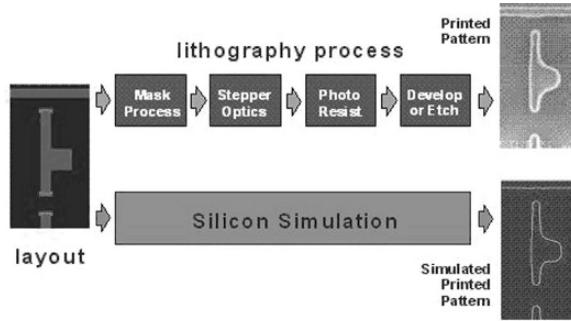

| 3.8.2  | Pattern Simulation                                     | 77  |

| 3.9    | Integrated Flow                                        | 77  |

| 3.9.1  | Mask Preparation and Repair                            | 77  |

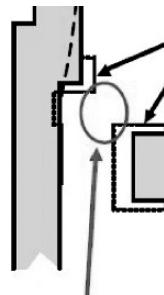

| 3.9.2  | Design Intent                                          | 79  |

| 3.9.3  | Silicon vs. Layout                                     | 80  |

| 3.10   | Yield Considerations                                   | 81  |

| 3.10.1 | Cell Design Considerations                             | 81  |

| 3.10.2 | Yield Optimized Routing                                | 82  |

| 3.11   | Practical Application                                  | 83  |

| 3.11.1 | Framing the problem                                    | 83  |

| 3.11.2 | Potential Solutions                                    | 84  |

| 3.11.3 | Proposed Solution                                      | 84  |

| 3.11.4 | Framing the Solution - Definitions and Presentation    | 85  |

| 3.11.5 | Litho-Hotspot Detection System                         | 88  |

| 3.11.6 | Summary & Results                                      | 95  |

| 3.12   | DFM & DFY Centric Summary                              | 96  |

| 3.13   | Lithography Specific Summary                           | 97  |

| 4.     | SYSTEMATIC YIELD - CHEMICAL MECHANICAL POLISHING (CMP) | 99  |

| 4.1    | Introduction                                           | 99  |

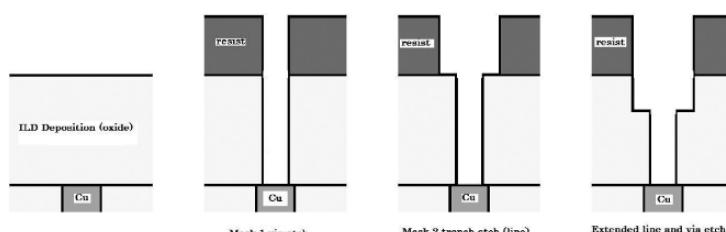

| 4.2    | The Dual Damascene Process                             | 100 |

| 4.2.1  | Via-first Dual-Damascene Process                       | 101 |

| 4.2.2  | The Dielectric                                         | 101 |

| 4.2.3  | The Metal Barrier                                      | 101 |

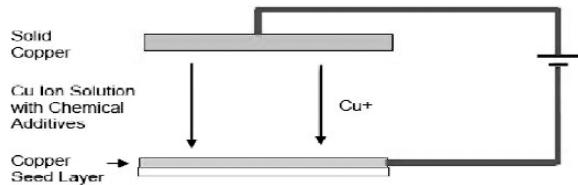

| 4.3    | Electroplating                                         | 102 |

| 4.3.1  | Procedure Description                                  | 102 |

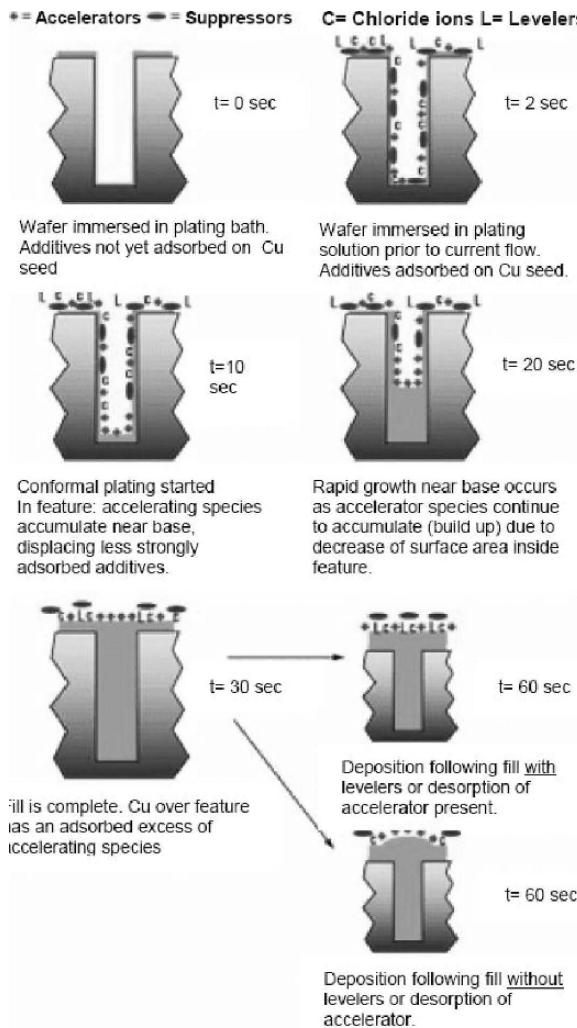

| 4.3.2  | Electroplating Model                                   | 105 |

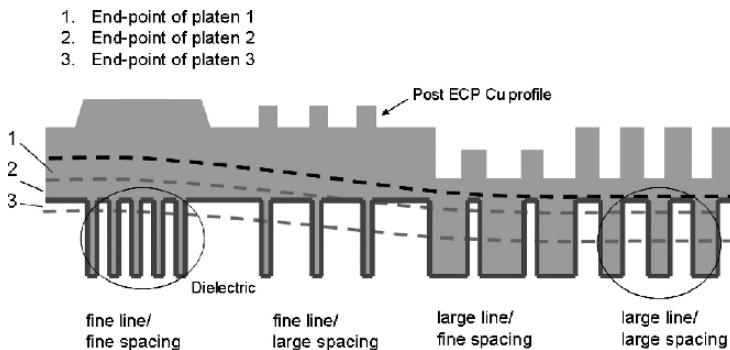

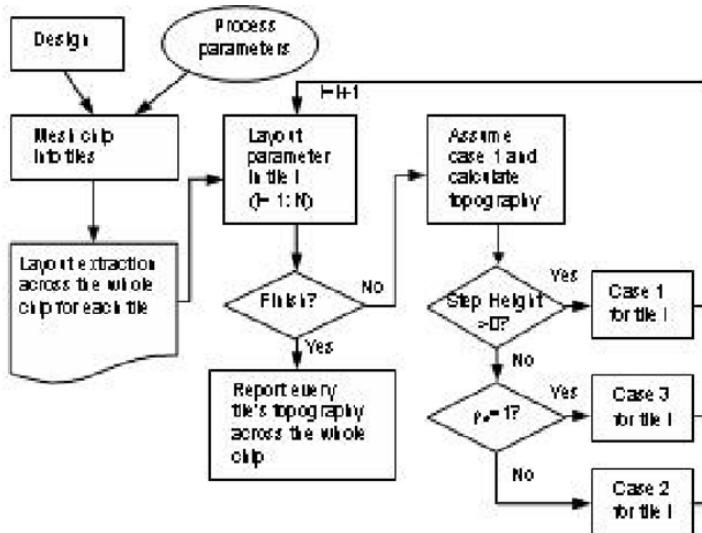

| 4.4    | A Full Chip Simulation Algorithm                       | 112 |

| 4.4.1  | Case Selection                                         | 113 |

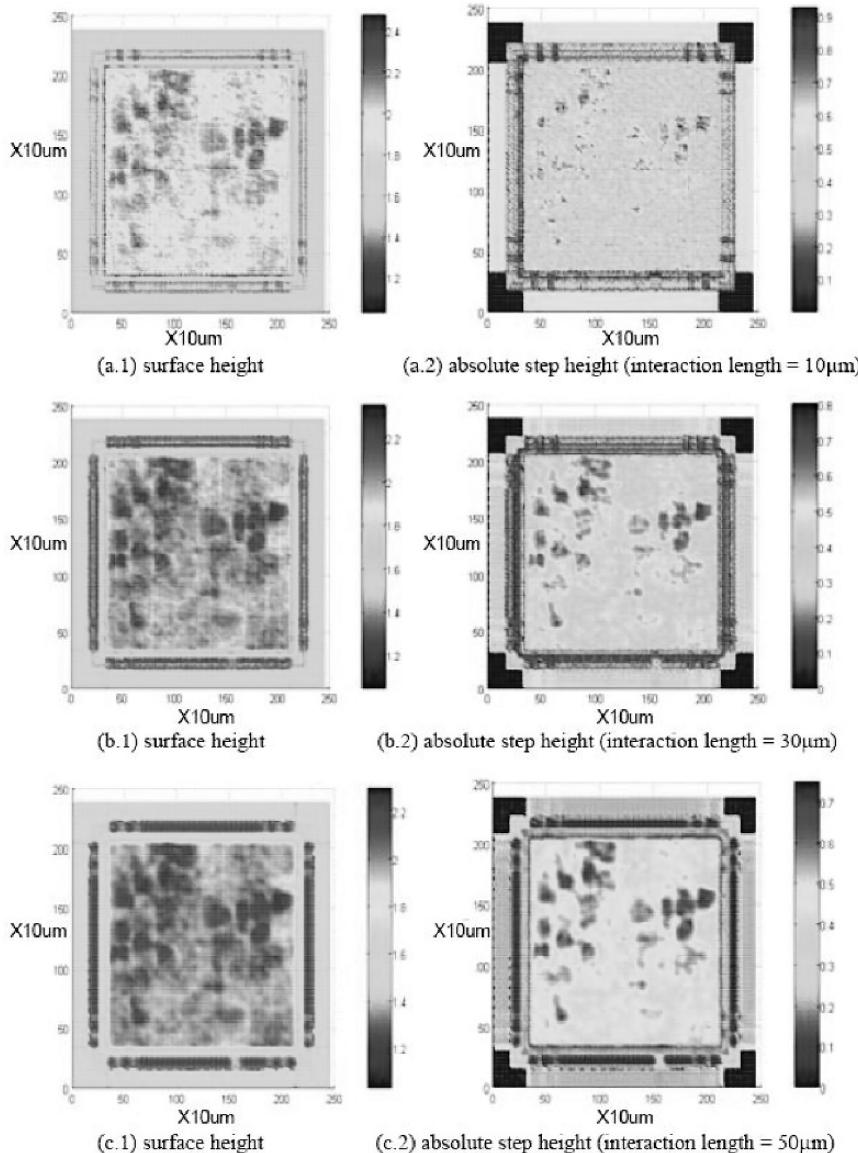

| 4.4.2  | Tile Size and Interaction Length                       | 115 |

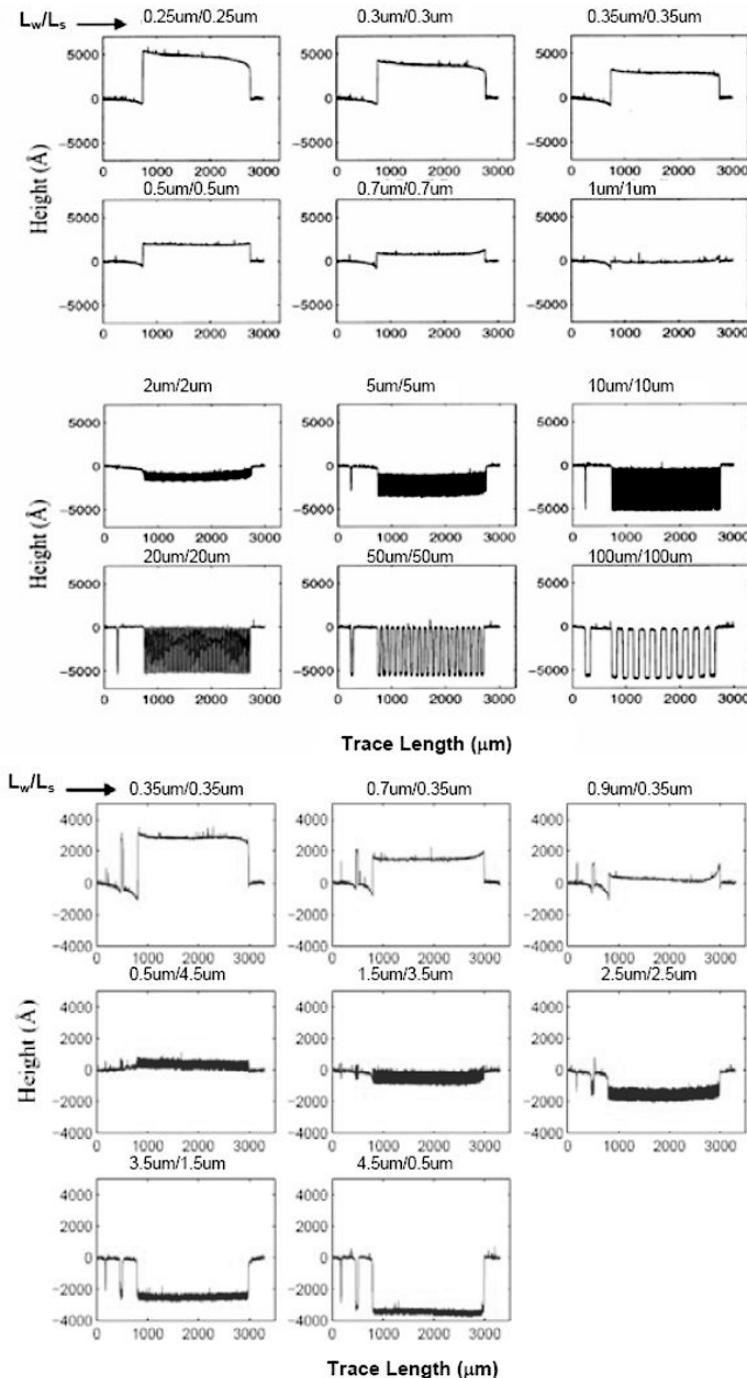

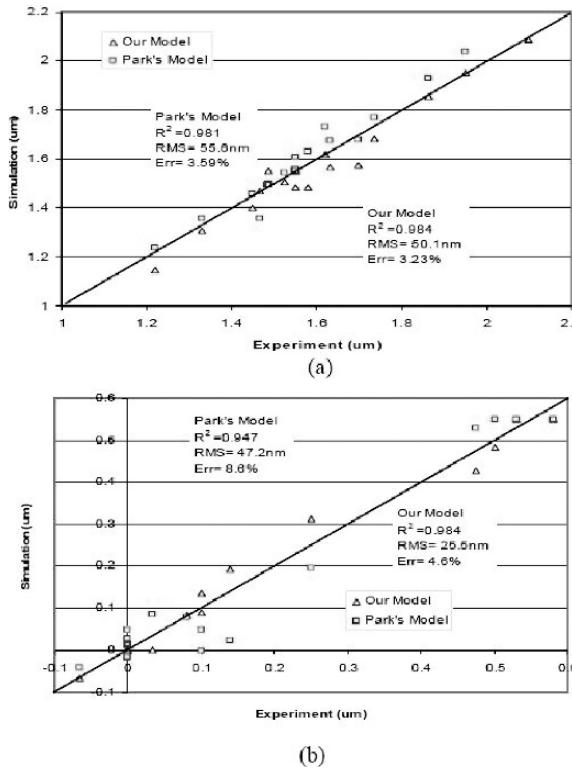

| 4.4.3  | Model Verification                                     | 116 |

|       |                                                    |     |

|-------|----------------------------------------------------|-----|

| 4.4.4 | Key Advantages of ECP Topography Model             | 121 |

| 4.5   | CMP                                                | 121 |

| 4.5.1 | CMP Process Description                            | 122 |

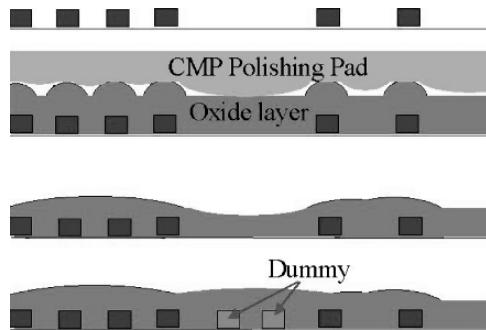

| 4.6   | Dummy Filling                                      | 124 |

| 4.6.1 | Rule Based                                         | 125 |

| 4.6.2 | Model Based                                        | 125 |

| 4.7   | Application: ILD CMP Model Based Dummy Filling     | 127 |

| 4.7.1 | Introduction                                       | 127 |

| 4.7.2 | The 2-D Low-pass-filter CMP Model                  | 128 |

| 4.7.3 | The Dummy Filling Problem                          | 128 |

| 4.7.4 | The Linear Programming Method                      | 129 |

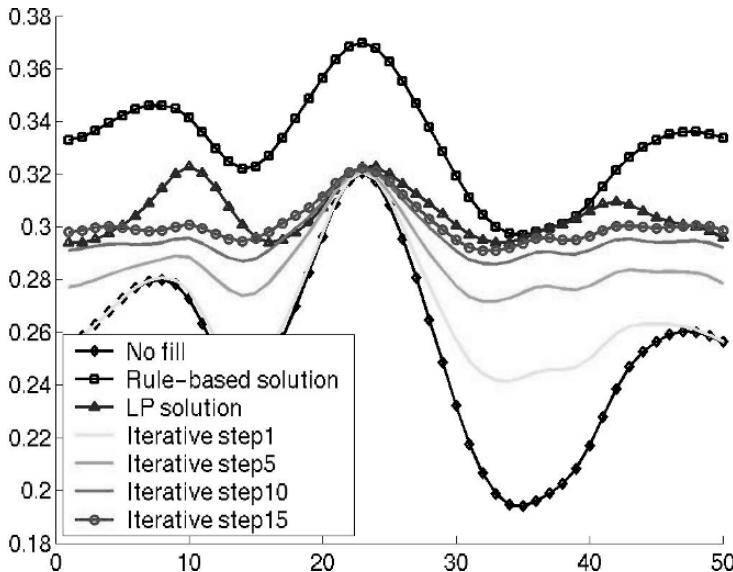

| 4.7.5 | The Min-variance Interactive Method                | 129 |

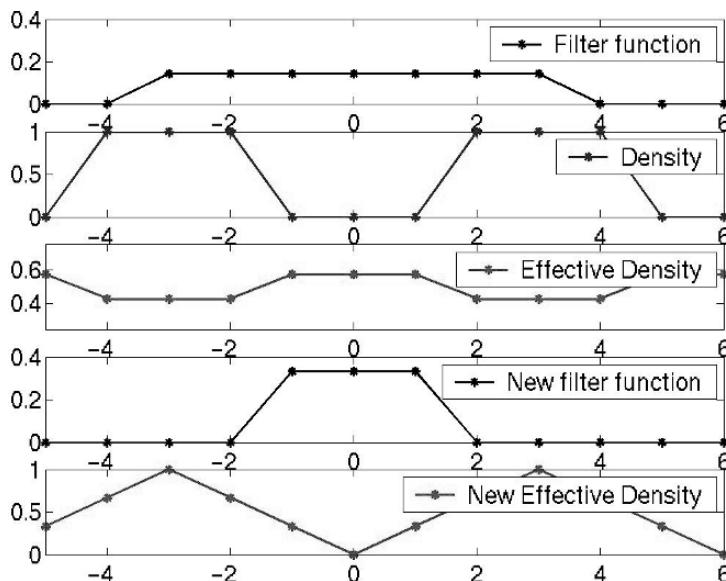

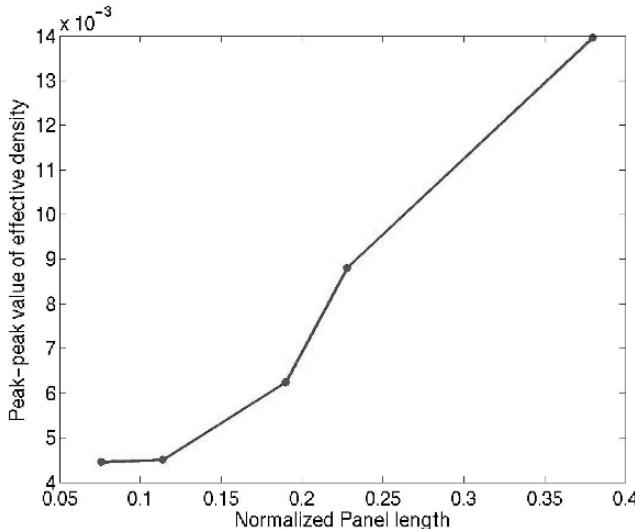

| 4.7.6 | Improving the Detection Capability                 | 132 |

| 4.7.7 | Simulation Results                                 | 134 |

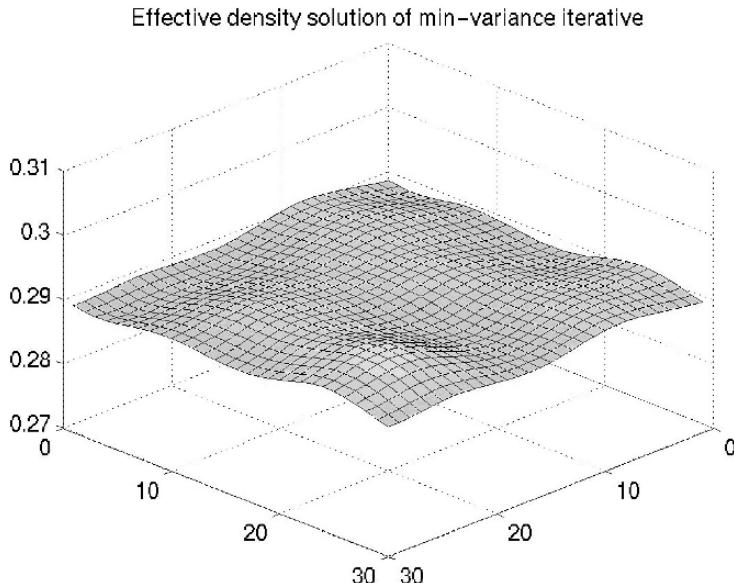

| 4.8   | Application: Cu CMP Model Based Dummy Filling      | 139 |

| 4.8.1 | Why Model Based Metal Filling?                     | 139 |

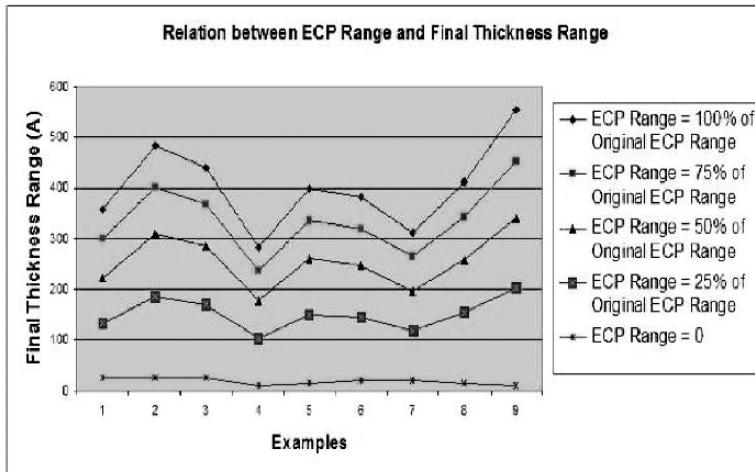

| 4.8.2 | Predictors of the Final (Post-CMP) Thickness Range | 140 |

| 4.8.3 | ECP Thickness Versus Final Thickness               | 141 |

| 4.8.4 | Effective Density Versus Final Thickness           | 141 |

| 4.8.5 | Details of the Proposed Metal Filling Algorithm    | 142 |

| 4.8.6 | Experimental Results                               | 148 |

| 4.8.7 | Discussion of Results                              | 148 |

| 5.    | VARIABILITY & PARAMETRIC YIELD                     | 151 |

| 5.1   | Introduction to Variability and Parametric Yield   | 151 |

| 5.2   | Nature of Variability                              | 151 |

| 5.3   | Source of Variability                              | 152 |

| 5.3.1 | Wafer Level Variability                            | 153 |

| 5.3.2 | Materials Based Variability                        | 155 |

| 5.3.3 | Atomistic Variability                              | 157 |

| 5.3.4 | Lithography Based Variability                      | 157 |

| 5.3.5 | Local Variability                                  | 159 |

| 5.3.6 | Environmental Variability & Aging                  | 159 |

| 5.3.7 | Device and Interconnect Parameters Variability     | 162 |

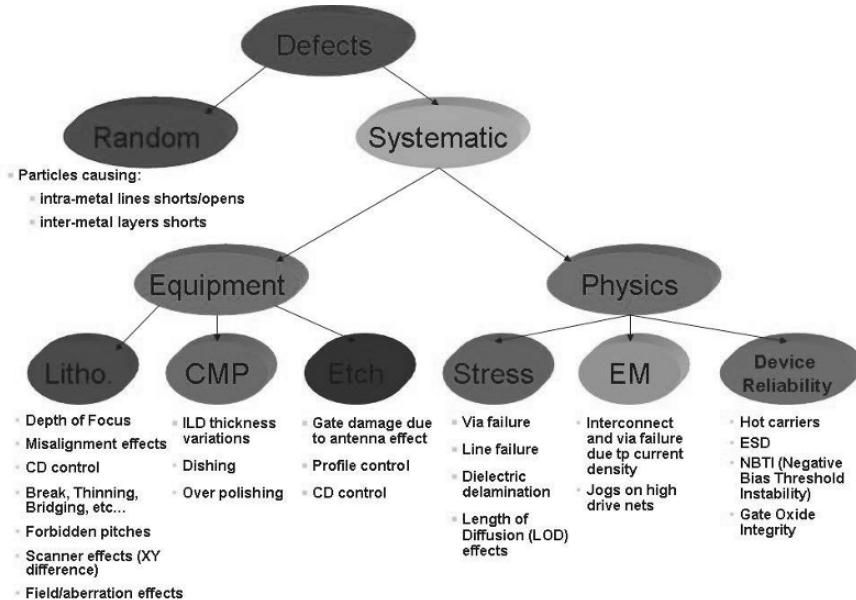

| 5.4   | Yield Loss Sources & Mechanisms                    | 164 |

| 5.5   | Parametric Yield                                   | 166 |

|       |                                                      |     |

|-------|------------------------------------------------------|-----|

| 5.6   | Parametric Yield Test Structures                     | 167 |

| 5.7   | Variability & Parametric Yield Summary & Conclusions | 168 |

| 6.    | DESIGN FOR YIELD                                     | 169 |

| 6.1   | Introduction                                         | 169 |

| 6.2   | Static Timing and Power Analysis                     | 170 |

| 6.2.1 | Overview                                             | 170 |

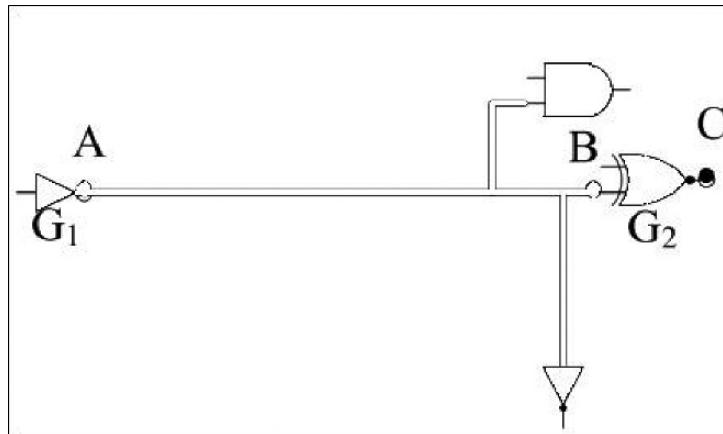

| 6.2.2 | Critical Path Method (CPM)                           | 171 |

| 6.3   | Design in the Presence of Variability                | 172 |

| 6.4   | Statistical Timing Analysis                          | 173 |

| 6.4.1 | Overview                                             | 173 |

| 6.4.2 | SSTA: Issues, Concerns, and Approaches               | 175 |

| 6.4.3 | Parametric and Delay Modeling PDFs                   | 177 |

| 6.4.4 | Correlation Issues                                   | 178 |

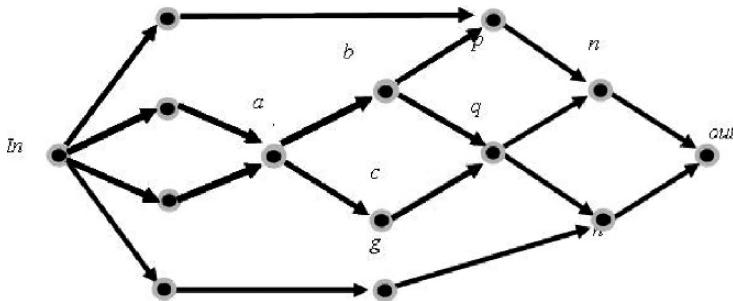

| 6.5   | A Plurality of SSTA Methodologies                    | 180 |

| 6.5.1 | Early SSTA Approach: Using Continuous PDFs           | 180 |

| 6.5.2 | Four Block-based Approaches                          | 181 |

| 6.6   | Bounding Approaches                                  | 185 |

| 6.7   | Statistical Design Optimization                      | 186 |

| 6.8   | On Chip Optimization Techniques                      | 188 |

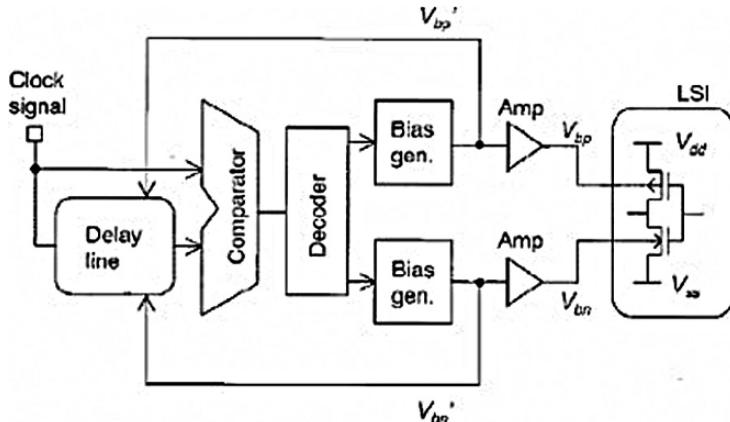

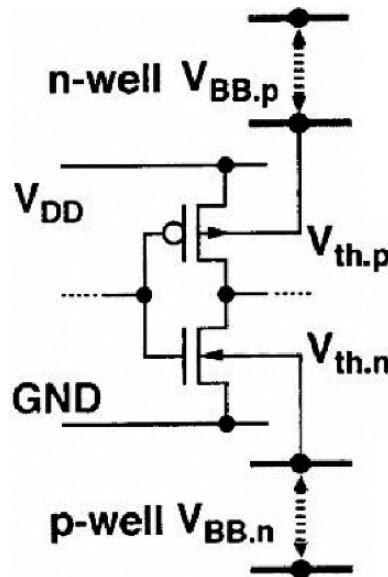

| 6.8.1 | Adaptive Body-biasing                                | 190 |

| 6.8.2 | Adaptive Voltage Scaling                             | 191 |

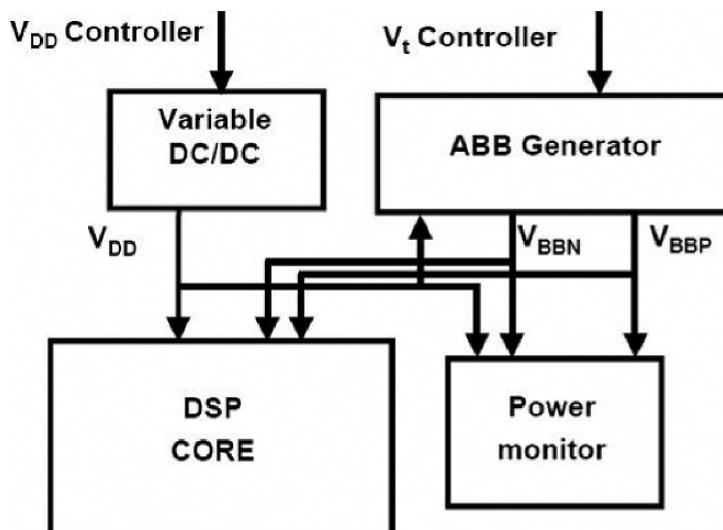

| 6.8.3 | A Combination                                        | 191 |

| 6.9   | Summary: Design for Yield                            | 192 |

| 6.9.1 | Summary for SSTA                                     | 192 |

| 6.9.2 | Summary for Statistical Design Optimization          | 192 |

| 7.    | YIELD PREDICTION                                     | 195 |

| 7.1   | Introduction                                         | 195 |

| 7.2   | Yield Loss Sources & Mechanisms                      | 196 |

| 7.3   | Yield Modeling                                       | 196 |

| 7.3.1 | Early Work in Yield Modeling                         | 196 |

| 7.4   | Yield Enhancement Mechanisms                         | 199 |

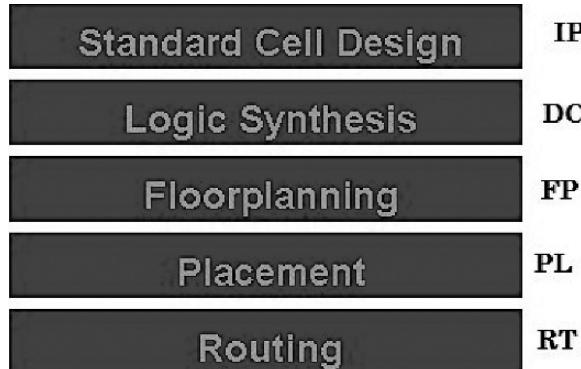

| 7.4.1 | IP Development                                       | 199 |

| 7.4.2 | Synthesis                                            | 199 |

| 7.4.3 | Placement and Routing                                | 199 |

|       |                                                       |     |

|-------|-------------------------------------------------------|-----|

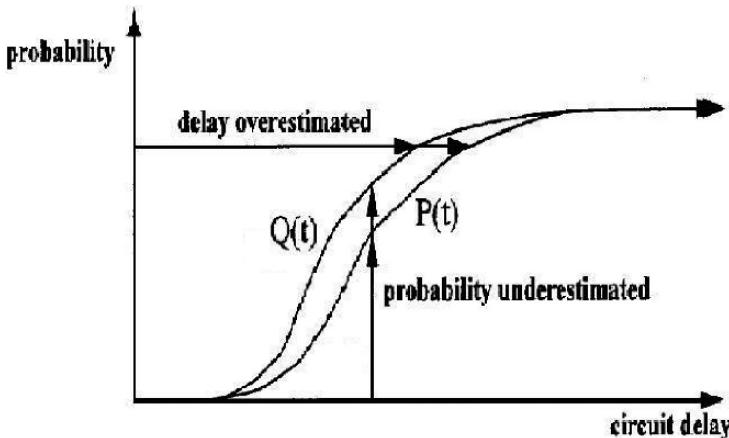

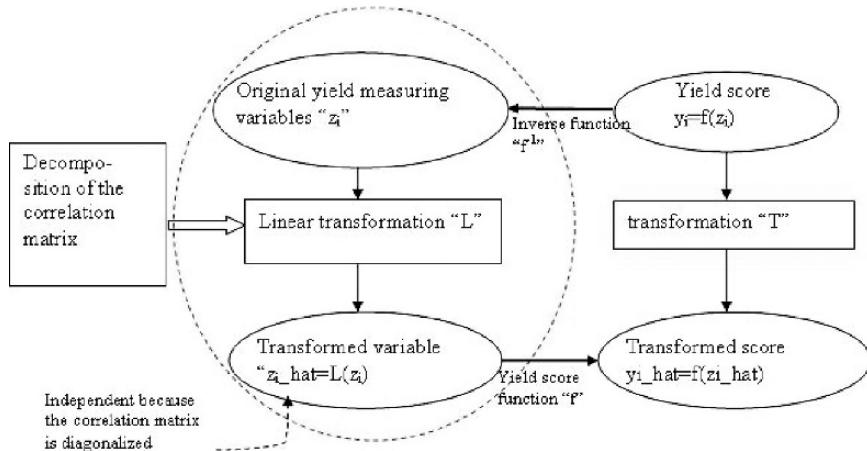

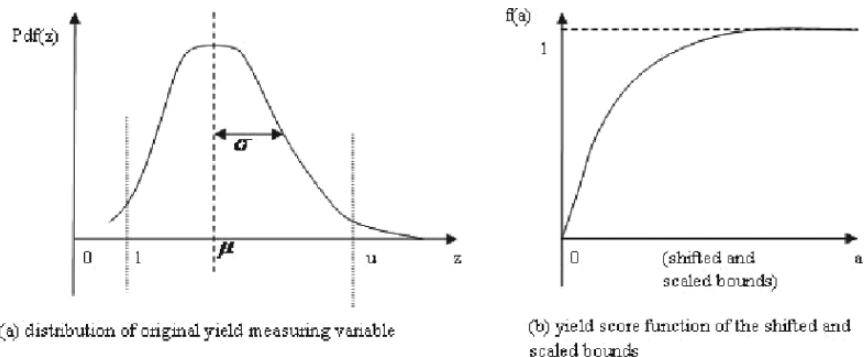

| 7.5   | EDA Application I                                     | 200 |

| 7.5.1 | Preliminary Definitions & the cdf Approach            | 200 |

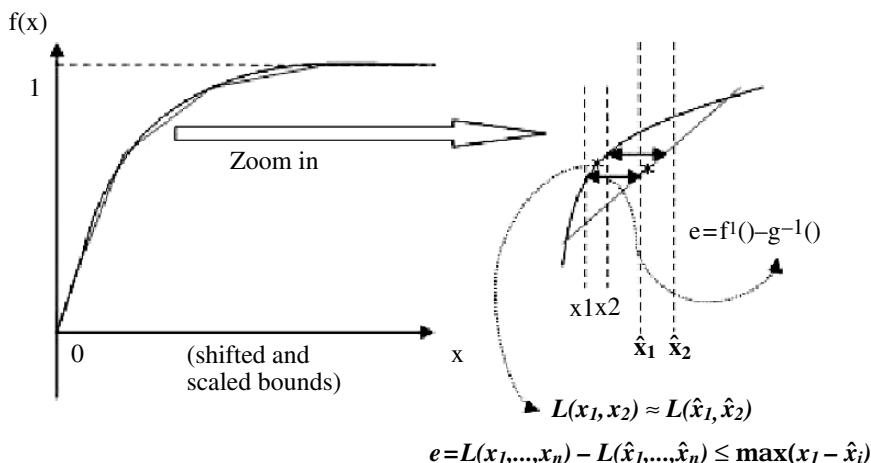

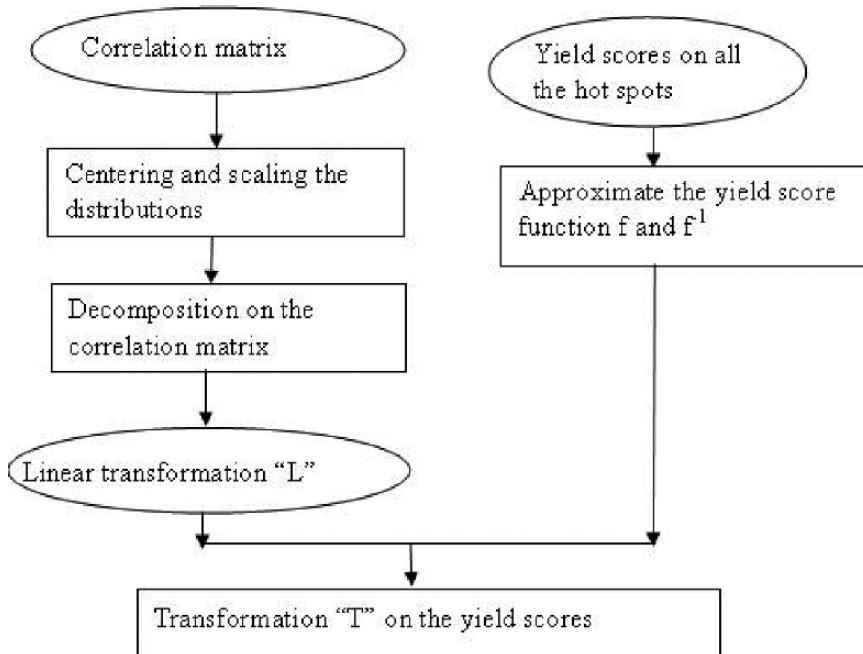

| 7.5.2 | Our Proposed Solution                                 | 201 |

| 7.5.3 | A Brief Description of the Key Ideas                  | 203 |

| 7.5.4 | Example and Results                                   | 208 |

| 7.6   | EDA Application II                                    | 211 |

| 7.6.1 | Background                                            | 211 |

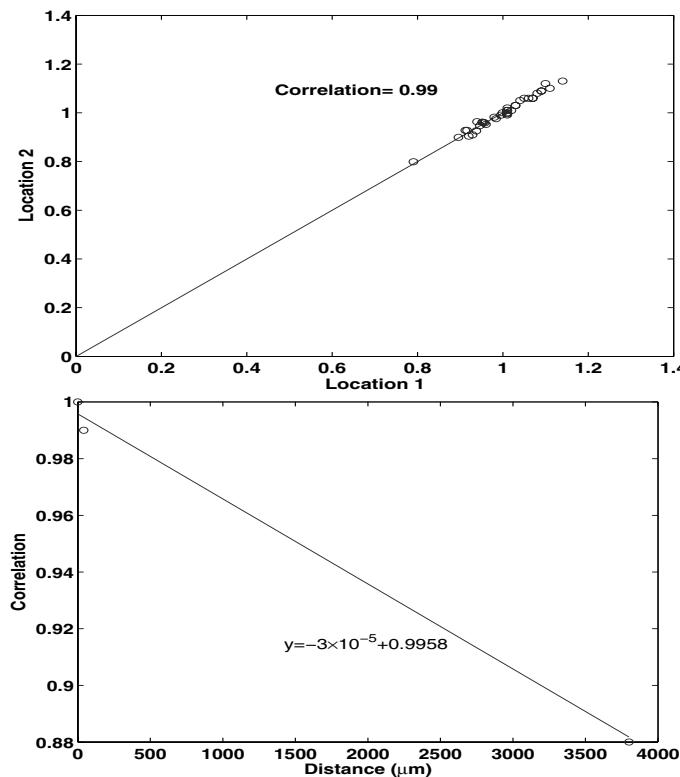

| 7.6.2 | Variation Decomposition                               | 212 |

| 7.6.3 | Variations Handled by Hotspot Model                   | 214 |

| 7.6.4 | Application Example: CMP Yield                        | 214 |

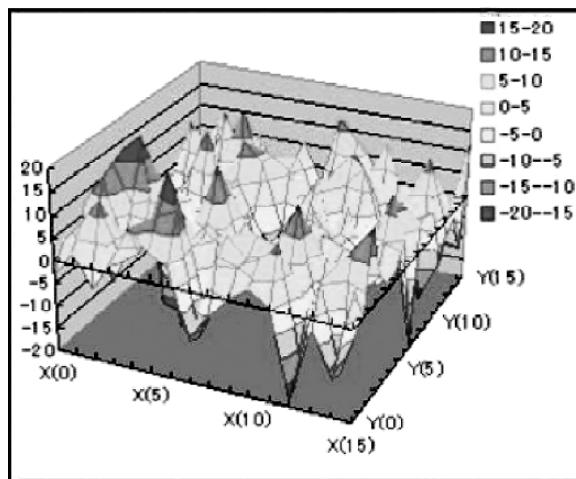

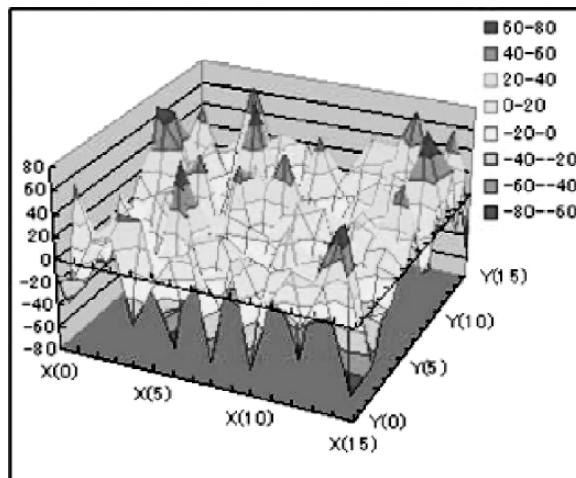

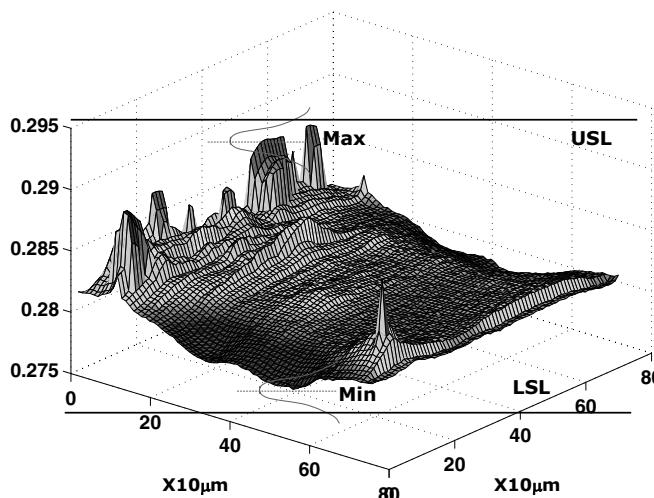

| 7.7   | CMP Yield Prediction Model                            | 215 |

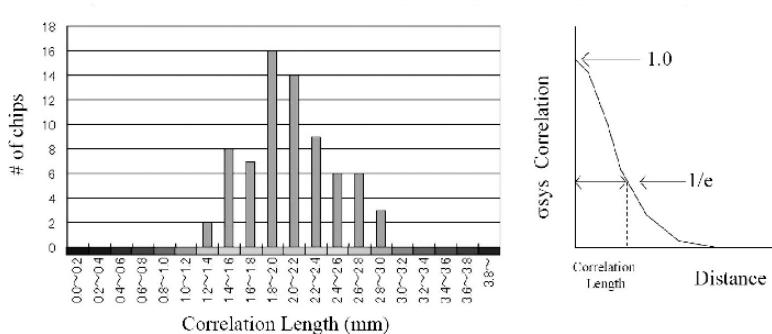

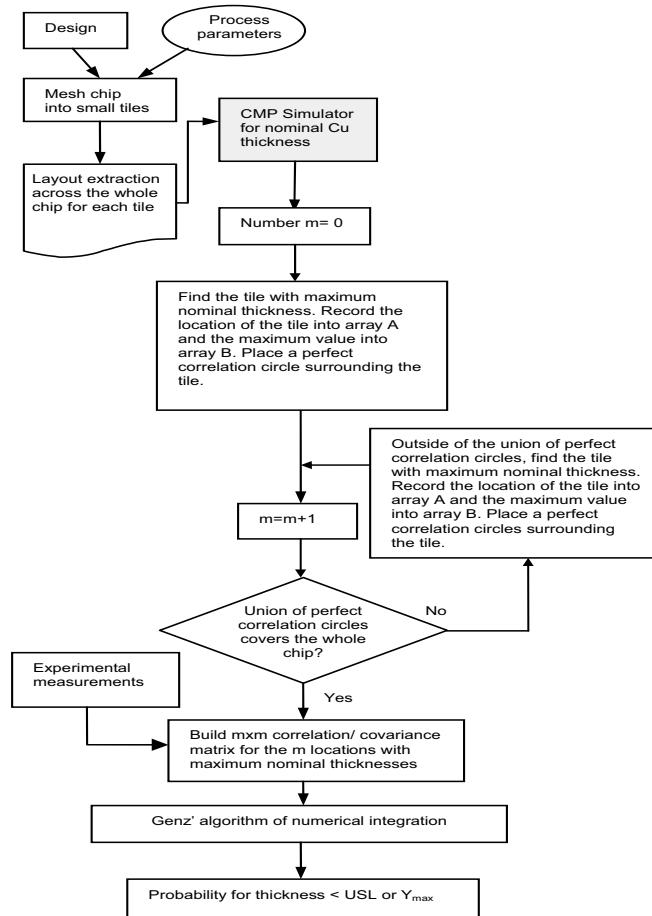

| 7.7.1 | Yield Prediction Algorithm                            | 216 |

| 7.7.2 | Simulation Examples                                   | 224 |

| 7.7.3 | Recap and some conclusions                            | 225 |

| 7.7.4 | Summary and Conclusions                               | 226 |

| 8.    | CONCLUSIONS                                           | 227 |

| 8.1   | The Case for a DFM/DFY Driven Design                  | 227 |

| 8.2   | Design Intent Manufacturing (Lithography) Centric DFM | 228 |

| 8.3   | Yield Centric DFM                                     | 229 |

| 8.4   | DFM/DFY EDA Design Tools                              | 229 |

| 8.4.1 | Implementation                                        | 231 |

| 8.4.2 | Physical Verification                                 | 235 |

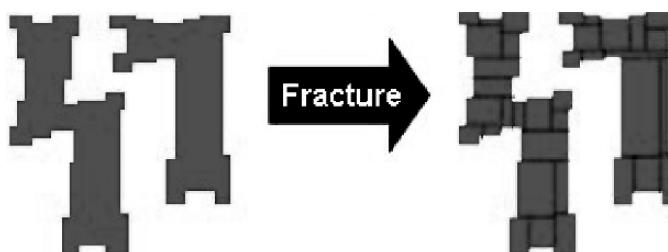

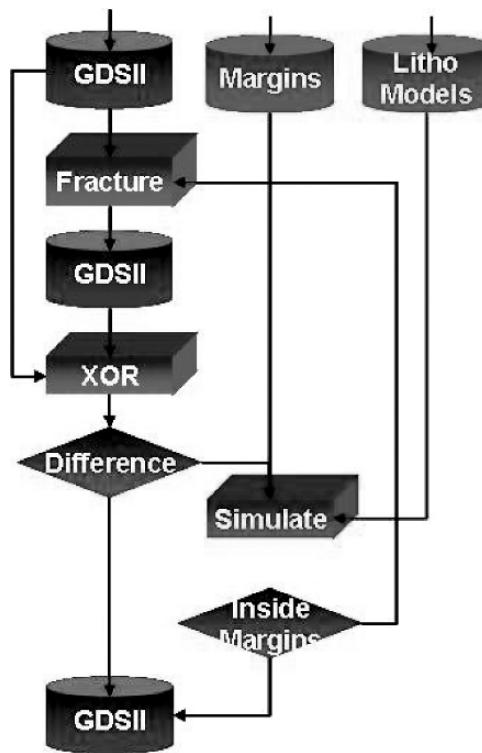

| 8.4.3 | Mask Synthesis                                        | 236 |

| 8.4.4 | Mask Inspection                                       | 237 |

| 8.4.5 | TCAD                                                  | 239 |

| 8.4.6 | Process Modeling and Simulation                       | 239 |

| 8.5   | Design Variability                                    | 240 |

| 8.6   | Closing Remarks                                       | 240 |

|       | References                                            | 243 |

|       | Index                                                 | 253 |

# List of Figures

|      |                                                                                          |    |

|------|------------------------------------------------------------------------------------------|----|

| 1.1  | Cu Cross Section Showing Potential Problems                                              | 4  |

| 1.2  | Basic Gate Illustration                                                                  | 4  |

| 1.3  | $NA = I \sin \alpha$                                                                     | 8  |

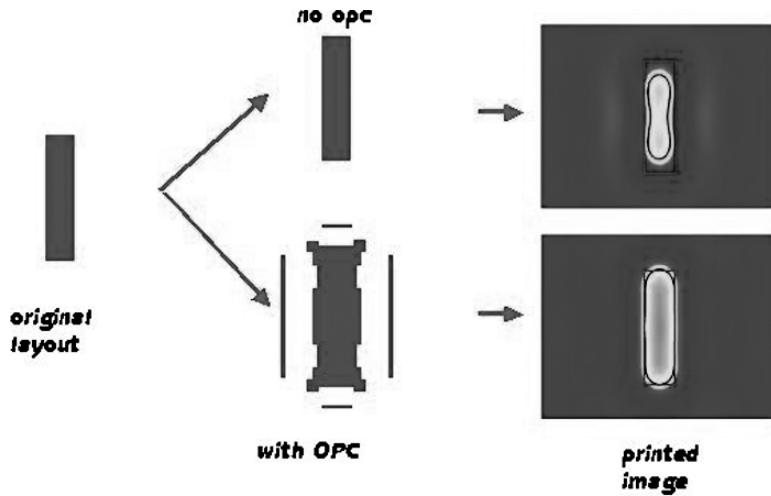

| 1.4  | Basic Example of OPC at 180nm                                                            | 9  |

| 1.5  | Example of Strong (180) PSM                                                              | 9  |

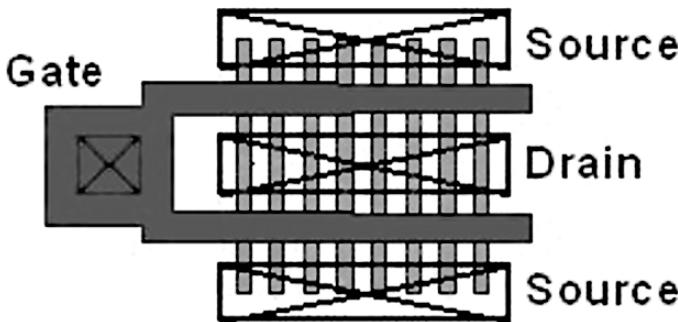

| 1.6  | Double-gate FET                                                                          | 10 |

| 1.7  | TCAD Simulated FinFET                                                                    | 11 |

| 1.8  | Layout of Multi-segment FinFET                                                           | 11 |

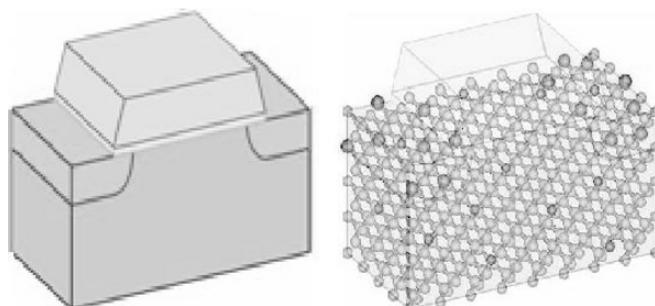

| 1.9  | Simulated 5nm MOSFET with Silicon Crystal<br>Superimposed Next to A Bulk-CMOS Equivalent | 13 |

| 1.10 | Revenue as a Function of Design Cycle                                                    | 16 |

| 1.11 | Typical ASIC Design Flow                                                                 | 18 |

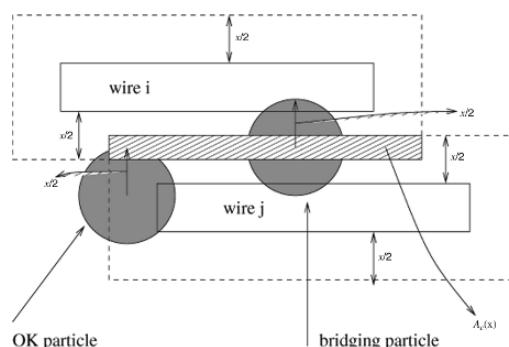

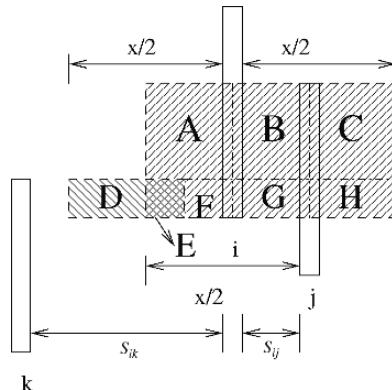

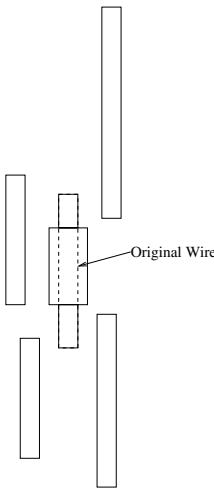

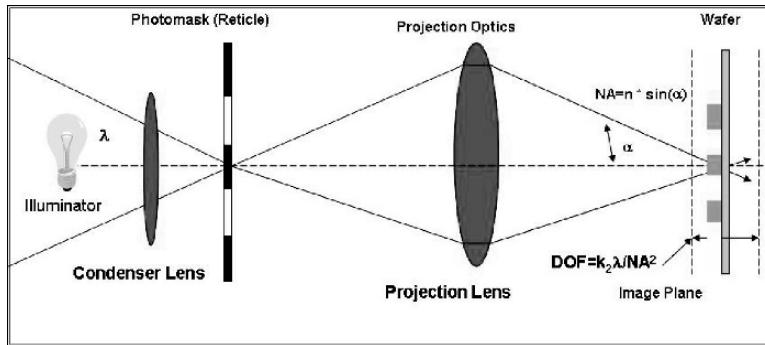

| 2.1  | Short CA Between Two Wires Caused by Particles with Size $x$                             | 22 |

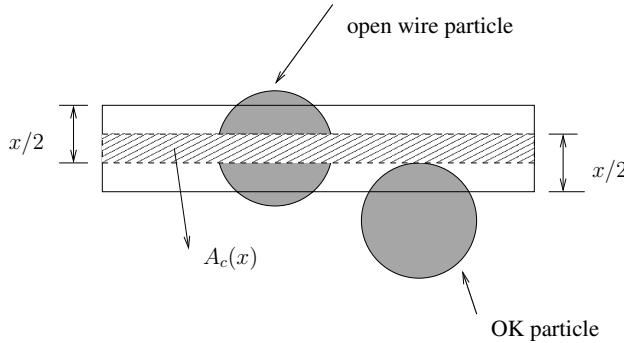

| 2.2  | Open CA on a Wire Caused by Particles with Size $x$                                      | 23 |

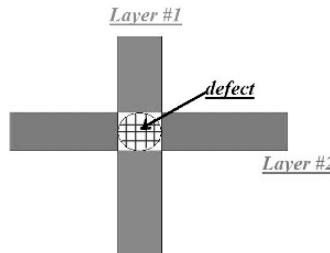

| 2.3  | Intra-layers Defect Particle Resulting in an Open or Short                               | 23 |

| 2.4  | Typical Short Critical Area                                                              | 28 |

| 2.5  | Short Critical Area at Large Defect Size                                                 | 28 |

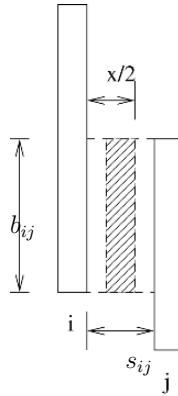

| 2.6  | Open Critical Area on Wire $i$                                                           | 32 |

| 2.7  | Example of Improving Poly Short CA and M1 Open CA                                        | 35 |

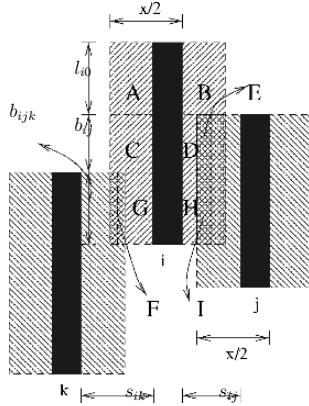

| 2.8  | Illustration of Wire Pushing                                                             | 40 |

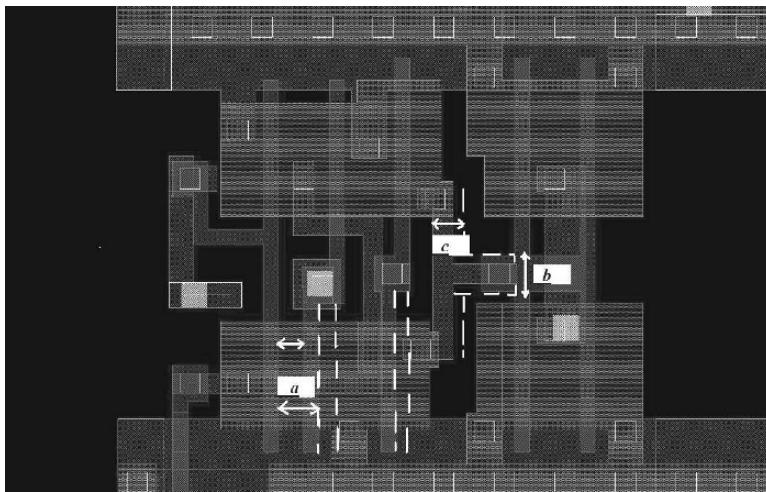

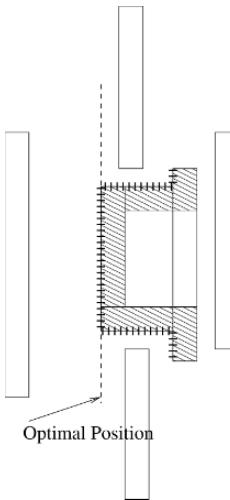

| 2.9  | Illustration of Wire-widening                                                            | 47 |

| 2.10 | Open Critical Area Correlation                                                           | 48 |

| 2.11 | Short Critical Area Correlation                                                          | 49 |

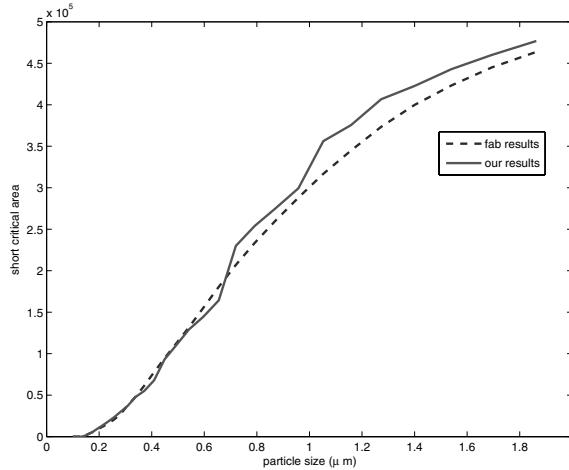

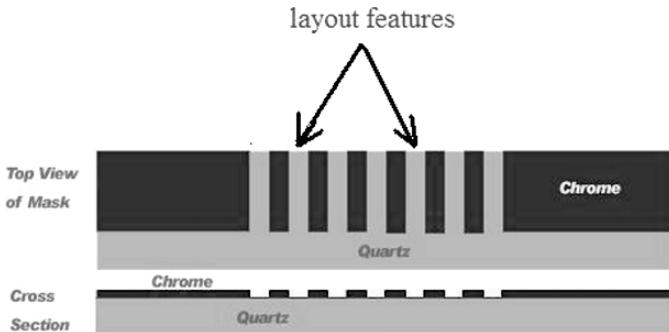

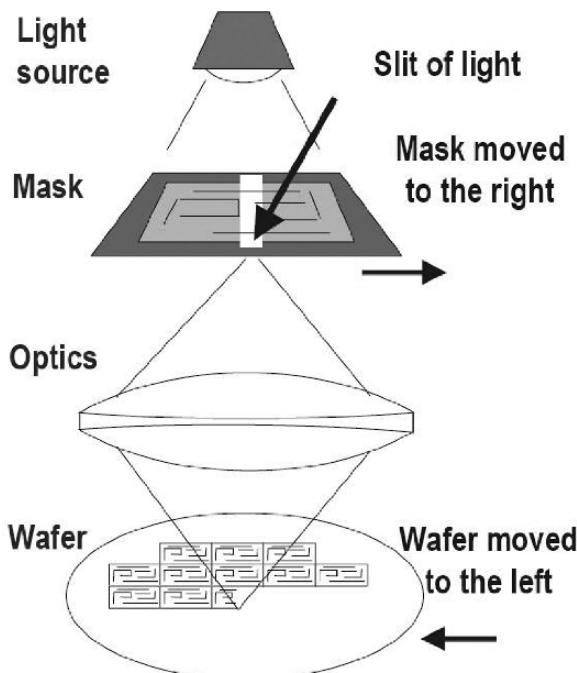

| 3.1  | Basic Optical Lithography IC Manufacturing System                                        | 54 |

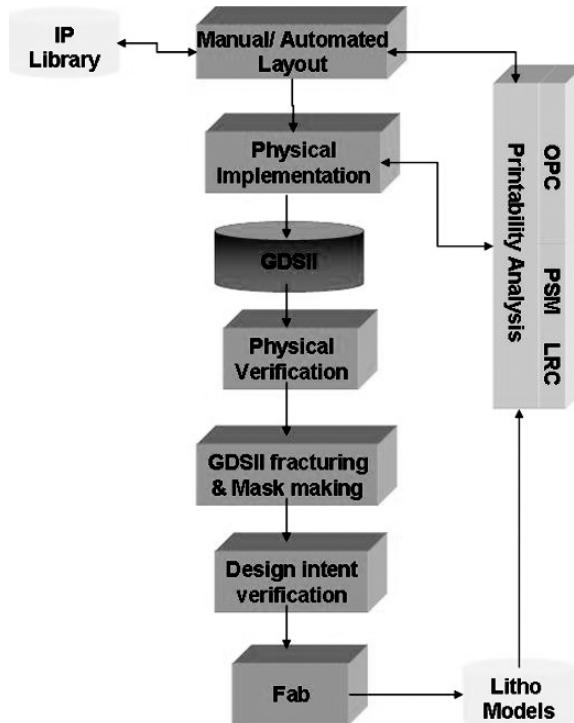

| 3.2  | Basic Design flow                                                                        | 56 |

|      |                                                                             |    |

|------|-----------------------------------------------------------------------------|----|

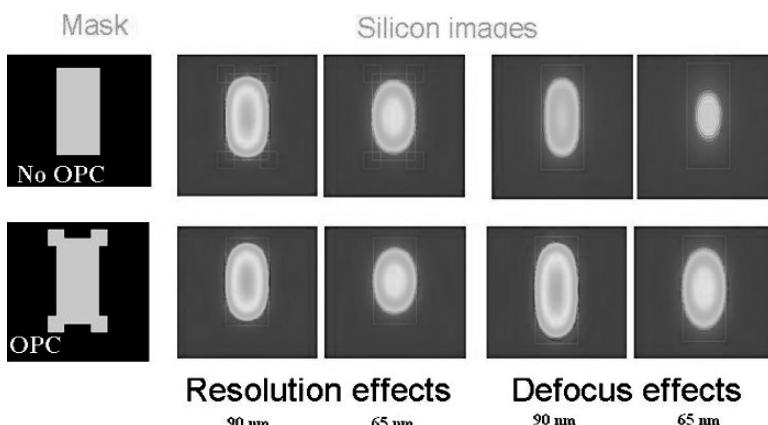

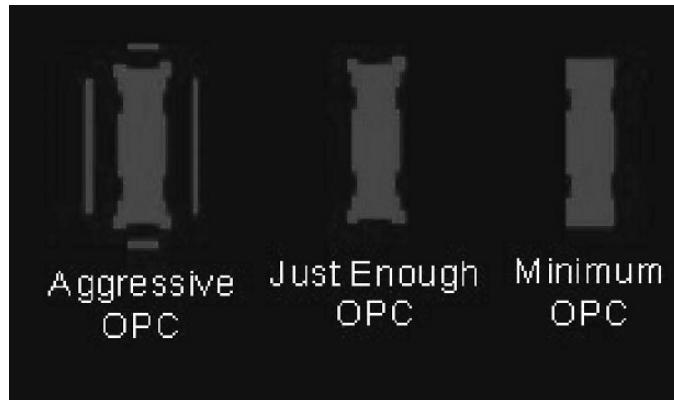

| 3.3  | Impact of OPC on Printability at 90 nm (Zero Defocus)                       | 59 |

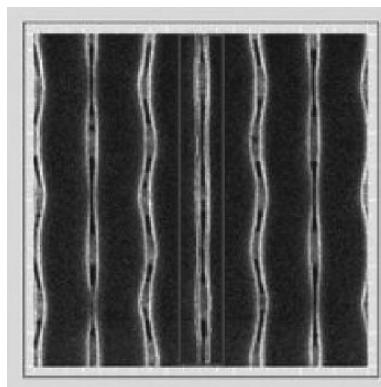

| 3.4  | Silicon Wafter Image with/without OPC<br>and with/without Defocus           | 60 |

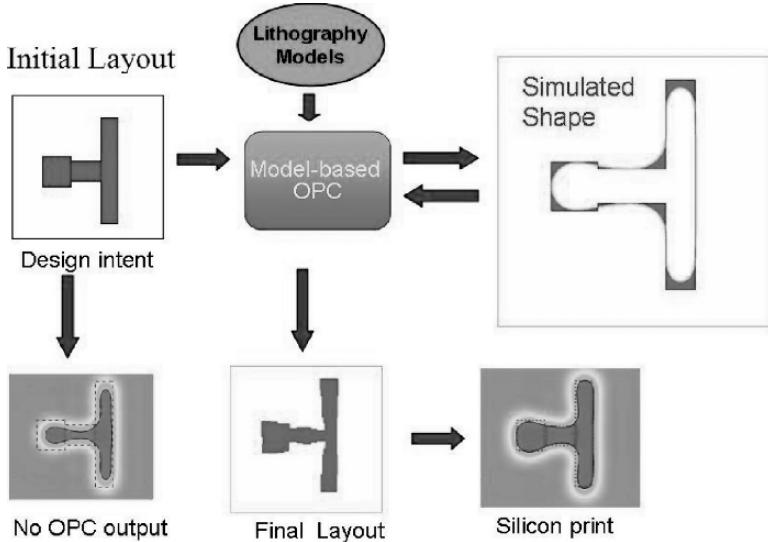

| 3.5  | Model Based OPC Flow                                                        | 62 |

| 3.6  | Layout                                                                      | 63 |

| 3.7  | A Case Where Rule Based OPC Is Good Enough                                  | 63 |

| 3.8  | OPC'd Geometry with Scatter Bars (SRAFs)                                    | 64 |

| 3.9  | Printability of Isolated Feature, No Scatter Bar                            | 64 |

| 3.10 | Printability of Isolated Feature, with Scatter Bar                          | 65 |

| 3.11 | A Dark Field (Positive) Binary Mask                                         | 65 |

| 3.12 | Basic Illustration of the Light-mask-resist Interaction                     | 66 |

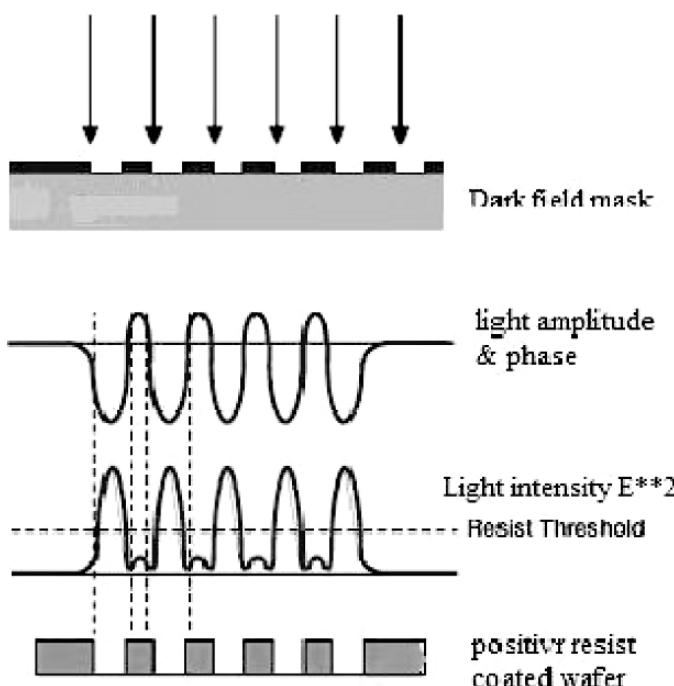

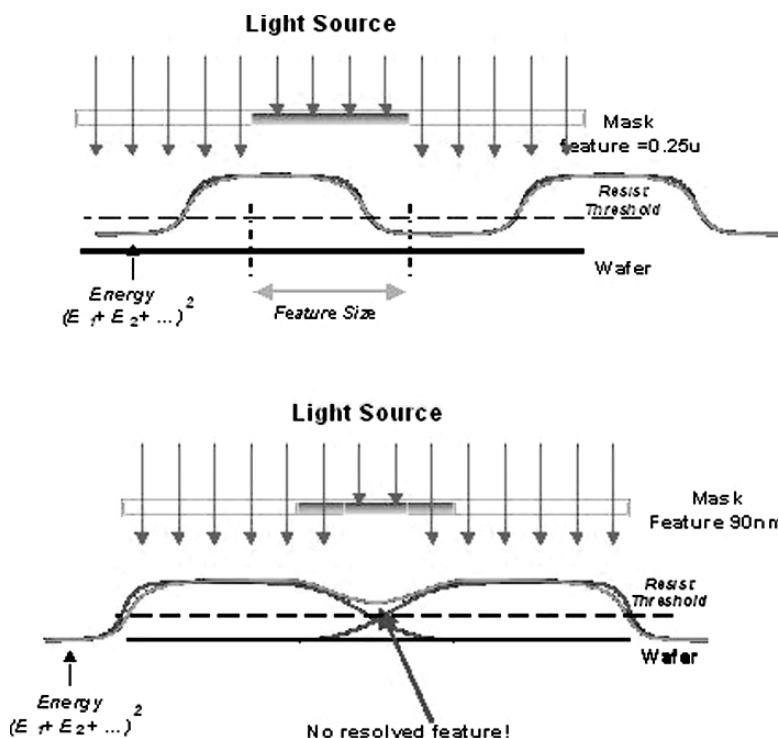

| 3.13 | Illustration of Resolution Problem with Regular Mask                        | 67 |

| 3.14 | Illustration of the Resolution Enhancement Due to 180° Phase<br>Inversion   | 68 |

| 3.15 | Illustration of a Layout with Phase Assignment Conflict                     | 68 |

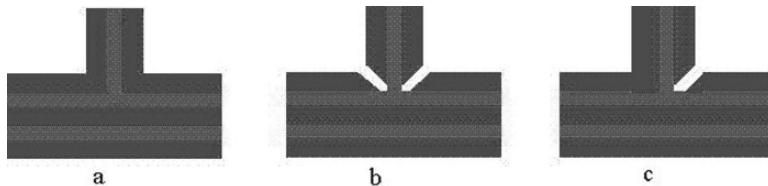

| 3.16 | Three Implementation of a Layout, Two have Phase Conflicts                  | 69 |

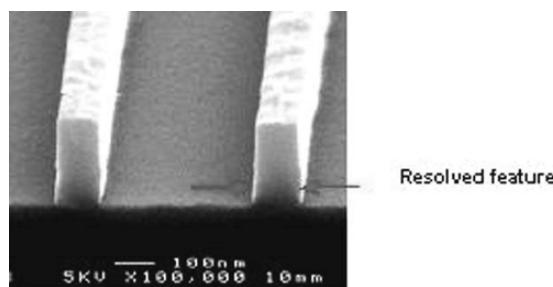

| 3.17 | Resolved Feature with PSM                                                   | 69 |

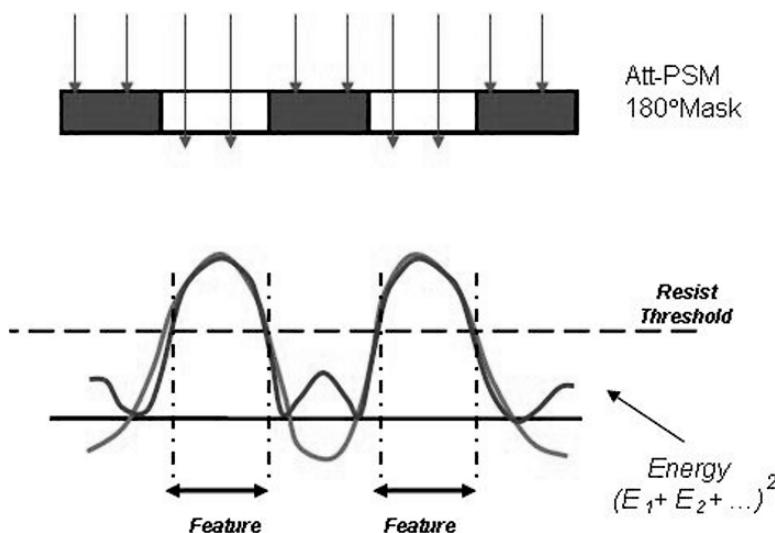

| 3.18 | Illustration of Concept of Attenuated PSM                                   | 70 |

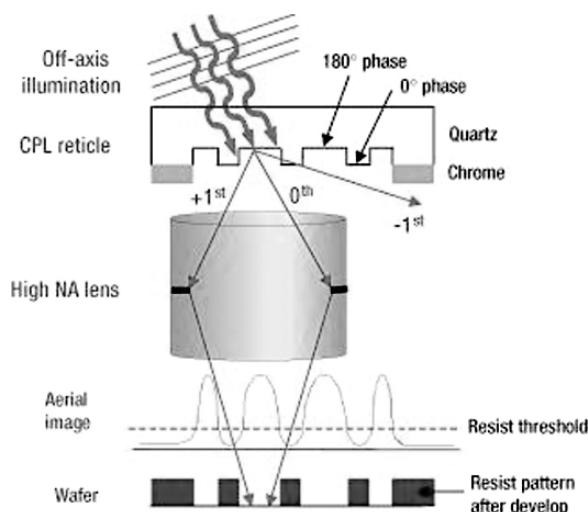

| 3.19 | Illustration of Off-axis Illumination                                       | 71 |

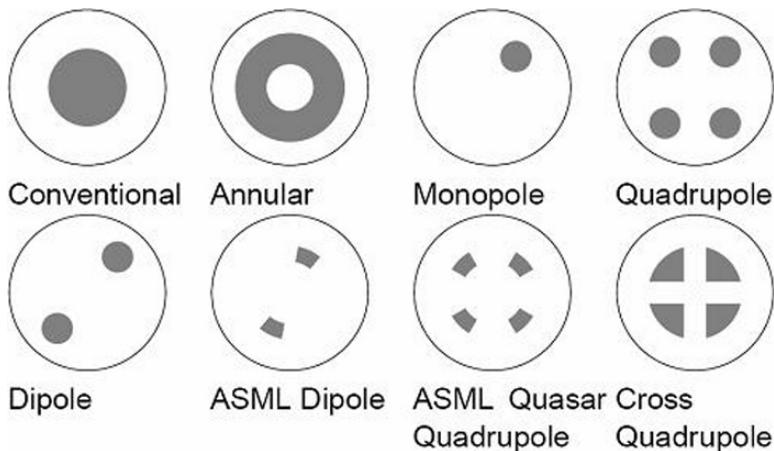

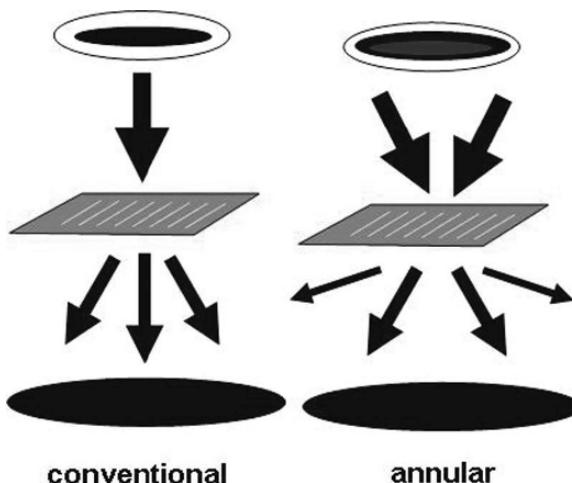

| 3.20 | Eight Different Filtering Pupil Alternatives                                | 72 |

| 3.21 | Illustration the Different Between Conventional<br>and Annular Illumination | 72 |

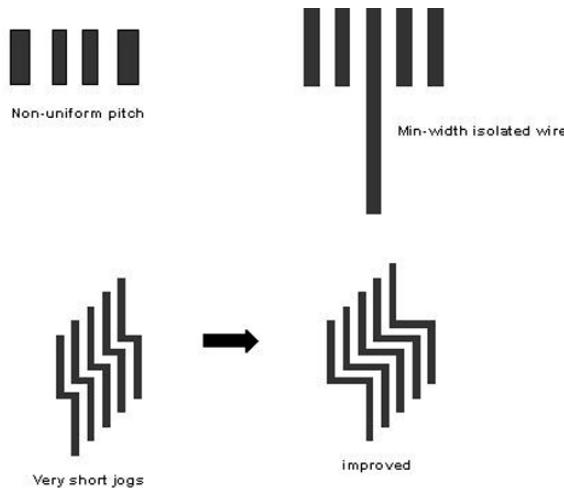

| 3.22 | Problem Place and Route Patterns                                            | 75 |

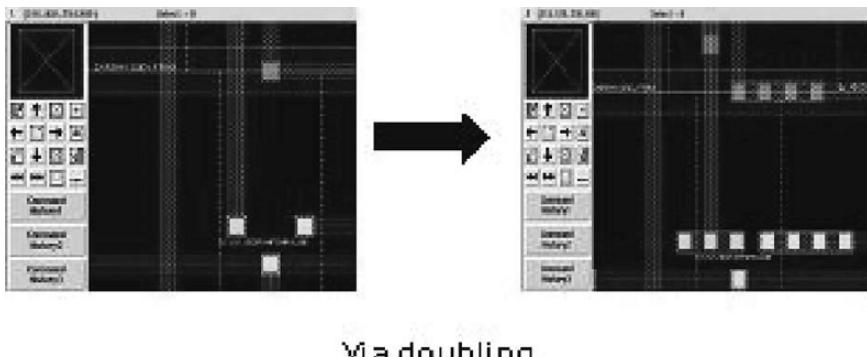

| 3.23 | ICC Place and Route Tool Implementation of Via Doubling                     | 75 |

| 3.24 | Three Known Problem Patterns from a 65nm LRC Library                        | 76 |

| 3.25 | Design Flow Including OPC and LRC                                           | 78 |

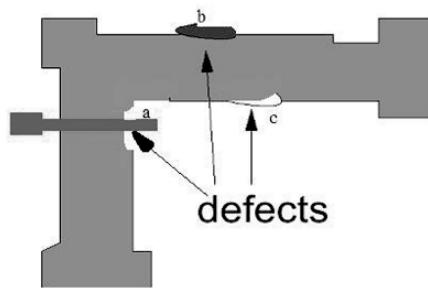

| 3.26 | Diffusion Mask Defects, Poly (Red) Superimposed<br>for Illustration         | 79 |

| 3.27 | Illustration of Steps Needed to Meet Design Intent                          | 80 |

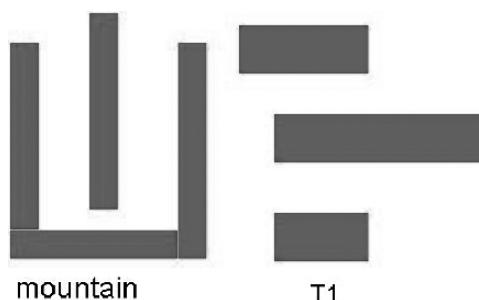

| 3.28 | Silicon vs Layout Simulation Flow                                           | 81 |

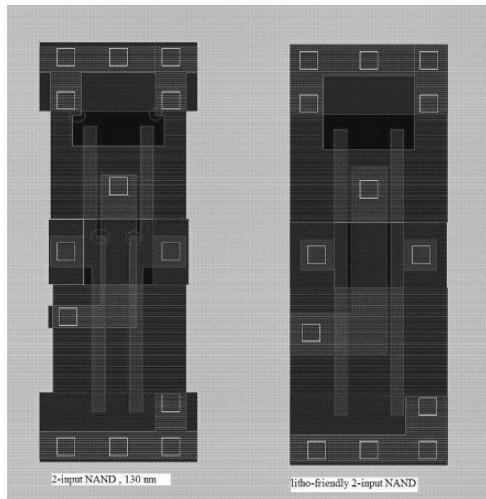

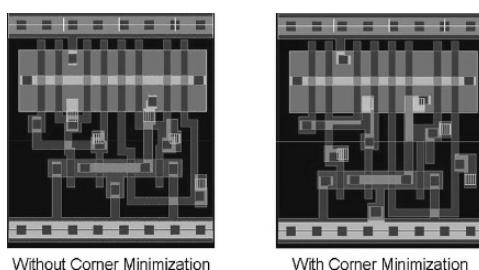

| 3.29 | Old Style “Compact” Layout vs Litho-friendly Cell Layout                    | 82 |

| 3.30 | Similar Layouts That Are Litho Hotspots                                     | 84 |

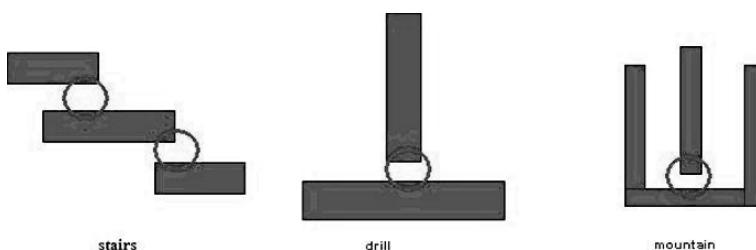

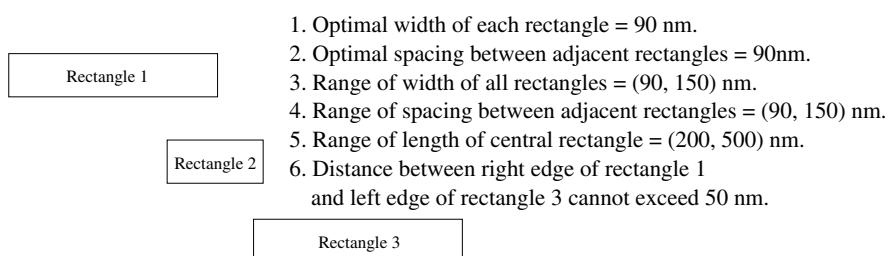

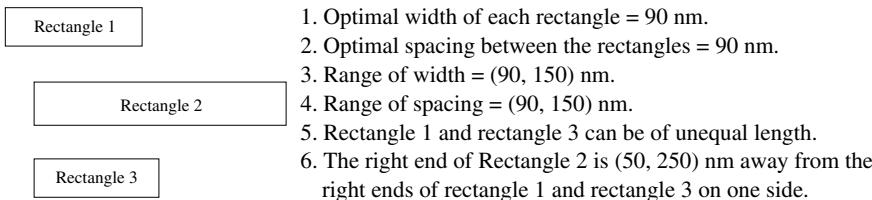

| 3.31 | Range Pattern Staircase                                                     | 85 |

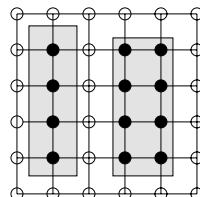

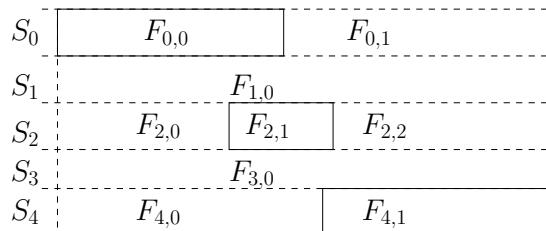

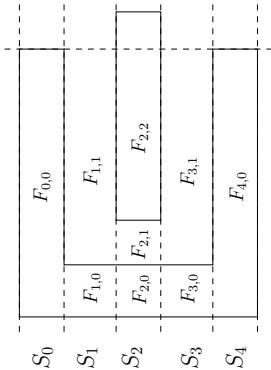

| 3.32 | Representation of Layout as Layout Matrix                                   | 86 |

| 3.33 | Cutting-slice of Range Pattern staircase                                    | 87 |

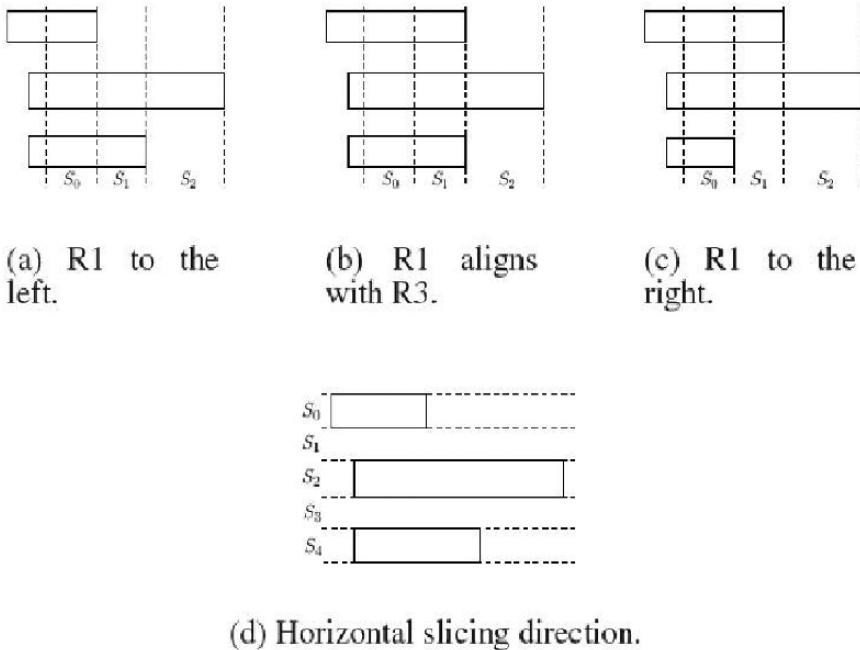

| 3.34 | Range Pattern “rocket”                                                      | 88 |

|      |                                                                                           |     |

|------|-------------------------------------------------------------------------------------------|-----|

| 3.35 | Horizontal and Vertical Cutting-slices of Range Pattern Rocket                            | 89  |

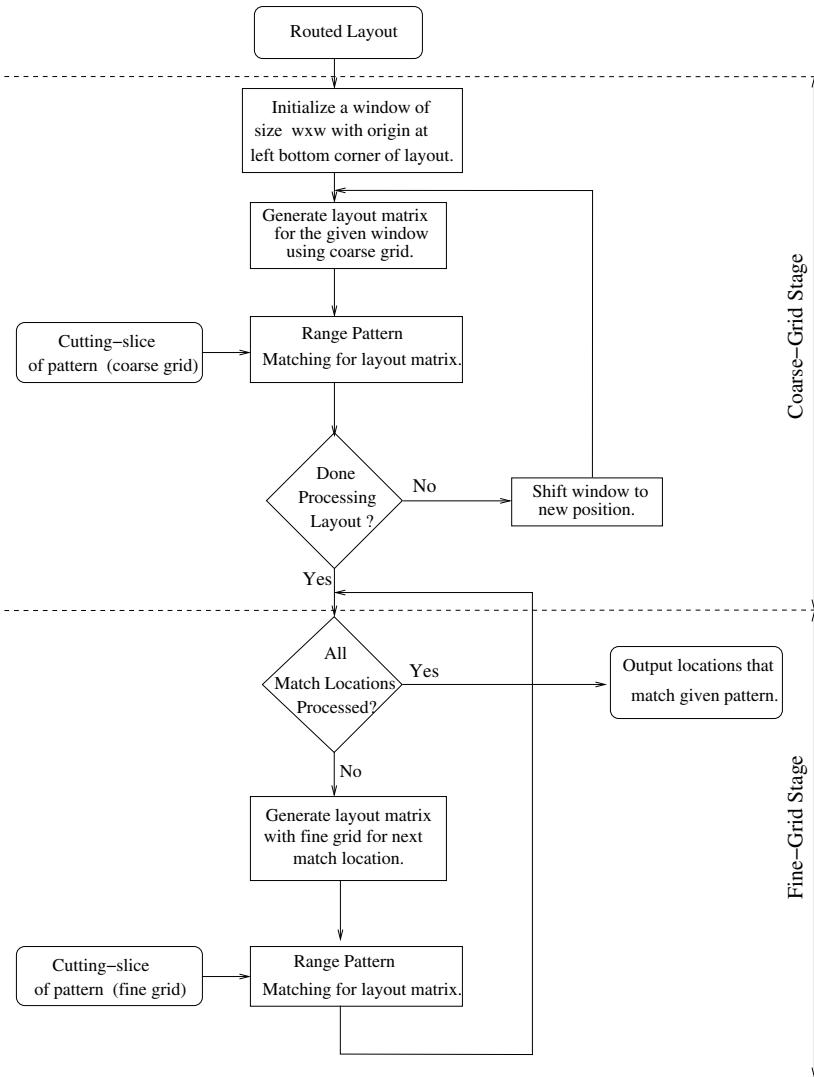

| 3.36 | Flowchart of the Hotspot Detection System                                                 | 90  |

| 3.37 | Cutting-slice of Range Pattern Mountain                                                   | 93  |

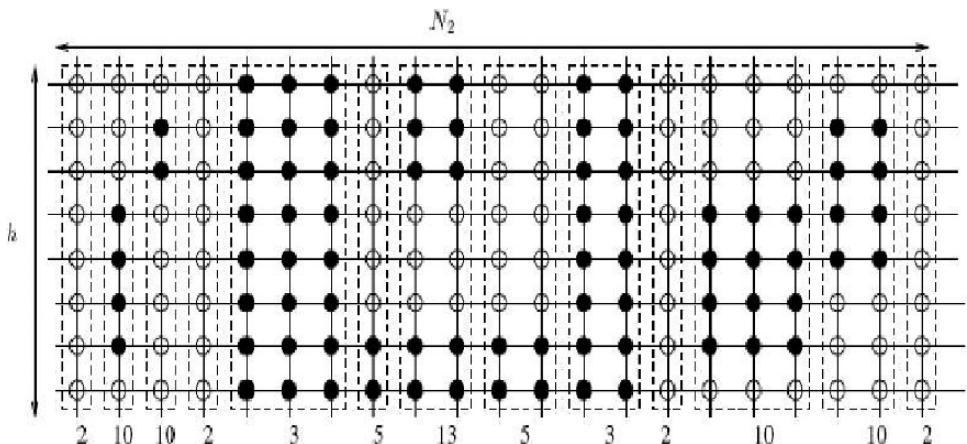

| 3.38 | Layout Block Encoding                                                                     | 93  |

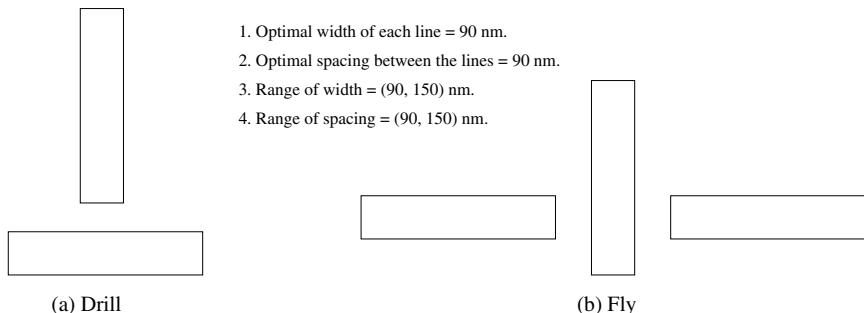

| 3.39 | Drill and Fly                                                                             | 95  |

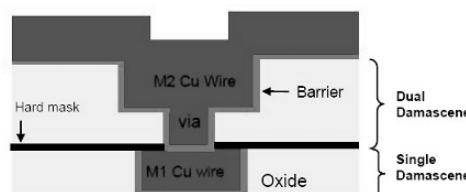

| 4.1  | Simplified Cross Section of a Single and a Dual Damascene Process                         | 100 |

| 4.2  | Lithography Steps of a Via-first Dual Damascene Process                                   | 101 |

| 4.3  | An Electroplating System [1]                                                              | 103 |

| 4.4  | Additive Absorption Behavior During ECP [2]                                               | 104 |

| 4.5  | A Typical Topography After ECP Process                                                    | 106 |

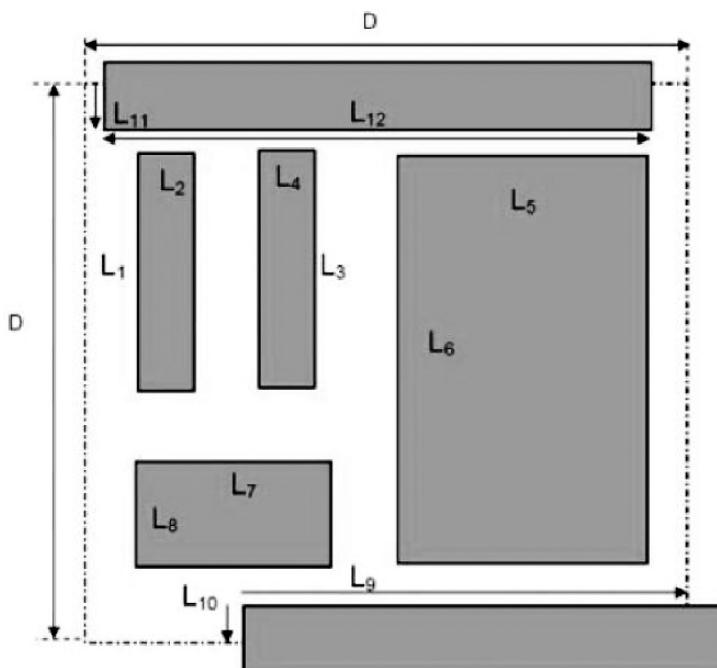

| 4.6  | An Arbitrary Layout in Window with Size DxD                                               | 107 |

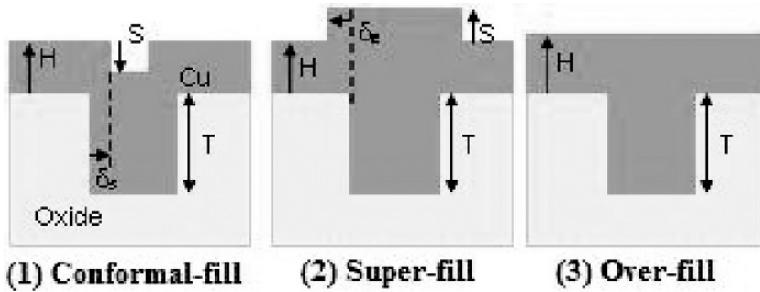

| 4.7  | Three Kinds of Post-ECP Topographies of a Wire                                            | 108 |

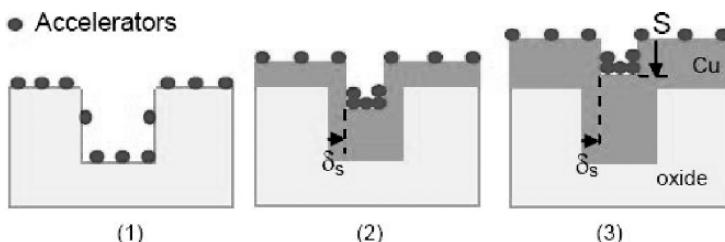

| 4.8  | The Evolution of Topography in Case (1) Conformal-fill                                    | 110 |

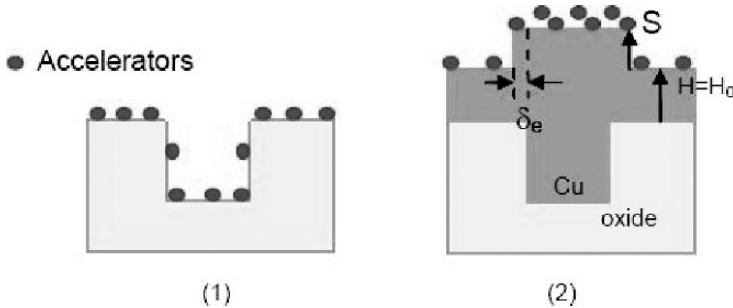

| 4.9  | The Evolution of Topography in Case (2) Super-fill                                        | 112 |

| 4.10 | Framework of The Full-chip ECP Topography Simulator                                       | 114 |

| 4.11 | Experimental Post-ECP Cu Topography from [1]                                              | 117 |

| 4.12 | Experimental vs Simulation Results for (a) $H$ and (b) $S$                                | 118 |

| 4.13 | Simulation of Surface Height and Absolute Step Height Under Different Interaction Lengths | 120 |

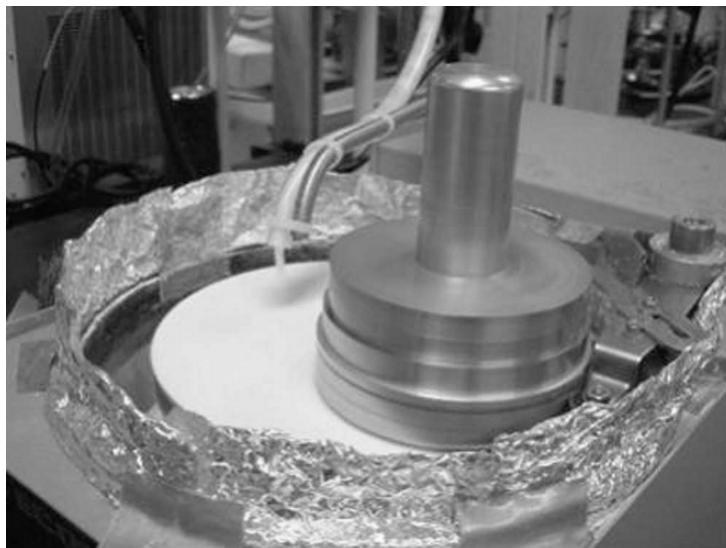

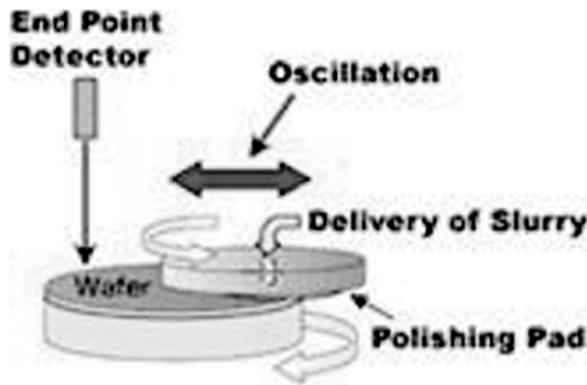

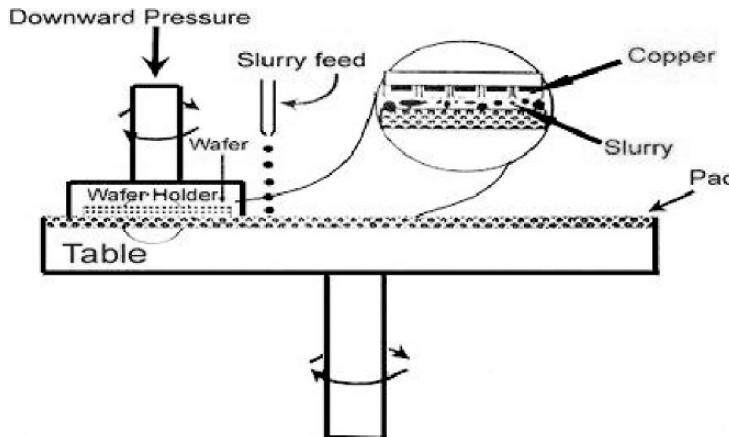

| 4.14 | Polish Table: A Picture of One Sector of A Polishing Table                                | 122 |

| 4.15 | A Break-down of the Details of A Polishing Station                                        | 123 |

| 4.16 | Schema: A Schematic Representation of A Polishing Station                                 | 123 |

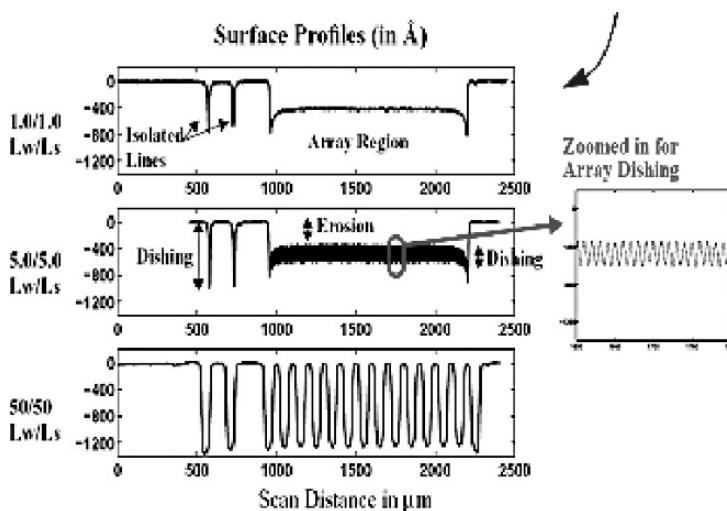

| 4.17 | Surface Topography Profiles for Pitch Structures                                          | 125 |

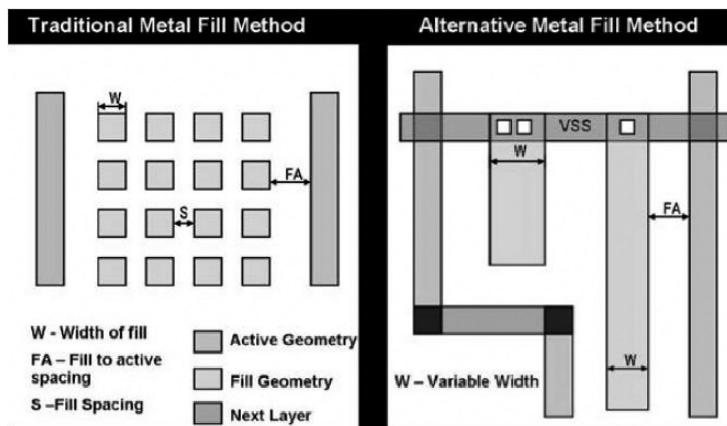

| 4.18 | Metal fill Illustrates the Rule Based (Traditional) vs Algorithmic (Alternative) Approach | 126 |

| 4.19 | Solutions of a Simple 1-D Problem                                                         | 132 |

| 4.20 | A Specific Case                                                                           | 133 |

| 4.21 | The Discretization Error of LP                                                            | 136 |

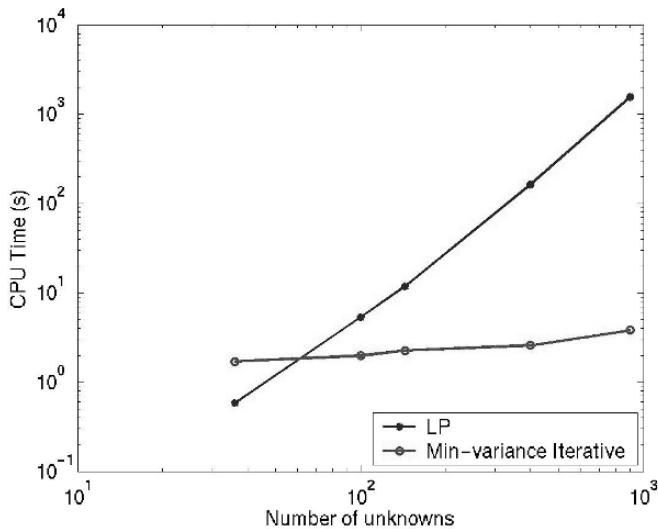

| 4.22 | The CPU Time Comparison                                                                   | 137 |

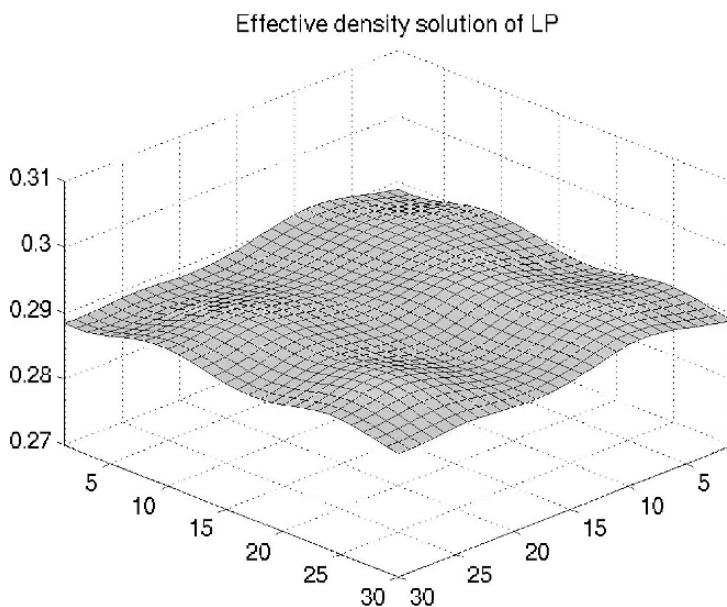

| 4.23 | The Effective Density of the LP Method                                                    | 137 |

| 4.24 | The Effective Density of the New Min-variance Iterative Method                            | 138 |

| 4.25 | Topography Results using CMP Simulator                                                    | 140 |

| 4.26 | Impact of ECP Thickness Range on Final Thickness Range                                    | 142 |

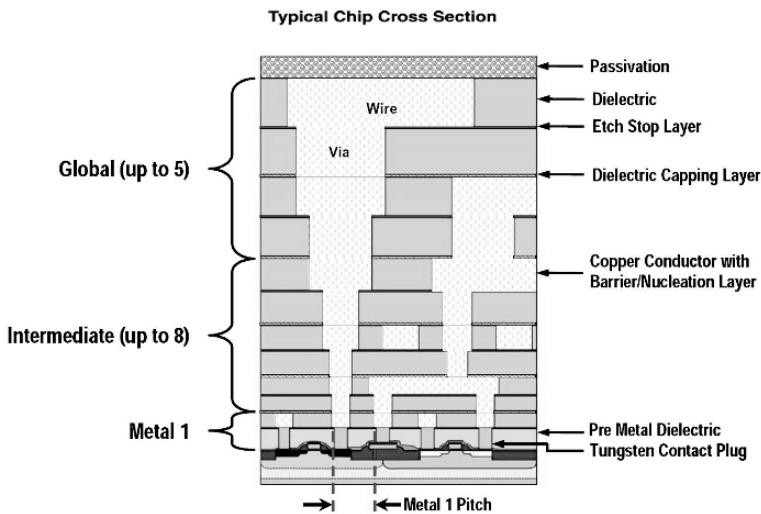

| 5.1  | Illustrative Cross Section of a CMOS IC with Metallization                                | 154 |

|      |                                                                                                                                 |     |

|------|---------------------------------------------------------------------------------------------------------------------------------|-----|

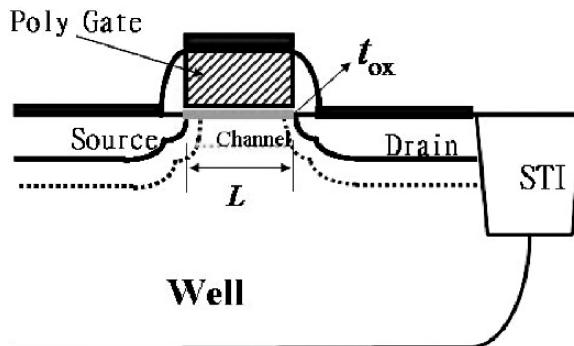

| 5.2  | Planar Cross Section of a CMOS Device Showing Main Physical Parameters                                                          | 154 |

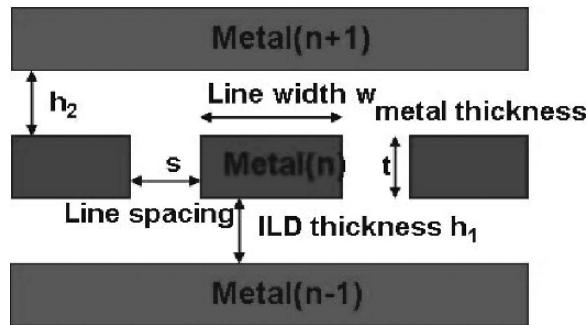

| 5.3  | Illustration of Interconnect Parameters for 2 Layers of Metal                                                                   | 155 |

| 5.4  | Example of Metal LER                                                                                                            | 155 |

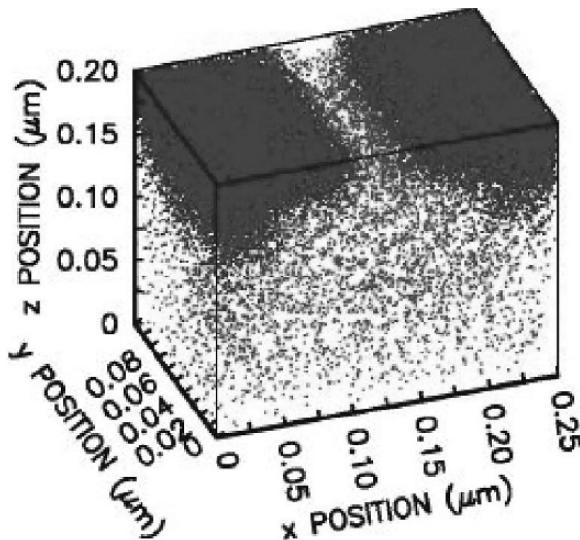

| 5.5  | LER for Device Gate                                                                                                             | 156 |

| 5.6  | Doping Fluctuations Are Pronounced at 45nm and Beyond                                                                           | 157 |

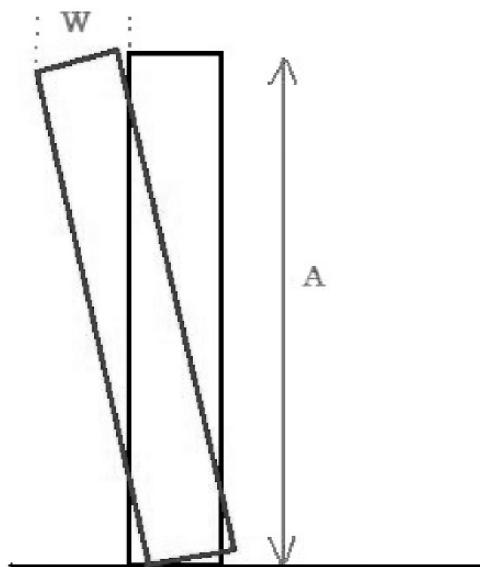

| 5.7  | A Scan and Step Lithography System Representation                                                                               | 158 |

| 5.8  | Die to Die Variability                                                                                                          | 159 |

| 5.9  | $I_{ds}$ within Die Variability                                                                                                 | 160 |

| 5.10 | $V_{th}$ within Die Variability                                                                                                 | 160 |

| 5.11 | Correlation Length                                                                                                              | 161 |

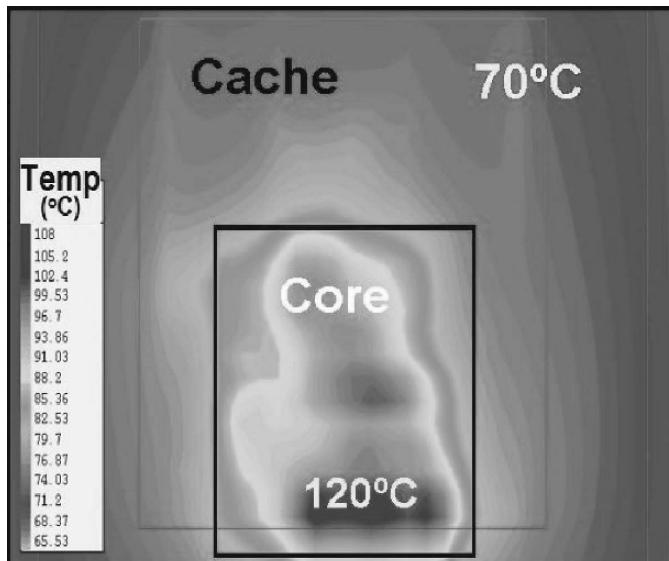

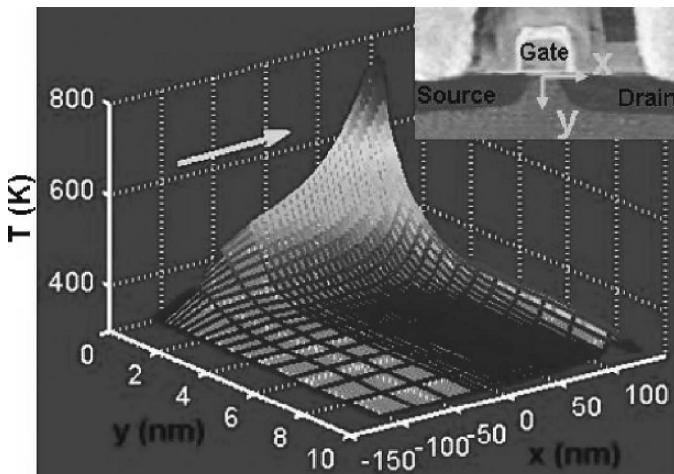

| 5.12 | A Temperature Distribution Map of a Typical Chip with a Core and Cache                                                          | 161 |

| 5.13 | Junction Temperature Distribution of a CMOS Device                                                                              | 162 |

| 5.14 | Interconnect Cross Section                                                                                                      | 163 |

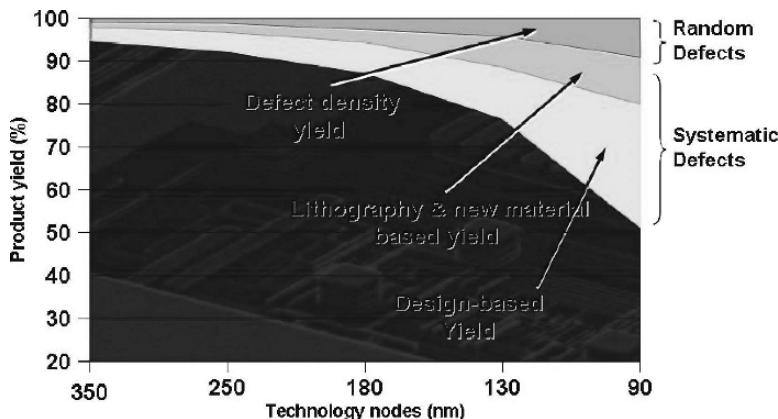

| 5.15 | Defect Categories Distribution Trend as a Function of Technology Node                                                           | 164 |

| 5.16 | A Comprehensive Chart of the Sources of Yield Loss                                                                              | 165 |

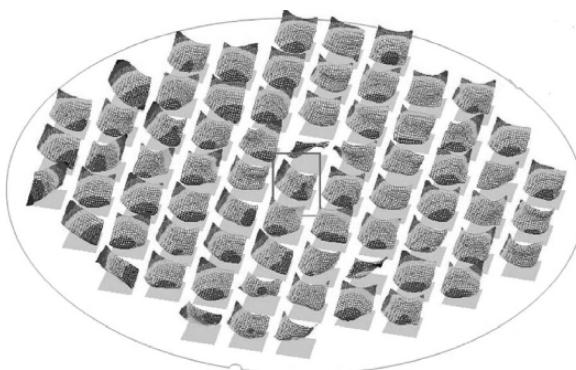

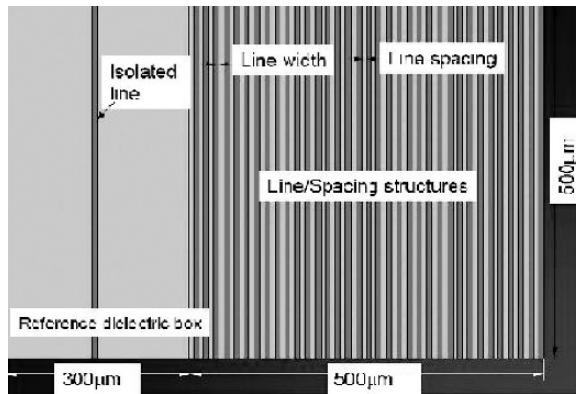

| 5.17 | A Well Designed Pattern for CMP Evaluation                                                                                      | 168 |

| 6.1  | Illustration of Gate Timing and Interconnect Timing                                                                             | 171 |

| 6.2  | Illustration of CPM Method for Path In->out                                                                                     | 172 |

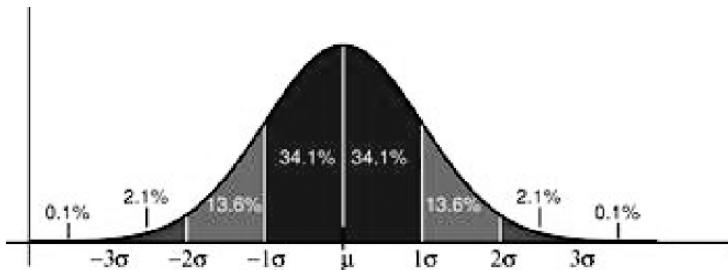

| 6.3  | Confidence Levels for $1\sigma$ , $2\sigma$ , and $3\sigma$ for a Normal Distribution                                           | 174 |

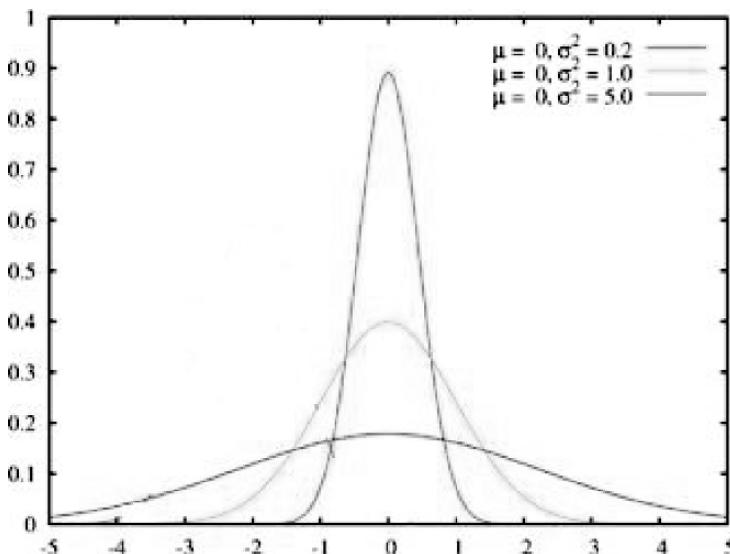

| 6.4  | Probability Density Function for a Normal Distribution Function of a Variable $x$ with $\mu = 0$ for Various Values of $\sigma$ | 174 |

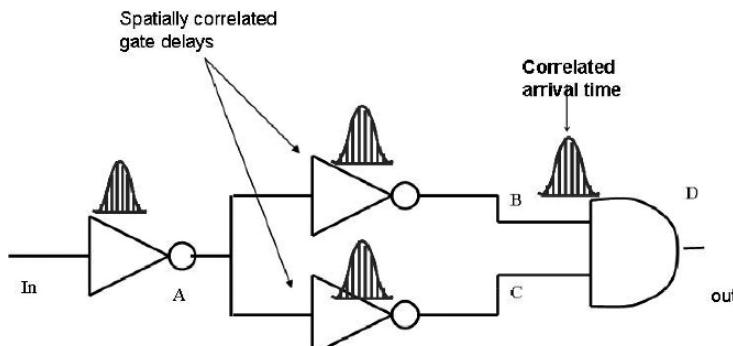

| 6.5  | Gate and Interconnect Delays Are Represented as PDFs in SSTA                                                                    | 177 |

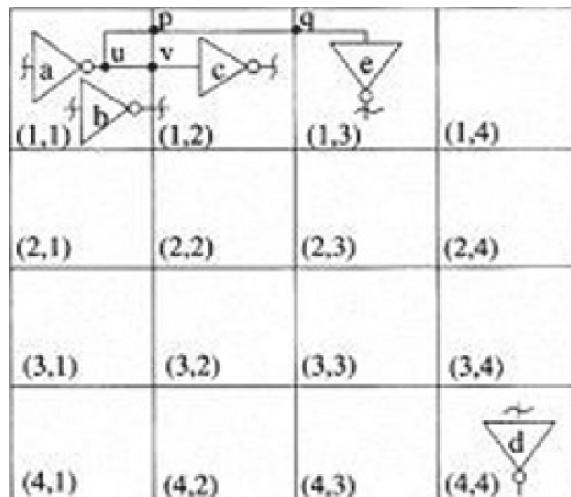

| 6.6  | Grid Model of Spatial Correlation                                                                                               | 179 |

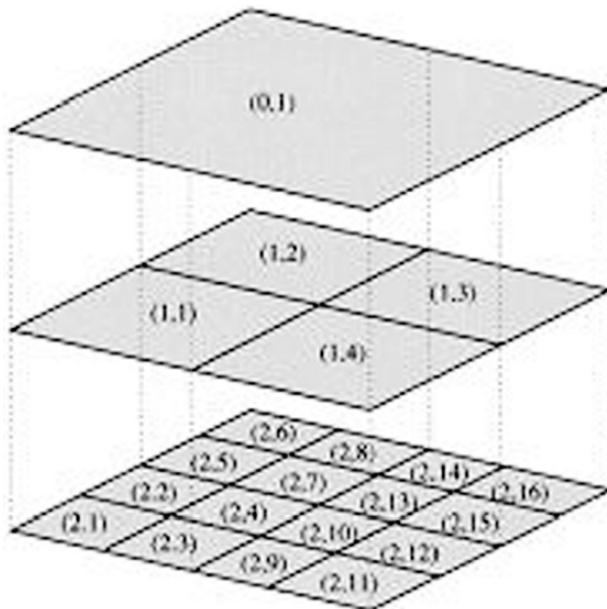

| 6.7  | The Quad-tree Model for Spatially Correlated Variations                                                                         | 180 |

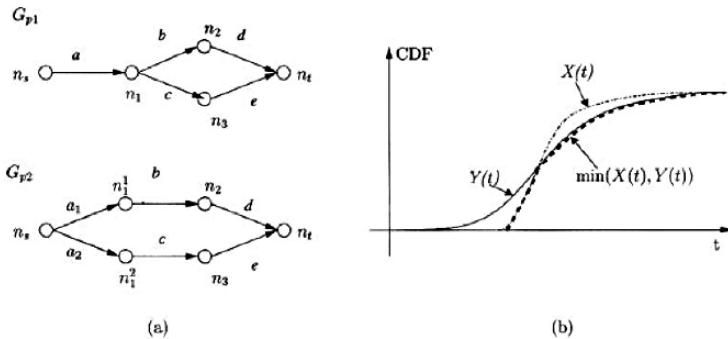

| 6.8  | Illustration of the Computation of (a) Upper and (b) Lower Bounds for the CDF $X(t)$ for Paths a-b-d and a-c-e [3, 4]           | 186 |

| 6.9  | Illustration of Upper and Lower Bound Functions                                                                                 | 186 |

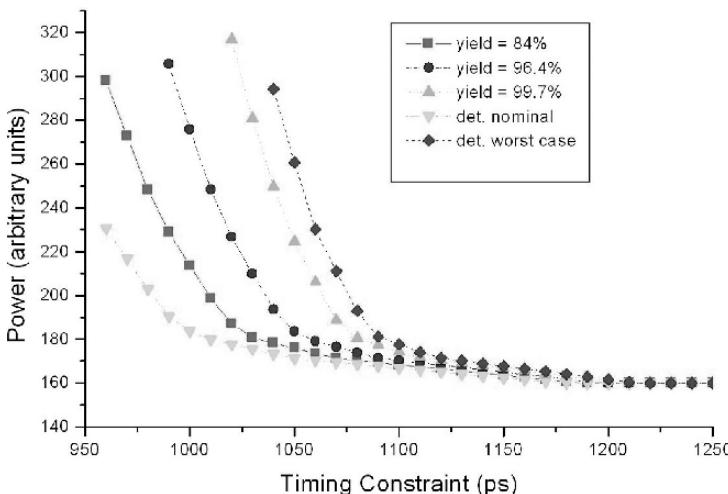

| 6.10 | Statistical Optimization Results for Static Power                                                                               | 187 |

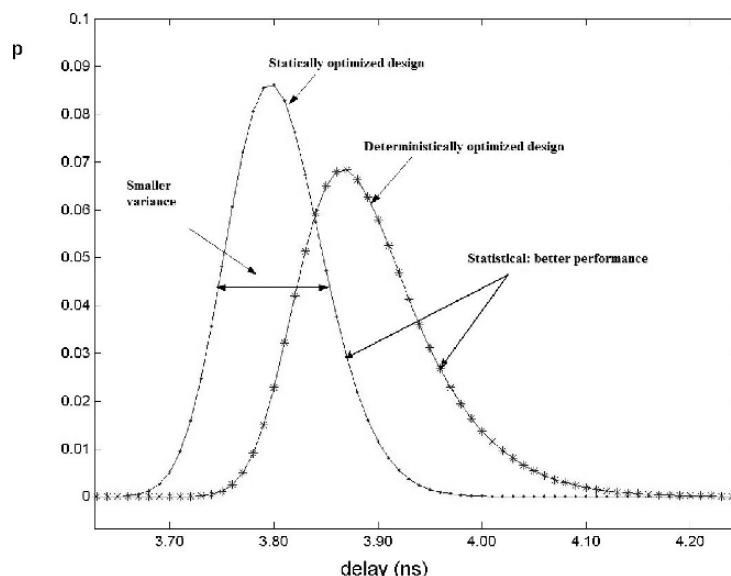

| 6.11 | Statistical Design Optimization Always Superior to Worst Case                                                                   | 188 |

| 6.12 | Block Diagram of Body-bias Implementation in [5]                                                                                | 189 |

| 6.13 | Basic Illustration of Body Bias for P and N Devices                                                                             | 190 |

|      |                                                                                       |     |

|------|---------------------------------------------------------------------------------------|-----|

| 6.14 | Block Diagram of a Combination of Adaptive Body Biasing and Adaptive Voltage Scaling  | 191 |

| 6.15 | Optimization of Speed and Power Using Both Adaptive Voltage Scaling and Body Bias [5] | 192 |

| 7.1  | Defect Categories Distribution Trend as a Function of Technology Node                 | 196 |

| 7.2  | A Simplified Design Flow for Illustration Purposes                                    | 198 |

| 7.3  | The Yield Prediction Flow in cdf Approach                                             | 201 |

| 7.4  | Derivation of the Transformation “T” for Hot-spot Yield Scores                        | 203 |

| 7.5  | Distribution of Yield Measuring Variable and Yield Score Function                     | 206 |

| 7.6  | Approximation of $f()$ and $f^{-1}()$                                                 | 207 |

| 7.7  | The Complete Flow for Deriving the Transformation “T”                                 | 208 |

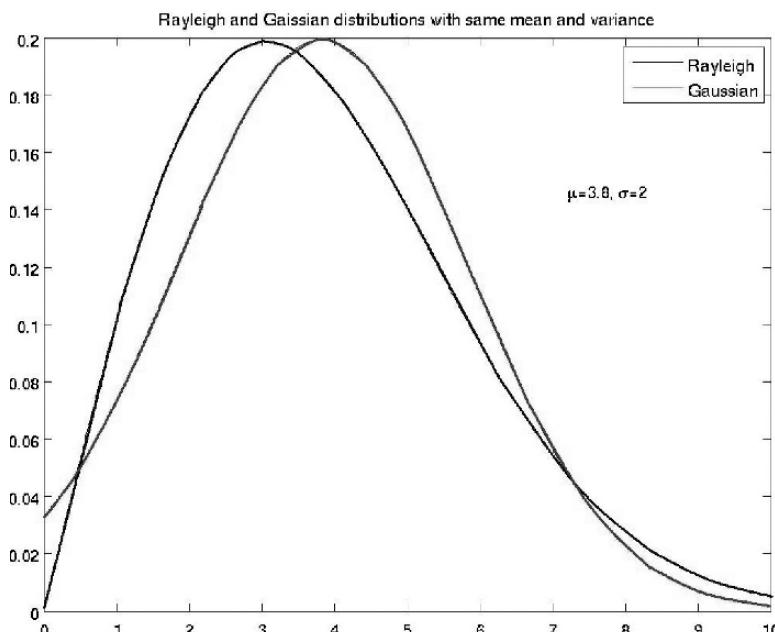

| 7.8  | Rayleigh and Gaussian Distributions with Same Mean and Variance                       | 209 |

| 7.9  | Typical Post-CMP Topography [6]                                                       | 215 |

| 7.10 | Yield Prediction for The Case of Perfect Across-chip Correlation                      | 217 |

| 7.11 | Spatial Correlations of Random Variation as Function of Distances                     | 218 |

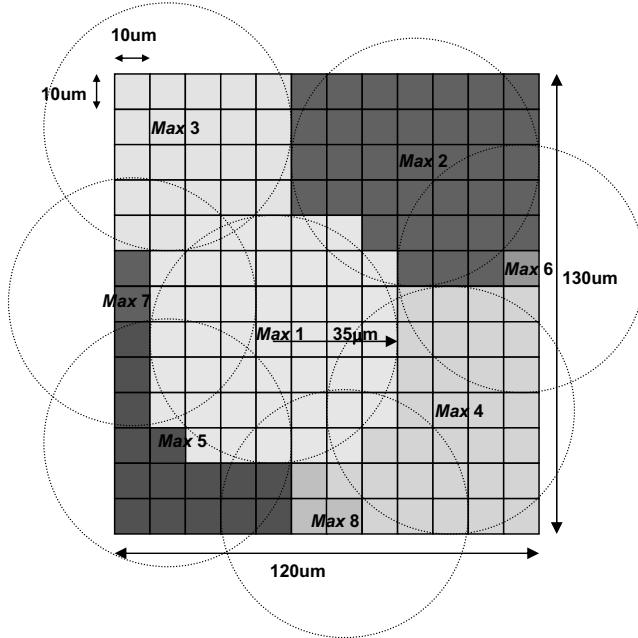

| 7.12 | Perfect Correlation Circles Surrounding Maximum Thickness Values                      | 220 |

| 7.13 | Flow Chart for $Y_{max}$ Calculation                                                  | 221 |

| 8.1  | A Top-down View of Manufacturability and Yield Derailing Factors                      | 228 |

| 8.2  | OPC Alternatives for a Digitized Geometry                                             | 229 |

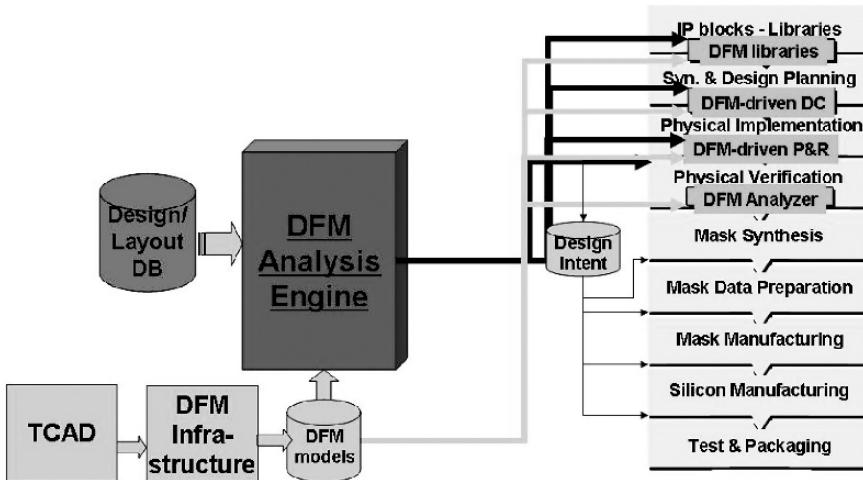

| 8.3  | An EDA DFM/DFY Centric Design Flow                                                    | 230 |

| 8.4  | An Example of a DFM Optimized Cell Form                                               | 231 |

| 8.5  | Table of Alternative Implementations of a Cell with Arcs                              | 232 |

| 8.6  | OPC Applicability Checking During Routing                                             | 233 |

| 8.7  | Wire Spreading                                                                        | 233 |

| 8.8  | Smart Metal Fill to Minimize Local ILD and Metal Thickness Variation                  | 234 |

| 8.9  | Illustration of Via Doubling                                                          | 234 |

| 8.10 | An Example of Prohibited Patterns                                                     | 235 |

| 8.11 | Data Fracturing                                                                       | 237 |

| 8.12 | Mask Inspection Flow                                                                  | 238 |

|      |                                                 |     |

|------|-------------------------------------------------|-----|

| 8.13 | Statistical vs Deterministic Design Delay Slack | 240 |

| 8.14 | Cross-bar Molecular Memory                      | 241 |

| 8.15 | Carbon Nano-tube Transistor [pfq]               | 241 |

| 8.16 | Nano-fluidic Valve [xyz]                        | 242 |

# List of Tables

|     |                                                                                     |     |

|-----|-------------------------------------------------------------------------------------|-----|

| 1.1 | Cost of Defect Repair at Every Stage of Production                                  | 2   |

| 1.2 | High K Oxide Materials and Their Dielectric Constants                               | 5   |

| 1.3 | Indicates the $k_1$ , NA Combinations vs Resolution                                 | 7   |

| 1.4 | Light Wavelength Versus the Technology Node                                         | 7   |

| 1.5 | Intra-die Variability Increase with Technology Node                                 | 15  |

| 1.6 | Mask Preparation File Data Size - ITRS 2004                                         | 15  |

| 2.1 | CA Results and Run Time in Shape Expansion Method and Our Method                    | 26  |

| 2.2 | Critical Area Optimization for Shorts                                               | 40  |

| 2.3 | Short, Open, and Total Weighted Critical Area Reductions Comparison, with $w = 0.1$ | 49  |

| 2.4 | Short, Open, and Total Weighted Critical Area Reductions Comparison, with $w = 10$  | 50  |

| 3.1 | Litho-Hotspot Detection Results                                                     | 96  |

| 4.1 | Peak-peak Value and the Standard Deviation of Effective Density                     | 132 |

| 4.2 | Peak-peak Value and the Standard Deviation of Effective Density                     | 138 |

| 4.3 | Comparison of Different Metal Filling Results                                       | 149 |

| 6.1 | Absolute and Relative Variability of $V_t$ for Successive Technology Nodes          | 173 |

| 7.1 | CD Variability Budget as a Function of Technology Node                              | 196 |

| 7.2 | A Possible CMP Hot Spot Specifications for 65nm                                     | 202 |

| 7.3 | CMP Hot Spot Scoring (Based on CMP Hotspot Specifications)                          | 204 |

|     |                                                                                                                    |     |

|-----|--------------------------------------------------------------------------------------------------------------------|-----|

| 7.4 | Litho Hot Spot and Score Specifications (Derived from a Foundry Specs)                                             | 205 |

| 7.5 | Simulation Results for the Case When True Distribution is Rayleigh ( $\sigma_1 = 2, \sigma_2 = 3$ )                | 210 |

| 7.6 | Simulation Results for the Case When True Distribution is Laplace ( $\sigma_1=2, \sigma_2=3; \mu_1=3, \mu_2=3.5$ ) | 210 |

| 7.7 | Yield Prediction under Different Radii of ‘Perfect Correlation Circles (PCC)’                                      | 224 |

| 7.8 | Yield Prediction for a Quicker Decrease of the Spatial Correlation                                                 | 225 |

# Preface

For any given industry striving to improve product quality, reliability, and yield on an ongoing basis is a fundamental task for the simple reason that higher product quality and reliability translates to higher sales, and higher yield translates to higher profitability. The electronic industry is no exception to that rule. In fact one of the driving considerations that transitioned the electronics industry from the era of discrete components to the era of the integrated circuit (IC) was the goal of achieving higher quality and reliability through less components to handle and assemble, and higher yields through smaller miniature devices. In this book we will focus on the technical aspects of manufacturability and yield as the industry moves well into the nano-era of integrated circuits.

Since the inception of the integrated circuits (IC) industry the manufacturing process has been based on optical lithography. The process of yield improvement focused on creating a cleaner processing environment (clean rooms) that reduced the number of particles in the manufacturing area which resulted in a lower number of random defects and thus higher yields, and on shrinking the design features that resulted in smaller die areas and thus more dies per wafer. Those two factors were on a collision course as smaller features meant that a smaller random particle could cause circuit defects that it did not cause when the geometries were more relaxed. Thus the requirement for cleaner fabrication facilities (clean rooms) and tighter process controls went hand in hand with shrinking geometric features.

Needless to say, along the IC progress path following Moore's law, solutions to challenges of high significance were required from all contributors to the manufacturing steps - from more accurate steppers, to lenses with larger numerical apertures, to illumination sources of light with shorter wavelengths, to mask writers (E-Beams) capable of parallel processing with tighter spot size and reasonable write time and throughput, to reticles with fewer defects, to new metal compounds capable of higher current densities, to more advanced etching materials and procedures, and to highly advanced metrology. And,

with every significant change there was a learning curve that resulted in a step back in yield until the particularities of each new step were fully understood and mastered, then yield was back on track and we moved forward. One such significant change was the use of Copper (Cu) instead of Aluminum (Al) or Al compounds; low K dielectrics was another such challenge, stacked vias with high aspect ratios, and the need for super planarization was also another significant challenge. Those four examples were by no means exclusive but were indeed major steps on the road to the nanometer era in IC manufacturing.

But, the IC optical manufacturing process found itself bumping its head against limitations rooted in physics that altered the learning curve process outlined in the last paragraph and called for a dramatically different approach not just to ensure yield improvement as we continue to shrink features, but to ensure that the manufacturability of smaller ICs is feasible in the first place. The IC industry was hitting barriers that threatened an end to the journey of optical lithography with an unpleasant outcome: zero yield; i.e. end of scalability. Moving from optical lithography to other means (atomic, molecular, self assembling structures, etc) meant a major discontinuity and a major disruption in the manufacturing and engineering techniques developed and mastered over the last fifty years at a staggering investment cost. Needless to say it is worth mentioning that re-training the design community in an alternative discipline of design cannot happen overnight either and will be very disruptive in nature should alternatives to the current manufacturing techniques emerge in short order. Simply put, the momentum of the optical lithography based IC industry is too strong to alter in such short order.

Optically, light source with a wavelength of 193 nano-meters (nm) was the end of the path in wavelength reduction with a big gap extending all the way to the 13nm extreme ultra-violet (EUV) light source. Efforts to develop 157nm and beyond came to a halt due to delays and to insurmountable technical challenges and we were faced with having to use 193nm light to print sub-90 nm features- features that are smaller than a half wave-length of the light source used. This called for a whole set of “engineering tricks” and techniques to extend the life of the 193nm based lithography. Also, on the materials front, “bulk” modeling of the behavior of dopant materials has quickly reached the end of its validity and quantum mechanical behavior of material needed to be taken into account. Unevenness in dopant distribution became very critical. Deterministic behavior had to be abandoned and replaced with statistical behavior and bulk properties had to be dealt with quantum mechanically. Single atomic layer gate oxides raised the need for high K gate dielectric with the challenge of making sure the electric field in the channel is not weakened. Fully salicided poly and metal gate options are considered to deal with this problem with a handful of new materials competing as candidates for the high k dielectric. The process of designing low K dielectric materials for intra-metal oxides

to reduce capacitance (improve speed) encountered big challenges in how to reduce K without increasing leakage. Not to be ignored is the complexity of the metallurgy and of other aspects of the manufacturing process. Via stacking and tighter metal pitches made planarization more critical than ever before; smart dummy fills that improved planarization without hurting the timing of a circuit became critical.

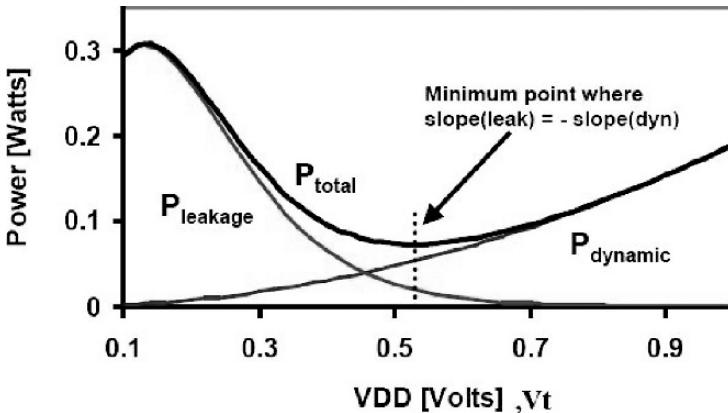

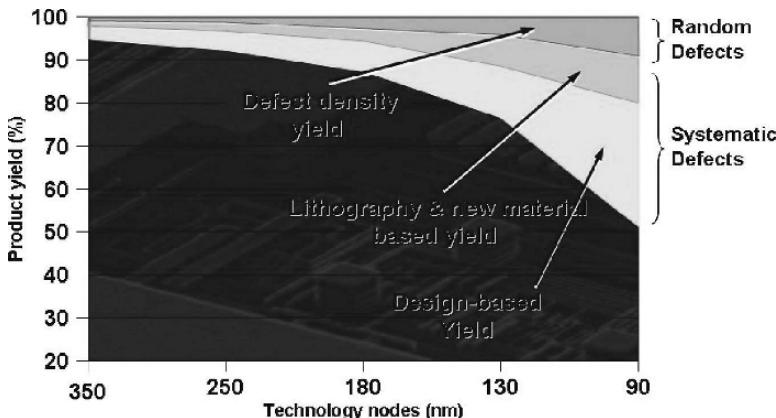

Thus designing for yield has changed to become designing for manufacturability and yield at the same time. The two go hand in hand - you cannot yield what you cannot manufacture. Also, faults impacting yield, which were dominated by particles (random defects) are not anymore the major mode of yield loss in ICs. Systematic variations impacting leakage, timing, and other manufacturing aspects in manufacturing are increasingly becoming the dominant factor; more so with every new technology node. Furthermore, the random component of variability which was strictly global in nature (die-die, wafer-wafer, lot-lot) has a new intra-die component of considerable significance.

In this book we start with a detailed definition of design for yield (DFY) and design for manufacturability (DFM) followed by a brief historical background of DFM/DFY where random (particle) defects were dominant and quickly move to the current challenges in manufacturability and yield and the solutions being devised to deal with those challenges for every step of a typical design flow. However, we do not present them in the order of steps in the typical design flow but in terms of categories that have logical and relational links.

In Chapter 1, after defining DFM/DFY and covering a brief historical perspective we go over why DFM/DFY has become so critical, we go through the classifications and categories of DFM and discuss what solutions are proposed for each problem and at what stage of the design flow, and through what tool(s) is such a problem addressed. We also start creating the logical link between DFM and DFY. Chapter 1 is a generic overview.

In Chapter 2 we cover a major random component of yield: critical area (CA), in depth. We discuss various algorithms used in critical area analysis (CAA) for extracting critical area of a design and evaluate them in terms of accuracy versus runtime. We cover techniques used in library design and in place and route that will improve the CA component of yield.

In Chapter 3 we move to define and explain the main systematic components of yield. We cover lithography in depth, explain the major problems associated with optical lithography, their root causes, and what remedies can be applied to solve them. We go over many examples of resolution enhancement techniques (RET) as it applies to the characteristics of light that we can manipulate in an effort to reduce the " $k_1$ " factor of the lithography system namely direction, amplitude, and phase. We discuss and analyze lithography aspects such as forbidden pitches, non-manufacturable patterns, etc. We discuss at length mask alternative styles, what problem is each alternative used to solve, their pros and

cons both technical and economical. We discuss mask preparation, generation, inspection, and repair. Lenses, filters, and illumination technologies are examined. Then we go over a practical design flow and examine what can be done at the routing stage after the major RET techniques are applied to the layout at the cell library design stage. We discuss lithography aware routing techniques. We also address various aspects of lithography rules checking and how it forms the link between classical design rule check (DRC) and manufacturability.

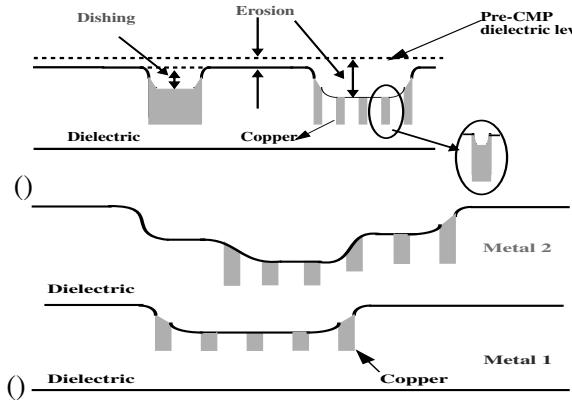

In Chapter 4 we cover the important planarization procedure of chemical mechanical polishing (CMP). We describe the process, identify the critical parameters that define it and the impact of each parameter on the overall planarization procedure. We cover Cu metallurgy, Cu deposition and etching and the following CMP steps, and address problems such as dishing and how they are related to the CMP parameters and to the neighboring metal patterns. We address the effects of the CMP variables and of the metal patterns on thickness variation in intra-metal insulating layers (ILD) and how that variation in turn affects manufacturability and yield. We cover the effect of metal patterns and local metal densities on ILD variation and get to the concept of metal “dummy fills”. We discuss and analyze rule based versus model based “dummy fills”. Finally, we address the ILD thickness variation on timing. Impacting parameters including resistance (R) and capacitance (C); and discuss how model based “smart fills” minimizes R and C variability, simultaneously.

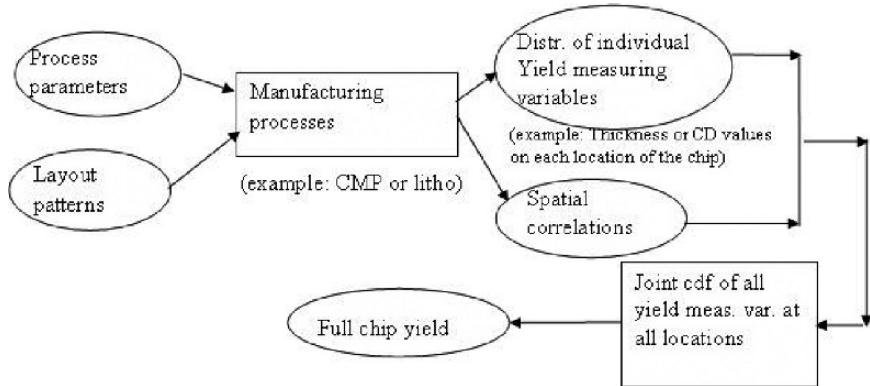

In Chapter 5 we include a comprehensive coverage of variability and of variability’s impact on parametric yield. We discuss the growing significance of parametric yield in the overall yield picture. We discuss intra-die variability vs. inter-die variability. We cover the critical process parameters that have the most significant impact on parametric yield, discuss the sources of variability for those parameters, and the impact of the variability in each parameter on parametric yield. We touch on techniques for reducing parametric variability towards improving parametric yield. Coverage of parametric yield in this chapter is restricted mainly to the variability components of major parameters.

Chapter 6 integrates the knowledge acquired in the previous chapters towards the concept of design for yield. It stresses techniques to avoid manufacturability bottlenecks and addresses analysis tools and methodologies for both manufacturability and yield optimization. It introduces and covers statistical timing analysis and statistical design as more productive and mature alternatives to the classical case-file design methodologies.

Chapter 7 sums up the contribution of the components of yield- random and systematic, towards the goals of yield modeling and yield prediction. We introduce several comprehensive yield models that a designer can use towards evaluating the overall yield of a design as well as towards enabling the designer to do a sensitivity analysis in order to evaluate the impact of key parameters under certain design topologies on yield. Such sensitivity analysis can go a

long way towards enhancing yield by avoiding patterns and topologies that have adverse impact on yield.

Finally, Chapter 8 is a review and summation of all the concepts of DFM & DFY introduced in this book. It enables the DFM/DFY student or practicing engineer to regroup in few pages the most important concepts one should keep in mind when designing for manufacturability and yield.

CHARLES C. CHIANG AND JAMIL KAWA

## **Acknowledgments**

Dr. Qing Su, Dr. Subarna Sinha, Dr. Jianfeng Luo, and Dr. Xin Wang of Synopsys, Inc., Mr. Yi Wang and Prof. Xuan Zeng from Fudan University, Shanghai, for their contribution to the materials presented in this book and Dr. Subarna Sinha, Dr. Qing Su, and Dr. Min-Chun Tsai of Synopsys, Inc, Huang-Yu Chen, Tai-Chen Chen, Szu-Jui Chou, Guang-Wan Liao, Chung-Wei Lin, and Professor Yao-Wen Chang of Taiwan University, Taipei, for their careful review of the manuscript and their valuable comments

# Chapter 1

## INTRODUCTION

### 1.1 What is DFM/DFY? Historical Prospective

Design for manufacturability (DFM) in its broad definition stands for the methodology of ensuring that a product can be manufactured repeatedly, consistently, reliably, and cost effectively by taking all the measures needed for that goal starting at the concept stage of a design and implementing these measures throughout the design, manufacturing, and assembly processes. It is a solid awareness that a product's quality and yield start at the design stage and are not simply a manufacturing responsibility. There are two motivations behind caring for DFM. Both motivations are rooted in maximizing the profit of any given project; the first is minimizing the cost of the final product of the project, and the second is minimizing the potential for loss associated with any defective parts that need to be replaced. In fact a study [7] estimates the cost of fixing a defective part at anywhere from 10 times to 10,000 times the initial cost of the part depending on the stage of the product cycle where the part is recalled (Table 1.1). Arguably, the numbers in Table 1.1 vary widely from product to product, and from industry to industry, but the trend in the scale of replacement cost is clear. You simply want to discover and eliminate any potential problem as close to the beginning of the product cycle as possible, preferably right at the design simulation and analysis stage.

The concept of DFM has been around for quite some time and has until recently stood by itself separate from “yield models” which were dedicated mainly to calculating yield as a function of defect densities. The concept of design for yield (DFY) is on the other hand a relatively new concept that stemmed from the fact that in the nano era of CMOS it is not sufficient to obey design rules, e.g., DFM rules, as the resulting yield could still be prohibitively low and therefore a new set of design procedures (model based) need to be applied to a design beyond manufacutability rules to ensure decent yield [8].

Table 1.1. Cost of Defect Repair at Every Stage of Production

| Level of Completion       | Cost to find and repair defect |

|---------------------------|--------------------------------|

| Part itself               | 1X                             |

| At sub-assembly           | 10X                            |

| At final assembly         | 100X                           |

| At the dealer/distributor | 1,000X                         |

| At the customer           | 10,000X                        |

Also, in this book we will focus on the DFM for the semiconductor IC industry but we would like to mention outright that all the historical classical concepts of DFM such as component simplification, standardization, minimization of the number of modules to be assembled, avoiding tight tolerances, and design robustness still apply in one form or another to the IC industry although DFM (and DFY) in the IC industry has many particularities that are new and that are unique to it.

Some early works in DFM and DFY for the IC industry tried to differentiate between DFM & DFY along the lines that anything rule based is DFM and anything model based is DFY. We believe the concepts of DFM and DFY have converged and that it does not make any sense to try to draw any distinction. Therefore we will use DFM to mean DFM/DFY.

As we mentioned earlier DFM and DFY have always been tied together, in fact most of the time whenever DFM was discussed, both DFM and DFY were implied. Yet we recently encounter a special stress in the IC industry on the concept of DFY and that is really an effort to emphasize the added concept that yield is no longer a manufacturing issue but a collectively shared issue between all participants of a production process. It is a statement that the design and implementation teams hold as much, if not more, responsibility for yield than does the manufacturing team. In 2004 a study estimated the total financial loss due to yield in the IC industry at \$30 Billion dollars per year. That is why DFM/DFY is currently the most active area of research in the EDA industry.

## 1.2 Why is DFM/DFY Becoming Ever so Critical for IC Manufacturing?

Rarely have so many variables (factors) of a particular design and manufacturing process undergone significant fundamental changes simultaneously such as what we are witnessing today in the nanometer era of the IC industry. Further complicating matters in the emergence of structurally novel new devices (double gate devices, triple gate devices, and FinFETs) and the proliferation of dedicated sub-processes at every technology node directed toward meeting the needs of specific applications. Needless to say, the increase in the number of new variables introduced into the mix of any process renders the probability of

error due to a fault in any of those variables higher, and thus the need for a meticulous accountability of the impact of each variable on the overall process flow. In this section we will give a brief introduction to a plurality of those variables. A more detailed coverage of each variable is left for the body of the book.

## 1.2.1 New Materials

A quick count of the number of elements of the periodic table used in the IC industry from its inception until the onset of the nano era of CMOS and that used or being experimented with as a potential solution to one of the problems the industry is facing is very revealing. It is not an increase of ten or fifteen percent but rather a multiple of greater than four. In this section we will focus on the materials being used for metallurgy, for low K dielectric, high K dielectric, and engineered mechanical strain materials.

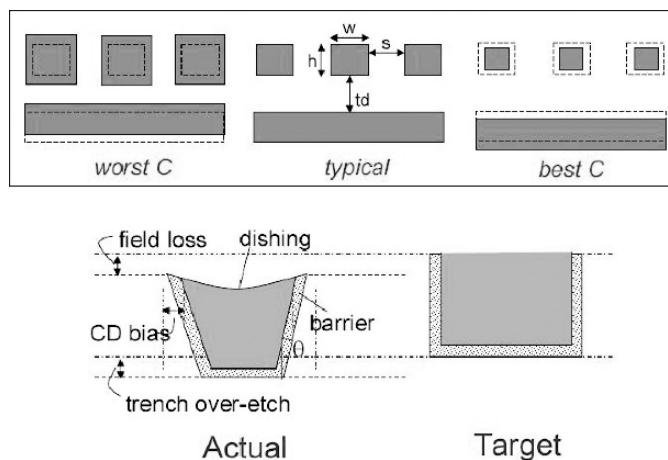

### 1.2.1.1 Copper

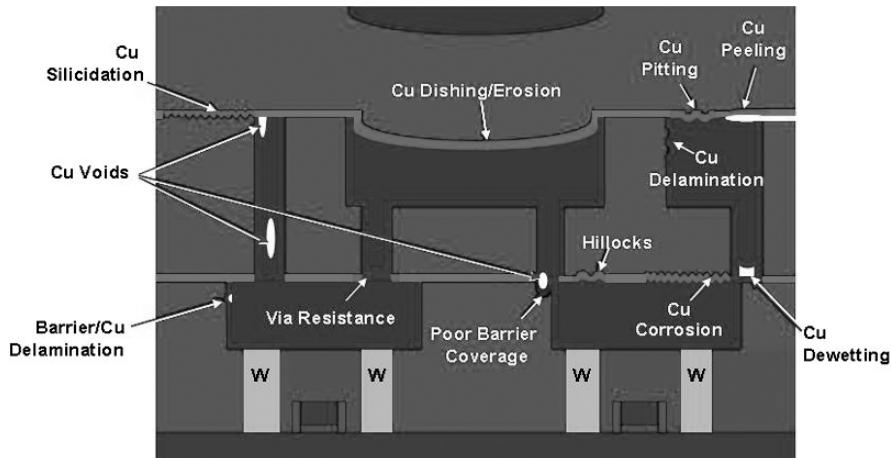

The switch from Aluminum (Al) and aluminum alloys to Copper (Cu) was a major and fundamental change. Aluminum metallurgy involved the deposition of aluminum (or aluminum alloy) all over the wafer and then the selective etch of that aluminum except for the traces forming the metal routes as defined by metal masks. The move to copper was needed as the wires were getting narrower and aluminum alloys could no longer deliver the current carrying capabilities needed by the circuitry. Copper had a higher current carrying capability, but, it couldn't be spun and etched the way aluminum could. Copper deposition is an electroplating procedure that will be described at length when chemical mechanical polishing (CMP) is discussed in Chapter 4. Metal migration (including open vias) was the main problem with Al but no other major problem was there. Figure 1.1 shows a typical cross section of a copper metallurgy for one layer and the slew of problems associated with it from dishing to field oxide loss, to erosion. Also, given that a typical CMOS process of 90 nm or beyond has no less than 8 metal layers, planarization of the layers becomes a must. CMP is used for that, and CMP issues are not trivial. Again it will be discussed at length in Chapter 4.

### 1.2.1.2 Low K and High K Dielectrics

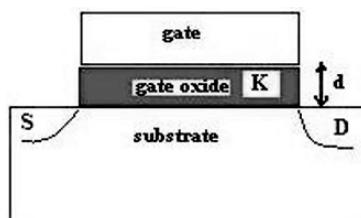

Gate oxide scaling has resulted in gate oxide thickness reaching the limit of a few mono-atomic layers that is very hard to control. The only way to use thicker gate oxide and still maintain the proper gate coupling capacitance is to resort to higher dielectric (K) materials. Figure 1.2 shows a simple basic gate structure.

$$C_{ox} = K \times A/d \quad (1.1)$$

Figure 1.1. Cu Cross Section Showing Potential Problems

where  $C_{ox}$  is the gate capacitance, A is the cross sectional area and d is the oxide thickness.

An increase in the value of K allows for an unchanged  $C_{ox}$  with a larger value of d. The issue is not as simple as that, as other aspects such as poly field degradation, etc. calls for additional measures such as the use of metal gates with their own set of work function matching between the metal gate and polysilicon related problems. Nonetheless the dominant trend is for higher K dielectrics for gate oxide. Use of plasma nitrided dielectrics and high K dielectrics is growing. Table 1.2 lists few of the options being considered for high K oxides to achieve a variety of dielectric characteristics.

The exact opposite trend applies to inter-metal oxide layers (ILD). There, a lower K is desired to lower the capacitance of the underlying interconnect since with the increasing gate count of a typical design and shrinking device dimensions and supply voltages renders the interconnect delays as the dominant component of delay in most given critical paths; thus a reduction of C through a reduction of K is desirable. However, lower K means more porous material, and

Figure 1.2. Basic Gate Illustration

Table 1.2. High K Oxide Materials and Their Dielectric Constants

|                   |         |

|-------------------|---------|

| $SiO_2$           | 3.9     |

| $Si_3N_4 / SiO_2$ | 5       |

| $Si_3N_4$         | 7       |

| $Al_2O_3$         | 10      |

| $HfSi_2Oy_3$      | 10-15   |

| $HfO_2$           | 15-30   |

| $TiO_2$           | 30-90   |

| $BaSrTiO_3$       | 100-300 |

higher leakage. So, coming up with the proper materials with the appropriate desirable characteristics is not a trivial matter.

### 1.2.1.3 SiN and SiGe Layers for Induced Strained Silicon Engineering

One of the emerging techniques for selectively enhancing the mobility of p-carriers or n-carriers involves intentionally creating mechanical stress in the channel caused by the mismatch in the lattice structure at the interface between the native silicon and the induced material - namely SiN, SiC, or SiGe. There are compressive strain techniques and tensile techniques depending on which device we intend to enhance. Mobility of p-type or n-type carriers has been reported to be enhanced by as much as 50% due to mechanical stress. A recessed SiGe source and drain is used to enhance p-type performance through compressive stress while a SiC channel is an example of tensile stress used to enhance n-type performance. Two things are worth noting here: first, when a stress enhancement technique is used to enhance devices of one carrier type, it results in deterioration (though smaller in magnitude than the enhancement) in the opposite type carrier; second, the extent of enhancement or degradation of a certain carrier type due to stress engineering is very dependent on lattice orientation (Miller indexes) which determine the unstressed mobility characteristics of that carrier in the first place. This has implications on the permitted direction of gates orientation in physical layout which used to be a free variable.

### 1.2.1.4 Miscellaneous

We could go on and talk about photoresist materials being considered to control line edge roughness, a significant contributor to leakage, and materials being used for high-resolution and for phase manipulated masks, and the list goes on. The common theme is that there is an explosion in the materials and elements being used as we continue to shrink CMOS technology. We stressed the ones above due to their higher significance and relevance to the design cycle and to DFM/DFY.

## 1.2.2 Sub-wavelength Lithography

Sub-wavelength lithography will be covered in depth in Chapter 3, so our coverage of this issue here will be brief and will focus mainly on the chronological turning points in lithography and their impact on yield and manufacturability.

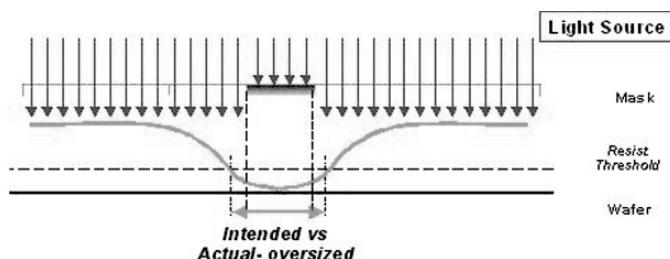

### 1.2.2.1 Some Basic Equations

Let us start by citing four characteristics of light that will guide our work in lithography related matters through the book. Light has wave properties namely wavelength, direction, amplitude, and phase. All lithography manipulation schemes revolve around manipulating one of those four characteristics. But, before addressing any issues impacting lithography it is useful to review some basic optical fundamentals. One such basic fundamental is that photoresist reacts to a threshold of light intensity (energy) and not to the wave shape nor its phase. We will need this fact later when we explain resolution enhancement through the use of phase-shift and others technologies. The other two fundamentals we would like to address briefly here are the two equations that describe the relation between resolution and depth of focus, the parameters of light wavelength, and the lens numerical aperture.

First is Rayleigh's equation for resolution

$$R = k_1 \times \lambda/NA \quad (1.2)$$

where  $R$  = resolution = minimum feature,  $k_1$  = resolution constant,  $\lambda$  = wavelength of the light source,  $NA$  = numerical aperture which is a function of the lens and of the refraction index of the medium between the wafer and the lens of the contact aligner.

Depth of Focus (DOF):

$$DOF = k_2 \times \lambda/NA^2 \quad (1.3)$$

where  $DOF$  is defined as the range of items in focus in an image and  $\lambda$  = wavelength of the light source.

At this point we want to bring into attention few implications of the above two equations. The necessity of using the 193nm light source for the 45nm technology node implies an effort to increase NA and to reduce  $k_1$ . While resolution improves with higher NA, DOF suffers at a squared rate of the increase in NA. The other point is that as  $k_1$  is reduced to very low values (0.25) to meet the need of 45nm the proximity interaction effects of neighboring geometries increases complicating things further (we will not cover here the factors impacting  $k_1$ ).

Table 1.3 before indicates the typical combination of NA and  $k_1$  needed to meet technology requirements for 193 nm light source.

Table 1.3. Indicates the  $k_1$ , NA Combinations vs Resolution

| Light source $\lambda$ | NA  | $k_1$ | Resolution |

|------------------------|-----|-------|------------|

| 193nm                  | 0.6 | 0.4   | 130nm      |

| 193nm                  | .75 | .35   | 90nm       |

| 193nm                  | .85 | .4    | 90nm       |

| 193nm                  | 1   | .34   | 65nm       |

| 193nm                  | 1.1 | .37   | 65nm       |

| 193nm                  | 1.1 | .25   | 45nm       |

| 193nm                  | 1.2 | .27   | 45nm       |

| 193nm                  | 1.3 | .3    | 45nm       |

Again, this topic will be covered at length in Chapter 3, but it is important to note that as  $k_1$  values drop below .4 heavy use of resolution enhancement techniques (RET) are needed to achieve any acceptable printability.

### 1.2.2.2 Light Sources

Table 1.4 shows the wavelength of the light source used versus the technology node processed using that source light. We obviously skipped many technology nodes but the point we wanted to stress here is that past the 130nm technology node the critical dimension (CD) of the featured technology is significantly less than half of the wavelength ( $\lambda$ ) of the light source used in the lithography.

It is also significant to mention that efforts to develop a 157 nm illumination source has been all but abandoned in 2005 due to vast technical difficulties associated with the mask and photoresist technologies needed to go along with that light source. There is practically no serious candidate for a lithography light source beyond the ArF (Argon Fluoride) 193nm light source until the extreme ultra violet (EUV) light source with a wavelength of 13 nm. A lot of progress in the development of the EUV illumination source has been reported in the last several years with two “alpha” EUV systems installed in the year 2006 but any serious deployment of that source for full production is still many years away at best estimate.

### 1.2.2.3 Lens Technology

As Rayleigh’s equation (Equation 1.2) indicates a higher NA leads to an improved resolution limit. One of the techniques successfully used to improve the NA of the lens projection medium has been immersion technology where a drop of fluid is introduced between the lens and the exposed wafer. The change in the index of refraction in which the light source travels translates in this

Table 1.4. Light Wavelength Versus the Technology Node

| Light source $\lambda$ | 436nm   | 365nm | 248nm | 193nm | 193nm |

|------------------------|---------|-------|-------|-------|-------|

| Technology node        | 3,000nm | 600nm | 130nm | 90nm  | 65nm  |

case to a shorter equivalent wavelength, thus improved resolution. The other technique is simply a direct improvement in the NA of the lens itself, however, this is capped at a theoretical limit of one and a practical limit around 0.8.

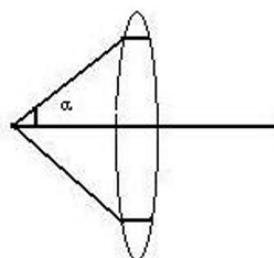

The NA of a lens is given by

$$NA = I \sin(\alpha) \quad (1.4)$$

Where  $I$  is the index of refraction of the media in which the lens is working. For air  $I$  is 1 putting a theoretical upper limit of 1 on the NA of a lens in air. Figure 1.3 is for the illustration of Equation 1.4.

With immersion technology where the medium is altered to water or oil, the index of refraction of some oils are as high as 1.5 allowing for an effective numerical aperture greater than one compared to the typical 0.6 ( $\alpha = 32^\circ$ ) to 0.8 ( $\alpha = 48^\circ$ ) range attainable through lens in air.

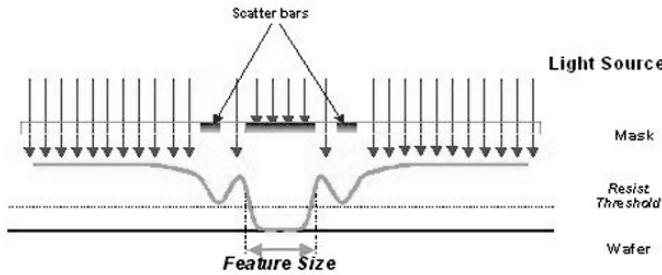

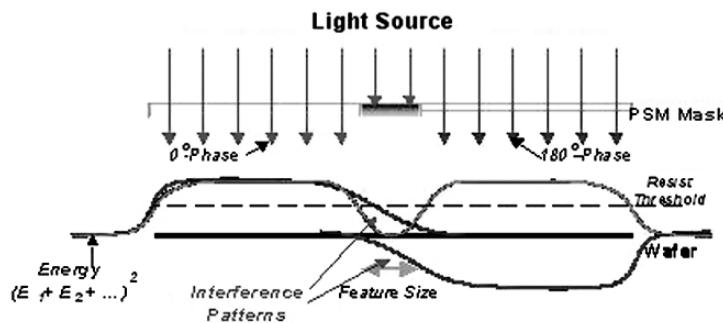

#### 1.2.2.4 Resolution Enhancement Techniques (RET)

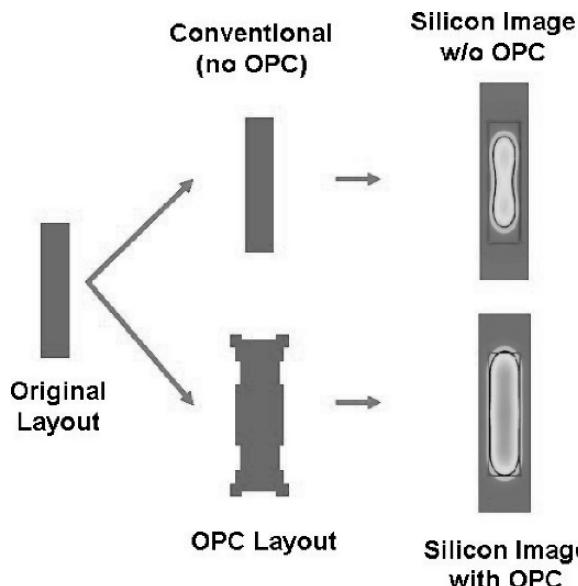

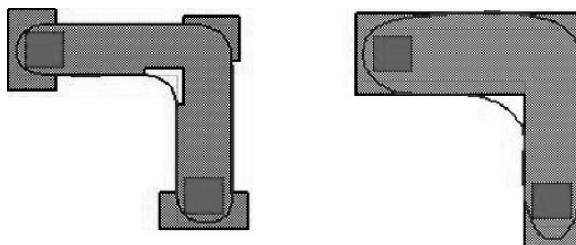

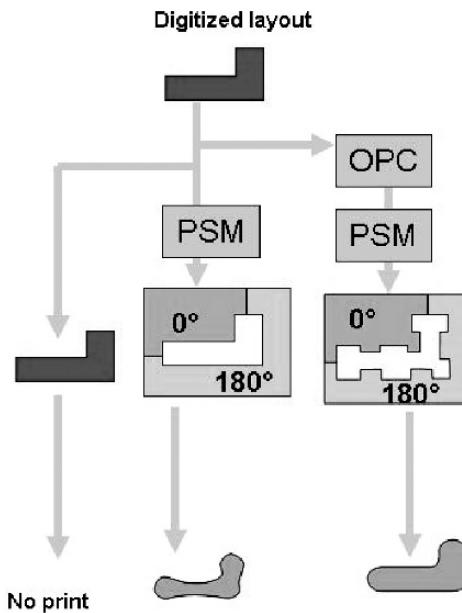

RET is defined as the set of optical and geometrical (layout) procedures performed individually or in any particular combination to enhance the printability of design features and to meet design intent. Figure 1.4 demonstrates the need for OPC in sub-wavelength lithography. Examples of layout procedures are optical proximity correction (OPC), which could be rule or model based, and which involves the addition of sub-resolution assist features (SRAF). An example of a combination of a layout-mask procedure would be phase-shift mask (PSM). Examples of optical procedures of RET includes off-axis illumination, pupil filtering, and multiple exposures. Since we will be covering these in detail in Chapter 3 we will limit our exposure of this topic to the basics.

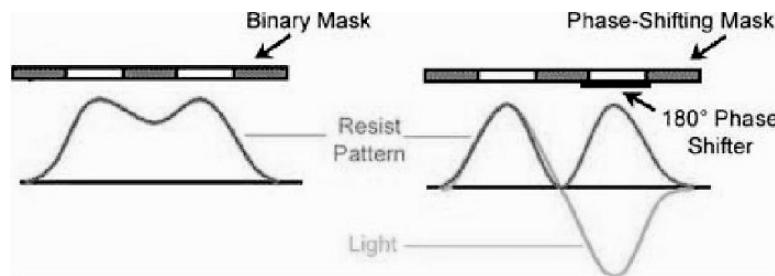

Figure 1.5 is illustrations of the use of strong PSM for tight geometry resolution. The resist pattern to the left reflects the result of the exposure of a binary mask with a feature smaller than half of the light source wavelength. There is simply no resolution of the geometry whatsoever and the intended feature is totally missed. By applying strong PSM (right) the light interference due to

Figure 1.3.  $NA = I \sin \alpha$

Figure 1.4. Basic Example of OPC at 180nm

the phase altered light wave allows a good resolution of the intended geometry. PSM is achieved by special processing of the mask based on a defined pattern to create a 180 degrees phase shift for light waves passing through the treated mask pattern.

### 1.2.3 New Devices

In this section we briefly touch on new devices in the context of the ever growing complexity of correctly extracting devices and interconnect, and in the context of growing complexity of process integration. The motivating factors are again dominated by power (especially leakage control) and performance considerations.

Figure 1.5. Example of Strong (180) PSM

### 1.2.3.1 Double-gates, Triple gates, and FinFETs

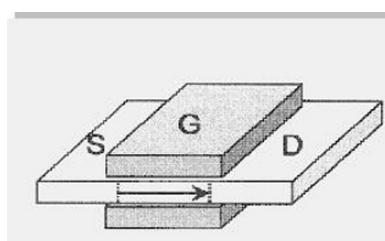

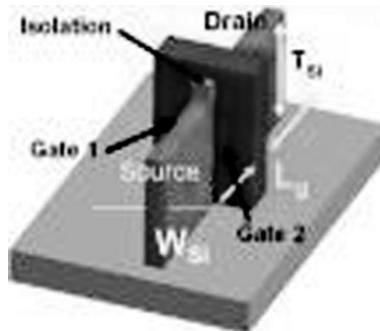

Double gates (Figure 1.6), triple-gates, and FinFETs (Figure 1.7) are all mainly a derivative of the desire to control leakage and short channel effects made worse by device scaling. The idea is rooted in the fact that most leakage occurs in the region far from the channel surface, therefore most of that leakage can be eliminated by having a thin body (shorter than channel length). The use of a double-gate, triple-gate, or finFET (triple gate with strict fin height ( $T_{si}$ ) and fin width ( $W_{si}$ ) ratio) will result in good controllability of both leakage and short channel effects without the need to resort to aggressive gate oxide scaling or heavy channel doping.

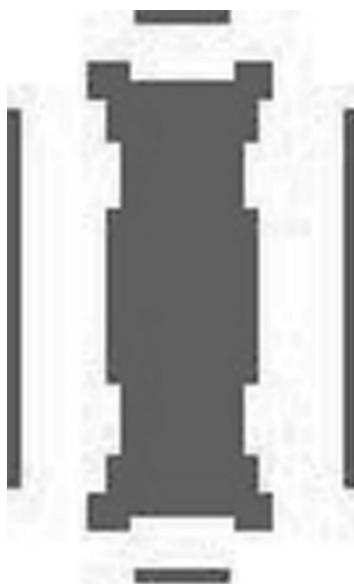

FinFET architecture is a bit restrictive for standard cell library generation but nonetheless manageable since most standard cell libraries use predetermined P/N device ratios to start with. Figure 1.8 shows an example of a multi-segment finFET layout for a standard cell implementation. However, it is worth noting (near term) that FinFET structures have been reported to have some structural reliability issues related to the mechanical stability of the fin structures. It is still not clear if FinFETs will be introduced any sooner than the 32 nm node. Most roadmaps still show bulk planar CMOS FETs at the 45nm node.

### 1.2.3.2 Silicon on Insulator (SOI)

The use of silicon on insulator in gaining ground as the cost differential between bulk CMOS and SOI continues to shrink and as the need for higher performance at lower power consumption grows (SOI delivers a technology node performance advantage at the same power level of an existing CMOS technology node, or, delivers same performance at a significantly reduced power- 15 to 20 percent). Originally partially depleted SOI was more dominant than fully depleted SOI. Uncertainties associated with history effects, characteristics of partially depleted SOI encouraged the move to fully depleted SOI. But, manufacturability issues associated with poor controllability of thresholds in fully depleted SOI reverted the interest back to partially depleted SOI.

Figure 1.6. Double-gate FET

Figure 1.7. TCAD Simulated FinFET

We bring the issue of SOI in this section because of the reliability and predictability issues associated with SOI in terms of history effects and  $V_t$  control, localized thermal heating profiles, Electro-static Discharge (ESD), and other SOI specific concerns that need to be addressed carefully.

SOI, with both flavors of partially depleted and fully depleted, is not a new technology. But, given that FinFETs and triple gate structures and similar devices aimed at reducing leakage are not yet proven technologies for 45nm and beyond, the interest in partially depleted SOI is once again on the rise as an alternative solution. The shrinkage in the price differential between SOI and bulk CMOS is helping that trend.

### 1.2.3.3 Carbon Nanotube Devices, MEMS, and Molecular Devices

We will limit ourselves to the simple mention that the integration of emerging nano-devices of all flavors as well as MEMS and nano-fluidic devices with classical CMOS processes is gaining momentum and simply adds to the complexity of DFM and DFY issues. We specifically mention single walled carbon

Figure 1.8. Layout of Multi-segment FinFET

nano-tubes (SWCNT) for via structures and nano wires (silicon and other materials) for devices and interconnect. We will not go into those issues with any depth as it is beyond the scope of this book but we simply wanted to alert the practicing engineer to keep a keen eye on these emerging technologies and their interaction and integration with the classical design flow.

### **1.2.4 Proliferation of Processes**

Traditionally the fabrication facilities (FAB) owned DFM and DFY in the sense that the starting point of the design process was a hand over of the process design rules from the process engineers to the designers and the end point was the process engineers continuously tweaking the process to improve parameters causing marginal yield or high failure rates until a process is mature. As we have already stressed in this chapter and we'll be stressing throughout the book the concept of "hand over" or design rules of solid boundaries between various functionaries in the product cycle is long over. In this section we will tackle two issues characteristic of the nano era fabrication facilities namely the proliferation of many processes at any given technology node, and the complexities of those processes with what this implies to EDA tools in general and technology computer-aided design (TCAD) tools in particular.

#### **1.2.4.1 Application Specific Processes**

The presence of multi-flavors of any technology node in the form of low power oriented and high performance oriented processes dates back to the 0.6um technology node, perhaps even before. But beyond the 90 nm node two factors have contributed to the further segregation and specialization of processes. One being power, or one should say the power crisis. With proliferation of hand held battery operated devices, and with idle (non-operating) leakage current becoming of comparable magnitude to operating current further division and segmentation within the power options has been exacerbated. The other originates in the level of integration where RF, analog, AMS, and digital functions need to co-exist with a very specific combination of power and performance. Therefore fine division lines entered the picture between processes resulting in separate technology roadmaps driven by the end products they are targeted for and the complexity of dealing with this plethora of processes increased significantly. Example will be: low cost, low power mobile, ultra low power biomedical, high performance, RF, etc.

#### **1.2.4.2 Processing Complexities**

We will not go in this introductory chapter into too many details of each of the process complexities except when it is related to EDA tools geared toward DFM / DFY, but nonetheless we enumerate many of the nano era process complexities

that impacts manufacturability and yield directly or indirectly. Most of those complexities are driven by scaling requirements (thin body, ultra shallow junctions, high dopant concentrations, etc) and power (leakage) requirements. To list but a few:

- Co-implantation of species to suppress diffusion

- Diffusion-less activation for ultra shallow junctions