## Lecture Notes in Computer Science

6371

Commenced Publication in 1973

Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

## **Editorial Board**

David Hutchison

Lancaster University, UK

Takeo Kanade

Carnegie Mellon University, Pittsburgh, PA, USA

Josef Kittler

University of Surrey, Guildford, UK

Jon M. Kleinberg

Cornell University, Ithaca, NY, USA

Alfred Kobsa

University of California, Irvine, CA, USA

Friedemann Mattern

ETH Zurich, Switzerland

John C. Mitchell

Stanford University, CA, USA

Moni Naor

Weizmann Institute of Science, Rehovot, Israel

Oscar Nierstrasz

University of Bern, Switzerland

C. Pandu Rangan

Indian Institute of Technology, Madras, India

Bernhard Steffen

TU Dortmund University, Germany

Madhu Sudan

Microsoft Research, Cambridge, MA, USA

Demetri Terzopoulos

University of California, Los Angeles, CA, USA

Doug Tygar

University of California, Berkeley, CA, USA

Gerhard Weikum

Max Planck Institute for Informatics, Saarbruecken, Germany

# Formal Methods for Industrial Critical Systems

15th International Workshop, FMICS 2010 Antwerp, Belgium, September 20-21, 2010 Proceedings

#### Volume Editors

Stefan Kowalewski RWTH Aachen, Embedded Software Laboratory Ahornstr. 55, 52074, Aachen, Germany E-mail: kowalewski@embedded.rwth-aachen.de

Marco Roveri Fondazione Bruno Kessler – IRST Via Sommarive 18, 38123, Povo (Trento), Italy E-mail: roveri@fbk.eu

Library of Congress Control Number: 2010934239

CR Subject Classification (1998): D.2.4, D.2, D.3, C.3, F.3, I.6

LNCS Sublibrary: SL 2 – Programming and Software Engineering

ISSN 0302-9743

ISBN-10 3-642-15897-8 Springer Berlin Heidelberg New York ISBN-13 978-3-642-15897-1 Springer Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

springer.com

© Springer-Verlag Berlin Heidelberg 2010 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India Printed on acid-free paper 06/3180

## Preface

This volume contains the papers presented at FMICS 2010, the 15th International Workshop on Formal Methods for Industrial Critical Systems, which was held on September 20-21, 2010, in Antwerp, Belgium. Previous workshops of the ERCIM working group on Formal Methods for Industrial Critical Systems were held in Oxford (March 1996), Cesena (July 1997), Amsterdam (May 1998), Trento (July 1999), Berlin (April 2000), Paris (July 2001), Malaga (July 2002), Trondheim (June 2003), Linz (September 2004), Lisbon (September 2005), Bonn (August 2006), Berlin (July 2007), L'Aquila (September 2008), and Eindhoven (November 2009).

The aim of the FMICS workshop series is to provide a forum for researchers who are interested in the development and application of formal methods in industry. In particular, these workshops bring together scientists and engineers who are active in the area of formal methods and are interested in exchanging their experiences in the industrial usage of these methods. These workshops also strive to promote research and development for the improvement of formal methods and tools for industrial applications.

The FMICS 2010 workshop was co-located with ASE 2010, the 25th IEEE/ACM International Conference on Automated Software Engineering, which offered a choice of events in the area in addition to the main conference. More information about ASE 2010 and the co-located events can be found on http://soft.vub.ac.be/ase2010/.

The topics chosen for FMICS 2010 included, but were not restricted to:

- Design, specification, code generation, and testing based on formal methods;

- Methods, techniques, and tools to support automated analysis, certification, debugging, learning, optimization, and transformation of complex, distributed, real-time systems, and embedded systems;

- Verification and validation methods that address shortcomings of existing methods with respect to their industrial applicability (e.g., scalability and usability issues);

- Tools for the development of formal design descriptions;

- Case studies and experience reports on industrial applications of formal methods, focusing on lessons learned or identification of new research directions;

- Impact of the adoption of formal methods on the development process and associated costs;

- Application of formal methods in standardization and industrial forums.

In response to the call for papers, 33 contributions were submitted from 16 different countries. The Program Committee selected 14 papers, basing this choice on their scientific quality, originality, and relevance to the workshop. Each paper was reviewed by at least four Program Committee members or external referees.

#### VI Preface

In addition to the regular papers, the workshop included four invited presentations by Aarti Gupta (NEC Labs, USA), Axel Simon (Technical University of Munich, Germany), Stephan Tobies (European Microsoft Innovation Center, Aachen, Germany), and Bert van Beek (Technical University of Eindhoven, The Netherlands).

Following a tradition established over the past few years, the European Association of Software Science and Technology (EASST) offered an award to the best FMICS paper. Further information about the FMICS working group and the next FMICS workshop can be found at: http://www.inrialpes.fr/vasy/fmics.

On behalf of the Program Committee, we would like to express our gratitude to all the authors who submitted papers and all external referees for their careful work in the reviewing process. Special thanks go to Jörg Brauer who supported the program chairs in many respects, and to Alessandro Fantechi, the coordinator of the ERCIM Working Group on Formal Methods for Industrial Critical Systems, for sharing his experiences. We are very grateful to the organizers of ASE 2010, who worked with enthusiasm in order to make this event possible. We are also grateful to Andrei Voronkov for making EasyChair available to us. Finally, we gratefully acknowledge the institutions which sponsored this event: Fondazione Bruno Kessler, RWTH Aachen University, ERCIM, EASST, European Microsoft Innovation Center, the research cluster Ultra High Speed Information and Communication Systems (UMIC), and AXXTEQ GmbH.

September 2010

Stefan Kowalewski Marco Roveri

## Organization

## **Program Chairs**

Stefan Kowalewski RWTH Aachen University, Germany

Marco Roveri FBK-irst, Italy

## **ERCIM FMICS Working Group Coordinator**

Alessandro Fantechi Università degli Studi di Firenze and

ISTI-CNR, Italy

## Program Committee

María Alpuente Technical University of Valencia, Spain Jörg Brauer RWTH Aachen University, Germany Luboš Brim Masarykova Univerzita, Czech Republic Dino Distefano Queen Mary, University of London, UK

Wan Fokkink Vrije Universiteit Amsterdam, The Netherlands

Hubert Garavel INRIA Rhône-Alpes, France

Stefania Gnesi ISTI-CNR, Italy Aarti Gupta NEC Labs, USA

Holger Hermanns Universität des Saarlandes, Germany

Barbara Jobstmann VERIMAG, France

Andy King Portcullis Computer Security, UK

Daniel Kroening Oxford University, UK

Thomas Kropf Bosch, Germany

Diego Latella CNR/IST Pisa, Italy

Thierry Lecomte ClearSy, France

Radu Mateescu INRIA Rhône-Alpes, France Pedro Merino Universidad de Málaga, Spain

Juan José Moreno-Navarro Universidad Politécnica de Madrid, Spain

Francois Pilarski Airbus, France

Andreas Podelski University of Freiburg, Germany

Jaco van de Pol Universiteit Twente, The Netherlands

Jakob Rehof Technische Universität Dortmund, Germany

Thomas Santen Microsoft (EMIC), Germany

Wilfried Steiner TTTech, Austria

#### External Reviewers

Mauricio F. Alba-Castro

Jiri Barnat

Maurice H. ter Beek

Clara Benac Earle Sebastian Biallas

Andrea Bracciali Doina Bucur

Manuel Carro Liñarez

Milan Češka

Jakub Chaloupka

Eva Darulova

Alessandro Fantechi

Marco A. Feliú Lars-Åke Fredlund

Emilio Jesús Gallego Arias

Rodolfo Gomez Nikos Gorogiannis

Daniele Grasso

Karin Greimel

Andreas Griesmayer Radu Grigore

Alex Groce

Raúl Gutiérrez Paul Hänsch Ángel Herranz Alexander Kaiser

Volker Kamin

Mark Kattenbelt

Jeroen Ketema

Viktor Kuncak

Frédéric Lang Ralf Laue

Julio Mariño Mieke Massink

Franco Mazzanti

Ralf Möller

Nannan He Jacob Palczynski

Laura Panizo

Technical University of Valencia, Spain Masarykova Universita, Czech Republic

CNR/IST, Italy

Universidad Politécnica de Madrid, Spain RWTH Aachen University, Germany

Università de Pisa, Italy Oxford University, UK

Technical University of Valencia, Spain

Brno University of Technology, Czech Republic

Masarykova Univerzita, Czech Republic

EPFL, Switzerland

Università degli Studi di Firenze and

ISTI-CNR, Italy

Technical University of Valencia, Spain Universidad Politécnica de Madrid, Spain Universidad Politécnica de Madrid, Spain

University of Kent, UK

Queen Mary, University of London, UK General Electric Transportation Systems

(GETS), Italy

Graz University of Technology, Austria

VERIMAG, France

Queen Mary, University of London, UK

Oregon State University, USA

Technical University of Valencia, Spain RWTH Aachen University, Germany Universidad Politécnica de Madrid, Spain

Oxford University, UK

RWTH Aachen University, Germany

Oxford University, UK

Universiteit Twente, The Netherlands

EPFL, Switzerland

INRIA Rhône-Alpes, France Universität Leipzig, Germany

Universidad Politécnica de Madrid, Spain

CNR/IST Pisa, Italy CNR/IST Pisa, Italy

Hamburg University of Technology, Germany

Oxford University, UK

RWTH Aachen University, Germany

Universidad de Málaga, Spain

Elwin Pater

Rasmus Lerchedahl Petersen

Daniel Riesco Petr Ročkai

Daniel Omar Romero

Gwen Salaün Alberto Salmerón David Sanan

Sonia Santiago Pinazo Mark Schellhase Wendelin Serwe Nicolas Stouls

Salvador Tamarit Muñoz

Fernando Tarín Andrei Tchaltsev Francesco Tiezzi Mark Timmer Laura Titolo Michael Weber Universiteit Twente, The Netherlands Queen Mary, University of London, UK National University of San Luis, Argentina Masarykova University, Czech Republic Technical University of Valencia, Spain

INRIA Rhône-Alpes, France Universidad de Málaga, Spain Universidad de Málaga, Spain

Technical University of Valencia, Spain Queen Mary, University of London, UK

INRIA Rhône-Alpes, France

Laboratoire CITI, INSA de Lyon, France Technical University of Valencia, Spain Technical University of Valencia, Spain

FBK-irst, Italy

Università degli Studi di Firenze, Italy Universiteit Twente, The Netherlands Technical University of Valencia, Spain Universiteit Twente, The Netherlands

## **Table of Contents**

| The Metrô Rio ATP Case Study                                                                                                                                                                 | 1   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Practical Issues with Formal Specifications: Lessons Learned from an Industrial Case Study                                                                                                   | 17  |

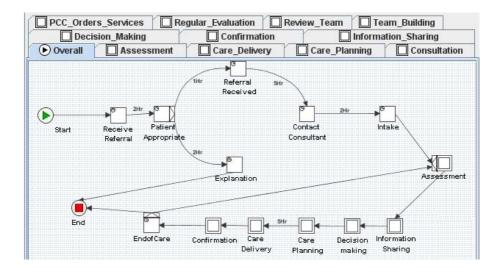

| Formal Analysis of BPMN Models Using Event-B                                                                                                                                                 | 33  |

| Developing Mode-Rich Satellite Software by Refinement in Event B Alexei Iliasov, Elena Troubitsyna, Linas Laibinis, Alexander Romanovsky, Kimmo Varpaaniemi, Dubravka Ilic, and Timo Latvala | 50  |

| Automatic Error Correction of Java Programs                                                                                                                                                  | 67  |

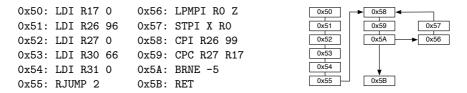

| Range Analysis of Microcontroller Code Using Bit-Level Congruences                                                                                                                           | 82  |

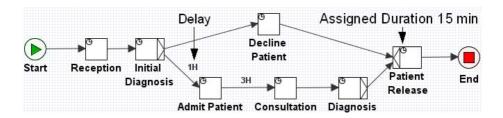

| An Automated Translator for Model Checking Time Constrained Workflow Systems                                                                                                                 | 99  |

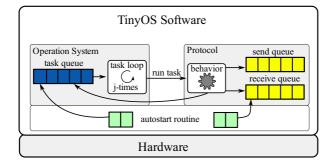

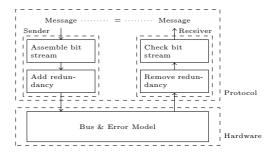

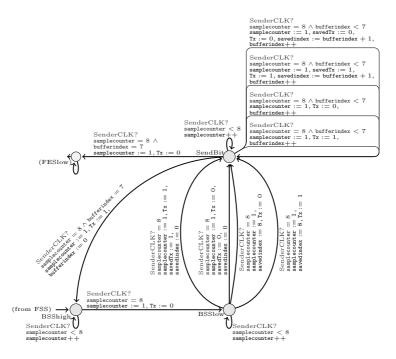

| Correctness of Sensor Network Applications by Software Bounded<br>Model Checking                                                                                                             | 115 |

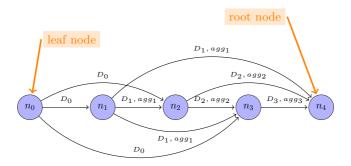

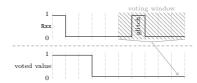

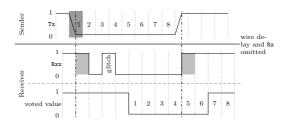

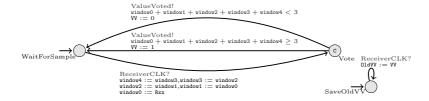

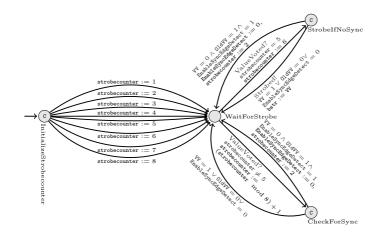

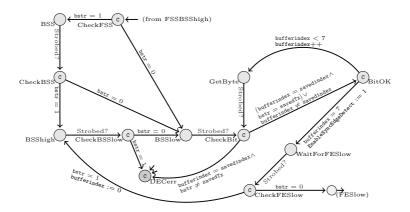

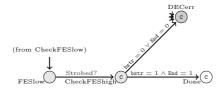

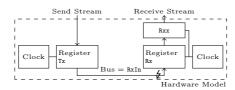

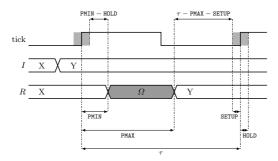

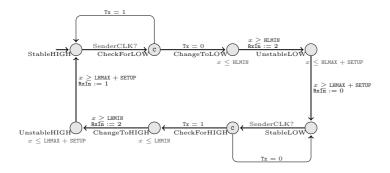

| Model Checking the FlexRay Physical Layer Protocol                                                                                                                                           | 132 |

| SMT-Based Formal Verification of a <i>TTEthernet</i> Synchronization Function                                                                                                                | 148 |

| Embedded Network Protocols for Mobile Devices                                                                                                                                                | 164 |

## XII Table of Contents

| A Study of Shared-Memory Mutual Exclusion Protocols Using CADP                         | 180 |

|----------------------------------------------------------------------------------------|-----|

| Radu Mateescu and Wendelin Serwe                                                       | 100 |

| A Formal Model of Identity Mixer                                                       | 198 |

| Automatic Structure-Based Code Generation from Coloured Petri Nets: A Proof of Concept | 215 |

| Author Index                                                                           | 231 |

## The Metrô Rio ATP Case Study

Alessio Ferrari<sup>1</sup>, Daniele Grasso<sup>2</sup>, Gianluca Magnani<sup>2</sup>, Alessandro Fantechi<sup>2</sup>, and Matteo Tempestini<sup>1</sup>

<sup>1</sup> General Electric Transportation Systems (GETS), Firenze, Italy

<sup>2</sup> Universitá di Firenze, DSI, Firenze, Italy

Abstract. This paper reports on the Simulink/Stateflow based development of the on-board equipment of the Metrô Rio Automatic Train Protection system. Particular focus is given to the strategies followed to address formal weaknesses and certification issues of the adopted toolsuite. On the development side, constraints on the Simulink/Stateflow semantics have been introduced and design practices have been adopted to gradually achieve a formal model of the system. On the verification side, a two-phase approach based on model based testing and abstract interpretation has been followed to enforce functional correctness and runtime error freedom.

Quantitative results are presented to assess the overall strategy: the effort required by the design activities is balanced by the effectiveness of the verification tasks enabled by model based development and automatic code generation.

## 1 Introduction

Industrial applications of formal methods and model based development for rail-way signaling systems are discussed in many case studies. The Paris Metro [16], the SACEM system [17], and the San Juan metro [18] are past and recent examples of successful stories about the usage of these technologies in the railway domain. In this paper, we offer a further insight into the actual industrial usage of formal methods, describing the experience of a railway signaling company, namely the railway signaling division of General Electric Transportation Systems (GETS), in adopting formal specification and development techniques by means of Simulink/Stateflow for the development of the Metrô Rio Automatic Train Protection (ATP) system.

GETS was commissioned for the adaptation of its SSC ATP to Metrô Rio at the end of 2008. This was a time when the company was finishing its first large scale development project that made use of formal model based development with Simulink/Stateflow. Introducing this tool-suite within a safety-critical process is not a straightforward step: the lack of a formal semantics of the language and the absence of a certified code generator require strategies to be defined in order to have a sound and safe development. SSC - Metrô Rio provided the opportunity to improve and assess the process practices experimented in previous projects to address these issues. Indeed, GETS adopted the Simulink/Stateflow

platform first for the development of prototypes [9] and afterwards for requirements formalization and code generation [2]. Experimentation with the code generator led to the definition of an internal set of modeling rules in the form of an extension of the MAAB guidelines [6], a stable and widely accepted standard developed by automotive companies. With SSC - Metrô Rio, additional rules have been introduced to constrain the language to a semantically unambiguous set and a hierarchical derivation approach has been defined in order to gradually achieve a formal model of the system. Concerning verification of models and generated code, an enhancement of the two-phase approach presented in [13] has been adopted: control-flow and functional properties have been verified through model based testing, while static analysis by means of abstract interpretation has been used to check data-flow properties. The model based testing activity has been performed through a code validation framework that executes the same test cases both at model level and at code level, automatically verifying consistency of the test results for each model unit. This idea basically settles the problem of having a qualified code generator, since certification of conformity can be ensured each time the code is synthesized from a model.

The successful application of the presented process, witnessed by encouraging results in terms of cost reduction and safety assurance, has actually open the door to formal verification and we are currently exploring activities in this direction.

## 2 SSC Metrô Rio ATP System

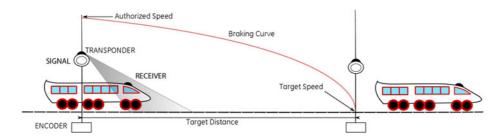

The role of a metro signaling system is to protect trains by keeping vehicles a safe distance apart. Traditionally, the traffic along metro tracks is managed by dividing each track into segments called *block sections* or simply *blocks*, and ensuring each train not to enter a given block section unless the block is clear of other trains. Signals are placed at the beginning of each block to inform the drivers about the status of the section that they are entering. The meaning of each signal aspect can be broadly represented by three pieces of information (see Fig. 1):

Authorized speed: the speed that is permitted in the block that is being entered; Target distance: the maximum distance that the train can move while still being protected;

Target speed: the maximum speed that the train is permitted to have over the target distance.

Automatic Train Protection (ATP) systems, such as the SSC Metrô Rio one, are typically embedded platforms that enforce the rules of signaling systems by adding an on-board automatic control over the speed limit allowed to trains along the track, thereby ensuring the safety of movement of the trains and consistent protection of the line traffic independent of train operator actions.

The SSC Metrô Rio system consists of wayside devices, composed by an encoder and a transponder, that respectively encode and transmit a telegram that contains the data to be processed by the carborne equipment. The wayside devices are positioned close to the actual signals, and the combination of encoder

Fig. 1. Authorized speed, Target distance and Target speed

and transponder is commonly referred to as an *information point*. The carborne equipment receives the telegram data and performs the actual enforcement of train speed. Information managed by the carborne equipment concerns the approach speed and distance for signals, but also other information typical for a metro, such as the distance to the next platform and speed reduction due to particular conditions of the line. All of this information is managed by the system as concurrent targets: for each restriction, multiple braking curves are computed to determine the most restrictive speed. Interaction with the driver is primarily via a touch-screen panel which displays a speedometer with the current speed and the active speed limit, and provides a set of buttons and icons to let the driver control and monitor the system.

## 3 Process Overview

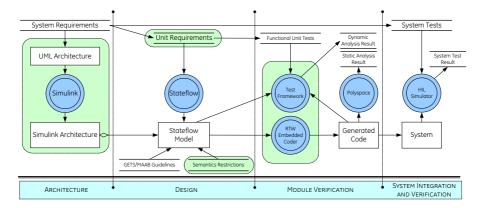

In this paper we focus on the approach followed for the development of the carborne equipment of the SSC Metrô Rio. The process adopted represents an application of model based practices to a V based life-cycle. Four phases are considered as the core of the system development: architecture, design, module verification and system integration/verification. Architecture and design activities concerning the project have been reported in a previous paper [15], while the verification steps represent an enhancement of the approach presented in [13].

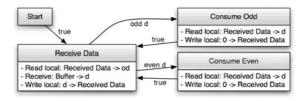

Fig. 2 summarizes the overall process structure. Embedded in gray rounded boxes are the novel elements that have been introduced for this project. Starting from system requirements and using domain knowledge, a functional architecture in the form of a UML component diagram has been defined consisting of independent functional units. According to this decomposition, system requirements are partitioned into mutually exclusive sets of unit requirements to be apportioned to the functions. The UML architecture is then translated into a Simulink architecture and the unit requirements are formalized in terms of Stateflow finite-state automata. The software of an on-board equipment of an ATP system, such as the SSC - Metrô Rio product, is characterized by the extensive usage of control modes logic and message analysis algorithms. These are all features that can be properly represented through state machines, and hence through discrete Stateflow models. Due to this reason, in the context of the project,

Fig. 2. Process Overview

only Stateflow has been adopted as specification language, while Simulink was only used as a simulation framework to allow interaction among Stateflow charts. Stateflow models have been designed using a safe subset of the language in order to ensure proper code synthesis. In previous projects already an extension of the MAAB guidelines was used, aimed at enhancing the readability, maintainability and structuring of the code, while with SSC Metrô Rio additional restrictions have been introduced to further constrain the Stateflow semantics to an unambiguous set of constructs. Concerning code generation, the company adopted the more customizable RTW Embedded Coder in place of Stateflow Coder: the transition was basically painless, since all the modeling rules developed for the previous tool resulted in being applicable also for the new one. Unit tests have been defined in the form of scenarios at Stateflow model level, using an internally developed framework that automatically executes the test suite on the Stateflow automaton and on the generated code to ensure functional coherence between model and software behaviour. The confidence on the correctness of the generated code is increased with the PolySpace tool for abstract interpretation, that completes the unit-level verification activities. Finally, system tests are performed on an ad-hoc train simulator with hardware in the loop.

#### 4 Hierarchical Architecture Definition

When a large requirements set is involved in formal modeling, a well defined architecture of the model can help in clarifying which are the components of the system and how they are interconnected, bridging the gap between requirements definition and component design. When automatic code generation is adopted, the architecture of the model is reflected in the software: an effort has hence to be made to create formal models having a structure that makes sense also in terms of the architecture of the software system.

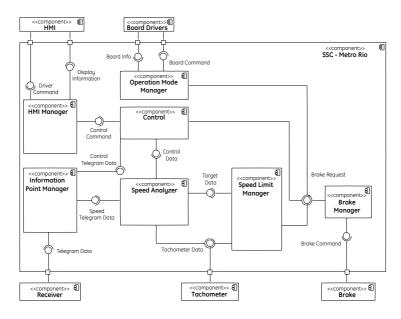

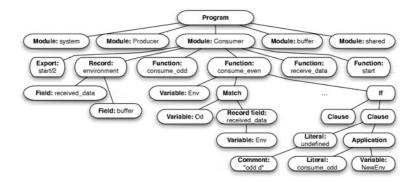

Fig. 3. Simplified component diagram

Though being powerful languages, Simulink and Stateflow are not suitable to represent the high-level architecture of a system and a more abstract approach was required in order to identify the semantic relationships between the software functional units to build up the conceptual architecture of the application. In the context of the project, we found useful to first represent the high-level software architecture through a UML component diagram (a simplified version is represented in Fig. 3). UML component diagrams focus on the interfaces and dependencies of the functional units. Each component is basically defined by a set of implemented interfaces, a set of required interfaces and a set of dependencies. In the diagram, the external components represent the software drivers that interface the system to external devices, such as the tachometer and the braking command device, while the internal components are the system functions (for a better insight refer to [15]).

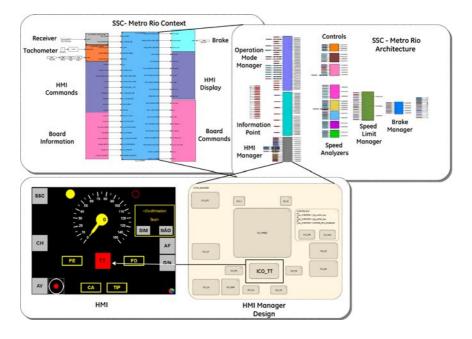

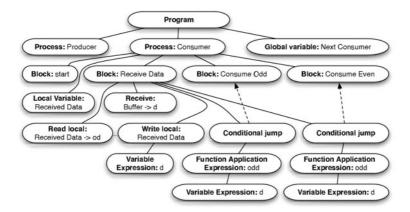

In order to properly formalize this architecture through Simulink/Stateflow, the chosen strategy was to represent the system through a multiple-level hierarchical model (see Fig. 4). The different levels are intended for different development stages, from a more abstract to a more detailed view. A first level is defining the context, which means the interfaces with the environment in terms of input/output data. Starting from the component diagram, this level has been derived considering the boundary ports and mapping them into signals entering or exiting the Simulink blocks. This approach allowed us defining the borders of the software system, which can be treated as a black box completely defined by

Fig. 4. The multiple level hierarchical model

its input/output signals. As part of this model we introduced other blocks simulating the actual interfaces (tachometer data, touch-screen buttons, telegram data, etc.), to perform interactive testing of the model.

A second level represents the internal software architecture in terms of interacting functional units modeled through Stateflow charts. For each one of the components of the original diagram, a Stateflow chart has been defined having the same input/output interfaces in terms of variables: each required interface becomes a set of input variables, while each implemented interface becomes a set of output variables. Note that no function is implemented through Simulink, used only as a simulation framework, and no block with continuous dynamics is used in our approach: any anlaysis problem that might be related to a hybrid semantics is therefore discarded.

A third level is actually the design level of the single Stateflow charts, each of them structured into parallel state machines formally modeling the system functional requirements. In order to derive such a formal model from the system requirements written in natural language, we first decomposed them into mutually exclusive sets of unit requirements, to identify the requirements apportioned to each single Stateflow chart. For example, consider the system functional requirement concerning the control over the unauthorized passing of a red signal (normally called Train Trip function): When a red signal is passed without authorization, the system shall brake the train and the Train Trip icon (ICO\_TT) shall blink on the display until the train come to a standstill.

The requirement is decomposed as reported in Table 1.

|   | 1.0                                                                                                                        | Module            |

|---|----------------------------------------------------------------------------------------------------------------------------|-------------------|

| 1 | If an information point with authorized speed equals to zero is received,                                                  | Information Point |

|   | If an information point with authorized speed equals to zero is received, the system shall raise the Train Trip (TT) event | Manager           |

| 2 | If the TT event is raised, the TT procedure shall be activated                                                             | Red Control       |

| 3 | If the TT procedure is active, it shall remain active until the train is                                                   | Red Control       |

|   | not standing                                                                                                               |                   |

| 4 | If the TT procedure is active, the brake shall be activated                                                                | Brake Manager     |

| 5 | If the TT procedure is active and ICO_TT is invisible, ICO_TT shall                                                        | HMI Manager       |

|   | start blinking                                                                                                             |                   |

Table 1. Unit requirements decomposition

The first unit requirement is apportioned to the Information Point Manager, since this component is intended to interpret the telegram data and to forward events to the other functions. The second and third requirements are apportioned to the Red Control, which manages authorized and unauthorized passing of red signals. The fourth requirement is apportioned to the Brake Manager, that enforces any brake condition, and the fifth requirement is apportioned to the HMI Manager, controlling the interaction with the driver.

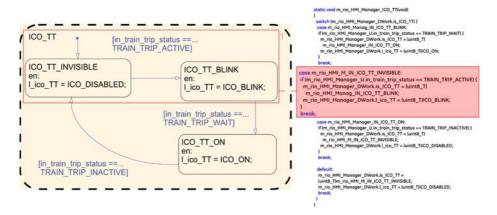

Fig. 5 shows the formal representation of the ICO\_TT state machine, modeling the fifth requirement of Table 1, together with the corresponding generated code.

Fig. 5. Example of unit requirement formalization

## 5 Modeling Guidelines

Stateflow implements a variant of Harel's hierarchical statecharts [3], normally called charts according to the Stateflow taxonomy. The complex semantics of Stateflow is not formally based, though research has been performed to define an operational semantics [4] and a denotational semantics [5] for a Stateflow subset. Along with the development of the SSC - Metrô Rio project, in order to achieve more easily an unambiguous interpretation of Stateflow models, coherent with the automatically generated code, we further extended the MAAB guidelines

| Original set                                        | Restricted subset                                                      |

|-----------------------------------------------------|------------------------------------------------------------------------|

| state s                                             | state s                                                                |

| active state $s_a = \oslash_s   s$                  | active state $s_a = \oslash_s   s$                                     |

| junction j                                          | junction j                                                             |

| path $p = \oslash_p   s.p$                          | path $p = \oslash_p   s.p$                                             |

| event e                                             | Ø                                                                      |

| destination $d = p j$                               | $\oslash$                                                              |

| action a                                            | action sequence $a = \bigcirc_a   ba.a$                                |

|                                                     | declarative action $da$                                                |

|                                                     | basic action $ba = da J$                                               |

| condition $c$                                       | condition $c$                                                          |

| transition $t = (e_t, c, a, a, d)$                  | state transition $t = (c, a, p), c \neq \emptyset, p \neq \emptyset_p$ |

|                                                     | junction transition $tj = ((c a), j)$                                  |

|                                                     | junction transition list $TJ = \oslash_{TJ}   tj.TJ$                   |

| transition list $T = \oslash_T   t.T$               | transition list $T = \oslash_T   t.T$                                  |

| composition                                         | composition                                                            |

| $C = OR(s_a, p, T, SD) AND(boolean, SD)$            | $C = OR(s_a, p, T, SD) AND(boolean, SD)$                               |

| state definition $sd = ((a, a, a), C, T_i, T_o, J)$ | state definition $sd = ((a, a, a), C, T_i, T_o)$                       |

|                                                     | where the conditions of the transitions in $T_o$                       |

|                                                     | are mutually exclusive                                                 |

| state definition list                               | state definition list                                                  |

| $SD = \{s_0 : sd_0; \dots; s_n : sd_n\}$            | $SD = \{s_0 : sd_0; \dots; s_n : sd_n\}$                               |

| junction definition list                            | junction definition list                                               |

| $I = \{i_0 \cdot T_0 \cdot i \cdot T \}$            | $I = \{i_0 \cdot T I_0 \cdot \cdots i_l \cdot T I_l\}$                 |

Table 2. Restricted Stateflow subset compared with the original language

adopted in previous projects with a set of restrictions oriented to restrict the use of the Stateflow language to a semantically unambiguous subset. With reference to the Stateflow language notation defined in [4], in Table 2 we represent the subset of Stateflow adopted for the SSC - Metrô Rio project that has been identified following the approach shown by Scaife et al. [8] for translating a subset of Stateflow into the Lustre formal language.

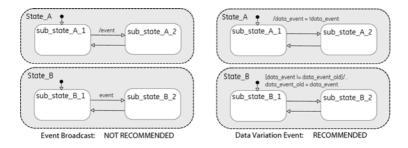

The main restriction concerns the elimination of events from the language, since, as pointed out in [8], use of events implies generation of recursive code that might lead to the risk of an infinite recursion call, stack overflow or anyway to state-space explosion problems. For this reason events are forbidden by the adopted modeling guidelines and they are simulated through variable assignments as depicted in Fig. 6. In Stateflow every chart is executed according to a deterministic sequence (State A executes always before State B) and therefore

Fig. 6. Events can be avoided through proper variable assignments

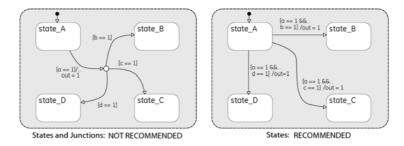

Fig. 7. State/Junctions transitions can be avoided through proper modeling solutions

any race condition is avoided. This approach preserves the sequential execution of the code, while allowing logical event implementation (each change on the variable value corresponds to an event).

Transitions have been distinguished between state transitions t and junction transition  $t_i$ : it is not allowed to define transitions between states and junctions. These are objects that have a different operational semantics: at each simulation step, states belonging to a single OR composition are mutually exclusive, while more than one junction can be traversed during the same step. The behavior discrepancy between the two objects might bring to improper combined usage. One of the well known possible hazards is backtracking without undo [8], a problem consisting in the possibility of traversing a path made of junctions, possibly assigning values to variables, and afterwards backtracking without restoring variable values. Fig. 7 shows how an improper modeling can be correctly translated into an equivalent, yet safer, representation. The restriction concerning the state definition object, besides eliminating junction definition lists from states, requires the conditions over outgoing transitions to be mutually exclusive in order to avoid Stateflow to evaluate firing of transitions according to the clockwise rule [4]. This rule implies that transitions are ordered by their graphical appearance: the first transition is the one whose edge starts closest to the upper left corner of the source state, and the others follow clockwise. This implies that transitions naturally perceived as non-deterministic by the user, and interpreted as non-deterministic in other formal statechart languages such as Statemate, are actually deterministic. For this reason we require to make this determinism explicit by using mutually exclusive condition on guards of transitions outgoing from the same state.

## 6 Verification Approach

Traditionally GETS has used, as the main approach to verification of code units, white-box testing based on path coverage. This approach has revealed to be almost unfeasible due to the high structural complexity of the automatically generated code. A two phase verification process [13] was defined to address this shortcoming: the first phase implements model based testing to verify the functional requirements coverage, the second phase employs abstract interpretation

[12] to statically enforce runtime errors detection. For the application to the Metrô Rio ATP the first phase has been improved to obtain an implicit validation of the code generator as well. The verification activity is completed by final system tests with hardware in the loop. In this paper we do not describe this last step since it is not strictly related to formal modeling.

#### 6.1 Model Based Testing and Code Validation

Products traditionally developed by GETS, like any railway signaling application developed for Europe, shall comply with the CENELEC standards [1]. This is a set of norms and methods to be used while implementing a product having a determined safety-critical nature. The CENELEC EN 50128 considers two alternative strategies to assure the correctness of the tools that produce code that is finally embedded in the product, such as compilers or automatic code generators: the first one requires the code generator to be validated, and the second one is based on the so called *proven in use* property. However, both strategies could not be applied for the adopted code generator: the validation of the generator is unfeasible, since the source code is proprietary and no information is given about its development process; the translator could anyway be considered as a *proven in use* tool, since it is used by a certain number of industries that operates in safety critical context. Furthermore, the creation of a specialized tool, and its validation, is not in line with the company strategy, that contemplates a strong usage of commercial tools.

The approach used in the context of the Metrô Rio project is inspired by the one presented in [10], called Translation Validation: this approach is not focused on the code generator itself, but on the inputs and the outputs of code generation process and on their comparison. The validation of the generated code is performed through two phases: the first one consists in running the same extensive test suite, (defined starting from the modeled requirements, with a 100% requirements coverage), on the models (by simulation) as well as on the generated code (by dynamic testing). In this phase a functional/black box testing is performed, where both model and code are stimulated with the same inputs, and their outputs are compared for equality. If there are differences between the model outputs and the code outputs, they shall be assessed. A successful outcome of this phase gives confidence that the model and the generated code will show the same behaviour in response to the same stimuli.

However it is still necessary to demonstrate that unexpected and unwanted behaviour has not been introduced during the translation process. The second phase is carried out to address this question: after the execution of the tests, the structural coverage percentage is measured on the models as well as on the code, and the measures are compared. As stated in [10], if the code coverage obtained after test execution is less than the model coverage, then some unwanted functionality might have been introduced by the translator. In order to perform this evaluation, it is necessary to use comparable metrics for model and code coverage [11]. In our case we chose to use decision coverage for the model and branch coverage for the code. The choice of those metrics is due to the fact that

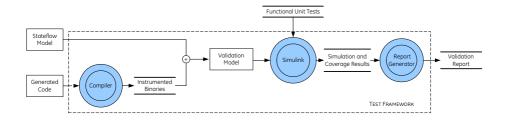

Fig. 8. 2M-TVF Test Framework

the CENELEC EN 50128 requires at least statements coverage; furthermore, since no continuos dynamic Simulink blocks are used in our modelling approach, the decision for those metrics is appropriate. A framework called 2M-TVF, that stands for Matlab Model Translation Validation Framework, has been developed to perform the model based testing and the code validation process. The framework works under the Simulink environment, and in order to carry out the validation process, allows for the definition of a validation model that includes both the Matlab model to be tested and the related generated code, embedded in a Simulink block. The code is previously instrumented to permit the evaluation of the coverage after the tests execution, and then it is compiled and linked to obtain the executable. The definition of the test suite is a manual activity, and derives the tests from the models and the unit requirements defined during the design phase of the system development, according to the requirement coverage criterion. Automatic test generation techniques were not used due to the fact that they generally requires models with a higher level of abstraction than the ones we use to generate code. The time needed to devise the tests, by a domain expert, is of the same order of magnitude than the time needed to model the system.

2M-TVF is totally automated: starting from the system under test (SUT) and a reference to the test suites, the framework uses RTW Embedded Coder to generate the code for the SUT and then it creates the validation model. The tests are then used as input for the validation model, and a report is visualized after the execution of every test. The report contains information about the result of the comparison of the model and code outputs and a detailed section on the coverage metrics obtained on both model and code. A subsequent analysis of the report is needed to assess every mismatch between outputs or coverage values.

By implementing the approach on many applications that use the same generator, it is possible to achieve the *proven in use* property for the code generator and, at the same time, to validate the generated code of every single application.

## 6.2 Abstract Interpretation

Abstract Interpretation is a static analysis method that is able to infer dynamic properties of the code and to detect runtime errors and faulty states of the program without executing the code. The method defines an overapproximation of

all the program reachable states, in order to check all the possible program runs. As one can infer from the theory, tools for abstract interpretation may lead to false positives caused by the analysis of runs possible in the overapproximation, but which do not belong to the real domain of the code. The tool chosen to perform abstract interpretation is PolySpace [14]. PolySpace works on C code and highlights possible runtime errors through the use of chromatic marks on the code:

- green if the statement can never lead to a runtime error;

- orange if the statement can produce an error;

- red if the statement leads to a runtime error in every analyzed runs;

- *grey* if the statement is not reachable.

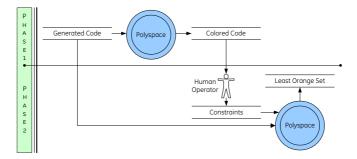

Usually, the critical issue in using PolySpace is the mining of actual code errors from the high number of orange warnings caused by overapproximation. GETS has adopted a two step process (see Fig. 9) in order to significantly reduce the orange checks that have to be manually reviewed. With the first step the code is quickly verified using a large overapproximation set. In the second step a finer approximation set is applied using the information obtained from the previous step. The first step is useful to detect systematic runtime errors (red) and

Fig. 9. Abstract Interpretation phase

unreachable statements (grey). Since no constraints are given in this analysis step, the set-up time spent is negligible. On the other hand results are not selective enough about the orange warnings, and, in order to define the constraints for the subsequent step, each orange has to be associated to the cause that could have produced it. An analyst with a minimum proficiency with the tool can easily evaluate the orange marks and quickly define the classes of causes they belong to, although in this step it is still difficult and time consuming to identify the oranges which are actually false positives. The identified classes give information sufficient to suggest input constraints to be given to the tool to restrict the analyzed abstract domain of the program. Examples of loose input constraints are related to interleaving of function calls and range of program variables. The tool generates an automatic call for each interface function of the module and initializes with full-range values the input parameters. Since the

tool has not information about the correct order of invocation of the interface functions, it verifies all the possible interleaving of the generated calls. In Fig. 10 the four orange warnings, highlighted by the arrows, are caused by the function call generation performed by the tool. The input parameters are initialized with full-range values and consequently the tool detects that the pointers could be outside their bounds. The information obtained in the first step are capitalised to identify the part of the approximation that it is needed to refine. In the case of the Fig. 10, the definition of the values range for the input parameters initialized by the tool represents a constraint to add for the execution of the subsequent step. The second verification step, performed with restrictive settings, allows a finer approximation of the real domain of the program and a reduction of the number of false positives. The analyst can quickly check the small number of

Fig. 10. Oranges caused by the automatic initialization of input function parameters

false positives and in the end is able to state that the code is free from runtime errors. It should be noticed that the use of two verification steps does not produce a high overhead. Our experience, as shown by the results given in the next section, confirms that the review performed on the first phase is simplified by the fact that the generated code is characterized by a limited number of classes of causes of orange warnings, while the results obtained with the second verification normally give a low number of warnings.

#### 6.3 Results

The SSC Metrô Rio ATP system consists of 13 Stateflow models for a total amount of approximately 120K lines of code. For each Stateflow model, unit test cases have been manually provided according to the functional requirement coverage. The test suite consists of 238 test-cases that cover 100% of functional requirements on the model. The test framework provides for executing the test cases, performed on the model, on the generated code. Table 3 compares the results of the verification activities on SSC Metrô Rio in terms of bugs found and time spent to detect and correct the bugs, with the results of these activities

**Table 3.** Bug detection and correction costs for comparable projects (modeling cost of approximately 4 man/months)

| Project       | #Modules | LOC  | #Bugs | Man/H |

|---------------|----------|------|-------|-------|

| SSC Metro Rio | 13       | 120K | 33    | 16    |

| SSC BL1Plus   | 12       | 40K  | 114   | 105   |

on SSC BL1 product, a previous ATP project based on model based development where only the MAAB guidelines with proper restrictions were used. Although the new system has considerably increased the number of lines of code, the guidelines refinement led to a notable reduction of bugs while the well defined architecture derived from the novel design approach has allowed us to detect the errors in shorter time.

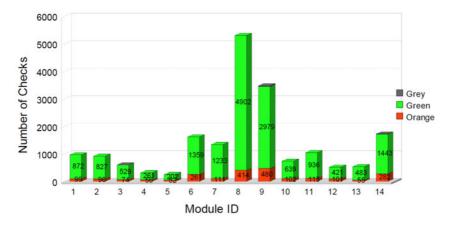

The first step of the PolySpace verification phase has detected no red errors, as shown in Fig. 11. Although many oranges have been detected, thanks to

Fig. 11. Results of the first PolySpace verification step

the characteristics of the generated code, it has not been time expensive to classify these warnings according to the kind of approximation that supposedly produced them. Indeed, due to the disciplined use of modeling guidelines, the generated code has an high number of simple structures and has well-defined module interfaces, which has helped to confine the causes of orange marks to the two only classes, already mentioned, of wrong interleaving of function calls and automatic initialization of input function parameters.

The second step of the PolySpace phase has led to only few orange warnings, and most modules turn out to be entirely green. The results have been compared with the ones obtained on another previous project where PolySpace was first applied, but where modeling guidelines were less restrictive. As in the previous project, the oranges detected in the first step are approximately 15% of the total number of checks for each module, but the time spent to classify the oranges and

| Project       | #Modules | Oranges | Analyse (hours) | Constraints (hours) |

|---------------|----------|---------|-----------------|---------------------|

| SSC Metro Rio | 13       | 2298    | 38              | 6                   |

| SSC BL3       | 21       | 1753    | 58              | 14                  |

Table 4. Comparison of costs for classification and constraints definition

to determine the constraints for the second step have been considerably reduced thanks to the well defined structure of the generated code (Table 4).

## 7 Conclusion

In this paper we presented the formal model based process adopted by a rail-way signaling manufacturer for the development of the on-board equipment of the Metrô Rio ATP system. The approach is the result of a long-term effort in introducing formal methods in the development process of the company. According to our experience, the cost of formal modeling is 30% higher than manual coding. This workload increase is partly due to the fact that graphic editing is inherently slower than textual editing, and partly to the training cost required by the technological shift. Nevertherless, the case study shows that this greater effort is payed back by the cost reduction of the verification activities (about 70% in total, with respect to a manual coding based process) and by the increased confidence on the product safety and quality.

A missing element in the presented process is formal verification: indeed, although experiments have been conducted by means of Simulink Design Verifier, they have not yet secured a place for formal verification inside the production development process. The company is currently investigating the optimal strategies to introduce a formal verification phase in the development process, also in relation to the added value with respect to certification issues: the investigation will not consider only commercial solutions such as Simulink Design Verifier, but also open source solutions like NuSMV and SPIN.

#### References

- European Committee for Electrotechnical Standardization: CENELEC EN 50128, Railway Applications - Software for Railway Control and Protection Systems (1997)

- Ferrari, A., Fantechi, A., Bacherini, S., Zingoni, N.: Modeling Guidelines for Code Generation in the Railway Signaling Context. In: 1st NASA Formal Methods Symphosium (NFM), Moffet Field, California, U.S.A. (2009)

- Harel, D.: Statecharts: A Visual Formalism for Complex Systems. Science of Computer Programming 8(3), 231–274 (1987)

- Hamon, G., Rushby, J.: An operational semantics for stateflow. In: Wermelinger, M., Margaria-Steffen, T. (eds.) FASE 2004. LNCS, vol. 2984, pp. 229–243. Springer, Heidelberg (2004)

- 5. Hamon, G.: A denotational semantics for stateflow. In: 5th ACM Int. Conf. on Embedded Software, Jersey City, NJ, USA, pp. 164–172 (2005)

- Mathworks Automotive Advisory Board (MAAB): Control Algorithm Modeling Guidelines Using Matlab, Simulink and Stateflow, Version 2.0 (2007), http://www.mathworks.com/industries/auto/maab.html

- Sahbani, A., Pascal, J.C.: Simulation of hybrid systems using stateflow. In: Proceedings of the 14th European Simulation Multiconference on Simulation and Modelling: Enablers for a Better Quality of Life, pp. 271–275 (2000)

- 8. Scaife, N., et al.: Defining and translating a safe subset of simulink/stateflow into lustre. In: 4th ACM Int. Conf. on Embedded Software, Pisa, Italy, pp. 259–268 (2004)

- Bacherini, S., Fantechi, A., Tempestini, M., Zingoni, N.: A Story about Formal Methods Adoption by a Railway Signaling Manufacturer. In: Misra, J., Nipkow, T., Sekerinski, E. (eds.) FM 2006. LNCS, vol. 4085, pp. 179–189. Springer, Heidelberg (2006)

- Conrad, M.: Testing-based translation validation of generated code in the context of IEC 61508. In: Formal Methods in System Design, pp. 389–401. Springer, Heidelberg (2009)

- Baresel, A., Conrad, M., Sadeghipour, S., Wegener, J.: The interplay between model coverage and code coverage. In: Proceedings of the 11th Eur. int. Conf. on Software Testing, Analysis and Review EuroSTAR'03, Amsterdam, Netherlands (2003)

- Cousot, P., Cousot, R.: Abstract interpretation: A unified lattice model for static analysis of programs by construction or approximation of fixpoints. In: 4th ACM Symp. on Principles of Programming Languages (POPL), Los Angeles, California, pp. 238–252 (1977)

- Grasso, D., Fantechi, A., Ferrari, A.: Model Based Testing and Abstract Interpretation in the Railway Signaling Context. In: 3rd International Conference on Software Testing, Verification and Validation (ICST), Paris, France, pp. 103–106 (2010)

- Deutsch, A.: Static verification of dynamic properties. PolySpace White Paper (2004)

- Ferrari, A., Fantechi, A., Papini, M., Grasso, D.: An industrial application of formal model based development: the Metrô Rio ATP case. In: 2nd International Workshop on Software Engineering for Resilient Systems, SERENE 2010 (2010)

- Faivre, A., Benoit, P.: Safety critical software of meteor developed with the B formal method and vital coded processor. In: Proc. of WCRR'99, pp. 84–89 (1999)

- 17. Guiho, G., Hennebert, A.: SACEM Software Validation. In: 12th International Conference on Software Engineering, pp. 186–191 (1990)

- Leuschel, M., et al.: Automated property verification for large scale B models.

In: Cavalcanti, A., Dams, D.R. (eds.) FM 2009. LNCS, vol. 5850, pp. 810–814.

Springer, Heidelberg (2009)

## Practical Issues with Formal Specifications Lessons Learned from an Industrial Case Study

Michael Altenhofen and Achim D. Brucker

SAP Research, Vincenz-Priessnitz-Str. 1, 76131 Karlsruhe, Germany {michael.altenhofen,achim.brucker}@sap.com

**Abstract.** Many software companies still seem to be reluctant to use formal specifications in their development processes. Nevertheless, the trend towards implementing critical business applications in distributed environments makes such applications an attractive target for formal methods. Additionally, the rising complexity also increases the willingness of the development teams to apply formal techniques.

In this paper, we report on our experiences in formally specifying several core components of one of our commercially available products. While writing the formal specification, we experienced several issues that had a noticeable consequences on our work. While most of these issues can be attributed to the specific method and tools we have used, we do consider some of the problems as more general, impeding the practical application of formal methods, especially by non-experts, in large scale industrial development.

**Keywords:** ASM, industrial case study, formal specification.

## 1 Introduction

In this paper, we report on experiences we made with writing a formal specification for certain aspects of an application that had been designed and built by one of our product groups. Given the actual time and resource constraints, we did not attempt to write a full-fledged specification that would allow us to (semi-)automatically prove system properties, but rather opted for an *executable* specification that would help us gaining further insights into the behavior of the system via proper simulation runs. This both seemed feasible and desirable, especially since the target application has to operate in a cluster environment where testing and debugging is notoriously difficult.

Based on the experiences we had made in previous research [4], we decided to use abstract state machines (ASMs) [7] for our formalization. In more detail, we created a set of specifications where the refined version could eventually be executed in CoreASM [13]. Since CoreASM comes with built-in support for *literate specifications* (similar to literate programming [15]), we wrote a document that contained extensive documentation explaining the specification. The final version of that document accumulated to roughly 130 pages containing approximately 3 200 lines of CoreASM specification (code).

S. Kowalewski and M. Roveri (Eds.): FMICS 2010, LNCS 6371, pp. 17–32, 2010.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2010

During the course of writing this specification we stumbled across several issues that had a noticeable influence on our work in general and the resulting specification in particular. While most of them can be clearly attributed to the method and tools we used, some of them seem to show more general problems that cannot be avoided by simply changing the underlying formal method. In this sense, we believe that our case study outlines several challenges that need to be tackled to foster the application of formal software specification methods in industrial product development environments.

The rest of the paper is organized as follows: In Sec. 2, we start with a short description of the application that we want to specify followed by an outline of the approach we have taken to eventually arrive at an executable formal specification. We then address the issues we have witnessed during the course of writing the specification in Sec. 3 and, finally, we conclude in Sec. 4.

## 2 Case Study: Distributed Object Management

In this section, we give an abstract description of the component we have specified formally. This component is part of an enterprise application that is built by one of our product development teams. Moreover, we briefly summarize the requirements that constrained the developers while designing and implementing the application.

## 2.1 The Problem: Consistent Distributed Object Management

In its essence, the application under consideration implements an event-conditionaction rule engine [17], where events are represented as object state changes, conditions are formulated as expressions on object attributes, and actions lead to further changes in object states. To efficiently compute the actions that need to be executed on events, the engine uses a modified version of the Rete algorithm [14] that propagates object state deltas through Rete networks. The actual implementation is multi-threaded, so access and updates to objects need to be coordinated among a potentially large set of threads running concurrently.

If the engine runs in a non-distributed setting, i.e., a single application instance, optimistic locking provides exclusive read/write access to the different objects. The engine, however, may be deployed in a cluster variant, where multiple application instances are running on different *server nodes*. In this case, we need to consistently coordinate object access across these engine instances.

Although the overall cluster size may be fixed, the system exhibits dynamic behavior in that application instances may start or stop during the overall lifetime of the cluster. Thus, we need mechanisms to deal with variations in the cluster topology, especially in the case of unexpected changes due to application or cluster node failures.

## 2.2 The Solution: Object Ownership and Cluster Failover Management

The implemented system does not use a distributed locking protocol, but rather tries to coordinate object access among different instances by maintaining meta information, called *object ownership*, in a shared data structure.

The solution needs to guarantee exclusive object ownership, i. e., at most one application instance may work with an object at any point in time. Thus, any application instance that wants to access or modify an object needs to successfully acquire ownership for that object from its current owner. As scalability is an important property of the overall system, the data structure that keeps track of ownership information is not maintained by a central instance, but managed in a distributed manner: Each application instance is responsible for managing ownership information for a fixed subset of all objects and is called authoritative indexer<sup>1</sup> for this set of objects. Fig. 1a illustrates a scenario with three application instances A, B, and C: instance A is authoritative indexer for objects 1 and 2, B for objects 3 and 4, and C for objects 5 and 6. Objects do not need to be owned by their authoritative indexer. In our example, object 1 is owned by instance B, object 6 by instance A, while all other objects are unused.

Instance B

Instance A

(a) Instance A is authoritative indexer for object 1 and 2, instance B for 3 and 4, and instance C for 5 and 6. Object 1 is owned by instance B, object 6 by instance A, while all other objects are unused.

(b) After instance C has left, instance A and B agree on a cluster of size 2, with A being authoritative indexer for objects 1 to 3, and instance B for objects 4 to 6. Instance B is informed that object 6 is owned by instance A.

Fig. 1. An example of a cluster distributed over several application instances

If an instance wants to acquire ownership for an object, it does so by always contacting the authoritative indexer of that object, not the current owner (if there is any). This approach has two advantages: first, the protocol requires at most two message exchanges; one from the requesting instance to the authoritative indexer and one from the authoritative indexer to the current owner. And

<sup>&</sup>lt;sup>1</sup> Indexer refers to the fact that objects have unique identifiers that serve as an index into this data structure.

second, each cluster instance is able to compute all authoritative indexer by itself once it has learned the cluster topology after a successful join of the cluster.

If cluster topology changes, ownership and authoritative indexer information needs to be redistributed among all cluster members. Ownership information is propagated via a restructuring protocol that, upon successful completion, is supposed to ensure two (mutually independent) properties:

- 1. all participating instances will agree on the same view (i. e., size and topology) of the cluster, which allows each instance to locally compute the same authoritative indexer for any object.

- 2. each instance will know current ownership for its authoritative set of objects.

To illustrate this, recall our example in Fig. 1a. If instance C leaves the cluster, instance A and B will eventually agree on a new cluster of size 2, with A being authoritative indexer for objects 1, 2, and 3, and instance B for objects 4, 5, and 6. Furthermore, instance B has to be informed that object 6 is owned by instance A. So far, that information had been maintained by the leaving instance C. Fig. 1b illustrates the resulting cluster topology.

While each instance maintains its local view of the cluster, there is one dedicated *master* instance providing the current view of the cluster to new instances joining the cluster. Using a dedicated master avoids (cluster) discovery protocols, but requires explicit means for *master election*, including recovery mechanisms in case the current master instance may leave the cluster unexpectedly due to an application or server node failure. In those cases, the remaining instances will compete against each other regarding mastership and the failing parties will try to join the cluster in the usual way.

## 2.3 Additional Implementation Constraints

Application development, especially in large software companies, rarely happens in isolation. Overall, it has to obey various requirements and boundary conditions imposed by application frameworks and platforms and programming models that are already used. These constraints often have a noticeable effect on the resulting solution architecture. In this section, we briefly review those aspects that also had a significant impact on our formal specification work.

Avoid additional functionality by reusing existing frameworks. Rather than building dedicated functionality into the runtime environment, the development team was urged to implement functionality by reuse existing software frameworks and components as much as possible. While it is, e.g., desirable to have a central facility for storing cluster meta data, like information on the current cluster topology or on the current master instance, much like [11], the given cluster implementation does not foresee such mechanisms. Therefore, the team opted for *named* communication channels implemented using the Java Naming and Directory Interface (JNDI).

Minimize Central Knowledge while Avoiding Redundancy. Centralized knowledge requires additional synchronization among the cluster participants and increases the communication overhead among them. Furthermore, any form of centralized knowledge introduces bottlenecks and threatens system availability should the central instance stop working properly. A common practice to increase system availability is redundancy (e. g., via replication [12]), but such a feature is not part of the underlying runtime platform. Therefore the decision was made to solely rely on local meta information (i. e., object ownership) per instance which needs to be synchronized whenever the cluster topology changes (which is expected to happen rarely).

Global Synchronization via Locks. Whenever an operation requires synchronization among the instances in a cluster, the initiating party needs to enforce that by acquiring a global lock maintained by a central lock server (i. e., a central infrastructure component). Master election is an example for such an operation. In fact, there is no real election going on and no elaborated agreement protocol is used; instead, being able to become the master is just bound to the ability to acquire a global, exclusive master lock from the central lock server.

Synchronous Mode of Operation. Although the platform provides different means of communication for application instances running on a cluster, any protocol-related communication is implemented as synchronous remote method invocation (RMI) calls since that required less changes in the code base when moving from a stand-alone to a cluster-enabled version.

Continuous Operation during Restructuring. Obviously, the restructuring protocol for updating meta information on object ownership is one of the most critical parts of the overall solution. A defensive approach would probably try to block any other interfering operations (like object requests) during cluster restructuring until the system has reached a stable state again. But overall performance had been given higher priority leading to a significantly more complicated restructuring protocol.

#### 2.4 Formal Specification

Ideally, we would have started with that formal specification, proven its correctness, and then iteratively refined it into executable code. Unfortunately, the real project settings were different and the development team had already designed and implemented a first version. Given that, we opted for a rather practical approach: our goal was to reverse-engineer the implementation into an executable specification that would allow us to simulate the system behavior in enough detail to detect any discrepancies between the desired and the implemented behavior. The initial plan was to focus on robustness of the protocol against communication failures. During our work, we followed a two-staged approach:

| Module                                   | Lines | Rules | Functions |

|------------------------------------------|-------|-------|-----------|

| Control ASM States                       | 50    | 0     | 1         |

| Cluster Master                           | 161   | 12    | 10        |

| Protocol Messages                        | 138   | 0     | 25        |

| Cluster Membership and Object Management | 1796  | 114   | 159       |

| Object Requests                          | 128   | 10    | 3         |

| Cluster Environment (Notification)       | 328   | 19    | 31        |

| Lock Management                          | 141   | 7     | 19        |

| Message Passing                          | 362   | 12    | 56        |

| Control Flow                             | 88    | 10    | 5         |

| Control State Handling                   | 63    | 5     | 9         |

| Total                                    | 3255  | 189   | 318       |

Table 1. An overview of the modules of the ASM specification

- 1. We started with a high-level abstract specification on paper to capture the essence of the functional features. This abstract specification was used as our primary communication and discussion medium with the development team to clarify our understanding of the overall system architecture and behavior and to discuss remaining open issues.

- 2. Once that abstract specification had reached a critical mass, we began to manually refine it towards an executable specification. After that, we updated both versions in parallel while trying to keep the overall structure and naming conventions aligned. Although this does by no means replace any sort of formal proof of the correctness of our refinement, it eventually helped us correcting errors in the abstract specification that surfaced through simulation runs of the executable specification.

Given the dynamic nature of the application, we decided to model the system as an asynchronous multi-agent ASM. With this, we came fairly close to the implementation where the parallelism induced by multiple Java threads was mapped to a set of agents with dedicated functionality. As a positive side-effect, this also led to a more modular specification.

Within a time-period of six months, we spent 80 person days to write a multiagent CoreASM specification that eventually consists of ten modules. Tab. 1 provides some details on the complexity of those modules. Out of these ten modules, the first four resemble the basic functionality outlined in Sec. 2.2. The fifth module, Object Requests, has been added to trigger random object access requests and thus simulate updates on ownership information. The next three modules provide functionality available via application frameworks (see Sec. 2.3), while the last two have been introduced to provide "syntactical sugar" when it comes to specifying complex control state machines. As the numbers show, we ended up with roughly 20% additional effort not providing core functionality, but is required to realistically model the implemented system behavior.

| Agent                    | Control States |

|--------------------------|----------------|

| Object Requester         | 8              |

| Object Request Processor | 5              |

| Node Failure Handling    | 22             |

| Meta Data Management     | 15             |

| Joining a Cluster        | 22             |

| Leaving a Cluster        | 24             |

Table 2. The different agents per node and their number of control states

For each cluster node, we have six agents performing different tasks in the overall protocol and each agent is modeled as a control state ASM (see Tab. 2). Since some of the control states are shared between these agents, the overall number of distinct states is 79.

Specification 1.1 presents invariants (in CoreASM notation) which must hold whenever a cluster is considered in a stable state, i. e., no nodes are in the process of joining or leaving the cluster: As the names imply, we want to assert that, at any point in time, object ownership information is "in sync" and "valid" across the cluster. Synchronized information requires that, for each object, its authoritative indexer and its current owner share that view. Ownership information is considered valid if the current owner is still a member of the current cluster.

```

derived IndicesInSync =

forall node in RunningNodes() holds IndexInSync(node)

derived IndicesAreValid =

forall node in RunningNodes() holds IndexIsValid(node)

derived IndexInSync(node) =

forall oid in [1..OID_MAX] holds SlotInSync(node, oid)

derived SlotInSync(node, oid) =

node = authIndexer(oid, node) implies

OWNER(OWNER(node, oid), oid) = OWNER(node, oid)

derived IndexIsValid(node) =

forall oid in [1..OID_MAX] holds SlotIsValid(node, oid)

derived SlotIsValid(node, oid) =

node = authIndexer(oid, node) implies

OWNER(node, oid) memberof RunningNodes()

```

Specification 1.1. Cluster Protocol Invariants

#### 2.5 Simulation Results

Given the specification above, a rough estimate shows that the state space required by a explicit state model checker is the range of  $10^{50}$ . Thus, we rather went for simulating dedicated scenarios, instead explicit brute-force model checking.

As with any other distributed coordination protocol, it soon became clear that we needed to simulate protocol runs for exceptional cases, especially situations where nodes leave the cluster unintentionally. When we started our work, we thought we would need to spend most of our efforts into simulating message transmission errors. But after several talks with the development team it turned out that the system takes a fairly defensive approach for dealing with such errors: most of the time, a message transmission failure will lead to a node restart. Thus, we decided to focus on exploring the alternative paths with regard to cluster topology changes and failover handling.

As it turned out, the modularity of the specification came in very handy and we were able to factor out parts of the overall protocol complexity, like, e.g., object request handling. With this simplifications, we eventually ended up with a streamlined simulation scenario that revealed a bug in the initial implementation, not yet discovered by any standard testing procedures: While investigating the failover handling during changes of the cluster topology, we realized that the original failover protocol was based upon a faulty assumption, namely that notifications in the case of failure would be sent *immediately after* a node failure. As this notification is sent by the runtime environment and, thus, not controlled by the application, one can easily think of scenarios where this is not true. Just assume that the notification is delayed while a new node is starting up in parallel during that delay. Then, that node will become the master of a new cluster that would just consist of that one node. If the delayed notification is then passed on to the remaining nodes from the old cluster, they will try to become master, will all fail, and thus do nothing, assuming that the (unknown) winner will perform the outstanding restructuring. Since the new master is not aware of the old cluster, no repair will happen and we will end up with two independent clusters operating in parallel.

This undesired behavior can be reliably reproduced with the following abbreviated simulation scenario.<sup>2</sup> We start by setting up a cluster with two nodes. Furthermore, we specify a distinct id for a third node that will be started at a later stage and will become the new master of the new cluster.

```

if (scenarioPhase = 0) then {

nodeList = ["N1", "N2"]

newMasterNode = "N3"

scenarioPhase = 1

}

```

<sup>&</sup>lt;sup>2</sup> We have omitted some variable and rule declarations. The overall simulation script is 89 lines long.

Once these nodes are running, we know that the cluster has reached a stable state. We now disable node failure detection, by suspending the corresponding agents.

```

if (scenarioPhase = 1) then {

if (AllNodesRunning()) then {

SuspendNodeFailureHandlers()

scenarioPhase := 2

clusterIsStable := true

}

}

```

After failure detection has been disabled, we forcefully shutdown the current master node.

```

if (scenarioPhase = 2) then {

killedMaster := MasterNode()

remove NodeID(MasterNode()) from nodeList

SignalNodeShutdown(MasterNode(), true)

scenarioPhase := 3

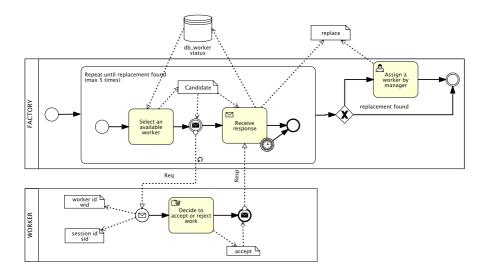

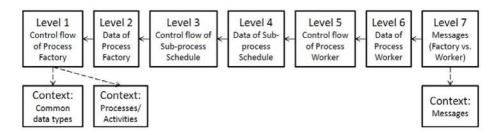

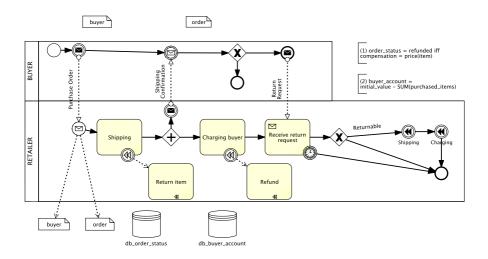

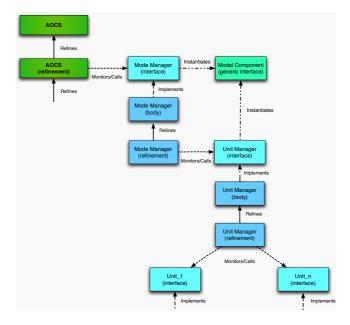

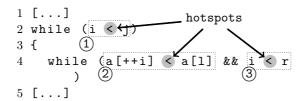

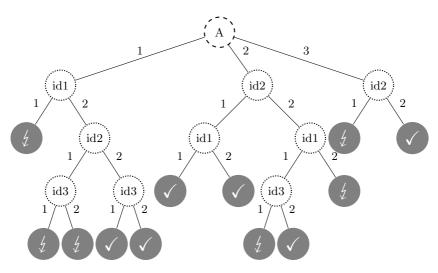

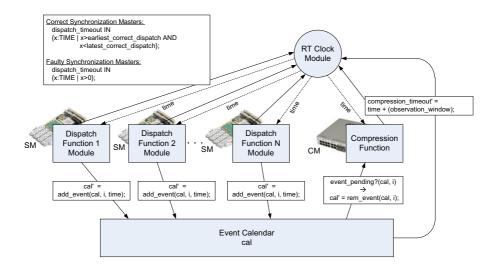

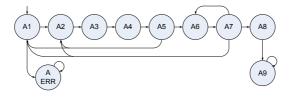

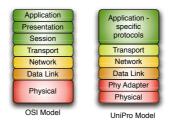

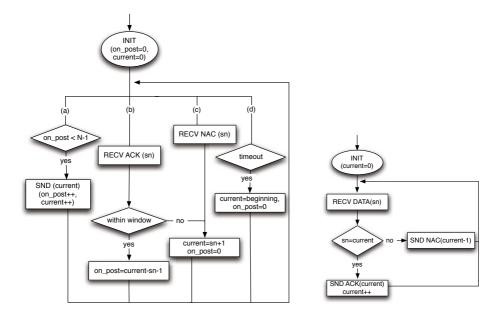

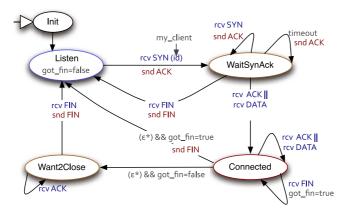

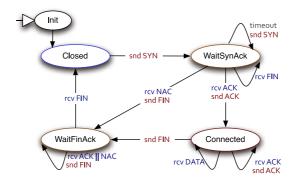

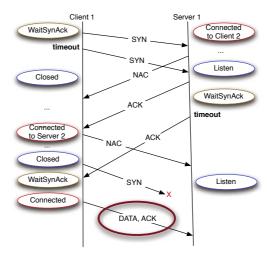

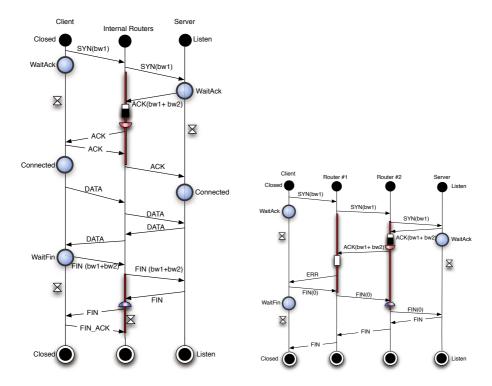

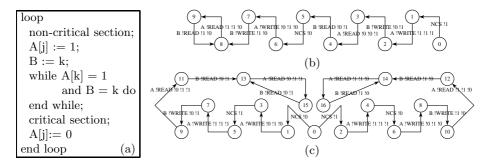

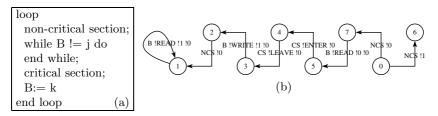

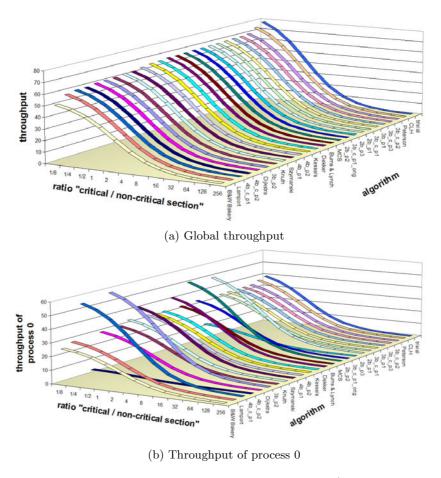

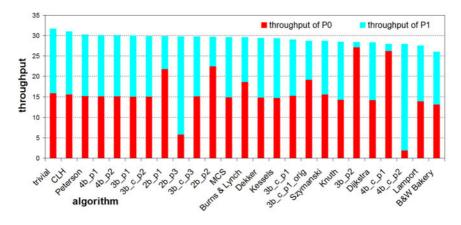

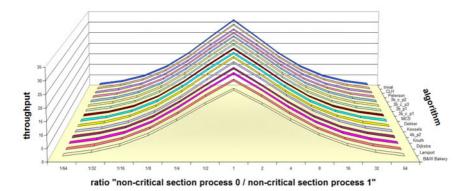

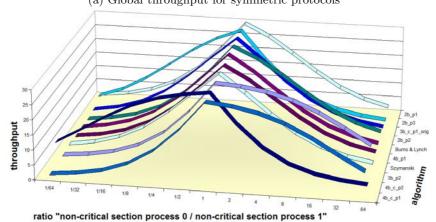

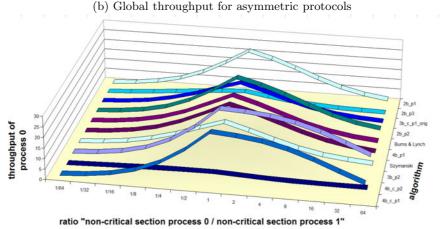

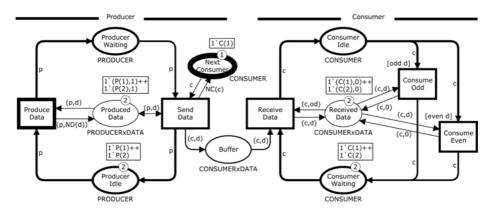

clusterIsStable := false