Gwen Salaün

Bernhard Schätz (Eds.)

LNCS 6959

# Formal Methods for Industrial Critical Systems

16th International Workshop, FMICS 2011

Trento, Italy, August 2011

Proceedings

*Commenced Publication in 1973*

Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

## Editorial Board

David Hutchison

*Lancaster University, UK*

Takeo Kanade

*Carnegie Mellon University, Pittsburgh, PA, USA*

Josef Kittler

*University of Surrey, Guildford, UK*

Jon M. Kleinberg

*Cornell University, Ithaca, NY, USA*

Alfred Kobsa

*University of California, Irvine, CA, USA*

Friedemann Mattern

*ETH Zurich, Switzerland*

John C. Mitchell

*Stanford University, CA, USA*

Moni Naor

*Weizmann Institute of Science, Rehovot, Israel*

Oscar Nierstrasz

*University of Bern, Switzerland*

C. Pandu Rangan

*Indian Institute of Technology, Madras, India*

Bernhard Steffen

*TU Dortmund University, Germany*

Madhu Sudan

*Microsoft Research, Cambridge, MA, USA*

Demetri Terzopoulos

*University of California, Los Angeles, CA, USA*

Doug Tygar

*University of California, Berkeley, CA, USA*

Gerhard Weikum

*Max Planck Institute for Informatics, Saarbruecken, Germany*

Gwen Salaün Bernhard Schätz (Eds.)

# Formal Methods for Industrial Critical Systems

16th International Workshop, FMICS 2011

Trento, Italy, August 29-30, 2011

Proceedings

## Volume Editors

Gwen Salaün

Grenoble INP - INRIA - LIG

Montbonnot Saint-Martin, France

E-mail: gwen.salaun@inria.fr

Bernhard Schätz

fortiss GmbH

München, Germany

E-mail: schaetz@fortiss.org

ISSN 0302-9743 e-ISSN 1611-3349

ISBN 978-3-642-24430-8 e-ISBN 978-3-642-24431-5

DOI 10.1007/978-3-642-24431-5

Springer Heidelberg Dordrecht London New York

Library of Congress Control Number: 2011936880

CR Subject Classification (1998): D.2.4, D.2, D.3, C.3, C.2.4, F.3, I.6

LNCS Sublibrary: SL 2 – Programming and Software Engineering

© Springer-Verlag Berlin Heidelberg 2011

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

The use of general descriptive names, registered names, trademarks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

*Typesetting:* Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India

Printed on acid-free paper

Springer is part of Springer Science+Business Media ([www.springer.com](http://www.springer.com))

# Preface

This volume contains the papers presented at FMICS 2011, the 16th International Workshop on Formal Methods for Industrial Critical Systems, taking place August 29–30, 2011, in Trento, Italy. Previous workshops of the ERCIM Working Group on Formal Methods for Industrial Critical Systems were held in Oxford (March 1996), Cesena (July 1997), Amsterdam (May 1998), Trento (July 1999), Berlin (April 2000), Paris (July 2001), Malaga (July 2002), Trondheim (June 2003), Linz (September 2004), Lisbon (September 2005), Bonn (August 2006), Berlin (July 2007), L’Aquila (September 2008), Eindhoven (November 2009), and Antwerp (September 2010). The FMICS 2011 workshop was co-located with the 19th IEEE International Requirements Engineering Conference (RE 2011).

The aim of the FMICS workshop series is to provide a forum for researchers who are interested in the development and application of formal methods in industry. In particular, these workshops bring together scientists and engineers who are active in the area of formal methods and are interested in exchanging their experiences in the industrial usage of these methods. These workshops also strive to promote research and development for the improvement of formal methods and tools for industrial applications.

Thus, topics of interest for FMICS 2011 include, but are not limited to:

- Design, specification, code generation and testing based on formal methods

- Methods, techniques and tools to support automated analysis, certification, debugging, learning, optimization and transformation of complex, distributed, real-time systems and embedded systems

- Verification and validation methods that address shortcomings of existing methods with respect to their industrial applicability (e.g., scalability and usability issues)

- Tools for the development of formal design descriptions

- Case studies and experience reports on industrial applications of formal methods, focusing on lessons learned or identification of new research directions

- Impact of the adoption of formal methods on the development process and associated costs

- Application of formal methods in standardization and industrial forums

This year, we received 39 submissions. Papers underwent a rigorous review process, and received three or four review reports. After the review process, the international Program Committee of FMICS 2011 decided to select 16 papers for presentation during the workshop and inclusion in these proceedings. The workshop featured two invited talks by Leonardo de Moura (Microsoft Research, USA) and Joost-Pieter Katoen (RWTH Aachen University, Germany); this volume includes two extended abstracts written by our invited speakers.

Following a tradition established over the past few years, the European Association of Software Science and Technology (EASST) offered an award to the best FMICS paper. This year, the reviewers selected the contribution by Thomas Reinbacher, Joerg Brauer, Martin Horauer, Andreas Steininger and Stefan Kowalewski on “Past Time LTL Runtime Verification for Microcontroller Binary Code.” Further information about the FMICS working group and the next FMICS workshop can be found at: <http://www.inrialpes.fr/vasy/fmics>.

We would like to thank the local organizers Anna Perini and Angelo Susi (Fondazione Bruno Kessler - IRST, Trento, Italy) for taking care of all the local arrangements to host FMICS in Trento, the ERCIM FMICS working group Coordinator Alessandro Fantechi (Univ. degli Studi di Firenze and ISTI-CNR, Italy) for guiding us when necessary, Jan Olaf Blech (fortiss GmbH, Germany) for acting as Publicity Chair and coordinating the publication process, EasyChair for supporting the review process, Springer for taking over the publication, all the members of the Program Committee for their great work during the review process, the external reviewers for their participation during the review process of the submissions, all the authors for submitting papers to the workshop, and the authors who participate in the workshop in Trento. All these people contributed to the success of the 2011 edition of FMICS.

August 2011

Bernhard Schätz

Gwen Salaün

# Organization

## Program Committee

|                   |                                                       |

|-------------------|-------------------------------------------------------|

| María Alpuente    | UPV, Spain                                            |

| Jiri Barnat       | Masaryk University, Czech Republic                    |

| Josh Berdine      | Microsoft Research, Cambridge, UK                     |

| Jan Olaf Blech    | fortiss GmbH, Germany                                 |

| Rance Cleaveland  | University of Maryland, USA                           |

| Cindy Eisner      | IBM Haifa Research Laboratory, Israel                 |

| Wan Fokkink       | Vrije Universiteit Amsterdam, The Netherlands         |

| Stefania Gnesi    | ISTI-CNR, Italy                                       |

| Holger Hermanns   | Saarland University, Germany                          |

| Daniel Kaestner   | AbsInt GmbH, Germany                                  |

| Stefan Kowalewski | RWTH Aachen University, Germany                       |

| Daniel Kroening   | Computing Laboratory, Oxford University, UK           |

| Frederic Lang     | INRIA Rhône-Alpes / VASY, France                      |

| Kim G. Larsen     | Aalborg University, Denmark                           |

| Diego Latella     | ISTI-CNR, Pisa, Italy                                 |

| Timo Latvala      | Space Systems, Finland                                |

| Corina Pasareanu  | CMU/NASA Ames Research Center, USA                    |

| Charles Pecheur   | UC Louvain, France                                    |

| Ernesto Pimentel  | University of Malaga, Spain                           |

| Marco Roveri      | FBK-irst, Italy                                       |

| John Rushby       | SRI International, USA                                |

| Gwen Salaün       | Grenoble INP - INRIA - LIG, France                    |

| Thomas Santen     | European Microsoft Innovation Center, Aachen, Germany |

| Bernhard Schätz   | fortiss GmbH, Germany                                 |

| Marjan Sirjani    | Reykjavik University, Iceland                         |

| Jaco Van De Pol   | University of Twente, The Netherlands                 |

| Helmut Veith      | TU Wien, Austria                                      |

## Additional Reviewers

|                    |                       |

|--------------------|-----------------------|

| Biallas, Sebastian | Crouzen, Pepijn       |

| Blom, Stefan       | Dražan, Sven          |

| Bortolussi, Luca   | Dräger, Klaus         |

| Bozzano, Marco     | Eisentraut, Christian |

| Brauer, Jörg       | Escobar, Santiago     |

| Bulychev, Peter    | Fantechi, Alessandro  |

| Ceska, Milan       | Ferrari, Alessio      |

## VIII Organization

Haller, Leopold

Hartmanns, Arnd

Hatefiardakani, Hassan

He, Nannan

Heckmann, Reinhold

Ilic, Dubravka

Kant, Gijs

Ketema, Jeroen

Khakpour, Narges

Khosravi, Ramtin

Konnov, Igor

Loreti, Michele

Mateescu, Radu

Mazzanti, Franco

Mousavi, Mohammadreza

Mover, Sergio

Nimal, Vincent

Olsen, Petur

Ouederni, Meriem

Panizo, Laura

Pfaller, Christian

Poll, Erik

Reinbacher, Thomas

Romero, Daniel

Sabouri, Hamideh

Sanan, David

Schuppan, Viktor

Serwe, Wendelin

Steiner, Wilfried

Tautschnig, Michael

Ter Beek, Maurice H.

Timmer, Mark

Titolo, Laura

Tonetta, Stefano

Trachtenherz, David

Tumova, Jana

Varpaaniemi, Kimmo

Villanueva, Alicia

Voss, Sebastian

Zuleger, Florian

# Table of Contents

|                                                                                                                               |     |

|-------------------------------------------------------------------------------------------------------------------------------|-----|

| Towards Trustworthy Aerospace Systems: An Experience Report .....                                                             | 1   |

| <i>Joost-Pieter Katoen</i>                                                                                                    |     |

| Satisfiability at Microsoft .....                                                                                             | 5   |

| <i>Leonardo de Moura</i>                                                                                                      |     |

| Lightweight Verification of a Multi-Task Threaded Server: A Case Study with the Plural Tool .....                             | 6   |

| <i>Néstor Cataño and Ijaz Ahmed</i>                                                                                           |     |

| Runtime Verification of Typical Requirements for a Space Critical SoC Platform .....                                          | 21  |

| <i>Luca Ferro, Laurence Pierre, Zeineb Bel Hadj Amor, Jérôme Lachaize, and Vincent Leftz</i>                                  |     |

| Past Time LTL Runtime Verification for Microcontroller Binary Code .....                                                      | 37  |

| <i>Thomas Reinbacher, Jörg Brauer, Martin Horauer, Andreas Steininger, and Stefan Kowalewski</i>                              |     |

| A SAT-Based Approach for the Construction of Reusable Control System Components .....                                         | 52  |

| <i>Daniel Côté, Benoît Fraikin, Marc Frappier, and Richard St-Denis</i>                                                       |     |

| Formal Safety Analysis in Industrial Practice .....                                                                           | 68  |

| <i>Ilyas Daskaya, Michaela Huhn, and Stefan Milius</i>                                                                        |     |

| Structural Test Coverage Criteria for Integration Testing of LUSTRE/SCADE Programs .....                                      | 85  |

| <i>Virginia Papailiopoulos, Ajitha Rajan, and Ioannis Parassis</i>                                                            |     |

| Formal Analysis of a Triplex Sensor Voter in an Industrial Context .....                                                      | 102 |

| <i>Michael Dierkes</i>                                                                                                        |     |

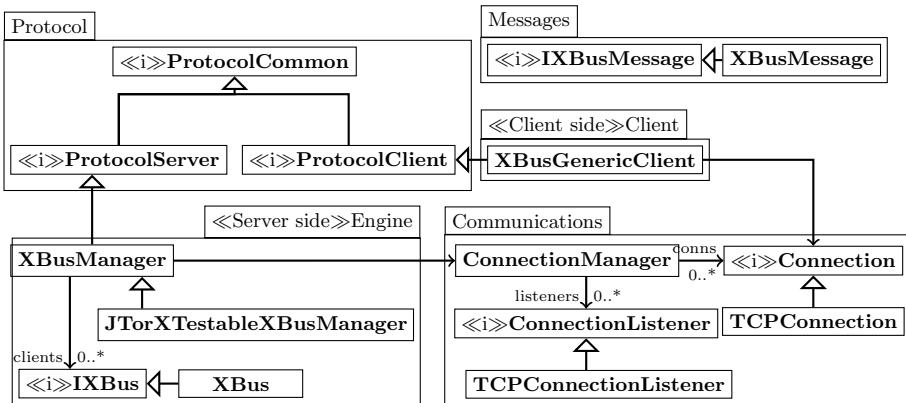

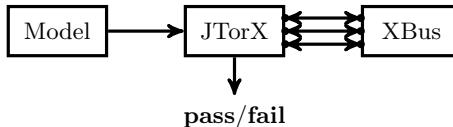

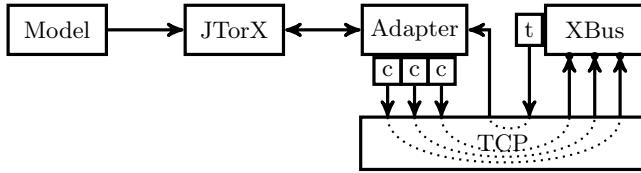

| Experiences with Formal Engineering: Model-Based Specification, Implementation and Testing of a Software Bus at Neopost ..... | 117 |

| <i>Marten Sijtema, Mariëlle I.A. Stoelinga, Axel Belinfante, and Lawrence Marinelli</i>                                       |     |

| Symbolic Power Analysis of Cell Libraries .....                                                                               | 134 |

| <i>Matthias Raffelsieper and MohammadReza Mousavi</i>                                                                         |     |

|                                                                                                             |            |

|-------------------------------------------------------------------------------------------------------------|------------|

| An Automated Semantic-Based Approach for Creating Tasks from Matlab Simulink Models .....                   | 149        |

| <i>Matthias Büker, Werner Damm, Günter Ehmen, and Ingo Stierand</i>                                         |            |

| Performability Measure Specification: Combining CSRL and MSL .....                                          | 165        |

| <i>Alessandro Aldini, Marco Bernardo, and Jeremy Sproston</i>                                               |            |

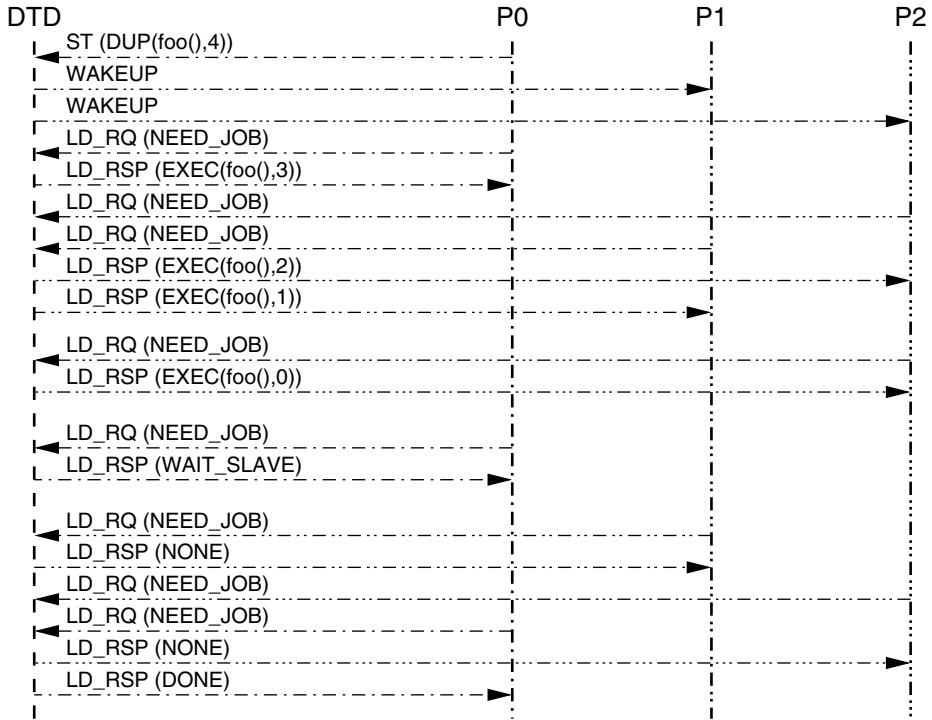

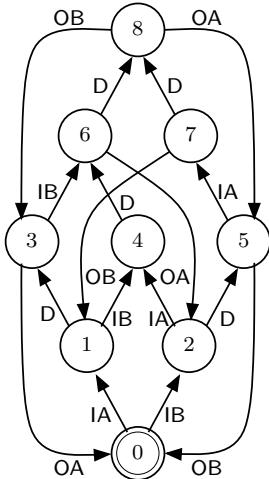

| Model Checking and Co-simulation of a Dynamic Task Dispatcher Circuit Using CADP .....                      | 180        |

| <i>Etienne Lantreibecq and Wendelin Serwe</i>                                                               |            |

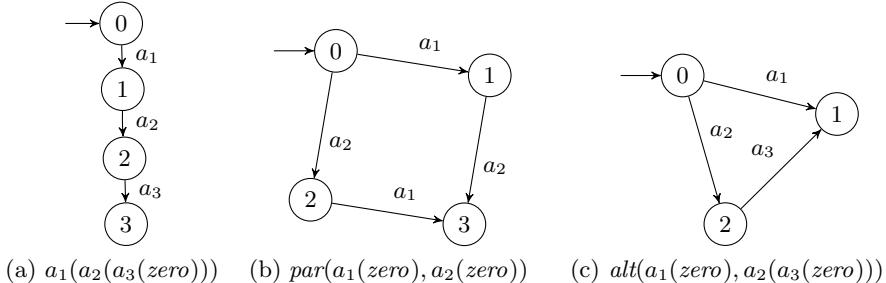

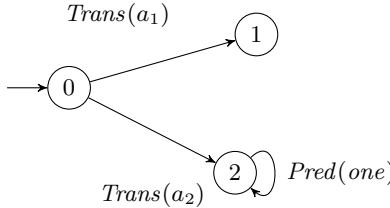

| Transforming SOS Specifications to Linear Processes .....                                                   | 196        |

| <i>Frank P.M. Stappers, Michel A. Reniers, and Sven Weber</i>                                               |            |

| Formal Verification of Real-Time Data Processing of the LHC Beam Loss Monitoring System: A Case Study ..... | 212        |

| <i>Naghmeh Ghafari, Ramana Kumar, Jeff Joyce, Bernd Dehning, and Christos Zamantzas</i>                     |            |

| Hierarchical Modeling and Formal Verification. An Industrial Case Study Using Reo and Vereofy .....         | 228        |

| <i>Joachim Klein, Sascha Klüppelholz, Andries Stam, and Christel Baier</i>                                  |            |

| Modeling and Verifying Timed Compensable Workflows and an Application to Health Care .....                  | 244        |

| <i>Ahmed Shah Mashiyat, Fazole Rabbi, and Wendy MacCaull</i>                                                |            |

| <b>Author Index .....</b>                                                                                   | <b>261</b> |

# Towards Trustworthy Aerospace Systems: An Experience Report

Joost-Pieter Katoen

RWTH Aachen University, Software Modeling and Verification Group, Germany

## 1 Introduction

Building modern aerospace systems is highly demanding. They should be extremely dependable. They must offer service without interruption (i.e., without failure) for a very long time — typically years or decades. Whereas “five nines” dependability, i.e., a 99.999 % availability, is satisfactory for most safety-critical systems, for on-board systems it is not. Faults are costly and may severely damage reputations. Dramatic examples are known. Fatal defects in the control software of the Ariane-5 rocket and the Mars Pathfinder have led to headlines in newspapers all over the world. Rigorous design support and analysis techniques are called for. Bugs must be found as early as possible in the design process while performance and reliability guarantees need to be checked whenever possible. The effect of fault diagnosis, isolation and recovery must be quantifiable.

Tailored effective techniques exist for specific system-level aspects. Peer reviewing and extensive testing find most of the software bugs, performance is checked using queueing networks or simulation, and hardware safety levels are analysed using an profiled Failure Modes and Effects Analysis (FMEA) approach. Fine. But how is the consistency between the analysis results ensured? What is the relevance of a zero- bug confirmation if its analysis is based on a system view that ignores critical performance bottlenecks? There is a clear need for an integrated, coherent approach! This is easier said than done: the inherent heterogeneous character of on-board systems involving software, sensors, actuators, hydraulics, electrical components, etc., each with its own specific development approach, severely complicates this.

## 2 Modeling Using an AADL Dialect

About three years ago we took up this grand challenge. Within the ESA-funded COMPASS (CORrectness, Modeling and Performance of Aerospace SyStems) project, an overarching model-based approach has been developed. The key is to model on-board systems at an adequate level of abstraction using a general-purpose modeling and specification formalism based on AADL (Architecture Analysis & Design Language) as standardised by SAE International. This enables engineers to use an industry-standard, textual and graphical notation with precise semantics to model system designs, including both hardware as well as software components. Ambiguities about the meaning of designs are abandoned. System aspects that can be modeled are, amongst others,

- (timed) hardware operations, specified on the level of processors, buses, etc.,

- software operations, supporting concepts such as processes and threads,

- hybrid aspects, i.e., continuous, real-valued variables with (linear) time-dependent dynamics, and

- faults with probabilistic failure rates and their propagation between components.

A complete system specification describes three parts: (1) nominal behavior, (2) error behavior, and (3) a fault injection—how does the error behavior influence the system’s nominal behavior? Systems are described in a component-based manner such that the structure of system models strongly resembles the real system’s structure. A detailed description of the language and its formal semantics can be found in [2].

### 3 Formal Verification

This coherent and multi-disciplinary modeling approach is complemented by a rich palette of analysis techniques. The richness of the AADL dialect gives the power to specify and generate a single system model that can be analysed for multiple qualities: reliability, availability, safety, performance, and their mixture. All analysis outcomes are related to the same system’s perspective, thus ensuring compatibility. First and foremost, mathematical techniques are used to enable an early integration of bug hunting in the design process. This reduces the time that is typically spent on a posteriori testing—in on-board systems, more time and effort is spent on verification than on construction!—and allows for early adaptations of the design. The true power of the applied techniques is their almost full automation: once a model and a property (e.g., can a system ever reach a state in which the system cannot progress?) are given, running the analysis is push-button technology. In case the property is violated, diagnostic feedback is provided in terms of a counterexample which is helpful to find the cause of the property refutation. These model-checking techniques [1] are based on a full state space exploration, and detect all kinds of bugs, in particular also those that are due to the intricacies of concurrency: multiple threads acting on shared data structures. This type of bugs are becoming increasingly frequent, as multi-threading grows at a staggering rate.

### 4 Requirements

Whereas academic tools rely on properties defined in mathematical logic, a language that is major obstacle for usage by design engineers, COMPASS uses specification patterns [5]. These patterns act as parametrised “templates” to the engineers and thus offer a comprehensible and easy-to-use framework for requirement specification. In order to ensure the quality of requirements, they can be validated independently of the system model. This includes property consistency (i.e., checking that requirements do not exclude each other), and property assertion (i.e., checking whether an assertion is a logical consequence of the requirements).

## 5 Safety

Analysing system safety and dependability is supported by key techniques such as (dynamic) fault tree analysis (FTA), (dynamic) Failure Modes and Effects Analysis (FMEA), fault tolerance evaluation, and criticality analysis [4]. System models can include a formal description of both the fault detection and isolation subsystems, and the recovery actions to be taken. Based on these models, tool facilities are provided to analyze the operational effectiveness of the FDIR (Fault Detection, Isolation and Recovery) measures, and to assess whether the observability of system parameters is sufficient to make failure situations diagnosable.

## 6 Toolset

All techniques and the full modeling approach are supported by the COMPASS toolset [3], developed in close cooperation with the Italian research institute Fondazione Bruno Kessler in Trento, and is freely downloadable for all ESA countries from the website [compass.informatik.rwth-aachen.de](http://compass.informatik.rwth-aachen.de). The tool is graphical, runs under Linux, and has an easy-to-use GUI.

## 7 Industrial Evaluation

The COMPASS approach and toolset was intensively tested on serious industrial cases by Thales Alenia Space in Cannes (France). These cases include thermal regulation in satellites and satellite mode management with its associated FDIR strategy. It was concluded that the modeling approach based on AADL provides sufficient expressiveness to model all hardware and software subsystems in satellite avionics. The hierarchical structure of specifications and the component-based paradigm enables the reuse of models. Also incremental modeling is very well supported. The RAMS analyses as provided by the toolset were found to be mature enough to be adopted by industry, and the corresponding results allowed the evaluation of design alternatives [6]. Current investigations indicate that the integrated COMPASS approach significantly reduces the time and cost for safety analysis compared to traditional on-board design processes.

**Acknowledgement.** We thank all co-workers in the COMPASS project for their contributions, in particular Thomas Noll and Viet Yen Nguyen (RWTH Aachen University), Marco Bozzano, Alessandro Cimatti and Marco Roveri (FBK, Trento), Xavier Olivé (Thales) and Yuri Yushstein (ESA). This research is funded by the European Space Agency via several grants.

## References

1. Baier, C., Katoen, J.-P.: Principles of Model Checking. MIT Press, Cambridge (2008)

2. Bozzano, M., Cimatti, A., Katoen, J.-P., Nguyen, V.Y., Noll, T., Roveri, M.: Safety, dependability, and performance analysis of extended AADL models. The Computer Journal (March 2010), doi:10.1093/com

3. Bozzano, M., Cimatti, A., Katoen, J.-P., Nguyen, V.Y., Noll, T., Roveri, M., Wimmer, R.: A model checker for AADL (tool presentation). In: Touili, T., Cook, B., Jackson, P. (eds.) CAV 2010. LNCS, vol. 6174, pp. 562–565. Springer, Heidelberg (2010)

4. Bozzano, M., Villafiorita, A.: Design and Safety Assessment of Critical Systems. CRC Press, Boca Raton (2010)

5. Grunske, L.: Specification patterns for probabilistic quality properties. In: Int. Conf. on Software Engineering (ICSE), pp. 31–40. ACM, New York (2008)

6. Yushstein, Y., Bozzano, M., Cimatti, A., Katoen, J.-P., Nguyen, V.Y., Noll, T., Olivé, X., Roveri, M.: System-software co-engineering: Dependability and safety perspective. In: 4th IEEE International Conference on Space Mission Challenges in Information Technology (SMC-IT). IEEE CS Press, Los Alamitos (2011)

# Satisfiability at Microsoft

Leonardo de Moura

Microsoft Research, One Microsoft Way, Redmond, WA 98052, USA

[leonardo@microsoft.com](mailto:leonardo@microsoft.com)

**Abstract.** Constraint satisfaction problems arise in many diverse areas including software and hardware verification, type inference, static program analysis, test-case generation, scheduling, planning and graph problems. These areas share a common trait, they include a core component using logical formulas for describing states and transformations between them. The most well-known constraint satisfaction problem is *propositional satisfiability*, SAT, where the goal is to decide whether a formula over Boolean variables, formed using logical connectives can be made *true* by choosing *true/false* values for its variables. Some problems are more naturally described using richer languages, such as arithmetic. A supporting *theory* (of arithmetic) is then required to capture the meaning of these formulas. Solvers for such formulations are commonly called *Satisfiability Modulo Theories* (SMT) solvers.

Modern software analysis and model-based tools are increasingly complex and multi-faceted software systems. However, at their core is invariably a component using logical formulas for describing states and transformations between system states. In a nutshell, symbolic logic is the *calculus* of computation. The state-of-the art SMT solver, Z3, developed at Microsoft Research, can be used to check the satisfiability of logical formulas over one or more theories. SMT solvers offer a compelling match for software tools, since several common software constructs map directly into supported theories.

SMT solvers have been the focus of increased recent attention thanks to technological advances and an increasing number of applications. The Z3 solver from Microsoft Research is particularly prolific both concerning applications and technological advances. We describe several of the applications of Z3 within Microsoft, some are included as critical components in tools shipped with Windows 7, others are used internally and yet more are available for academic research. Z3 ranks as the premier SMT solver available today.

# Lightweight Verification of a Multi-Task Threaded Server: A Case Study With The Plural Tool\*

Néstor Cataño and Ijaz Ahmed

Carnegie Mellon University - Portugal, Madeira ITI

Campus da Penteada, Funchal, Portugal

`{nestor.catano,ijaz.ahmed}@m-iti.org`

**Abstract.** In this case study, we used the Plural tool to verify the design of a commercial multi-task threaded application (MTTS) implemented by Novabase, which has been used for massively parallelising computational tasks. The effort undertaken in this case study has revealed several issues related with the design of the MTTS, with programming practices used in its implementation, and with domain specific properties of the MTTS. This case study has also provided insight on how the analysis done by the Plural tool can be improved. The Plural tool performs lightweight verification of Java programs. Plural specification language combines typestates and access permissions, backed by Linear Logic. The Plural specifications we wrote for the MTTS are based on its code, its informal documentation, sometimes embedded in the code, and our discussions with Novabase's engineers, who validated our understanding of the MTTS application.

**Keywords:** Concurrency, Formal Methods, Parallelism, The Plural Tool, Verification.

## 1 Introduction

Hardware engineers and chip manufacturers are currently developing even bigger multi-core processors to develop desktops that will be massively parallel within the next few years. To take advantage of this new parallel technology, computer scientists are working on the development of programming languages and programming paradigms that exploit the massively parallel power provided by the (future) hardware. As an example of this, the *Æminium* research project is working in the development of a platform [16] that allows programmers to write concurrent-by-default programs and that supports massive parallelism. *Æminium* platform is under development and its evolution has been greatly influenced by the Plural tool [14], its predecessor. Plural provides support to *typestates* and *access permissions*. Typestates define protocols on finite state

---

\* This work has been supported by the Portuguese Research Agency FCT through the CMU-Portugal program, R&D Project *Æminium*, CMU-PT/SE/0038/2008.

machines [17]. Access permissions are abstractions describing how objects are accessed. For instance, a **Unique** access permission describes the case when a sole reference to a particular object exists, and a **Shared** access permission models the case when an object is accessed by multiple references. Access permissions are inspired by Girard’s Linear Logic [11], hence, they can be used as part of specifications, and can be produced and consumed.

For this case study, we used the Plural tool for the specification and verification of a multi-task threaded server (MTTS), implemented by Novabase [13], which has extensively used for massively parallelising the processing of computational tasks. The MTTS has historically been a robust and reliable core application. The MTTS is part of several software applications used by Novabase’s clientele, e.g. it is used in the financial sector to parallelise the archiving and processing of documents. MTTS has been implemented in Java. It utilises queues to store tasks, which are executed by a pool of threads.

Our goals for the case study included verifying the design of a massively parallel application, determining how well the Plural tool works on a complex commercial application - what kinds of specifications and code can and cannot be analysed by Plural. This case study further allowed us to make a list of desirable properties and features the Plural tool (and  $\mathcal{A}$ eminium, its successor) must implement to become a more powerful and usable lightweight verification tool. The process of verifying MTTS with Plural revealed a series of issues related with good programming practises and with design decisions made in the implementation of the MTTS. These issues would not have been revealed otherwise, e.g. through direct code inspection. Furthermore, the specification we wrote can be used by Novabase to generate a collection of documents describing the behaviour of the MTTS, and the use of an automated tool like Plural increases our confidence on the correctness of the specifications. This documentation can be used to resolve differences between members of the quality assurance team of Novabase, their programmers, or any of those and Novabase’ clientele itself, regarding the expected behaviour of the MTTS. The Plural specifications we wrote for the MTTS are based on our understanding of the MTTS application, built from direct inspection of its code and from our discussions with Novabase’s engineers, who validated our understanding.

The rest of this paper is organised as follows. In the following, we present some related work. Section 2 introduces the specification language used by Plural (access permissions and typestates), and describes how verification is performed with the Plural tool. Section 3 presents the structure of the MTTS application. Section 4 presents the specification of the MTTS application and shows miscellaneous aspects of the verification of the MTTS with Plural. Section 4 includes a discussion on the limitations of the analysis performed by Plural and how we overcame these limitations. This discussion includes a list of desirable features regarding the analysis done by Plural. Section 5 discusses our current work on the implementation of some of these features.

**Related Work.** In previous work [8], we used JML to specify an electronic purse application written in the Java Card dialect of Java. JML is a behavioural interface specification language for Java [12]. Typestates can be regarded as JML abstract variables and, therefore, JML tools can be used to simulate the typestate verification of specifications. However, JML does not provide support for the reasoning about access permissions and JML’s support for concurrency is rather limited. The work presented here is more complex than the work in [8], as it involves reasoning on concurrency properties of a system.

The Plural group has conducted several case studies on the use of typestates to verify Java I/O stream libraries [3] and Java database libraries [4]. The case studies show that Plural can effectively be used to check violation of APIs protocols. The case study presented in this paper takes a further step in considering a large commercial application with about fifty Java classes.

In [10], Robert DeLine and Manuel Fähndrich use the Fugue protocol checker on a relatively large .Net web based application. Likewise Plural, Fugue provides support to typestate verification, however, it does not provide support to access permissions. In [9], the Vault programming language is used to describe resource management protocols. Protocols can specify that certain operations must be performed in a certain order and that certain operations must be performed before accessing a given data object. The technique has been used on the interface between the Windows kernel and its device drivers.

## 2 Preliminaries

### 2.1 Plural Specification Language

Plural specification language combines typestates and access permissions specifications. Typestates define protocols on finite state machines [17]. Access permissions are abstract definitions on the capability of a method to access a particular state [3,5]. Plural uses access permissions to keep track of the various references to a particular object, and to check the types of accesses these references have. Accesses can be reading and writing (modifying). Plural provides support to five types of access permissions, namely, **Unique**, **Share**, **Immutable**, **Full**, and **Pure**. Figure 1 presents a taxonomy of how different access permissions can coexist, e.g. **Full** access to a referenced object allows the existence of any other reference with **Pure** access to the same referenced object.

- **Unique(x).** It guarantees that reference **x** is the sole reference to the referenced object. No other reference exists, so **x** has exclusive reading and modifying (writing) access to the object.

- **Full(x).** It provides reference **x** with reading and modifying access to the referenced object. Additionally, it allows other references to the object (called aliases) to exist and to read from it, but not to modify it.

- **Share(x).** Its definition is similar to the definition of **Full(x)**, except that other references to the object can further modify it.

| This reference   | Other references                    |

|------------------|-------------------------------------|

| <b>Unique</b>    | $\emptyset$                         |

| <b>Full</b>      | <b>Pure</b>                         |

| <b>Share</b>     | <b>Share, Pure</b>                  |

| <b>Pure</b>      | <b>Full, Share, Pure, Immutable</b> |

| <b>Immutable</b> | <b>Pure, Immutable</b>              |

| Current permission<br>read/write | read-only        | Access through<br>other permission |

|----------------------------------|------------------|------------------------------------|

| <b>Unique</b>                    | -                | none                               |

| <b>Full</b>                      | <b>Immutable</b> | read-only                          |

| <b>Share</b>                     | <b>Pure</b>      | read/write                         |

**Fig. 1.** Simultaneous access permissions taxonomy [3]

- **Pure(x)**. It provides reference **x** with reading-only access to the referenced object. It further allows the existence of other references to the same object with read-only access or read-and-modify access.

- **Immutable(x)**. It provides **x** and any other existing reference to the same referenced object with non-modifying access (read-only) to the referenced object. An **Immutable** permission guarantees that all other existing references to the referenced object are also immutable permissions.

Access permissions are inspired by Girard’s Linear Logic [11], hence, they can be used, produced and consumed. In Plural, typestates are declared with the aid of the **@ClassStates** clause. Method specifications are written with the aid of the **@Perm** clause, composed of a “requires” part, describing the resources required by a method to be executed, and an “ensures” part, describing the resources generated after method execution. So, the Linear Logic formula  $P \multimap Q$  is written as **@Perm**(requires=“**P**”, ensures=“**Q**”). The semantics of the operator  $\otimes$  of Linear Logic, which denotes simultaneous occurrence of resources, is captured by the operator “\*”. **P** and **Q** above are specifications such as **Unique(x) in A** \* **Full(y) in B**, which requires (ensures) that reference “**x**” has **Unique** permission to its referenced object, which should be in state **A**, and simultaneously requires (ensures) that “**y**” has **Full** permission to its referenced object, which should be in state **B**. The semantics of the additive conjunction operator “&” of Linear Logic, which represents the alternate occurrence of resources, is captured by the use of a **@Cases** specification, the decision of which is made according to a required resource in one of its **@Perm** specifications. The additive disjunction operator  $\oplus$  of Linear Logic is modelled by the use of a **@Cases** specification, the decision of which is made according to an ensured resource by one of its **@Perm**.

Figure 2 illustrates an example of specification with Plural taken from the case study. Class **Task** models a generic processing task in the MTTS. The internal information about the task is stored in an object “**data**” of type **MttsTaskDataX**. We identify four possible typestates a task can be, namely, **Created**, **Ready**,

```

@ClassStates({

@State(name = "Created", inv = "data == null"),

@State(name = "Ready", inv = "data != null"),

@State(name = "Running", inv = "data != null"),

@State(name = "Finished", inv = "data == null")

})

public Task implements AbstractTask {

private MttsTaskDataX data;

@Perm(ensures = "Unique(this) in Created")

public Task() { ... }

@Perm(requires = "Full(this) in Created * #0 != null",

ensures = "Full(this) in Ready")

public void setData(MttsTaskDataX data) { ... }

@Perm(requires = "Full(this) in Ready",

ensures = "Full(this) in Finished")

public void execute() throws Exception { ... }

}

```

**Fig. 2.** Example of a specification for a generic task

**Running**, and **Finished**. The state **Created** is the initial state of any task. This uniqueness property is enforced by the class constructor. A task is in state **Ready** once it has been given some data to be run. It is in state **Running** when it is running, and it is in state **Finished** when it has been executed and the task data has been consumed. The constructor of class **Task** creates a **Unique** object that is initially in state **Created**. Method “**setData()**” requires **this** to have **Full** permission on its referenced object, which should be in state **Created**, and simultaneously requires that its first parameter is different than **null**. The operator “**\***” combines several specifications. Expression “**#i**” stands for the parameter number “**i+1**” of a method. Method “**execute()**” requires **this** to have **Full** permission and to be in state **Ready**, and ensures that **this** will have **Full** permission on its referenced object, which will be in state **Finished**. Additionally (not shown in this example), in Plural, the clause **@Cases** allows the annotation of several **@Perm** specifications for a method.

## 2.2 Checking Programs with Plural

Plural is a typestate specification and checker tool, implemented as a plug-in of Eclipse [14]. The Plural tool takes a Java program annotated with Plural specifications and checks whether the program complies with its specifications. Plural performs several types of program analysis, e.g. fractional analysis (influenced by Boyland’s work in [6]), hence, access permissions can be split in several more *relaxed* permissions and then joined back again to form more *restrictive* permissions. Plural has also a simple effects-analyser that checks if a particular method has side-effects, and an annotation analysis tool that checks whether annotations are well-formed.

Plural employs a *packing* and *unpacking* object mechanism that is used to transition objects into valid states in which invariants can be checked. Plural implementation of the packing and unpacking mechanism has been influenced

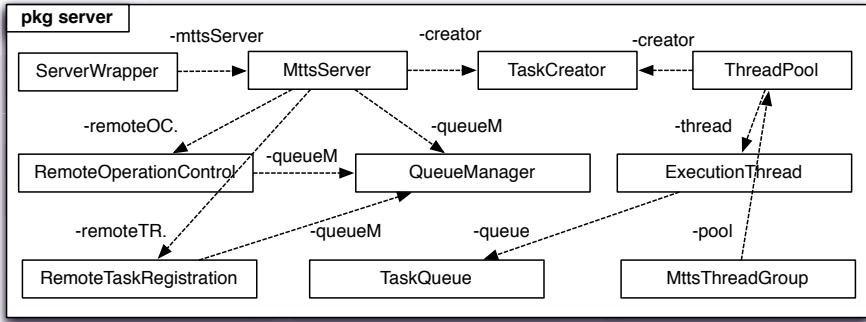

**Fig. 3.** The server package

by the work of M. Barnett and al. in [2]. Hence, Plural packs receiver objects to some state before methods are called. This ensures that objects are seen in consistent states during method calls.

### 3 General Outline of the MTTS Application

The MTTS is the core of a task distribution server that is used to run tasks over different execution threads. The core is used in the financial sector to process bank checks in parallel with time bound limits. MTTS' implementation is general in the sense that it makes no assumptions on the nature of the running tasks. The MTTS organises tasks through queues and schedules threads to execute the task queues. Tasks are stored in databases.

The MTTS is a typical client server application, which is divided into 3 main components, namely, TaskRegistration, RemoteOperationControl and QueueManager. MTTS' clients use the TaskRegistration component to register tasks. This component stores the registered tasks in a database. The QueueManager component implements some working threads that fetch and execute tasks. The RemoteOperationControl component is used to monitor and to control the progress of the tasks. Every queue implements a mutex manager algorithm to synchronise tasks.

**Implementation of the MTTS.** The MTTS is composed of three main packages, namely, mtts-api, il and server. The structure of the server Package is shown in Figure 3. The mtts-api package models tasks and queues. Class Task implements tasks and QueueInfo implements queues. Class IMutexImp in the il (intelligent lock) package implements a mutex algorithm to synchronise tasks, and class MutexManager creates and destroys locks. Lock status and statistics are implemented in classes IMutexStatus and IMutexStatistics respectively.

The server package is the main package of the MTTS application and uses features implemented by the other packages. The server package implements

code that fetches tasks from the database and distributes them through different threads. Class ServerWrapper runs the server as a system service and Class MttsServer implements the basic functionality to start and stop the server. Class TaskCreator and class QueueManager create tasks and manage queues respectively. Class RemoteTaskRegistration provides an interface to remotely register tasks and class RemoteOperationControl provides an interface to clients to remotely view the progress of tasks. Class ThreadPool keeps a list of class ExecutionThread objects that execute running threads. Class DBConnection implements the basic features to communicate with database.

## 4 Specification and Verification of MTTS

### 4.1 The General Specification Approach

The specification of the MTTS application is based on its informal documentation, sometimes embedded in the code as comments, and on our discussions with Novabase’s engineers. After our discussions with Novabase’s engineers took place, we wrote a technical report describing the architecture of the MTTS application [1]. The report was then validated by Novabase.

Since Plural performs a modular analysis of programs, we commenced writing specifications, starting from the most basic classes of the MTTS, e.g. classes that are inherited from or are used by other classes. Since the specification of more complex classes depends on the specification of the most basic ones, we provided basic classes with a sufficiently detailed specification. We specified the basic packages mtts-api and il first and specified package server last. Because Plural does not include a specification for Java standard classes, e.g. List and Map, we wrote specifications for these Java classes as well. We also wrote specifications for Java classes related with database interaction, e.g. Connection and DriverManager. In the following, we present and discuss some of the specifications of the three main packages of the MTTS and discuss miscellaneous aspects of the specification and verification of the MTTS application with Plural.

### 4.2 Miscellaneous Aspects of the Specification of the MTTS

**Processing Tasks.** Figure 2 presents an excerpt of the specification of class Task (see Section 2.1). There are some miscellaneous aspects about the specification of this class that are worthy to mention. Although we would like to distinguish typestates **Ready** and **Running**, their associated invariants are the same. In Plural, if an object is in state **Ready**, then “data” is different than **null**. However, the opposite direction is not necessarily **true**. If one wished to fully distinguish these two typestates then one could add conditions “isready” and “!isready” to their respective invariants. But then one would need to modify the source code of class Task by creating a boolean variable “ready” and to keep track of the value of this variable through the code of class Task. This is error-prone and we further wanted to keep the source code of the MTTS intact as much as possible.

The specification of class Task ensures that a task cannot be execute twice. Only the class constructor leaves a task in state **Created**. Only method “setData” transitions a task from **Created** to **Ready**. And a task needs to be in state **Ready** to be executed. The specification also ensures that “setData” must be called before “execute()”.

**Mutual Exclusion.** Method “acquire()” acquires a lock and method “release()” gives the lock up. Method “acquire()” is the only class method that transitions into typestate **Acq**, and method “release()” is the only class method that takes an object from typestate **Acq** into typestate **FStat**. These methods are defined in class IMutex. Mutual exclusion to a critical section is ensured by enclosing the code of the critical section between a call to method “acquire()” and a call to method “release()”. Hence, two different threads cannot execute a critical section simultaneously. If a first thread acquires a lock by successfully completing a call to “acquire()”, a second thread can only acquire the lock after the first thread has released it.

```

@Full( requires = “FStat” , ensures = “Acq” )

public abstract void acquire() { }

@Full( requires = “Acq” , ensures = “FStat” )

public abstract void release() { }

```

An object of type ExecutionThread (see below) is in state **FullMutex** if it has **Full** access permission to field “mutex” of type IMutex. Hence, mutual exclusion to a certain code (e.g. method “doErrorRecovery”) is attained by enclosing it between a call to “mutex.acquire()” and a call to “mutex.release()”.

```

@ClassStates( {

@State(name = “FullMutex” , inv = “Full(mutex) in FStat” ) ,

})

class ExecutionThread extends Thread {

private IMutex mutex;

@Perm( requires = “FullMutex” , ensures = “FullMutex” )

private void doErrorRecovery( Exception e ) {

try { mutex.acquire(); ... }

finally { ... mutex.release(); }

}

}

```

**Absence of Deadlocks.** The Plural specification provided to methods “acquire()” and “release()” ensures that if a thread has acquired a lock, then the thread needs to release the lock before another thread can acquire the lock. This is a source for deadlocks: one needs to check that an acquired lock is eventually released. Plural does not provide support to reachability analysis so we did not prove the absence of deadlocks in general, but only in particular settings, e.g. by direct code inspection. As an example of this, the code of method “doErrorRecovery” in class “ExecutionThread” below is enclosed between a call to “acquire()”

and a call to “release()”. This was often the case for methods in class “ExecutionThread”. Method “doErrorRecovery” uses a Java try-catch-finally statement to ensure that the “release()” method is always finally called regardless of the method termination status (normal or exceptional). Plural analysers take the semantics of the try-catch-finally Java statement into account.

**Destroying a Non-Released Lock.** Method `destroy(IMutex m)` in class `MutexManager` removes a mutex from the list of mutexes. However, destroying (removing) a mutex can lead the system to a deadlock (or to a state that might enable some abnormal behaviour) as the thread that acquired the lock will never be able to release the lock and so threads waiting for the thread to release the lock will await forever. To ensure that a mutex is not destroyed before it is first released, we added the specification **Full(#0) in NotAcq** to the “requires” part of method “destroy” (“#0” refers to the first parameter of the method, i.e. `m`). Therefore, Plural will generate an error for any code that calls method “destroy” with a mutex object “`m`” in a state other than **NotAcq**.

**Reentrant Mutexes.** According to the implementation and the documentation of the MTTS, although two different threads cannot acquire the same lock, a single thread can acquire the same lock several times. Class `IMutexImp` implements interface `IMutex`. It declares a thread field “`o`” that keeps track of the thread that owns the lock, and an integer variable “nesting” that keeps track of the number of times the owner thread has acquired the lock. From the implementation of class `IMutexImp`, it appears evident that “nesting” is 0 whenever object “`o`” is **null** (a class invariant property). We define a typestate **NestAcq** (acquired several times by the same thread) related to the invariant “`o != null * nesting > 1`” and use this typestate in the specification of all the methods of the class, e.g. “`acquire()`” and “`release()`”. However, Plural does not provide support to integer arithmetic. We then thought of modifying the code of class `IMutexImp` to declare and use a boolean variable “`nested`” to be **true** whenever “nesting” is greater than 1, and modifying the invariant associated to the typestate **NestAcq** to be “`o != null * nested==true`”. This approach however is error-prone: it requires us to set “`nested`” accordingly all through class `IMutexImp` whose code is large.

An additional problem related to the specification of reentrant mutexes has to do with the analysis performed by Plural. We describe this problem with the aid of the specification of the method “`release()`” below. This method requires the receiver object to be in state **NestAcq** that means “`nested`”  $\neq \text{false}$ . This indicates that if-statement in method “`release()`” can never be executed, and hence the receiver object remains in the state **NestAcq**. However, the Plural tool issues a warning saying that it cannot establish the post-typestate specification. This proves another limitation of the analysis performed by Plural. To determine that the if-statement is never executed, it is necessary to analyse the invariant property associated with the definition of the **NestAcq** typestate. The actual

implementation of Plural does not perform such data-flow analysis. Due to all these limitations in the analysis performed by Plural, the actual specification for class IMutexImp does not introduce a **NestAcq** typestate.

```

@Full(requires = "NestAcq", ensures = "NestAcq")

public void release() {

if(o != null && nested==false) { ... }

}

```

**Plural and Good Programming Practices.** Class ExecutionThread declares a boolean variable “terminate” that is used to determine whether the thread has finished its execution or not. The variable is not explicitly initialised in its declaration, yet according to the Java specification language its default value is **false**. Typestate **ThreadCreated** represents the state in which a thread has just been created. The constructor of class ExecutionThread does not set variable “terminate”. Despite the fact that the initial value of variable “terminate” is **false**, Plural issues an error for the execution of the constructor of class ExecutionThread. This error states that the object cannot be packed to typestate **ThreadCreated**.

Although this shows a bug in the Plural tool, we report it as a programming bad practice. Programmers should explicitly initialise variables to their intended value, thus avoiding relying on the underlying compiler or on external tools, e.g. external typestate analysers like Plural. In this sense, Plural can be used to enforce initialisation of class variables.

```

@ClassStates({

@State(name = "ThreadCreated", inv = "terminate==false"),

...

})

class ExecutionThread extends Thread {

private boolean terminate;

...

@Perm (ensures = "Unique(this) in ThreadCreated")

ExecutionThread(...) { ... }

...

}

```

**Specification of Standard Libraries.** The MTTS stores tasks and related information into a database. The DBConnection class of MTTS implements the basic features that support communication with databases. Plural does not furnish specification of standard Java classes such as Connection and DriverManager, so we needed to write specifications for these classes as well. The specification of these classes allowed us to prove that the MTTS adheres to general protocols of database interaction. For instance, we proved that a connection is always open whenever database operations such as fetching a task from the database and updating task information stored in the database are taking place.

Abstract class MttsConnection below presents part of the specification we wrote for class MttsConnection. Class MttsConnection defines a root typestate **Connection** with two sub-typestates **OpenConnection** and **ClosedConnection**, modelling an open and closed database connection respectively. According

to the Java specification language, method “open()” can be called on an object that is in state **OpenConnection**, and “close()” can be called on an object that is in state **ClosedConnection**. The specification of other standard libraries was conducted in a similar way. They were all specified in Java abstract classes.

```

@Refine({

@States(dim="Connection",

value={"OpenConnection", "ClosedConnection"})

})

public abstract class MttsConnection {

@Perm(ensures = "Unique(this) in OpenConnection")

MttsConnection() { }

@Full(value="Connection", ensures="OpenConnection")

public abstract void open() throws java.sql.SQLException;

@Full(value="Connection", ensures="ClosedConnection")

public abstract void close() throws java.sql.SQLException;

}

```

**Checking for Non-Nullness.** One of the most common properties to verify is the one restricting values to be different than **null**. For instance, method “setName” (see below) in class “MttsTaskDataX” restricts parameter “name” to be different than **null**. This parameter is used to set the internal name of the underlying task. Plural issues an error for any call to method “setName” with a parameter that cannot be proved to be different than **null**.

```

@Perm(requires = "#0 != null")

public void setName(String name) { ... }

```

**Starting and Shutting Down the MTTS Server.** Class MttsServer is the main class of the MTTS application. It implements methods “start()” and “stop()” to start and to shutdown the server. It declares three variables “OpControlRemote”, “TaskRegistrationRemote” and “queueManager” to manage the three major features of the server: control of remote operations, task registration, and the queue manager, respectively.

We wanted to check some design consistency aspects of the server, e.g. the server is in its starting state **ServerStart** if and only if its three components are in their starting states **TStart**, **CStart** and **QStart** respectively. Similarly, we wanted to prove that the MTTS server is in state **TShutdown** if and only if its three components are in their respective shutdown states **TShutdown**, **CShutdown** and **QShutdown**. Although, the implementation of method “start()” verified the definition of typestate **ServerStart**, the implementation of method “stop()” did not verify the definition of typestate **ServerShutdown**. Method “stop()” does not shutdown all its components but only the “queueManager”.

We report this as a flaw in the design of the MTTS server application. Due to the size of the MttsServer class and all the classes it uses, discovering this design flaw would not be possible through direct code inspection.

```

@ClassStates({

@State(name="ServerStart",

inv="Full(queueManager) in QStart *

Full(OpControlRemote) in CStart *

Full(TaskRegistrationRemote) in TStart"),

@State(name="ServerShutdown",

inv="Full(queueManager) in QShutdown *

Full(OpControlRemote) in CShutdown *

Full(TaskRegistrationRemote) in TShutdown"),

})

class MttsServer {

private OpControl OpControlRemote;

private TaskRegistration TaskRegistrationRemote;

private QueueManager queueManager;

@Perm(ensures="Full(this) in ServerStart")

public void start() throws MttsException { ... }

@Perm(requires="Full(this) in ServerStart",

ensures="Full(this) in ServerShutdown")

public void stop() throws MttsException {

queueManager.shutdown();

}

...

}

```

### 4.3 Discussion on the Limitations of Plural

We verified significant properties of the MTTS application ranging from simple non-null properties to absence of deadlocks and mutual exclusion to a critical section. Our experience dictates that Plural is a practical tool that can effectively be used to verify complex system properties that are harder to verify using other automated approaches. We also used Plural to check design decision in the implementation of the MTTS. We consider that the specification we have written can be used to enhance the quality of the implementation of the MTTS application. The mere exercise of writing abstractions (typestates) for an application forced us to fully understand and evaluate the MTTS application. The incompleteness of the written specifications are mainly due to the incompleteness of the analysis performed by Plural.

In the following, we summarise Plural limitations. Some of these limitations have already been discussed in previous sections.

- The Plural tool does not provide support to the analysis of programs with loops. For instance, method “run()” in class ExecutionThread loops while no termination request has not been placed - “while(! terminate){...}”. To check method “run()”, we modified it so that it loops once at the most - “if(! terminate){ ... }”. The if-statement abstracts the while-loop statement. This abstraction is a source of incompleteness in the analysis we performed of the MTTS application. Nonetheless, abstracting loops as conditional statements is often a decision made in the implementation of formal methods tools, e.g. the ESC/Java tool [7] implements a similar approach to deal with loops.

- Plural does not provide support to integer arithmetic. So, one cannot define invariants that use integer variables. Plural provides support to the analysis

of boolean expressions that check equality or non-equality of references, or to boolean expressions that check (non-) nullness of references.

In the implementation of the MTTS, class `IMutexImp` implements a mutex algorithm that is used to synchronise threads. Mutexes can be acquired or released. Thus, if a thread acquires a lock then no other thread can acquire the same lock. A thread can acquire a lock several times. So, it must release the lock the same number of times it acquired it for any other thread to (eventually) be able to acquire the lock. However, in Plural it is not possible to define a typestate that describes the situation when a thread has acquired a lock several times as this will require the invariant related to the typestate to rely on an integer arithmetic expression “nesting > 1”.

- Plural does not implement a strong specification typechecker, so programmers can unconsciously write specifications that include misspelled (nonexistent) typestates, and the Plural analysers can unconsciously use the misspelled typestate in their analysis. Plural does not issue any error on a specification that uses a nonexistent typestate.

- Plural does not provide support to reachability analysis. If a thread object is in state **Acq**, will the object ever be in state **NotAcq**? Plural does not provide support to reachability analysis. Nonetheless, in practice, for small classes, one can inspect the code and trace how states evolve. For large classes and large pieces of code this becomes impossible.

- Method “execute()” in Figure 2 transitions a task object from typestate **Ready** to typestate **Running**, and thereafter to typestate **Finished**. These two transitions occur both within method “execute()”. Typestate **Ready** is required by method “execute()” and typestate **Finished** is produced by method “execute()”. **Running** is an intermediate typestate for which the specification of method “execute()” does not provide any information. Not being able to reason about intermediate program states is a limitation of the analysis performed by the Plural tool. The information about intermediate states can be used by programmers (and tools) to assert certain facts that otherwise cannot be asserted. For instance, in the verification of the MTTS, we could not specify the property stating that a running task cannot be deleted.

## 5 Conclusion and Future Work

The MTTS is a relatively large size commercial application that implements a server with a thread pool that runs processing tasks. The specification and verification of the MTTS was a challenging and laborious task. The authors spent about six months writing the specifications and verifying the MTTS application with Plural. We specified and verified forty nine Java classes with 14451 lines of Java code and 546 lines of program specifications written in Plural. The automation of the analyses performed by the Plural tool ranges from a couple of milliseconds for the verification of small classes to a couple of minutes for the verification of large classes, e.g. the server class. The first author had previous

experience in the specification and verification of Java applications using JML but did not have any previous experience with Plural. The second author had no previous experience in the use of formal methods tools. The code of the MTTS was not originally documented so we needed to write its documentation prior to its specification and verification. We kept the code of the MTTS unchanged as much as possible and tried to keep the semantics of the code intact whenever we introduced any changes to it.

This is the first case study on the use of Plural for the verification of a commercial large sized application. Some of the limitations of Plural (see discussion in Section 4.3 for a full list) hampered our specification and verification work. Nonetheless, we managed to specify and verify important design properties backing the implementation of the MTTS application. The written typestate specifications can further be used to generate a collection of documents describing the behaviour of the MTTS, which can be used for the quality assurance team of Novabase for different purposes.

We are currently working on the implementation of some features to overcome some of these limitations. The two authors and Radu Siminiceanu, at the National Institute of Aerospace in Virginia, are currently working on a formal methods based approach to the verification of Plural and  $\mathcal{A}$ eminium specifications. Hence, specifications are translated into an abstract state-machine that captures all possible behaviour of the specifications, and the EVMDD (Edge-Valued MDD) symbolic model-checker [15] is used to check the specifications. Furthermore, we are working on a Petri net inspired semantics to represent access permissions. The translation is carried out for specifications alone, regardless of the program source code. This ongoing work enables reachability analysis of Plural specifications and the checking for absence of misspelled specifications.

Writing program specifications for medium sized or large applications is a laborious and sometimes complex task. To help programmers write Plural specifications, we are currently working on a prototype tool that infers likely access permissions automatically. Roughly speaking, we analyse a Java program and store in a graph the information on how program objects are read or written. The graph is stored as an XML file, which is then used to generate the access permissions. We are currently working on the implementation of the prototype tool as an Eclipse plug-in.

**Acknowledgements.** We thank Jonathan Aldrich and Nels Beckman at Carnegie Mellon University, and Filipe Martins, Manuel Beja, and Paulo Casanova at Novabase for useful feedback on the work presented in this paper.

## References

1. Ahmed, I., Cataño, N.: Architecture of Novabase' MTTS application. Technical report, The University of Madeira (2010), [http://www3.uma.pt/ncatano/aeminium/Documents\\_files/mtts.pdf](http://www3.uma.pt/ncatano/aeminium/Documents_files/mtts.pdf)

2. Barnett, M., DeLine, R., Fhndrich, M., Rustan, K., Leino, M., Schulte, W.: Verification of object-oriented programs with invariants. *Journal of Object Technology* 3 (2004)

3. Bierhoff, K., Aldrich, J.: Modular typestate checking of aliased objects. In: Proceedings of the 22nd Annual ACM SIGPLAN Conference on Object-Oriented Programming Systems and Applications, OOPSLA, pp. 301–320 (2007)

4. Bierhoff, K., Beckman, N.E., Aldrich, J.: Practical API protocol checking with access permissions. In: Drossopoulou, S. (ed.) ECOOP 2009. LNCS, vol. 5653, pp. 195–219. Springer, Heidelberg (2009)

5. Bierhoff, N.B.K., Aldrich, J.: Verifying correct usage of atomic blocks and types-state. In: OOPSLA (2008)

6. Boyland, J.: Checking interference with fractional permissions. In: Proceedings of the 10th International Conference on Static Analysis, SAS, pp. 55–72 (2003)

7. Burdy, L., Cheon, Y., Cok, D., Ernst, M.D., Kiniry, J., Leavens, G.T., Rustan, K., Leino, M., Poll, E.: An overview of JML tools and applications (2003)

8. Cataño, N., Wahls, T.: Executing JML specifications of java card applications: A case study. In: 24th ACM Symposium on Applied Computing, Software Engineering Track (SAC-SE), Honolulu, Hawaii, March 8-12, pp. 404–408 (2009)

9. DeLine, R., Fähndrich, M.: Enforcing high-level protocols in low-level software. In: Proceedings of the ACM SIGPLAN 2001 Conference on Programming Language Design and Implementation, PLDI, pp. 59–69 (2001)

10. DeLine, R., Fähndrich, M.: The Fugue protocol checker: Is your software baroque (2003)

11. Girard, J.-Y.: Linear logic. *Theoretical Computer Science* 50, 1–102 (1987)

12. Leavens, G.T., Baker, A.L., Ruby, C.: Preliminary design of JML: A behavioral interface specification language for Java. *ACM SIGSOFT (Software Engineering Symposium)* 31(3), 1–38 (2006)

13. Novabase, <http://www.novabase.pt>

14. The Plural Tool, <http://code.google.com/p/pluralism/>

15. Roux, P., Siminiceanu, R.: Model checking with edge-valued decision diagrams. In: NASA Formal Methods Symposium (NFM), NASA/CP-2010-216215, pp. 222–226. Langley Research Center, NASA (April 2010)

16. Stork, S., Marques, P., Aldrich, J.: Concurrency by default: using permissions to express dataflow in stateful programs. In: Conference on Object-Oriented Programming Systems and Applications, OOPSLA, pp. 933–940 (2009)

17. Strom, R.E., Yemini, S.: Typestate: A programming language concept for enhancing software reliability. *IEEE Transactions on Software Engineering* 12, 157–171 (1986)

# Runtime Verification of Typical Requirements for a Space Critical SoC Platform\*

Luca Ferro<sup>1</sup>, Laurence Pierre<sup>1</sup>, Zeineb Bel Hadj Amor<sup>1</sup>,

Jérôme Lachaize<sup>2</sup>, and Vincent Lefftz<sup>2</sup>

<sup>1</sup> TIMA (CNRS-INPG-UJF), 46 Av. Félix Viallet, 38031 Grenoble cedex, France

<sup>2</sup> EADS Astrium Satellites, Central Engineering, 31402 Toulouse cedex, France

**Abstract.** SystemC TLM (Transaction Level Modeling) enables the description of complex Systems on Chip (SoC) at a high level of abstraction. It offers a number of advantages regarding architecture exploration, simulation performance, and early software development. The tendency is therefore to use TLM-based descriptions of SoC platforms as golden models that, by essence, must be flawless.

In this paper, a SoC critical embedded platform under development by Astrium is used as proof-of-concept demonstrator, to assess the ISIS prototype tool which is devoted to the verification of SystemC TLM designs. Given temporal properties that capture the intended requirements, ISIS automatically instruments the design with ad hoc checkers that inform about the satisfaction of the properties during simulation.

After a description of the target platform design, we show that the PSL language enables the unambiguous expression of the required properties, and that the checkers produced by ISIS verify their satisfaction with a limited simulation time overhead.

## 1 Introduction

As the complexity of Systems on Chips (SoC's) drastically increases, the need for new design methodologies is compelling, and the interest in languages like SystemC [1] is growing (SystemC is in fact a library of C++ classes for modeling electronic circuits). SystemC TLM (*Transaction Level Modeling*) [10] favors design reuse, architecture exploration, and early software development [4]. Also, due to its high level of abstraction, in particular for specifying the communication of complex data types between the components of the SoC, the simulation of TLM models is several orders of magnitude faster than RTL (*Register Transfer Level*) simulation, thus considerably improving productivity in SoC design [15]. Hence it is widely being adopted, and TLM specifications tend to become golden reference models [11] that, by essence, must be completely flawless. To that goal, Assertion-Based Verification (ABV) brings an attractive solution.

ABV addresses the issue of verifying that the design obeys a given collection of temporal assertions (or properties). Those assertions, written in languages such

---

\* This work is supported by the French project SoCKET (FUI).

as the IEEE standards PSL [3] and SVA [2], are used to capture the desired characteristics. They provide a way to drive the formal analysis of the design model. This is now a well-established technology *at the RT level* [19]. The leading CAD companies have integrated property checking in their RTL simulators; e.g., *ModelSim* (Mentor Graphics), *VCS* (Synopsys) and the *Incisive* platform of Cadence allow to complement VHDL or Verilog descriptions with temporal assertions to be checked during simulation. *No equivalent solution* exists for SystemC TLM descriptions, which are algorithmic specifications that make use of elaborate communication models for complex data types (“transactions”) and communication interfaces.

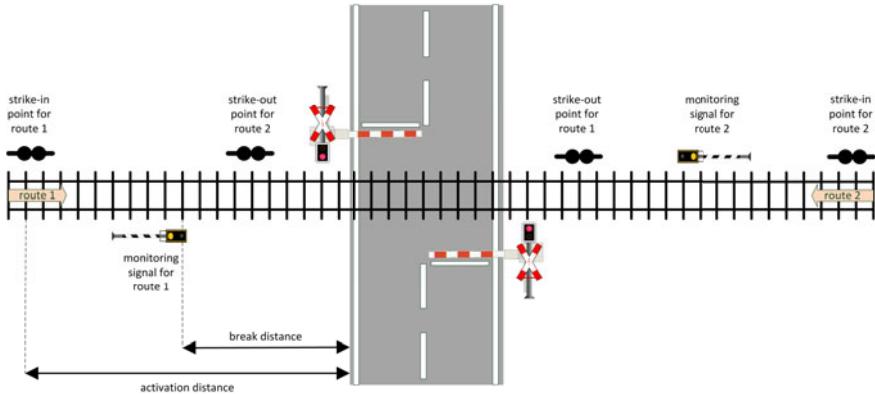

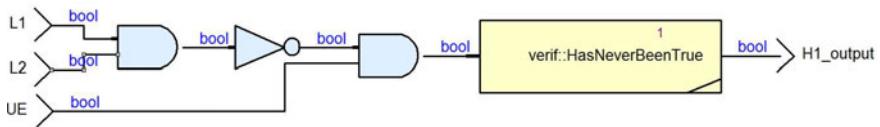

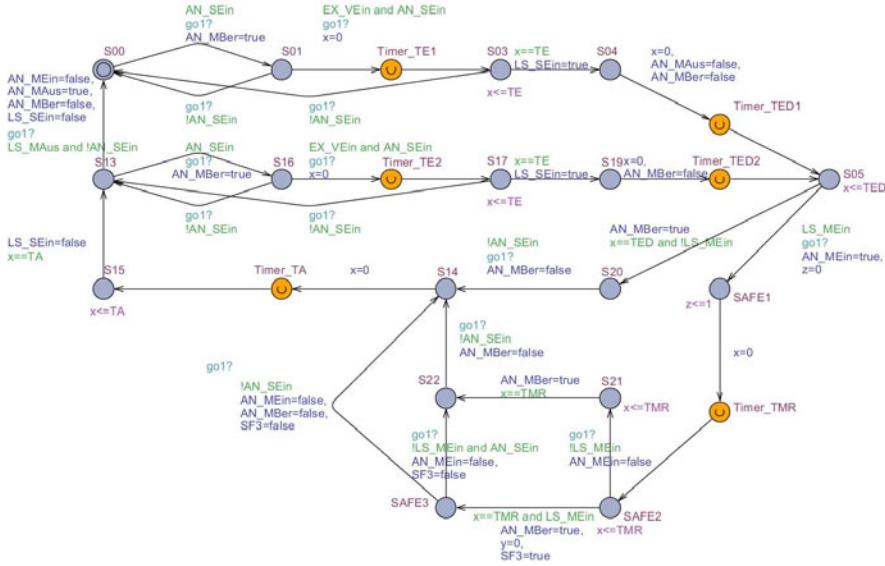

ISIS [23,9] is an academic tool that actually answers the need for ABV at the system level. Given PSL assertions that express the intended behaviour, it automatically instruments the SystemC TLM design with ad hoc checkers. During simulation, those checkers provide information about the satisfaction of the assertions. The original simulation testbenches can be used, there is no need of specific ones. In the context of TLM descriptions, assertions of interest mainly target the verification of the hardware/software interoperability in the interactions on the SoC. They express properties regarding communications i.e., properties associated with transactional events (for instance, data are transferred at the right place in memory, a transfer does not start before the completion of the previous one, etc.). ISIS enables the verification of those kinds of requirements, and is usable with timed or untimed models. This paper illustrates its applicability to a representative SoC platform developed by Astrium.

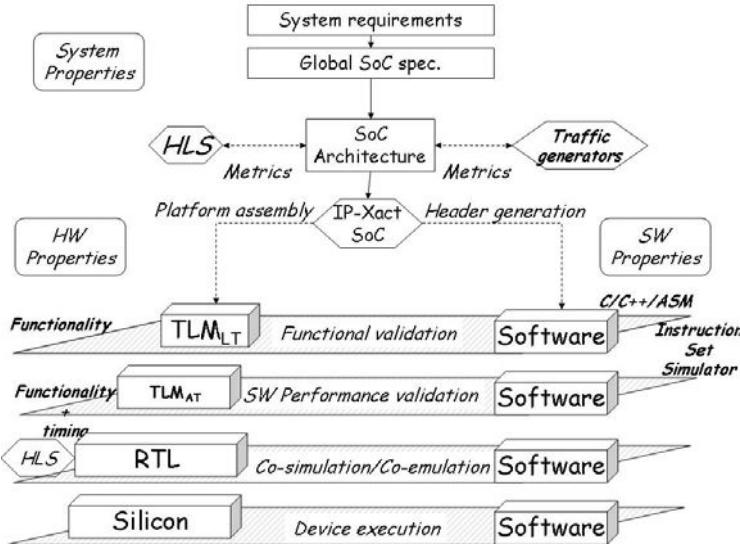

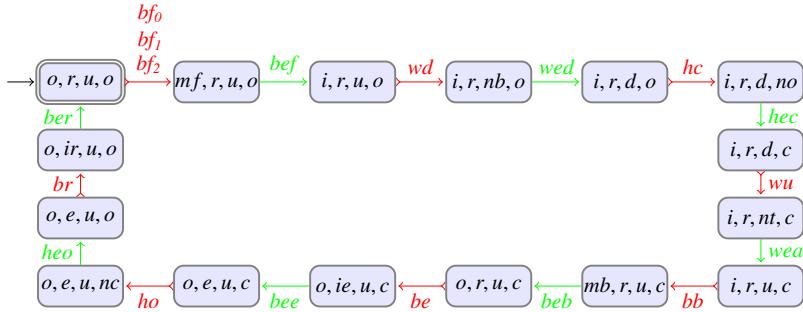

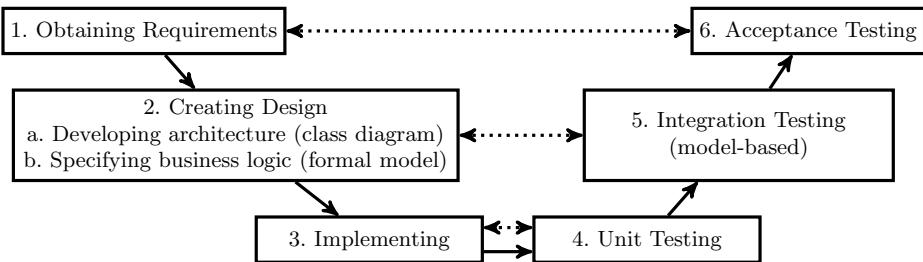

The SoCKET project<sup>1</sup> gathers industrial and academic partners to address the issue of design methodologies for *critical* embedded systems. At different phases of the SoCKET design flow (see Fig. 1) [18], the satisfaction of dedicated properties has to be guaranteed (namely at the System level, and after HW/SW partitioning). Some of these requirements, originally provided as textual descriptions, can be fully disambiguated when translated into PSL assertions.

The ultimate goal of Astrium is to verify these properties at the System Level using TLM-based Virtual Platforms, but also at the implementation level using RTL designs. The ISIS tool fits the Functional Validation and SW Performance Validation steps.

In that framework, Astrium is developing a toolbox in SystemC dedicated to architecture prototyping and to benchmarking architecture performance. The prototype platform is an assembly of software and hardware models. Following the standard test process, we usually run one or more test scenario and check the results. This procedure is useful, but its outcome is only a measure of the quality of the results. It does not ensure that there is no unexpected side effect. The ISIS approach gives the possibility to complement this process by automatically instrumenting the code with functional properties in order to check them while executing a test scenario (e.g., to verify that a client does not read data in a DMA destination area when a transfer is on-going).

---

<sup>1</sup> *SoC toolKit for critical Embedded sysTems*, see <http://socket.imag.fr/>

Fig. 1. SoCKET design flow [18]

## 2 ABV for SoC Platforms

### 2.1 Expression of Requirements for TLM Designs

**Brief Overview of PSL.** The core of the PSL (*Property Specification Language*) language is the *Temporal layer* that gives the possibility to describe complex temporal relations, evaluated over a set of evaluation cycles. Basic expressions of the *Boolean layer* are used by the other layers. The *Modeling layer* is used to augment what is possible using PSL alone, in particular it allows to manage auxiliary (global) variables. The *Boolean* and *Modeling* layers borrow the syntax of the hardware description language in which the PSL assertions are included (SystemC, or more generally C++, in our case).

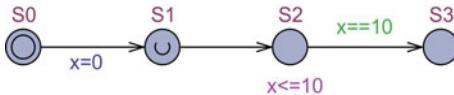

Formulas of the FL (Foundation Language) class of the PSL Temporal layer essentially represent linear temporal logic. Their semantics is defined with respect to *execution traces* (we will see thereafter that these traces are obtained by different discretizations depending on the abstraction level).

One key basic operator of the FL class is *strong until*, denoted *until!* or  $U$ : roughly speaking,  $\varphi$  until!  $\psi$  holds iff there exists an evaluation point in the trace from which  $\psi$  holds, and  $\varphi$  holds until that point.

The PSL formula *always*  $\varphi$  means that  $\varphi$  must be verified on each evaluation point of the trace.

Using the strong *next\_event!* operator, formula  $\text{next\_event!}(b)(\varphi)$  requires the satisfaction of  $\varphi$  the next time the boolean expression  $b$  is verified.

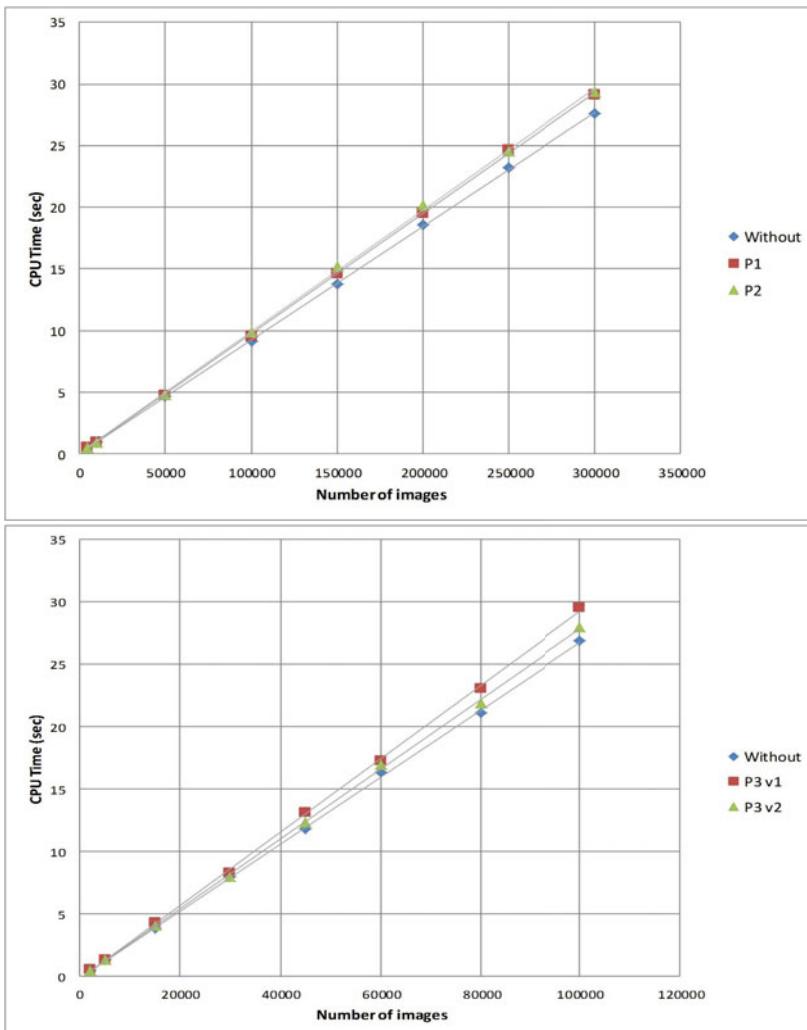

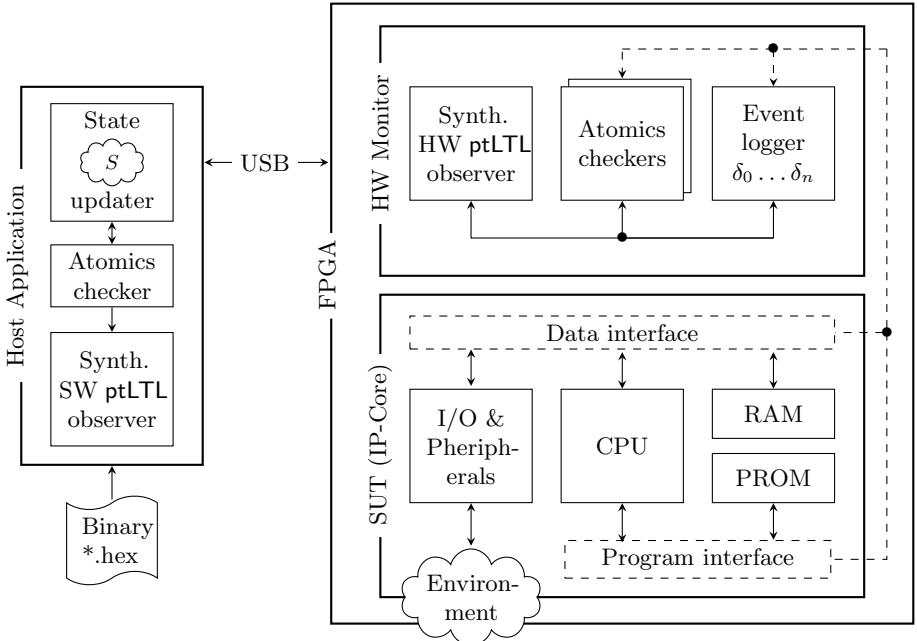

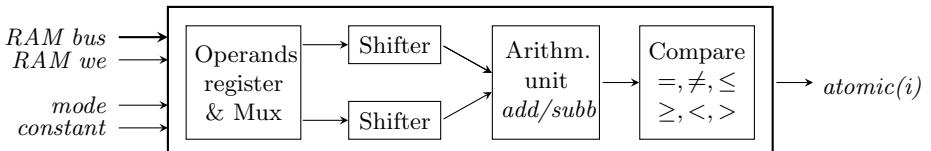

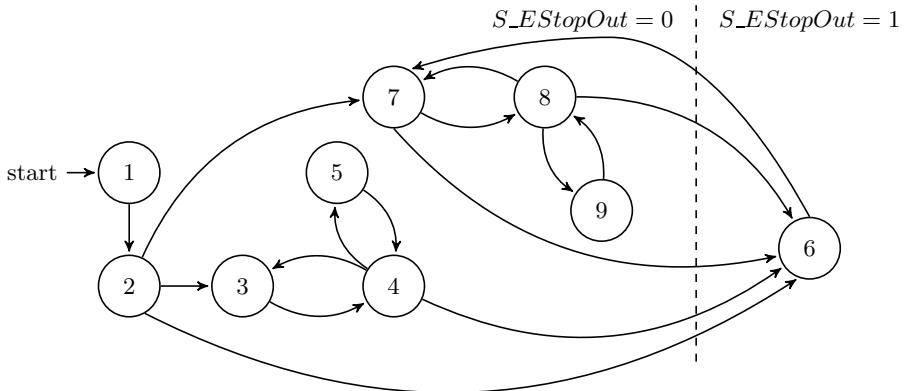

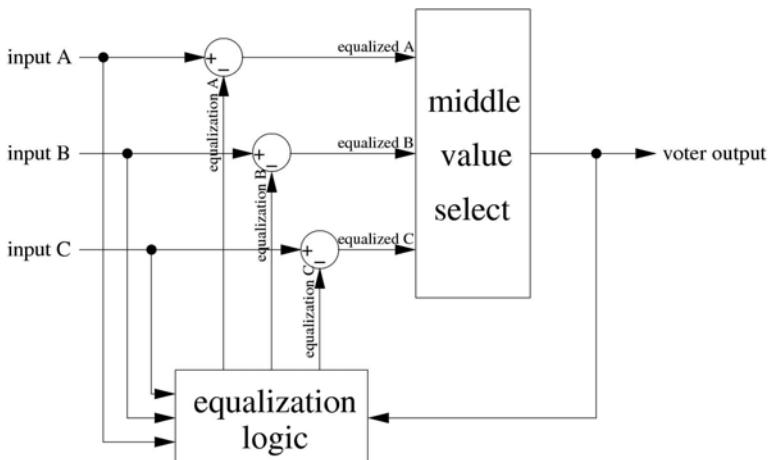

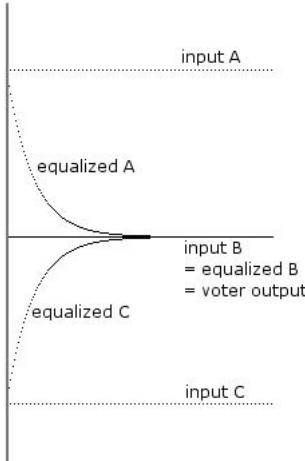

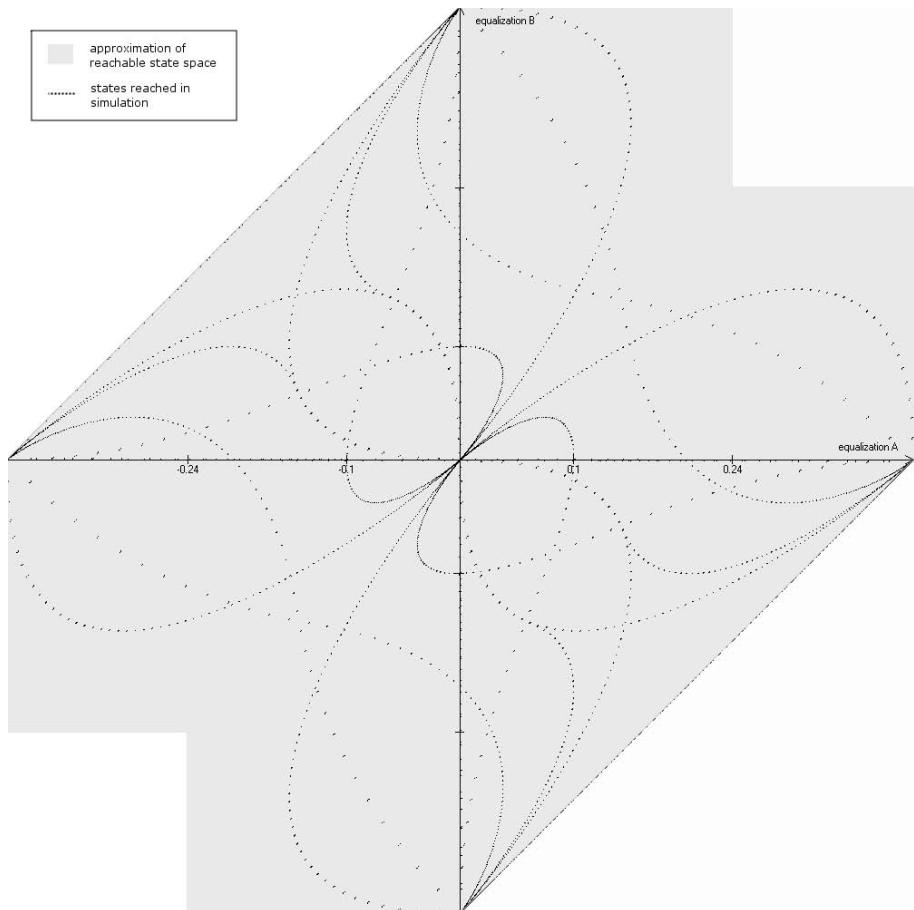

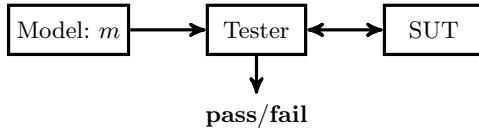

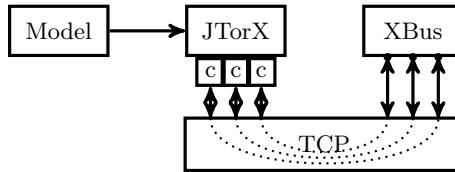

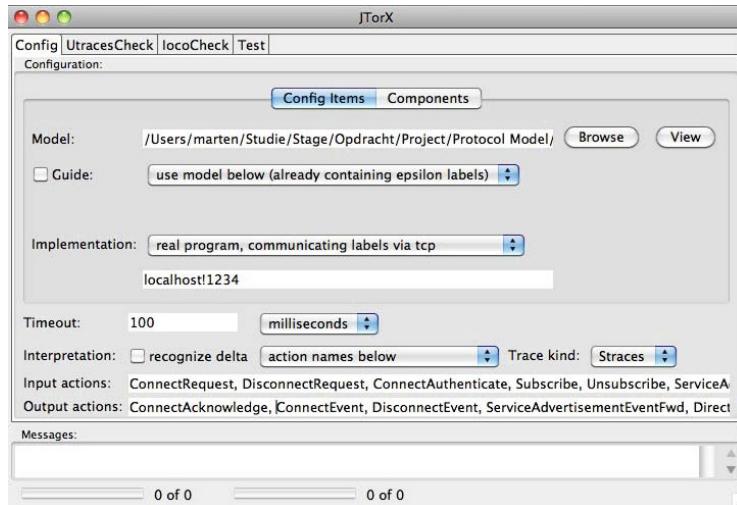

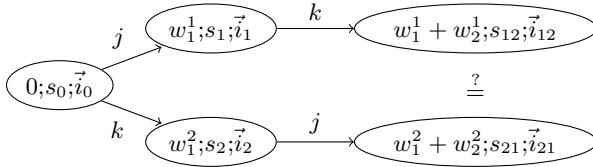

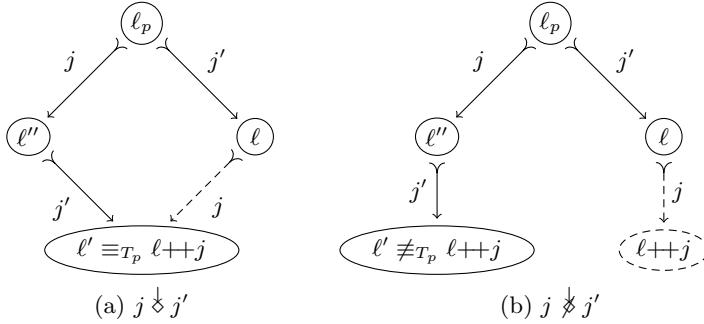

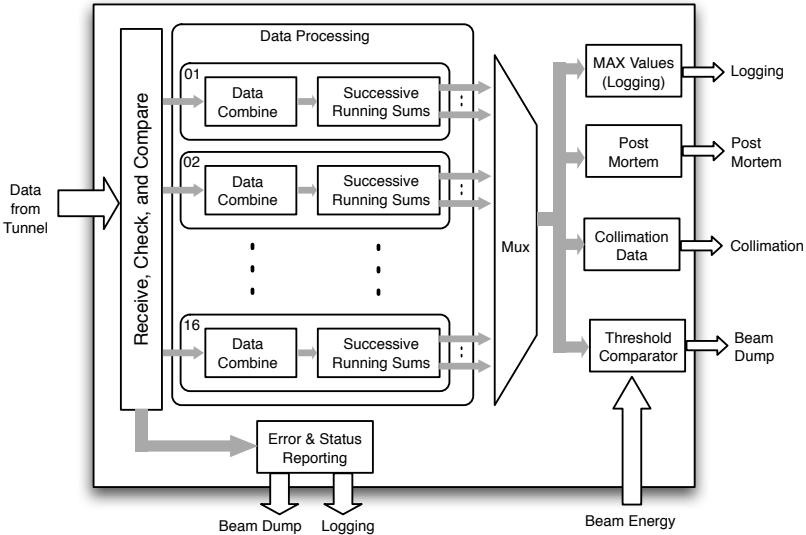

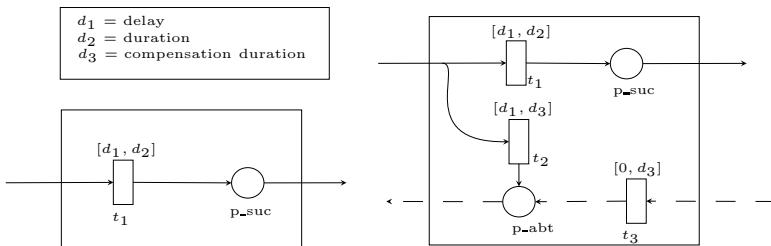

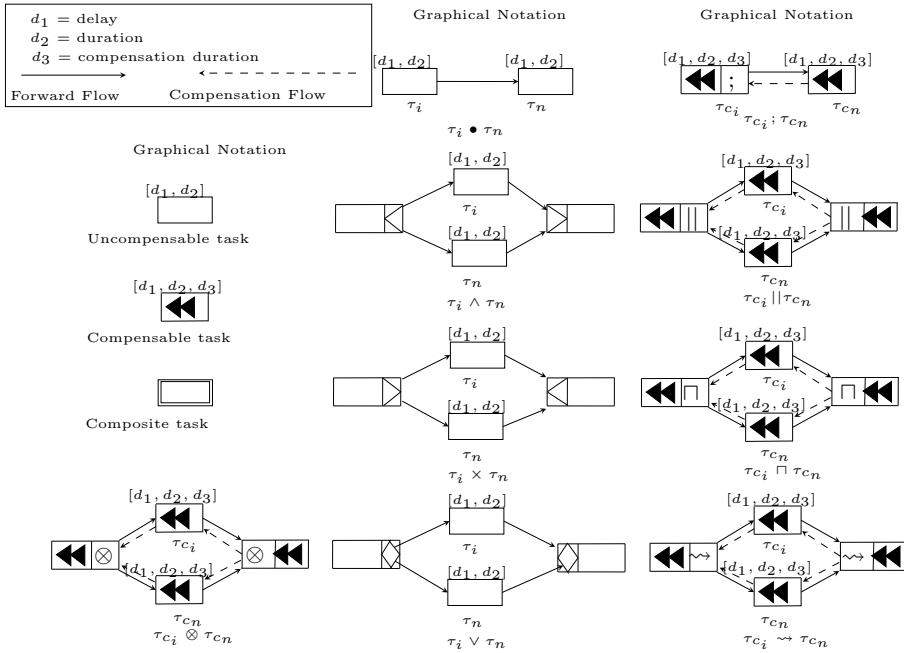

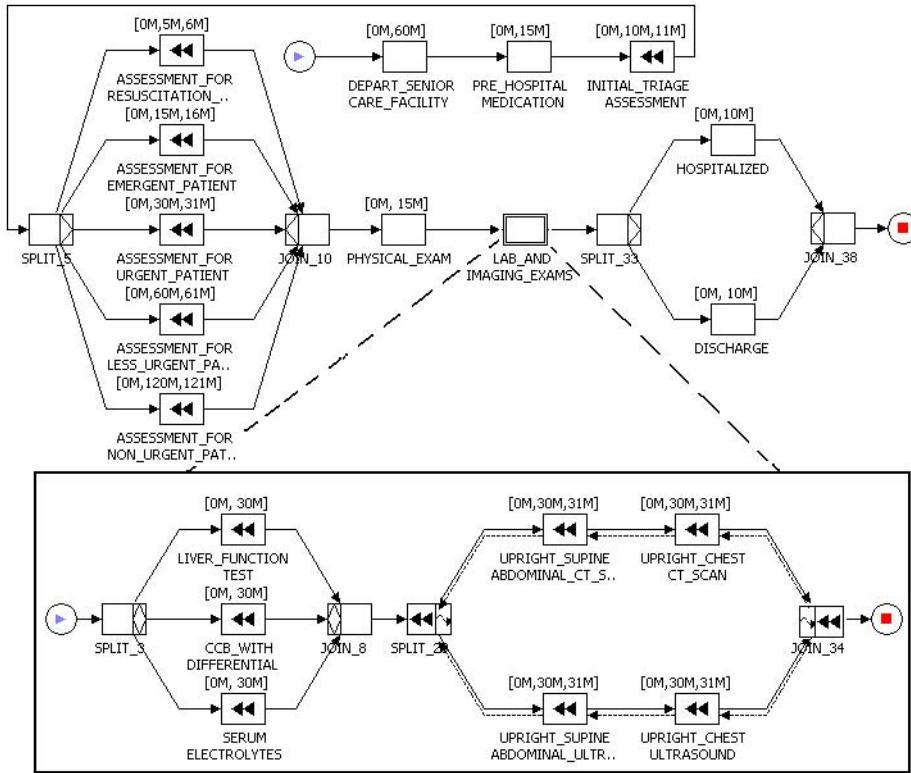

Finally, formula  $\varphi$  before!  $\psi$  means that  $\varphi$  must be satisfied before the point from which  $\psi$  holds.